JP2011237992A - テスト項目生成装置及び方法及びプログラム - Google Patents

テスト項目生成装置及び方法及びプログラム Download PDFInfo

- Publication number

- JP2011237992A JP2011237992A JP2010108362A JP2010108362A JP2011237992A JP 2011237992 A JP2011237992 A JP 2011237992A JP 2010108362 A JP2010108362 A JP 2010108362A JP 2010108362 A JP2010108362 A JP 2010108362A JP 2011237992 A JP2011237992 A JP 2011237992A

- Authority

- JP

- Japan

- Prior art keywords

- test

- loop

- route

- test item

- specified

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Stored Programmes (AREA)

- Debugging And Monitoring (AREA)

Abstract

【課題】 生成されるテスト項目の爆発的増加を防ぐ。

【解決手段】 本発明は、設計モデル内のフロー図を読み込み、ユーザ端末から指定されたループ回数の上限値であるユーザ指定ループ最大通過数を取得し、設計モデルのフロー図内の全ノードと全エッジを読み込み、ユーザ指定ループ最大通過数で指定された回数のループを通る開始エッジから終了エッジまでの経路を探索することにより抽出された経路をテスト経路とし、該テスト経路の途中に出現するループの回数であるループ出現回数をカウントし、カウントされたループ出現回数Mと、ユーザ指定ループ最大通過数Nと比較し、M>Nの経路探索は打ち切り、M≦Nの経路だけを出力することによりテスト項目の爆発的増加を防ぐ。

【選択図】 図9

【解決手段】 本発明は、設計モデル内のフロー図を読み込み、ユーザ端末から指定されたループ回数の上限値であるユーザ指定ループ最大通過数を取得し、設計モデルのフロー図内の全ノードと全エッジを読み込み、ユーザ指定ループ最大通過数で指定された回数のループを通る開始エッジから終了エッジまでの経路を探索することにより抽出された経路をテスト経路とし、該テスト経路の途中に出現するループの回数であるループ出現回数をカウントし、カウントされたループ出現回数Mと、ユーザ指定ループ最大通過数Nと比較し、M>Nの経路探索は打ち切り、M≦Nの経路だけを出力することによりテスト項目の爆発的増加を防ぐ。

【選択図】 図9

Description

本発明は、テスト項目生成装置及び方法及びプログラムに係り、特に、ソフトウェア開発における結合テスト用のテスト項目を生成するためのテスト項目生成装置及び方法及びプログラムに関する。

ソフトウェア開発のためのテスト項目を生成する技術として、UML(設計書相当)のアクティビティ図、クラス図を入力とし、テスト経路やテストデータをテスト項目として出力する技術(第1の従来技術)がある(例えば、非特許文献1参照)。

また、入力したソースプログラムの実行経路(2回以上のループを除く)を出力する技術(第2の従来技術)がある(例えば、特許文献1参照)。

また、入力したソースコードの実行経路(複数回のループを含む)を出力する技術(第3の従来技術)がある(例えば、特許文献2参照)。

張暁晶、星野隆、"設計モデルを用いたテスト項目抽出とテストデータ生成手法"、電子情報通信学会技術研究報告、KDSE、知能ソフトウェア工学、Technical report of IEICE. KBSE 109(41) pp. 37-42, 20090514.

しかしながら、上記第1の従来技術は、経路抽出に関して、ループを0回、1回通るような経路しか抽出できないため、ループの上限値が1より大きい場合の限界値テスト項目の抽出を行うことができない。例えば、パスワード誤入力の回数がn(n=2)と指定されている場合、n回誤入力した際の動作を確認するテスト項目の抽出を行うことができないという問題がある。

また、上記第2の従来技術は、ソースコードを入力としており、フロー図(設計書)を扱うことができない。また、経路抽出に関して、ループを0回、1回通るような経路しか抽出できないという問題がある。

また、上記第3の従来技術は、ソースコードを対象としており、フロー図(設計書)を扱うことができない。

本発明は、上記の点に鑑みなされたもので、ソフトウェア設計情報から繰り返し処理に関する必要十分なテスト項目を抽出することが可能なテスト項目生成装置及び方法及びプログラムを提供することを目的とする。

上記の課題を解決するため、本発明(請求項1)は、ソフトウェア開発のためのテスト項目を生成するテスト項目抽出装置であって、

設計モデル内のフロー図を読み込み、ユーザ端末から指定されたループ回数の上限値であるユーザ指定ループ最大通過数を取得し、記憶手段に格納する入力手段と、

記憶手段から設計モデルのフロー図内の全ノードと全エッジを読み込み、ユーザ指定ループ最大通過数で指定された回数のループを通る開始エッジから終了エッジまでの経路を探索することにより抽出された経路をテスト経路とし、該テスト経路の途中に出現するループの回数であるループ出現回数をカウントする経路探索手段と、

経路探索数手段でカウントされたループ出現回数Mと、ユーザ指定ループ最大通過数Nと比較し、M≦Nのテスト経路をテスト項目として出力するテスト項目生成手段と、を有する。

設計モデル内のフロー図を読み込み、ユーザ端末から指定されたループ回数の上限値であるユーザ指定ループ最大通過数を取得し、記憶手段に格納する入力手段と、

記憶手段から設計モデルのフロー図内の全ノードと全エッジを読み込み、ユーザ指定ループ最大通過数で指定された回数のループを通る開始エッジから終了エッジまでの経路を探索することにより抽出された経路をテスト経路とし、該テスト経路の途中に出現するループの回数であるループ出現回数をカウントする経路探索手段と、

経路探索数手段でカウントされたループ出現回数Mと、ユーザ指定ループ最大通過数Nと比較し、M≦Nのテスト経路をテスト項目として出力するテスト項目生成手段と、を有する。

上記のように、テスト対象であるプログラムの振る舞いのうち、テスト項目に含める範囲を簡便に指定することができ、その範囲の振る舞いを網羅的に抽出することができる。

また、フロー図を入力することにより、開発段階の早期にテスト項目が抽出できると共に、フロー図は設計情報であるため、設計書通りに実装されているかを確認するテスト項目を生成することが可能となる。

また、本発明(請求項2)は、上記の経路探索手段において、探索途中でカウントするテスト経路の途中のループ出現回数が、ユーザ指定ループ最大通過数を超えた場合には、探索を打ち切る手段を含む。

これにより、テスト項目数の爆発的増加を防ぐことができる。

本発明(請求項3)は、ソフトウェア開発のためのテスト項目を生成するテスト項目抽出方法であって、

記憶手段、入力手段、経路探索手段、テスト項目生成手段と、を有する装置において、

入力手段が、設計モデル内のフロー図を読み込み、ユーザ端末から指定されたループ回数の上限値であるユーザ指定ループ最大通過数を取得し、記憶手段に格納する入力ステップと、

経路探索手段が、記憶手段から設計モデルのフロー図内の全ノードと全エッジを読み込み、ユーザ指定ループ最大通過数で指定された回数のループを通る開始エッジから終了エッジまでの経路を探索することにより抽出された経路をテスト経路とし、該テスト経路の途中に出現するループの回数であるループ出現回数をカウントする経路探索ステップと、

テスト項目生成手段が、経路探索数ステップでカウントされたループ出現回数Mと、ユーザ指定ループ最大通過数Nと比較し、M≦Nのテスト経路をテスト項目として出力するテスト項目生成ステップと、からなる。

記憶手段、入力手段、経路探索手段、テスト項目生成手段と、を有する装置において、

入力手段が、設計モデル内のフロー図を読み込み、ユーザ端末から指定されたループ回数の上限値であるユーザ指定ループ最大通過数を取得し、記憶手段に格納する入力ステップと、

経路探索手段が、記憶手段から設計モデルのフロー図内の全ノードと全エッジを読み込み、ユーザ指定ループ最大通過数で指定された回数のループを通る開始エッジから終了エッジまでの経路を探索することにより抽出された経路をテスト経路とし、該テスト経路の途中に出現するループの回数であるループ出現回数をカウントする経路探索ステップと、

テスト項目生成手段が、経路探索数ステップでカウントされたループ出現回数Mと、ユーザ指定ループ最大通過数Nと比較し、M≦Nのテスト経路をテスト項目として出力するテスト項目生成ステップと、からなる。

また、本発明(請求項4)は、上記の経路探索ステップにおいて、

探索途中でカウントするテスト経路の途中のループ出現回数が、ユーザ指定ループ最大通過数を超えた場合には、探索を打ち切る。

探索途中でカウントするテスト経路の途中のループ出現回数が、ユーザ指定ループ最大通過数を超えた場合には、探索を打ち切る。

本発明(請求項5)は、請求項1または2に記載のテスト項目抽出装置を構成する各手段としてコンピュータを機能させるためのテスト項目抽出プログラムである。

上記のように本発明によれば、ソフトウェア開発における結合テスト用のテスト項目生成において、探索途中経路に存在するループ経路の数が、一定数(ユーザが指定した値)を超えた場合には、そこで経路探索を打ち切りにすることにより、テスト項目数の爆発的増加を防ぐことが可能となる。

また、探索途中経路に含まれる全ループ経路の中で、ループ出現回数が閾値(ユーザ指定の最大通過数)を超えるものがなければ探索は続けられるため、最終的には、各ループ経路の出現回数(ユーザ指定ループ最大通過数以下)と各ループを通る順番の組み合わせのパターンを網羅したテスト経路を出力できる。また、閾値として与える入力はユーザ指定ループ最大通過数だけでよいため、ユーザはほかの条件(個々のループ出現回数の上限値)について考慮する必要がない。

また、テスト経路の定義は開始エッジから終了エッジまでの経路であるため、終了エッジを見つけた時点で探索途中経路をテスト経路として出力するため、漏らさず網羅的なテスト経路を出力することが可能である。

さらに、フロー図(ソフトウェア設計情報)を入力として扱えるため、開発段階の早期にテスト項目の抽出が可能となる。また、設計書通りに実装されているかどうかを確認するテスト項目生成が可能となる。

以下図面と共に、本発明の実施の形態を説明する。

本発明の説明をする前に、本明細書で用いる用語について定義する。

・フロー図:ソフトウェア設計情報の一種であり、振る舞い(ソフトウェアの処理の流れ)を表す。フローチャート、UMLアクティビティ図などの種類がある。

・エッジ:フロー図の矢印部分。両側(始点と終点)にノードが接続されている(但し、開始エッジのみ、始点にノードが接続されていない。

・ノード:フロー図内の節の部分であり、各ノードはエッジ(始点との接続)群を保持している。

・開始エッジ:フロー図に1つ存在し、フローの開始を表すエッジである。

・終了エッジ:フロー図に1つ以上存在し、フローの終了を表すエッジである。

・エッジ用スタック:フロー図内でたどったエッジを順番どおりに保存するためのスタックである。

・最上位:スタックで積まれた要素のうち最も最近に積まれたものを指す。

・次展開エッジ群:次に辿るエッジ(自ノードと始点で接続しているエッジ)の候補群である。

・次展開用エッジ群用スタック:図1に示すように、これまで辿った経路中で、まだ辿っていない次展開エッジ群を保存しておくスタックを指す。

・現在エッジ:現在辿ろうとしているエッジ(新しくエッジ用スタックに追加するため、次展開エッジ群から取り出したエッジ)を指す。

・現在次展開エッジ群:次展開エッジ群用スタックの最上位を指す。

・ループ経路:X,E0,E1,…,En(但し、X≠EiかつEnの次展開エッジ群にXが含まれる)となるフロー図内の部分経路である。

・現在ループ経路:これまでの経路(エッジ用スタックに積まれているエッジ)において、スタック最上位のエッジから、最上位に最も近い現在エッジまでの経路を指す。

・ユーザ指定ループ最大通過数:ユーザが指定したループ最大通過数の上限値であり、これを探索打ち切りの閾値として用いる。

・ループ出現回数:ループが経路中に何回出現したかの回数である。

本発明のテスト項目抽出装置の構成を説明する。

図2は、本発明の一実施の形態におけるテスト項目抽出装置の構成図である。

同図に示すテスト項目抽出装置100は、ユーザ端末10からユーザ指定の最大通過回数を取得すると共に、設計モデル20を読み込む入力部110、メモリ120に格納された情報から経路を抽出する経路抽出部130、抽出された経路からテスト項目表を生成するテスト項目表生成部140、テスト項目表を出力する出力部150から構成される。

設計モデル20は、設計モデル生成装置にて設計ドキュメント群を読み込むことにより生成されたものであり、XMIファイルとしてディスク装置等に格納されているものとする。

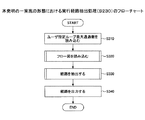

図3は、本発明の一実施の形態における概要動作のフローチャートである。

ステップ210) 入力部110は、設計モデル(XMI(XML Metadata Interchange)ファイル)20を読み込み、メモリ120に格納する。

ステップ230) 経路抽出部130は、メモリ120から設計モデル内のフロー図リストを読み込み、当該フロー図からテストすべき実行経路を抽出する。当該フロー図は、ソフトウェア設計情報を指す。

ステップ280) テスト項目表生成部140は、経路抽出部130で抽出された情報を項目としてまとめるため、画面名、処理の振る舞い(テスト経路)、テスト項目作成時に必要となる情報を取得し、処理の振る舞い(テスト経路)、テスト項目作成時に必要となる情報をひとつのテスト項目としてグループ化する。

ステップ290) テスト項目表生成部140は、上記のテスト項目群とメモリ120から読み出したフロー図を用いて、テスト項目群を要素として持つ表(テスト項目表)を作成し、出力部150からテスト項目表を出力する。

次に、上記の図3のステップ230の実行経路抽出処理について詳述する。

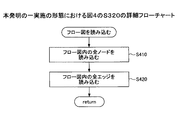

図4は、本発明の一実施の形態における実行経路抽出処理(S230)のフローチャートである。

ステップ310) 経路抽出部130は、ユーザ端末10からユーザによって指定されたループ最大通過回数(以下、「ユーザ指定ループ最大通過数」と記す)を取得してメモリ120に格納する。

ステップ320) 経路抽出部130は、メモリ120からフロー図を読み込む。当該処理の詳細は図5で説明する。

ステップ330) 経路抽出部130は、読み込んだフロー図からループ最大通過回数で指定された回数のループを通るような経路のリストを生成する。当該処理の詳細は図7で説明する。

ステップ340) 経路抽出部130は、生成された経路リストをテスト項目表生成部140に出力する。

上記の図4のステップ320の詳細を以下に示す。

図5は、本発明の一実施の形態における図4のS320の詳細フローチャートである。

ステップ410) 経路抽出部130は、メモリ120から図6に示すフロー図内の全ノードを読み込む。当該ノード情報は、ノードID,ノード内テキスト、次展開エッジ群からなる。

ステップ420) 経路抽出部130は、メモリ120から図6に示すフロー図内の全エッジを読み込む。当該エッジ情報は、エッジID,始点接続ノードID,終点接続ノードID,遷移条件からなる。

上記の図4のステップ330の詳細を以下に示す。

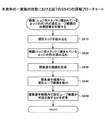

図7は、本発明の一実施の形態における図4のS330の詳細フローチャートである。

ステップ510) 経路抽出部130は、ステップ420で読み込まれた開始エッジを次展開エッジ群用スタックに積む。なお、当該経路抽出部130は内部にバッファを有し、当該バッファにスタックの領域を設けるものとする。

ステップ515) 次展開エッジ群用スタックは空であるかを判定し、空である場合は当該処理を終了する。

ステップ516) 次展開エッジ群用スタックの最上位にある次展開エッジ群に要素があるかを判定し、ない場合はステップ580に移行する。

ステップ520) 次展開エッジ群スタックの最上位にある要素(現在次展開エッジ群)から、ひとつエッジを得て現在エッジとする。

ステップ530) 現在次展開エッジ群から現在エッジを取り除く。

ステップ540) 経路(エッジ用スタックに積まれているエッジの列)内のループ出現回数を計算する。当該処理は、探索途中経路に存在する現在ループ経路の数(ループ出現回数)を計算するものである。当該処理の詳細については後述する。

ステップ545) ループの出現回数(ループ最大出現回数)がユーザ端末10より入力されたユーザ指定ループ最大通過数より大きければ、ステップ515に移行する。当該処理は、探索途中の経路のループ最大出現回数がユーザ指定ループ最大通過数を超えたらその経路の探索を打ち切ることである。なお、「ループ最大出現回数」とは、探索途中経路に含まれる複数のループ経路のうちループ出現回数が最大であるループ経路のループ出現回数である。

ステップ550) 現在エッジをエッジ用スタックに積む。

ステップ560) 現在のエッジのもつ終点ノードIDに基づいて、フロー図からノードを取得し、そのノードのエッジ(始点との接続)群を取得し、その取得したエッジ(始点との接続)群を、次展開エッジとして、次展開エッジ群スタックに積む。

ステップ565) 現在のエッジが終了ノードに接続していない場合はステップ515に移行する。

ステップ570) エッジ用スタックの中身を経路として出力し、ステップ515に出力する。

ステップ580) 次展開エッジ群用スタックをポップする。

ステップ585) ポップしたエッジ用スタックが空である場合は、当該処理を終了する。空でない場合はステップ590に移行する。

ステップ590) エッジ用スタックをポップして、処理を終了する。

次に、上記の図7のステップ540の経路(エッジ用スタックに積まれているエッジの列)内の現在ループ経路の出現回数を計算する処理について詳述する。

図8は、本発明の一実施の形態における図7のS540の詳細フローチャートである。

ステップ610) 経路抽出部130は、バッファから現在エッジを読み込む。

ステップ620) 経路(エッジ用スタックに積まれているエッジの列)を読み込む。

ステップ630) 探索途中経路を生成する。具体的には、経路を複製し、複製した経路を探索途中経路とする。

ステップ640) 探索途中経路の先頭から、先頭に一番近い現在エッジまでを現在ループ経路が何回出現するか計算する。

ステップ650) 探索途中経路内で現在ループ経路が何回出現するか(ループ出現回数)を求める。当該ループ出現回数を求める手法として、文献1「R.S. boyer: J. S. Moore (1997). "A fast string searching algorithm". Comm. ACM 20: 762-772」等の技術を用いることができる。当該文献1の手法は、文字列照合のアルゴリズムであるが、ひとつのエッジをひとつの文字とみなし、経路(エッジの列)を文字列とみなせば適用可能である。

次に、上記の図7のステップ570のエッジ用スタックの中身を経路として出力する処理について詳述する。

上記の処理を具体的に説明する。

図9は、本発明の一実施の形態における経路抽出部によるテスト経路抽出処理の例を示す。入力されたフロー図を同図(A)に示す。ユーザ端末10から入力されたユーザ指定最大通過数をN、ループ最大出現回数をMとし、この例ではN=3とする。テスト経路の候補は、開始エッジから終了エッジまでの経路とする。

なお、以下のテスト経路において、(X,Y)*2は、X,Y,X,Yの略であり、(X,Y)*3は、X,Y,X,Y,X,Yの略である。

(1)フロー図のテスト経路E0→E1→E2→E5の場合は、ループ回路なし(M=0)であり、M≦Nであるので、テスト経路として抽出する。

(2)フロー図のテスト経路E0→E1→E2→E3→E4→E1→E2→E5の場合は、ループ経路は{E1,E2,E3,E4}であり、ループ回数M=1となり、M≦Nであるので、テスト経路として抽出する。

(3)フロー図のテスト経路E0→(E1→E2→E3→E4)*2→E1→E2→E5の場合は、ループ経路は{E1,E2,E3,E4}であり、ループ回数は"*2"により、M=2となり、M≦Nであるので、テスト経路として抽出する。

(4)フロー図のテスト経路E0→(E1→E2→E3→E4)*3→E1→E2→E5の場合は、ループ経路は{E1,E2,E3,E4}であり、ループ回数は"*3"によりM=3となり、M≦Nであるので、テスト経路として抽出する。

(5)フロー図のテスト経路E0→(E1,E2,E3,E4)*4→E1,E2,E5の場合は、ループ経路は{E1,E2,E3,E4}であり、ループ回数は"*4"によりM=4となり、M>Nであるため途中で探索を打ち切る。図10に示すように、例えば、現在エッジが「E1」である場合には、すでにM>Nとなっているため途中で探索を打ち切る。

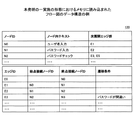

また、図9のフロー図はループ経路が1つのみの場合を示したが、図11に示すようにフロー図に複数のループ経路が存在する場合がある。図11の例では、ユーザ指定ループ最大通過数(N)=2とした場合で、フロー図において、A→B→C→D→G→C→D→E→Fをループ[小]とし、A→C→D→E→H→B→C→D→E→Fをループ[大]とする。同図のように2つのループ経路が存在する場合は、これらのループ[小]とループ[大]の組み合わせより抽出される経路が決定される。図11の例では(1)〜(19)の経路がM≦Nを満たす経路として抽出される。

図12は、本発明の一実施の形態におけるテスト項目抽出装置の適用例を示す。

設計モデル20から同図(A)のようなフロー図が入力され、ユーザ端末10からユーザ指定ループ最大通過数(上限値)=3が入力され、上記のような経路抽出部130の処理により、以下のようなテスト経路がテスト項目としてテスト項目生成部140に入力される。フロー図は、ユーザ名とパスワードが入力され、パスワードの入力を3回間違えるとロックされるロジックを示している。

(1)テスト経路E0→E1→E2→E5は、パスワードを1回で正しく入力した際の動作を確認するテスト項目である。

(2)テスト経路E0→E1→E2→E3→E4→E1→E2→E5は、パスワードを1回間違った際の動作を確認するテスト項目である。

(3)テスト経路E0→(E1,E2,E3,E4)*2→E1→E2→E5は、パスワードを2回間違った際の動作を確認するテスト項目である。

(4)テスト経路E0→(E1,E2,E3,E4)*3→E1→E2→E5は、パスワードを3回間違った際の動作を確認するテスト項目である。

上記の(1)、(2)については従来の技術でも抽出可能であるが、本発明では、(3)、(4)についても抽出が可能となる。

これにより、テスト項目生成部140は、図12(B)に示すようなテスト項目表を生成し、出力部150に出力する。

なお、上記のテスト項目抽出装置の各構成要素の動作をプログラムとして構築し、テスト項目抽出装置として利用されるコンピュータにインストールして実行させる、または、ネットワークを介して流通させることが可能である。

また、構築されたプログラムをハードディスクや、フレキシブルディスク・CD−ROM等の可搬記憶媒体に格納し、コンピュータにインストールする、または、配布することが可能である。

本発明は、上記の実施の形態の例に限定されることなく、特許請求の範囲内において、種々変更・応用が可能である。

10 ユーザ端末

20 設計モデル

100 テスト項目抽出装置

110 入力部

120 メモリ

130 経路抽出部

140 テスト項目表生成部

150 出力部

20 設計モデル

100 テスト項目抽出装置

110 入力部

120 メモリ

130 経路抽出部

140 テスト項目表生成部

150 出力部

Claims (5)

- ソフトウェア開発のためのテスト項目を生成するテスト項目抽出装置であって、

設計モデル内のフロー図を読み込み、ユーザ端末から指定されたループ回数の上限値であるユーザ指定ループ最大通過数を取得し、記憶手段に格納する入力手段と、

前記記憶手段から前記設計モデルのフロー図内の全ノードと全エッジを読み込み、前記ユーザ指定ループ最大通過数で指定された回数のループを通る開始エッジから終了エッジまでの経路を探索することにより抽出された経路をテスト経路とし、該テスト経路の途中に出現するループの回数であるループ出現回数をカウントする経路探索手段と、

前記経路探索数手段でカウントされた前記ループ出現回数Mと、前記ユーザ指定ループ最大通過数Nと比較し、M≦Nのテスト経路をテスト項目として出力するテスト項目生成手段と、

を有することを特徴とするテスト項目抽出装置。 - 前記経路探索手段は、

探索途中でカウントする前記テスト経路の途中のループ出現回数が、前記ユーザ指定ループ最大通過数を超えた場合には、探索を打ち切る手段を含む

請求項1記載のテスト項目抽出装置。 - ソフトウェア開発のためのテスト項目を生成するテスト項目抽出方法であって、

記憶手段、入力手段、経路探索手段、テスト項目生成手段と、を有する装置において、

前記入力手段が、設計モデル内のフロー図を読み込み、ユーザ端末から指定されたループ回数の上限値であるユーザ指定ループ最大通過数を取得し、前記記憶手段に格納する入力ステップと、

経路探索手段が、前記記憶手段から前記設計モデルのフロー図内の全ノードと全エッジを読み込み、前記ユーザ指定ループ最大通過数で指定された回数のループを通る開始エッジから終了エッジまでの経路を探索することにより抽出された経路をテスト経路とし、該テスト経路の途中に出現するループの回数であるループ出現回数をカウントする経路探索ステップと、

前記テスト項目生成手段が、前記経路探索数ステップでカウントされた前記ループ出現回数Mと、前記ユーザ指定ループ最大通過数Nと比較し、M≦Nのテスト経路をテスト項目として出力するテスト項目生成ステップと、

からなることを特徴とするテスト項目抽出方法。 - 前記経路探索ステップにおいて、

探索途中でカウントする前記テスト経路の途中のループ出現回数が、前記ユーザ指定ループ最大通過数を超えた場合には、探索を打ち切る

請求項4記載のテスト項目抽出方法。 - 請求項1または2に記載のテスト項目抽出装置を構成する各手段としてコンピュータを機能させるためのテスト項目抽出プログラム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010108362A JP2011237992A (ja) | 2010-05-10 | 2010-05-10 | テスト項目生成装置及び方法及びプログラム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010108362A JP2011237992A (ja) | 2010-05-10 | 2010-05-10 | テスト項目生成装置及び方法及びプログラム |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2011237992A true JP2011237992A (ja) | 2011-11-24 |

Family

ID=45325906

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010108362A Pending JP2011237992A (ja) | 2010-05-10 | 2010-05-10 | テスト項目生成装置及び方法及びプログラム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2011237992A (ja) |

-

2010

- 2010-05-10 JP JP2010108362A patent/JP2011237992A/ja active Pending

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5324792B2 (ja) | システムの動作を検証するシステムおよび方法 | |

| Fraigniaud et al. | What can be decided locally without identifiers? | |

| JP2005025763A (ja) | 構造化文書の分割プログラム、分割装置、及び分割方法 | |

| CN104657140A (zh) | 代码生成方法及装置 | |

| Azriel et al. | SoK: An overview of algorithmic methods in IC reverse engineering | |

| JP6331756B2 (ja) | テストケース生成プログラム、テストケース生成方法、及びテストケース生成装置 | |

| Carmona et al. | Process discovery algorithms using numerical abstract domains | |

| JP7040003B2 (ja) | グラフ生成方法、情報処理装置およびグラフ生成プログラム | |

| JP2013077124A (ja) | ソフトウェアテストケース生成装置 | |

| US7827179B2 (en) | Data clustering system, data clustering method, and data clustering program | |

| Pomeranz et al. | Test generation for multiple state-table faults in finite-state machines | |

| US8418119B2 (en) | Logical circuit netlist reduction and model simplification using simulation results containing symbolic values | |

| Gafni et al. | The weakest failure detector for solving k-set agreement | |

| BELL et al. | Model-based mutation testing using pushdown automata | |

| JP2010267023A (ja) | テストデータ生成方法及び装置及びプログラム | |

| Fey et al. | Finding good counter-examples to aid design verification | |

| JP2011237992A (ja) | テスト項目生成装置及び方法及びプログラム | |

| US11526529B2 (en) | Efficient discovery of a binary tree pattern from a large amount of binary tree data | |

| JP4370335B2 (ja) | Lsi解析プログラム、該プログラムを記録した記録媒体、lsi解析装置、およびlsi解析方法 | |

| Huang et al. | A game-theoretic foundation for the maximum software resilience against dense errors | |

| JP2011237991A (ja) | テスト項目生成装置及び方法及びプログラム | |

| JP6773115B2 (ja) | 類似データ検索装置、類似データ検索方法および記録媒体 | |

| JP6636873B2 (ja) | ソースコードからの仕様抽出装置 | |

| JP5404720B2 (ja) | 単独の異常系シナリオを任意回数実行するテスト項目生成装置及び方法及びプログラム | |

| CN111428245B (zh) | 面向自主芯片硬件逻辑漏洞的激活序列生成方法 |