JP2011129017A - 半導体集積回路およびプログラム転送方法 - Google Patents

半導体集積回路およびプログラム転送方法 Download PDFInfo

- Publication number

- JP2011129017A JP2011129017A JP2009288864A JP2009288864A JP2011129017A JP 2011129017 A JP2011129017 A JP 2011129017A JP 2009288864 A JP2009288864 A JP 2009288864A JP 2009288864 A JP2009288864 A JP 2009288864A JP 2011129017 A JP2011129017 A JP 2011129017A

- Authority

- JP

- Japan

- Prior art keywords

- program

- flash memory

- serial flash

- serial

- interface means

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Abstract

【課題】様々なタイプのシリアル型フラッシュメモリに柔軟に対応して、格納されているプログラムの転送を行うことのできる半導体集積回路およびプログラム転送方法を提供する。

【解決手段】CPU1は、ROM3から読み出した変数受信プログラムを実行して、通信インターフェース部5を介してシリアル型フラッシュメモリ100の仕様に関する変数データを受信し、ROM3から読み出したシリアルフラッシュメモリリードプログラムを、受信した変数データを用いて実行し、シリアルインターフェース部4を介してシリアル型フラッシュメモリ100に格納されているプログラムをRAM2へ転送する。

【選択図】図1

【解決手段】CPU1は、ROM3から読み出した変数受信プログラムを実行して、通信インターフェース部5を介してシリアル型フラッシュメモリ100の仕様に関する変数データを受信し、ROM3から読み出したシリアルフラッシュメモリリードプログラムを、受信した変数データを用いて実行し、シリアルインターフェース部4を介してシリアル型フラッシュメモリ100に格納されているプログラムをRAM2へ転送する。

【選択図】図1

Description

本発明は、半導体集積回路およびプログラム転送方法に関する。

携帯電話、デジタルカメラ、音楽プレーヤなどの携帯機器では、CPUを搭載する半導体集積回路の外部に不揮発性メモリであるフラッシュメモリを接続し、このフラッシュメモリにアプリケーションプログラムを格納することによりさまざまな機能を実現している。

従来、このプログラム格納用のフラッシュメモリには、CPUとの接続にアドレスバス、データバス、及び制御信号を使用するパラレル型のフラッシュメモリが用いられてきたが、近年、車載電子機器システムの高集積化、基板サイズの小型化に伴い、CPUとの接続端子が少ないシリアル型のフラッシュメモリが用いられるようになってきた。

しかし、シリアル型フラッシュメモリを使用する場合、半導体集積回路に搭載された汎用のシリアルインターフェース回路に接続するだけでは、CPUはシリアル型フラッシュメモリのアドレスを認識することができず、プログラムとして実行することができない。

そのため、従来、半導体集積回路の内部に搭載した、シリアル型フラッシュメモリのアドレスを認識するための専用のシリアルフラッシュインターフェース回路、もしくは専用のブートプログラムを用いて、シリアル型フラッシュメモリから半導体集積回路に内蔵のRAMへプログラムを転送し、この内蔵のRAMをアクセスすることによりプログラムを実行する方法が用いられている(例えば、特許文献1参照。)。

しかし、専用のハードウェア回路、もしくは専用のブートプログラムを搭載する場合、シリアル型フラッシュメモリとの接続性に自由度がないという問題があった。

そこで、本発明の目的は、様々なタイプのシリアル型フラッシュメモリに柔軟に対応して、格納されているプログラムの転送を行うことのできる半導体集積回路およびプログラム転送方法を提供することにある。

本発明の一態様によれば、CPUと、RAMと、変数受信プログラムおよびシリアルフラッシュメモリリードプログラムが格納されたROMと、シリアル型フラッシュメモリが接続されるシリアルインターフェース手段と、外部から送信されるデータを受信する通信インターフェース手段とを備え、前記CPUが、前記ROMから読み出した前記変数受信プログラムを実行して前記通信インターフェース手段を介して前記シリアル型フラッシュメモリの仕様に関する変数データを受信し、前記ROMから読み出した前記シリアルフラッシュメモリリードプログラムを、前記変数データを用いて実行し、前記シリアルインターフェース手段を介して前記シリアル型フラッシュメモリに格納されているプログラムを前記RAMへ転送することを特徴とする半導体集積回路が提供される。

また、本発明の別の一態様によれば、CPUと、RAMと、プログラム転送用プログラムが格納されたROMと、シリアル型フラッシュメモリが接続されるシリアルインターフェース手段と、外部から送信されるデータを受信する通信インターフェース手段とを備え、前記CPUが、前記ROMから読み出した前記プログラム転送用プログラムを実行して前記通信インターフェース手段を介してシリアルフラッシュメモリリードプログラムを受信し、前記受信した前記シリアルフラッシュメモリリードプログラムを実行し、前記シリアルインターフェース手段を介して前記シリアル型フラッシュメモリに格納されているプログラムを前記RAMへ転送することを特徴とする半導体集積回路が提供される。

また、本発明のさらに別の一態様によれば、CPUと、RAMと、変数受信プログラムおよびシリアルフラッシュメモリリードプログラムが格納されたROMと、シリアル型フラッシュメモリが接続されるシリアルインターフェース手段と、外部から送信されるデータを受信する通信インターフェース手段とを備える半導体集積回路へ、前記外部シリアル型フラッシュメモリに格納されているプログラムを転送するプログラム転送方法であって、前記CPUが、前記ROMから前記変数受信プログラムを読み出すステップと、前記変数受信プログラムを実行して前記通信インターフェース手段を介して前記シリアルフラッシュメモリの仕様に関する変数データを受信するステップと、前記ROMから前記シリアルフラッシュメモリリードプログラムを読み出すステップと、前記変数データを用いて前記シリアルフラッシュメモリリードプログラムを実行し、前記シリアルインターフェース手段を介して前記シリアル型フラッシュメモリに格納されているプログラムを前記RAMへ転送するステップとを実行することを特徴とするプログラム転送方法が提供される。

また、本発明のさらに別の一態様によれば、CPUと、RAMと、プログラム転送用プログラムが格納されたROMと、シリアル型フラッシュメモリが接続されるシリアルインターフェース手段と、外部から送信されるデータを受信する通信インターフェース手段とを備える半導体集積回路へ、前記シリアル型フラッシュメモリに格納されているプログラムを転送するプログラム転送方法であって、前記CPUが、前記ROMから前記プログラム転送用プログラムを読み出すステップと、前記プログラム転送用プログラムを実行して前記通信インターフェース手段を介してシリアルフラッシュメモリリードプログラムを受信するステップと、前記受信した前記シリアルフラッシュメモリリードプログラムを実行し、前記シリアルインターフェース手段を介して前記シリアル型フラッシュメモリに格納されているプログラムを前記RAMへ転送するステップとを実行することを特徴とするプログラム転送方法が提供される。

本発明によれば、様々なタイプのシリアル型フラッシュメモリに柔軟に対応して、シリアル型フラッシュメモリに格納されているプログラムの転送を行うことができる。

以下、本発明の実施例について図面を参照して説明する。なお、図中、同一または相当部分には同一の符号を付して、その説明は繰り返さない。

図1は、本発明の実施例1に係る半導体集積回路の構成の例を示すブロック図である。

本実施例の半導体集積回路10は、CPU1と、RAM2と、変数受信プログラムおよびシリアルフラッシュメモリリードプログラムが格納されたROM3と、シリアル型フラッシュメモリ100が接続されるシリアルインターフェース部4と、外部から送信されるデータを受信する通信インターフェース部5と、を備える。

通信インターフェース部5は、例えばUARTのような汎用の通信インターフェースであり、通信速度が遅いものの、広く普及しているために、多種多様な外部デバイスと接続することができる。

ROM3は、例えばマスクROMであり、シリアル型フラッシュメモリ100の仕様に関する変数データを受信するための変数受信プログラム、およびシリアル型フラッシュメモリ100からデータを読み出すためのシリアルフラッシュメモリリードプログラムが格納されている。

ここで、シリアル型フラッシュメモリ100の仕様に関する変数データには、メモリ容量、ブロックサイズ、ページサイズ、アクセス速度、プログラムサイズ、格納アドレス、バス幅などの情報が含まれている。

変数受信プログラムは、外部から通信インターフェース部5を介して変数データを受信し、その変数データをRAM2に格納する、という処理を行うプログラムである。

また、シリアルフラッシュメモリリードプログラムは、シリアル型フラッシュメモリの仕様に関する変数データを外部から読み込んで、その仕様のシリアル型フラッシュメモリに適したリードコマンドを発行する方式のプログラムである。

シリアル型フラッシュメモリ100には、半導体集積回路10にて実行する、アプリケーションプログラムなどのプログラムが格納されている。

本実施例では、シリアル型フラッシュメモリ100に格納されているプログラムを実行する場合、そのプログラムを一旦RAM2へ転送し、その後CPU1がRAM2をアクセスすることによりそのプログラムを実行する。

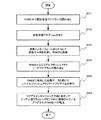

そこで、本実施例におけるプログラムの転送処理について、図2のフロー図を用いて説明する。

図2は、シリアル型フラッシュメモリ100からプログラムを転送するときに、本実施例のCPU1が実行する処理のフローを示すフロー図である。

シリアル型フラッシュメモリ100からのプログラムの転送の開始にあたって、CPU1は、まず、ROM3から変数受信プログラムを読み出す(ステップS01)。

続いて、CPU1は、その変数受信プログラムを実行し、通信インターフェース部5を介して、例えば外部デバイスからシリアル型フラッシュメモリ100の仕様に関する変数データを受信し(ステップS02)、その変数データをRAM2に格納する(ステップS03)。

次に、CPU1は、ROM3からシリアルフラッシュメモリリードプログラムを読み出し(ステップS04)、RAM2に格納した変数データを読み出しながらシリアルフラッシュメモリリードプログラムを実行し(ステップS05)、シリアルインターフェース部4を介してシリアル型フラッシュメモリ100に格納されているプログラムをRAM2へ転送する(ステップS06)。この転送の終了により、一連の処理は終了する。

このような本実施例によれば、使用するシリアル型フラッシュメモリの仕様に関する変数データを外部から受信し、その変数データを使用してROM3に格納されているシリアルフラッシュメモリリードプログラムを実行するので、どのような仕様のシリアルフラッシュメモリからでもデータを読み出すことができ、そのシリアル型フラッシュメモリに格納されているプログラムをRAM2へ転送することができる。

図3は、本発明の実施例2に係る半導体集積回路の構成の例を示すブロック図である。

本実施例の半導体集積回路20の基本的な構成は、実施例1の半導体集積回路10と同じである。本実施例の半導体集積回路20が実施例1と異なる点は、実施例1のROM3の代わりに、プログラム転送用プログラムが格納されたROM3Aを備えている点である。

プログラム転送用プログラムは、外部から通信インターフェース部5を介してシリアルフラッシュメモリリードプログラムを受信し、そのシリアルフラッシュメモリリードプログラムをRAM2に格納する、という処理を行うプログラムである。

ここで、外部から受信するシリアルフラッシュメモリリードプログラムは、実施例1で用いたシリアルフラッシュメモリリードプログラムとは異なり、指定されたシリアル型フラッシュメモリの仕様に応じたリードコマンドを発生する方式のプログラムである。このようにすることで、実施例1における変数データの変更では対応できないような新規のシリアル型フラッシュメモリ100に対しても、シリアル型フラッシュメモリ100に格納されているプログラムをRAM2に格納することが可能になる。

次に、本実施例における、シリアル型フラッシュメモリ100からのプログラムの転送処理について、図4のフロー図を用いて説明する。

図4は、シリアル型フラッシュメモリ100からプログラムを転送するときに、本実施例のCPU1が実行する処理のフローを示すフロー図である。

シリアル型フラッシュメモリ100からのプログラムの転送の開始にあたって、CPU1は、まず、ROM3からプログラム転送用プログラムを読み出す(ステップS11)。

続いて、CPU1は、そのプログラム転送用プログラムを実行し(ステップS12)、通信インターフェース部5を介して、例えば外部デバイスから、使用するシリアル型フラッシュメモリ100に適したシリアルフラッシュメモリリードプログラムを受信し、そのシリアルフラッシュメモリリードプログラムをRAM2に格納する(ステップS13)。

次に、CPU1は、RAM2に格納したシリアルフラッシュメモリリードプログラムを実行し(ステップS14)、シリアルインターフェース部4を介してシリアル型フラッシュメモリ100に格納されているプログラムをRAM2へ転送する(ステップS15)。この転送の終了により、一連の処理は終了する。

このような本実施例によれば、使用するシリアル型フラッシュメモリの仕様に適したシリアルフラッシュメモリリードプログラムを外部から受信し、実行するので、どのような仕様のシリアル型フラッシュメモリからでもデータを読み出すことができ、そのシリアル型フラッシュメモリに格納されているプログラムをRAM2へ転送することができる。

1 CPU

2 RAM

3、3A ROM

4 シリアルインターフェース部

5 通信インターフェース部

10、20 半導体集積回路

2 RAM

3、3A ROM

4 シリアルインターフェース部

5 通信インターフェース部

10、20 半導体集積回路

Claims (4)

- CPUと、

RAMと、

変数受信プログラムおよびシリアルフラッシュメモリリードプログラムが格納されたROMと、

シリアル型フラッシュメモリが接続されるシリアルインターフェース手段と、

外部から送信されるデータを受信する通信インターフェース手段と

を備え、

前記CPUが、

前記ROMから読み出した前記変数受信プログラムを実行して前記通信インターフェース手段を介して前記シリアル型フラッシュメモリの仕様に関する変数データを受信し、前記ROMから読み出した前記シリアルフラッシュメモリリードプログラムを、前記変数データを用いて実行し、前記シリアルインターフェース手段を介して前記シリアル型フラッシュメモリに格納されているプログラムを前記RAMへ転送する

ことを特徴とする半導体集積回路。 - CPUと、

RAMと、

プログラム転送用プログラムが格納されたROMと、

シリアル型フラッシュメモリが接続されるシリアルインターフェース手段と、

外部から送信されるデータを受信する通信インターフェース手段と

を備え、

前記CPUが、

前記ROMから読み出した前記プログラム転送用プログラムを実行して前記通信インターフェース手段を介してシリアルフラッシュメモリリードプログラムを受信し、前記受信した前記シリアルフラッシュメモリリードプログラムを実行し、前記シリアルインターフェース手段を介して前記シリアル型フラッシュメモリに格納されているプログラムを前記RAMへ転送する

ことを特徴とする半導体集積回路。 - CPUと、

RAMと、

変数受信プログラムおよびシリアルフラッシュメモリリードプログラムが格納されたROMと、

シリアル型フラッシュメモリが接続されるシリアルインターフェース手段と、

外部から送信されるデータを受信する通信インターフェース手段と

を備える半導体集積回路へ、前記外部シリアル型フラッシュメモリに格納されているプログラムを転送するプログラム転送方法であって、

前記CPUが、

前記ROMから前記変数受信プログラムを読み出すステップと、

前記変数受信プログラムを実行して前記通信インターフェース手段を介して前記シリアル型フラッシュメモリの仕様に関する変数データを受信するステップと、

前記ROMから前記シリアルフラッシュメモリリードプログラムを読み出すステップと、前記変数データを用いて前記シリアルフラッシュメモリリードプログラムを実行し、前記シリアルインターフェース手段を介して前記シリアル型フラッシュメモリに格納されているプログラムを前記RAMへ転送するステップと

を実行することを特徴とするプログラム転送方法。 - CPUと、

RAMと、

プログラム転送用プログラムが格納されたROMと、

シリアル型フラッシュメモリが接続されるシリアルインターフェース手段と、

外部から送信されるデータを受信する通信インターフェース手段と

を備える半導体集積回路へ、前記シリアル型フラッシュメモリに格納されているプログラムを転送するプログラム転送方法であって、

前記CPUが、

前記ROMから前記プログラム転送用プログラムを読み出すステップと、

前記プログラム転送用プログラムを実行して前記通信インターフェース手段を介してシリアルフラッシュメモリリードプログラムを受信するステップと、

前記受信した前記シリアルフラッシュメモリリードプログラムを実行し、前記シリアルインターフェース手段を介して前記シリアル型フラッシュメモリに格納されているプログラムを前記RAMへ転送するステップと

を実行することを特徴とするプログラム転送方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009288864A JP2011129017A (ja) | 2009-12-21 | 2009-12-21 | 半導体集積回路およびプログラム転送方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009288864A JP2011129017A (ja) | 2009-12-21 | 2009-12-21 | 半導体集積回路およびプログラム転送方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2011129017A true JP2011129017A (ja) | 2011-06-30 |

Family

ID=44291520

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009288864A Pending JP2011129017A (ja) | 2009-12-21 | 2009-12-21 | 半導体集積回路およびプログラム転送方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2011129017A (ja) |

-

2009

- 2009-12-21 JP JP2009288864A patent/JP2011129017A/ja active Pending

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8281072B2 (en) | Data processing system, controller, and method thereof for searching for specific memory area | |

| US6810444B2 (en) | Memory system allowing fast operation of processor while using flash memory incapable of random access | |

| CN1322441C (zh) | 多芯片封装型存储器系统 | |

| KR101173539B1 (ko) | 멀티프로세서 시스템 그리고 멀티프로세서 시스템의 초기화방법 | |

| WO2008138258A1 (en) | Peripheral device operation method, peripheral device and host | |

| KR100758301B1 (ko) | 메모리 카드 및 그것의 데이터 저장 방법 | |

| US9037783B2 (en) | Non-volatile memory device having parallel queues with respect to concurrently addressable units, system including the same, and method of operating the same | |

| KR102174337B1 (ko) | 메모리 시스템 및 이를 포함하는 전자 장치 | |

| US9471530B2 (en) | Semiconductor device and mobile terminal device | |

| CN114911412B (zh) | 一种数据读写方法和混合型存储器 | |

| KR20110078171A (ko) | 부팅가능한 휘발성 메모리 장치와 그를 구비한 메모리 모듈 및 프로세싱 시스템, 및 그를 이용한 프로세싱 시스템 부팅 방법 | |

| JP2011129017A (ja) | 半導体集積回路およびプログラム転送方法 | |

| JP4703753B2 (ja) | 情報処理装置、半導体記憶装置、及びプログラム | |

| CN101952813A (zh) | 具有卡片主机lsi的成套设备以及卡片主机lsi | |

| JP2002207715A (ja) | マイクロコンピュータ及びそれに用いるメモリ制御方法 | |

| US7377432B2 (en) | Interface converting apparatus | |

| JP4461760B2 (ja) | コンピュータの起動システム | |

| CN101754448A (zh) | 一种用于移动通信的双核智能卡及其数据传输处理方法 | |

| JP2004192051A (ja) | 共用端子制御装置 | |

| CN116775526B (zh) | 一种扩展装置及电子设备 | |

| CN103646001B (zh) | Dma数据传输控制方法及系统 | |

| US20100199000A1 (en) | Data storage device and method for operating the same | |

| JP2006127407A (ja) | 半導体集積回路 | |

| JP4024713B2 (ja) | データ処理システム及び制御装置 | |

| CN101126803B (zh) | 全球卫星定位系统及其控制集成电路及集成电路制作方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20111125 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20111205 |