JP2010238323A - Shift register and electronic device - Google Patents

Shift register and electronic device Download PDFInfo

- Publication number

- JP2010238323A JP2010238323A JP2009087287A JP2009087287A JP2010238323A JP 2010238323 A JP2010238323 A JP 2010238323A JP 2009087287 A JP2009087287 A JP 2009087287A JP 2009087287 A JP2009087287 A JP 2009087287A JP 2010238323 A JP2010238323 A JP 2010238323A

- Authority

- JP

- Japan

- Prior art keywords

- node

- terminal

- transistor

- potential

- supplied

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000011159 matrix material Substances 0.000 claims description 3

- 239000003990 capacitor Substances 0.000 description 15

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 8

- 241001125929 Trisopterus luscus Species 0.000 description 7

- 238000010586 diagram Methods 0.000 description 6

- 230000006866 deterioration Effects 0.000 description 5

- 239000004065 semiconductor Substances 0.000 description 5

- 230000000630 rising effect Effects 0.000 description 4

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 229920005591 polysilicon Polymers 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 101150010989 VCATH gene Proteins 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000008859 change Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000003780 insertion Methods 0.000 description 1

- 230000037431 insertion Effects 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 238000011144 upstream manufacturing Methods 0.000 description 1

Images

Landscapes

- Control Of El Displays (AREA)

- Shift Register Type Memory (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Abstract

【課題】シフトレジスタの消費電力を削減するとともに、動作を安定させる。

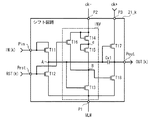

【解決手段】トランジスタT13〜T16によって、ノードAの電位Vaを反転させてノードBの電位VbとするインバータINVが構成される。前段のシフト回路からHighレベルの入力信号IN(k)が供給されると、ノードAの電位VaはHighレベルとなり、トランジスタT13がオンして、ノードBの電位VbはLowレベルとなる。電流は、電圧VHIのラインから、トランジスタT14,T15,T13を経由して、電圧VLWのアノードラインLaへと流れる。電圧VHIが印加される第2の端子P2とノードB間の電圧はトランジスタT14,T15によって分圧されて、各トランジスタのバイアス電圧が分圧される。従って、第2の端子P2とノードB間の抵抗の増加によってインバータINVに流れる貫通電流が低減されて消費電力が削減されるとともに、トランジスタT14、T15の閾値電圧のシフトが抑制されて、シフト回路21_kの動作が安定する。

【選択図】図3The power consumption of a shift register is reduced and the operation is stabilized.

Transistors T13 to T16 constitute an inverter INV that inverts a potential Va of a node A to a potential Vb of a node B. When the high-level input signal IN (k) is supplied from the preceding shift circuit, the potential Va of the node A becomes the high level, the transistor T13 is turned on, and the potential Vb of the node B becomes the low level. The current flows from the voltage VHI line to the anode line La of the voltage VLW via the transistors T14, T15, T13. The voltage between the second terminal P2 to which the voltage VHI is applied and the node B is divided by the transistors T14 and T15, and the bias voltage of each transistor is divided. Accordingly, an increase in resistance between the second terminal P2 and the node B reduces a through current flowing through the inverter INV, thereby reducing power consumption and suppressing a shift in threshold voltage of the transistors T14 and T15, thereby reducing the shift circuit. The operation of 21_k is stabilized.

[Selection] Figure 3

Description

本発明は、シフトレジスタ及びこれを備えてなる電子機器に関するものである。 The present invention relates to a shift register and an electronic apparatus including the shift register.

電子機器として、TFTを利用したゲートドライバ用シフトレジスタによって,有機EL素子やLCDをアクティブ駆動し、表示する表示装置が開発されている(例えば、特許文献1参照)。 As an electronic device, a display device has been developed in which an organic EL element or LCD is actively driven and displayed by a gate driver shift register using a TFT (for example, see Patent Document 1).

具体的には、アクティブ駆動型の表示装置は、行毎に配列された各画素をスイッチする画素回路を選択するゲートドライバを備え、このゲートドライバには、通常、シフトレジスタ回路が用いられる。 Specifically, the active drive type display device includes a gate driver that selects a pixel circuit that switches each pixel arranged in each row, and a shift register circuit is usually used as the gate driver.

このシフトレジスタ回路は、例えば、各段に、図10に示すようなインバータINVを備えたシフト回路を有し、複数のシフト回路が直列接続されることによって構成される。 This shift register circuit includes, for example, a shift circuit including an inverter INV as shown in FIG. 10 in each stage, and is configured by connecting a plurality of shift circuits in series.

このインバータINVは、トランジスタT51,T52によって構成される。トランジスタT51,T52は、nチャンネル型のFET(Field Effect Transistor;電界効果トランジスタ)によって構成されたポリシリコンまたはアモルファスシリコン薄膜トランジスタ(TFT;Thin Film Transistor)である。 The inverter INV is composed of transistors T51 and T52. The transistors T51 and T52 are polysilicon or amorphous silicon thin film transistors (TFTs) constituted by n-channel FETs (Field Effect Transistors).

インバータINVは、ノードAの電位を反転させ、反転させた電位をノードBの電位とする。 The inverter INV inverts the potential of the node A and sets the inverted potential as the potential of the node B.

しかし、従来のシフト回路では、トランジスタT51,T52がTFTによって構成されているため、インバータINVにHiレベルの入力信号が供給される入力期間と出力期間において、トランジスタT51,T52には、比較的大きなバイアス電圧が印加される。 However, in the conventional shift circuit, since the transistors T51 and T52 are constituted by TFTs, the transistors T51 and T52 are relatively large in the input period and the output period in which the Hi-level input signal is supplied to the inverter INV. A bias voltage is applied.

このため、電圧VHIの電源から、このトランジスタT51,T52を経由して電圧VLWの電源に、貫通電流として大きな電流量の電流が流れる。このため、消費電力が増大する。 For this reason, a large amount of current flows as a through current from the power supply of the voltage VHI to the power supply of the voltage VLW via the transistors T51 and T52. For this reason, power consumption increases.

また、トランジスタT51,T52は、ゲート−ソース間への電圧印加により経時劣化して、閾値電圧が次第に高くなることが知られている。また、ドレイン−ソース間に過大な電流が流れると、上記の経時劣化が促進されることも知られている。 Further, it is known that the transistors T51 and T52 are deteriorated with time due to voltage application between the gate and the source, and the threshold voltage gradually increases. It is also known that when an excessive current flows between the drain and source, the deterioration with time is promoted.

ここで、トランジスタT51が経時劣化して閾値電圧が高くなると、非選択期間において本来HiレベルとなるべきノードBの電圧が低下して、このインバータINVに接続される回路の動作が不安定になってしまう。 Here, when the transistor T51 is deteriorated with time and the threshold voltage is increased, the voltage of the node B that should be originally at the Hi level in the non-selection period is decreased, and the operation of the circuit connected to the inverter INV becomes unstable. End up.

本発明は、このような従来の問題点に鑑みてなされたもので、消費電力を削減するとともに、動作を安定させることが可能なシフトレジスタ及び電子機器を提供することを目的とする。 The present invention has been made in view of such a conventional problem, and an object of the present invention is to provide a shift register and an electronic apparatus that can reduce power consumption and stabilize operation.

この目的を達成するため、本発明の第1の観点に係るシフトレジスタは、

縦続接続された複数のシフト回路からなる複数段のシフトレジスタであって、

前記各シフト回路は、

前段の出力信号が入力信号として供給される入力端子と、次段の出力信号がリセット信号として供給されるリセット端子と、第1のノードと、を有し、前記入力端子に前記入力信号が供給されたときに前記第1のノードの電位を前記入力信号のレベルに従った電位に設定する入力回路と、

第2のノードと、第1の端子と、第2の端子と、を有し、前記第1のノードの電位が供給され、前記第2のノードの電位を、前記第1のノードの電位を反転した電位とするインバータ回路と、

前記出力信号を出力する出力端子と、第1のクロック信号が供給される第3の端子と、を有し、前記第1のノードの電位と前記第2のノードの電位とが供給され、前記出力信号の電位を、前記第1のクロック信号に基づく電位とする出力回路と、を備え、

前記インバータ回路は、

前記第1の端子と前記第2のノードとの間に電流路が接続され、制御端子に前記第1のノードの電位が供給される第1のトランジスタと、電流路の一端が前記第2のノードに接続される第2のトランジスタと、電流路の一端が前記第2のトランジスタの前記電流路の他端に接続され、電流路の他端が前記第2の端子又は前記第3の端子のいずれか一方に接続される第3のトランジスタと、を備えたことを特徴とする。

In order to achieve this object, a shift register according to the first aspect of the present invention provides:

A multi-stage shift register comprising a plurality of cascaded shift circuits,

Each of the shift circuits is

An input terminal to which the output signal of the previous stage is supplied as an input signal, a reset terminal to which the output signal of the next stage is supplied as a reset signal, and a first node, and the input signal is supplied to the input terminal An input circuit for setting the potential of the first node to a potential according to the level of the input signal when

A second node; a first terminal; and a second terminal, to which the potential of the first node is supplied, and the potential of the second node is set to the potential of the first node. An inverter circuit having an inverted potential;

An output terminal for outputting the output signal; and a third terminal to which a first clock signal is supplied, and the potential of the first node and the potential of the second node are supplied, An output circuit for setting the potential of the output signal to a potential based on the first clock signal,

The inverter circuit is

A current path is connected between the first terminal and the second node, and a potential of the first node is supplied to a control terminal, and one end of the current path is connected to the second node A second transistor connected to the node, and one end of a current path connected to the other end of the current path of the second transistor, and the other end of the current path connected to the second terminal or the third terminal. And a third transistor connected to either one of the transistors.

前記第2のトランジスタは制御端子が該第2のトランジスタの電流路の他端に接続され、前記第3のトランジスタは制御端子が該第3のトランジスタの電流路の他端に接続されていてもよい。 The control terminal of the second transistor is connected to the other end of the current path of the second transistor, and the control terminal of the third transistor is connected to the other end of the current path of the third transistor. Good.

前記インバータ回路は、電流路の一端が前記第2のノードに接続され、前記電流路の他端が前記第2の端子に接続され、制御端子に前記リセット信号が供給されて、前記第2のノードの電位を制御する第4のトランジスタを備えたものであってもよい。 In the inverter circuit, one end of a current path is connected to the second node, the other end of the current path is connected to the second terminal, the reset signal is supplied to a control terminal, and the second circuit A fourth transistor for controlling the potential of the node may be provided.

前記第1の端子は一定の基準電位に設定され、前記第2の端子には前記基準電位より高い電位を有する一定の電圧が供給されていてもよい。 The first terminal may be set to a constant reference potential, and a constant voltage having a potential higher than the reference potential may be supplied to the second terminal.

前記第2の端子には、前記第1のクロック信号に対して逆相の第2のクロック信号が供給されていてもよい。 A second clock signal having a phase opposite to that of the first clock signal may be supplied to the second terminal.

本発明の第2の観点に係る電子機器は、

発光素子を備えて行列配置された複数の画素回路と、

上述のシフトレジスタを含み、当該シフトレジスタに含まれる各シフト回路の出力信号を、行を選択する行選択信号として各行毎に供給し、前記複数の画素回路を行毎に選択する行選択ドライバを備えたことを特徴とする。

An electronic device according to a second aspect of the present invention is:

A plurality of pixel circuits arranged in a matrix with light emitting elements;

A row selection driver that includes the shift register described above, supplies an output signal of each shift circuit included in the shift register as a row selection signal for selecting a row for each row, and selects the plurality of pixel circuits for each row. It is characterized by having.

本発明によれば、シフトレジスタにおいて、消費電力を削減するとともに、動作を安定させることができる。 According to the present invention, in the shift register, power consumption can be reduced and operation can be stabilized.

以下、本発明の実施形態に係る電子機器を、図面を参照して説明する。尚、本実施形態では、電子機器を、複数の画素を有し、各画素に発光素子として有機エレクトロルミネッセンス素子(以下、「有機EL素子」と略記する)を備えた表示装置として説明する。 Hereinafter, electronic devices according to embodiments of the present invention will be described with reference to the drawings. In the present embodiment, the electronic apparatus is described as a display device having a plurality of pixels and each pixel including an organic electroluminescence element (hereinafter abbreviated as “organic EL element”) as a light emitting element.

<第1の実施形態>

本発明の第1の実施形態に係る表示装置の構成を図1に示す。

本実施形態に係る表示装置1は、図1(a)に示すように、n行、m列の複数の画素回路11(i,j)(i=1〜m,j=1〜n,m,nは、それぞれ、自然数)と、ゲートドライバ(行選択ドライバ)12と、アノードドライバ13と、データドライバ14と、コントローラ15と、を備える。

<First Embodiment>

FIG. 1 shows the configuration of the display device according to the first embodiment of the present invention.

As shown in FIG. 1A, the

画素回路11(i,j)は、画像の各画素に対応するものであり、行列配置される。この画素回路11(i,j)は、図1(b)に示すように、有機EL素子OLED101と、トランジスタT1,T2と、キャパシタC1と、を有する。 The pixel circuit 11 (i, j) corresponds to each pixel of the image and is arranged in a matrix. As shown in FIG. 1B, the pixel circuit 11 (i, j) includes an organic EL element OLED 101, transistors T1 and T2, and a capacitor C1.

キャパシタC1は、トランジスタT2のゲート−ソース間に設けられたキャパシタである。 The capacitor C1 is a capacitor provided between the gate and source of the transistor T2.

有機EL素子OLED101は、画素電極(アノード電極)、単数或いは複数のキャリア輸送層からなる有機EL層、対向電極が積層された構造を有する表示素子であり、対向電極(カソード電極)にはカソード電位Vcathが印加されている。 The organic EL element OLED 101 is a display element having a structure in which a pixel electrode (anode electrode), an organic EL layer composed of one or a plurality of carrier transport layers, and a counter electrode are stacked, and the counter electrode (cathode electrode) has a cathode potential. Vcath is applied.

トランジスタT1,T2は、nチャンネル型のFET(Field Effect Transistor;電界効果トランジスタ)によって構成されたポリシリコンまたはアモルファスシリコンによって形成されたTFTであり、ドレイン、ソースとゲートを有し、ドレイン−ソース間には半導体層が設けられ、ドレイン−ソース間に所定のバイアス電圧が印加されるとともに、ゲートに閾値電圧より大きい電圧が印加されたとき、半導体層中にチャネルが形成され、このチャネルがドレイン−ソース間の電流路となる。 The transistors T1 and T2 are TFTs formed of polysilicon or amorphous silicon constituted by n-channel FETs (Field Effect Transistors), and have a drain, a source and a gate, and between the drain and the source. Is provided with a semiconductor layer, and when a predetermined bias voltage is applied between the drain and the source, and when a voltage higher than the threshold voltage is applied to the gate, a channel is formed in the semiconductor layer. This is the current path between the sources.

トランジスタT1は、キャパシタC1の一端に、画像データDataの階調を示す階調信号Vdataを印加するためのトランジスタである。各画素回路11(i,j)のトランジスタT1のソースは、トランジスタT2のゲート及びキャパシタC1の一端に接続される。 The transistor T1 is a transistor for applying a gradation signal Vdata indicating the gradation of the image data Data to one end of the capacitor C1. The source of the transistor T1 of each pixel circuit 11 (i, j) is connected to the gate of the transistor T2 and one end of the capacitor C1.

画素回路11(i,1),・・・,11(i,n)のトランジスタT1のドレインは、それぞれ、i列目のデータラインLdiに接続される。画素回路11(1,j),・・・,11(m,j)の各トランジスタT1のゲートは、それぞれ、第j行目のゲートラインLgjに接続される。 The drains of the transistors T1 of the pixel circuits 11 (i, 1),..., 11 (i, n) are connected to the i-th data line Ldi. The gates of the respective transistors T1 of the pixel circuits 11 (1, j),..., 11 (m, j) are connected to the gate line Lgj of the j-th row.

そして、それぞれ、ゲートラインLg1,・・・,LgnにHighレベルの信号が順次出力されると、画素回路11(1,j),・・・,11(m,j)の各トランジスタT1はオンし、データラインLd1,・・・,Ldmにそれぞれ入力された階調信号VdataをトランジスタT2のゲート及びキャパシタC1の一端に出力する。 When high level signals are sequentially output to the gate lines Lg1,..., Lgn, the respective transistors T1 of the pixel circuits 11 (1, j),. Then, the gradation signal Vdata input to each of the data lines Ld1,..., Ldm is output to the gate of the transistor T2 and one end of the capacitor C1.

トランジスタT2は、階調信号Vdataに基づいた電流量の電流を制御しつつ、有機EL素子OLED101に供給するトランジスタであり、そのゲートがトランジスタT1のソース及びキャパシタC1の一端に接続され、ドレインは、アノードラインLajに接続され、ソースがキャパシタC1の他端及び有機EL素子OLED101のアノードに接続されている。 The transistor T2 is a transistor that supplies current to the organic EL element OLED101 while controlling the amount of current based on the gradation signal Vdata. The gate of the transistor T2 is connected to the source of the transistor T1 and one end of the capacitor C1. Connected to the anode line Laj, the source is connected to the other end of the capacitor C1 and the anode of the organic EL element OLED101.

ゲートドライバ12は、行毎に画素回路11(i,j)を選択するためのドライバである。ゲートドライバ12は、コントローラ15から、電圧VHI,VLW(VHI>VLW)が印加され、スタート信号St、クロック信号CK1,CK2,end信号が供給されて動作を開始する。

The

ゲートドライバ12は、スタート信号Stが供給されて動作を開始し、クロック信号CK1,CK2に従って、出力信号OUT(1)〜(n)を、ゲートラインLg1〜Lgnに、順次、出力する。

The

ゲートドライバ12は、このようにして、画素回路11(1,1)〜11(m,1),・・・,11(1,n)〜11(m,n)を選択する。

In this way, the

このゲートドライバ12は、図2に示すようなシフトレジスタを有する。なお、ゲートドライバ12は、シフトレジスタの出力端にバッファが設けられていてもよい。このシフトレジスタは、コントローラ15から供給されたスタート信号Stによって動作を開始し、クロック信号CK1,CK2に同期させてスタート信号Stを転送し、出力信号OUT(1)〜OUT(n)を順次出力するものである。

The

シフトレジスタは、第1段乃至第n段のシフト回路21_1〜21_nを備え、シフト回路21_1〜21_nが直列に接続されている。 The shift register includes first to n-th shift circuits 21_1 to 21_n, and the shift circuits 21_1 to 21_n are connected in series.

シフト回路21_1〜21_nは、入力信号IN(スタート信号Stを含む)とクロック信号CK1又はCK2とが供給され、供給された入力信号INをクロック信号CK1又はCK2に従ってシフトし、シフトした信号を出力信号OUT(k)(k=1〜n)として出力するものである。 The shift circuits 21_1 to 21_n are supplied with the input signal IN (including the start signal St) and the clock signal CK1 or CK2, shift the supplied input signal IN according to the clock signal CK1 or CK2, and output the shifted signal as an output signal. It is output as OUT (k) (k = 1 to n).

シフト回路21_k(k=1〜n)は、図3に示すように、入力端子Pinと、出力端子Poutと、リセット端子Prstと、電圧端子として機能する第1の端子P1と、電圧端子として機能する第2の端子P2と、クロック端子として機能する第3の端子P3と、を有している。 As shown in FIG. 3, the shift circuit 21_k (k = 1 to n) functions as an input terminal Pin, an output terminal Pout, a reset terminal Prest, a first terminal P1 that functions as a voltage terminal, and a voltage terminal. And a third terminal P3 functioning as a clock terminal.

入力端子Pinは、入力信号IN(k)が供給される端子である。シフト回路21_1の入力端子Pinには、コントローラ15からスタート信号Stが入力信号IN(1)として供給される。

The input terminal Pin is a terminal to which an input signal IN (k) is supplied. The start signal St is supplied as the input signal IN (1) from the

出力端子Poutは、出力信号OUT(k)を出力する端子であり、ゲートラインLgkに接続されている。シフト回路21_2〜21_nの入力端子Pinは、それぞれ、前段のシフト回路21_1〜21_(n−1)の出力端子Poutに接続される。 The output terminal Pout is a terminal that outputs an output signal OUT (k), and is connected to the gate line Lgk. The input terminals Pin of the shift circuits 21_2 to 21_n are connected to the output terminals Pout of the preceding shift circuits 21_1 to 21_ (n−1), respectively.

リセット端子Prstは、リセット信号RST(k)が供給される端子である。シフト回路21_1〜21_(n−1)のリセット端子Prstは、それぞれ、次段のシフト回路21_2〜21_nの出力端子Poutに接続され、出力信号OUT(2)〜OUT(n)がリセット信号RST(1)〜RST(n−1)として供給される。また、シフト回路21_nには、コントローラ15からend信号が供給される。

The reset terminal Prst is a terminal to which a reset signal RST (k) is supplied. The reset terminals Prst of the shift circuits 21_1 to 21_ (n-1) are respectively connected to the output terminals Pout of the shift circuits 21_2 to 21_n of the next stage, and the output signals OUT (2) to OUT (n) are reset signals RST ( 1) to RST (n-1). Further, the end signal is supplied from the

第3の端子P3は、クロック信号(第1のクロック信号)CK1又はCK2が供給される端子であり、奇数段であるシフト回路21_kの第3の端子P3には、コントローラ15から、クロック信号CK1が供給される。

The third terminal P3 is a terminal to which a clock signal (first clock signal) CK1 or CK2 is supplied. The third terminal P3 of the odd-numbered shift circuit 21_k is supplied from the

また、偶数段であるシフト回路21_(k+1)の第3のクロック端子P3には、コントローラ15から、クロック信号CK2が供給される。

The clock signal CK2 is supplied from the

第2の端子P2は、電圧VHIが印加される端子であり、第1の端子P1は、基準電圧としての電圧VLWが印加される端子である。 The second terminal P2 is a terminal to which a voltage VHI is applied, and the first terminal P1 is a terminal to which a voltage VLW as a reference voltage is applied.

このシフト回路21_kは、トランジスタT11〜T18を備えている。トランジスタT11〜T18は、nチャンネル型のFETによって構成されたトランジスタである。 The shift circuit 21_k includes transistors T11 to T18. The transistors T11 to T18 are transistors configured by n-channel FETs.

このトランジスタT11〜T18は、単結晶シリコントランジスタでもよく、また画素回路11(i,j)と一体に構成されるためにポリシリコンTFTやアモルファスシリコンTFT(a−TFT)によって構成されてもよい。 The transistors T11 to T18 may be single crystal silicon transistors, or may be configured by polysilicon TFTs or amorphous silicon TFTs (a-TFTs) in order to be integrated with the pixel circuit 11 (i, j).

トランジスタT11〜T18は、ドレイン、ソースとゲートを有し、ドレイン−ソース間には半導体層が設けられ、ドレイン−ソース間に所定のバイアス電圧が印加されるとともに、ゲートに閾値電圧より大きい電圧が印加されたとき、半導体層中にチャネルが形成され、このチャネルがドレイン−ソース間の電流路となる。 The transistors T11 to T18 have a drain, a source, and a gate, a semiconductor layer is provided between the drain and the source, a predetermined bias voltage is applied between the drain and the source, and a voltage larger than the threshold voltage is applied to the gate. When applied, a channel is formed in the semiconductor layer, and this channel becomes a current path between the drain and the source.

トランジスタT11は、入力端子Pinに供給された入力信号IN(k)の信号レベルに従って、ノードAの電位Vaを決定するためのトランジスタである。このトランジスタT11のゲートとドレインとは、入力端子Pinに接続される。ノードAは、信号出力端としてのトランジスタT11のソースに接続された接続点である。 The transistor T11 is a transistor for determining the potential Va of the node A in accordance with the signal level of the input signal IN (k) supplied to the input terminal Pin. The gate and drain of the transistor T11 are connected to the input terminal Pin. The node A is a connection point connected to the source of the transistor T11 as a signal output terminal.

トランジスタT12は、リセット端子Prstに供給されたHighレベルのリセット信号RST(k)でシフト回路21_kをリセットするためのトランジスタである。 The transistor T12 is a transistor for resetting the shift circuit 21_k with the high level reset signal RST (k) supplied to the reset terminal Prst.

このトランジスタT12のゲートは、リセット端子Prstに接続され、ドレインは、トランジスタT11のソースとノードAとに接続され、ソースは、第1の端子P1に接続される。トランジスタT11、T12は入力回路に相当する。 The gate of the transistor T12 is connected to the reset terminal Prst, the drain is connected to the source of the transistor T11 and the node A, and the source is connected to the first terminal P1. Transistors T11 and T12 correspond to an input circuit.

トランジスタT13〜T16は、ノードAの電位を反転するインバータINVを構成するトランジスタである。インバータINVはインバータ回路に相当する。 The transistors T13 to T16 are transistors that constitute an inverter INV that inverts the potential of the node A. The inverter INV corresponds to an inverter circuit.

トランジスタT13は、ノードAの電位Vaに従って、ノードBの電位Vbをコントロールするためのトランジスタである。このトランジスタT13のゲートは、ノードAに接続され、電流上流端としてのドレインは、ノードBに接続され、電流下流端としてのソースは第1の端子P1に接続される。ノードBはトランジスタT15のソースとトランジスタT13のドレインとの接続点である。 The transistor T13 is a transistor for controlling the potential Vb of the node B in accordance with the potential Va of the node A. The gate of the transistor T13 is connected to the node A, the drain as the current upstream end is connected to the node B, and the source as the current downstream end is connected to the first terminal P1. Node B is a connection point between the source of the transistor T15 and the drain of the transistor T13.

トランジスタT14,T15は、ダイオード接続されて抵抗として機能する半導体素子であり、トランジスタT14のドレインとゲートとは、第2の端子P2に接続される。トランジスタT14は、電圧VHIが印加されて、電流量を制限しつつトランジスタT15、T13に電流を供給する。 The transistors T14 and T15 are semiconductor elements that are diode-connected and function as resistors, and the drain and gate of the transistor T14 are connected to the second terminal P2. The transistor T14 is supplied with a voltage VHI and supplies current to the transistors T15 and T13 while limiting the amount of current.

またトランジスタT15のゲートとドレインとは、トランジスタT14のソースに接続され、ソースはノードBに接続される。トランジスタT15は、トランジスタT14と直列に接続されて、電流下流端としてのソースがノードBに接続されて、第2の端子P2とノードB間の電圧を分圧するトランジスタである。 The gate and drain of the transistor T15 are connected to the source of the transistor T14, and the source is connected to the node B. The transistor T15 is a transistor that is connected in series with the transistor T14, the source serving as the current downstream end is connected to the node B, and divides the voltage between the second terminal P2 and the node B.

このように、電圧VHIが印加される第2の端子P2とノードB間との間にダイオード接続されたトランジスタT14、T15が直列接続されるため、各トランジスタT14、15のバイアス電圧が分圧(ストレス電圧が分散)される。また、これにより、第2の端子P2とノードB間の抵抗値が従来の構成に比べて増加して、貫通電流の電流値が従来の構成に比べて減少する。 Thus, since the diode-connected transistors T14 and T15 are connected in series between the second terminal P2 to which the voltage VHI is applied and the node B, the bias voltage of each of the transistors T14 and 15 is divided ( Stress voltage is distributed). As a result, the resistance value between the second terminal P2 and the node B increases compared to the conventional configuration, and the current value of the through current decreases compared to the conventional configuration.

トランジスタT16は、ノードBの電位Vbの立ち上がり速度の低下を抑制するためのトランジスタである。トランジスタT16がトランジスタT14,T15と並列に接続されるように、トランジスタT16のドレインはトランジスタT14のドレイン(及びゲート)に接続されるとともに第2の端子P2に接続され、ソースはノードBに接続される。 The transistor T16 is a transistor for suppressing a decrease in the rising speed of the potential Vb of the node B. The drain of the transistor T16 is connected to the drain (and gate) of the transistor T14 and to the second terminal P2, and the source is connected to the node B so that the transistor T16 is connected in parallel with the transistors T14 and T15. The

また、トランジスタT16のゲートは、リセット端子Prstに接続され、トランジスタT16は、リセット信号RST(k)の信号レベルに従って、ノードBの電位をコントロールする。 The gate of the transistor T16 is connected to the reset terminal Prst, and the transistor T16 controls the potential of the node B in accordance with the signal level of the reset signal RST (k).

尚、このトランジスタT16は、Highレベルのリセット信号RST(k)で動作するため、リセット信号RST(k)の立ち上がりの際に、過渡的にしか電圧ストレス(ゲート−ソース間電圧)を受けないため、比較的劣化が少ない素子である。 Since the transistor T16 operates with a high level reset signal RST (k), the transistor T16 receives voltage stress (gate-source voltage) only transiently when the reset signal RST (k) rises. It is an element with relatively little deterioration.

このトランジスタT13〜T16によって構成されるインバータINVにより、ノードAの電位Va、ノードBの電位Vbは相補的にHigh(オンレベル)、Low(オフレベル)にスイッチされ、一方がHighであれば、他方がLowとなる。 By the inverter INV constituted by the transistors T13 to T16, the potential Va of the node A and the potential Vb of the node B are complementarily switched to High (on level) and Low (off level), and if one of them is High, The other becomes Low.

尚、トランジスタT13〜T16のトランジスタサイズは、チャネル長が互いに同じ値である場合、チャネル幅も互いに同じ値に設定してよい。これに対し、図10に示す従来のインバータINVでは、電圧VHIと電圧VLWとの間に接続されているトランジスタは、トランジスタT51,T52の2つであり、ノードBの電圧を低下させるため、トランジスタT51,T52のトランジスタサイズを、チャネル長を同じとして、チャネル幅を、例えば1:3程度にする必要があった。 The transistor sizes of the transistors T13 to T16 may be set to the same value when the channel length is the same value. On the other hand, in the conventional inverter INV shown in FIG. 10, there are two transistors T51 and T52 connected between the voltage VHI and the voltage VLW. The transistor sizes of T51 and T52 have to be the same channel length, and the channel width needs to be about 1: 3, for example.

しかし、図3に示すインバータINVでは、トランジスタT15が介挿されているため、トランジスタT13のトランジスタサイズをT14、T15と同程度に小さくしてもノードBの電位Vbを充分に低下させることができる。 However, in the inverter INV shown in FIG. 3, since the transistor T15 is interposed, even if the transistor size of the transistor T13 is made as small as T14 and T15, the potential Vb of the node B can be sufficiently reduced. .

また、ダイオード接続されたトランジスタT51を備える従来の構成に比べて、T16があることによってノードBの電圧の立ち上がりが速められているため、トランジスタT14、T15のトランジスタサイズをT51のトランジスタサイズより小さくすることができる。以上により、従来の構成に対してトランジスタが2つ増加されているものの、各トランジスタの大きさを比較的小さくすることが出来て、回路面積の増加を抑えることができる。 Further, since the rise of the voltage at the node B is accelerated by the presence of T16 as compared with the conventional configuration including the diode-connected transistor T51, the transistor sizes of the transistors T14 and T15 are made smaller than the transistor size of the T51. be able to. As described above, although two transistors are added to the conventional configuration, the size of each transistor can be made relatively small, and an increase in circuit area can be suppressed.

トランジスタT17は、クロック信号CK1がドレインに供給され、ノードAの電位Vaに従ってオン、オフし、オンしたときに、クロック信号CK1に同期して、シフト信号としての出力信号OUT(k)として出力するトランジスタである。 The transistor T17 is supplied with the clock signal CK1 to the drain and is turned on / off according to the potential Va of the node A. When the transistor T17 is turned on, the transistor T17 outputs the output signal OUT (k) as the shift signal in synchronization with the clock signal CK1. It is a transistor.

このトランジスタT17のゲートは、ノードAに接続され、ドレインは、第3の端子P3に接続され、ソースは出力端子Poutに接続される。このトランジスタT17のゲート−ソース間には、ブートストラップ効果をもたらすためのキャパシタCx1が接続される。 The transistor T17 has a gate connected to the node A, a drain connected to the third terminal P3, and a source connected to the output terminal Pout. A capacitor Cx1 for providing a bootstrap effect is connected between the gate and source of the transistor T17.

トランジスタT18は、ノードBの電位Vbに従ってオン、オフし、第k行の画素回路11(i,k)の非選択期間にオンして出力信号OUT(k)を基準電圧としての電圧VLWに固定して出力信号OUT(k)を安定させるためのトランジスタである。 The transistor T18 is turned on / off according to the potential Vb of the node B, and is turned on during a non-selection period of the pixel circuit 11 (i, k) in the k-th row, and the output signal OUT (k) is fixed to the voltage VLW as a reference voltage. This is a transistor for stabilizing the output signal OUT (k).

トランジスタT18のゲートは、ノードBに接続され、ドレインは、トランジスタT17のソースと出力端子Poutとに接続され、ソースは、第1の端子P1に接続される。トランジスタT17、T18は出力回路に相当する。 The gate of the transistor T18 is connected to the node B, the drain is connected to the source of the transistor T17 and the output terminal Pout, and the source is connected to the first terminal P1. Transistors T17 and T18 correspond to an output circuit.

図1(a),(b)に戻り、アノードドライバ13は、アノードラインLa(1)〜La(n)に、それぞれ、電圧VL又はVHの信号Vsource(1)〜Vsource(n)を出力するドライバである。アノードドライバ13は、それぞれ、アノードラインLaj(j=1〜n)を介して、各画素回路11(i,j)のトランジスタT3のドレインに接続される。

1A and 1B, the

アノードドライバ13は、コントローラ15から供給されたスタート信号Stにより動作を開始し、コントローラ15から供給されたクロック信号CK1に従って動作する。

The

そして、アノードドライバ13は、電圧VL又はVHの電圧信号Vsource(1)〜Vsource(n)を出力する。電圧VLは、書き込み処理時等において、各画素回路11(i,j)の有機EL素子OLED101を非発光状態にするための電圧である。

Then, the

本実施形態では、有機EL素子OLED101のカソード電圧Vcathが0Vに設定され、電圧VLは、0V、もしくは0Vより低い電位に設定される。また、電圧VHは、各画素回路11(i,j)の有機EL素子OLED101を発光状態にするための電圧であり、例えば、+15Vに設定される。

In the present embodiment, the cathode voltage Vcath of the organic EL element OLED101 is set to 0V, and the voltage VL is set to 0V or a potential lower than 0V. The voltage VH is a voltage for setting the organic

データドライバ14は、画素回路11(i,j)の各キャパシタC1に供給された画像データDataに基づく表示信号の階調信号Vdataを書き込むドライバである。

The

データドライバ14は、コントローラ15から画像データDataが供給され、この画像データDataに基づいて、行毎の階調信号Vdataを生成する。

The

データドライバ14は、生成した階調信号Vdataを、それぞれ、データラインLd1〜Ldmを介して、ゲートドライバ12が選択した第j行の画素回路11(1,j)〜11(m,j)に供給する。

The

コントローラ15は、ゲートドライバ12、データドライバ14を制御するものであり、CPU(Central Processing Unit)、ROM(Read Only Memory),RAM(Random Access Memory)、等を備える(いずれも図示せず)。

The

コントローラ15は、シフト回路21_1〜21_nのうち奇数段にクロック信号CK1を出力し、偶数段にクロック信号CK2を出力した状態で、動作を開始させるスタート信号Stをゲートドライバ12の初段のシフト回路21_1に供給する。コントローラ15は、このようにして、ゲートドライバ12に動作を開始させる。

The

また、コントローラ15は、ゲートドライバ12に、最終段のシフト回路21_nのリセット信号RST(n)としてend信号を供給する。

Further, the

コントローラ15は、データドライバ14にスタート信号St及び画像データData、クロック信号CK1等を供給する。

The

次に本実施形態に係る表示装置1の動作を説明する。図4は、ゲートドライバ12におけるシフト回路21_k及びシフトレジスタの動作を説明するためのタイミングチャートである。なお、Va、Vb、Vcは初段のシフト回路21_1のノードA、B、Cの電位を示す。

Next, the operation of the

図4に示すように、コントローラ15は、位相が180°異なるクロック信号CK1,CK2とHighレベルのスタート信号Stとをゲートドライバ12に供給する。

As shown in FIG. 4, the

クロック信号CK1がLowレベルになる時刻t10において、このHighレベルのスタート信号Stは、第1段のシフト回路21_1の入力端子Pinに、入力信号IN(1)として供給される。 At time t10 when the clock signal CK1 becomes low level, the high-level start signal St is supplied as the input signal IN (1) to the input terminal Pin of the first-stage shift circuit 21_1.

このHighレベルのスタート信号Stが供給される期間を入力期間Tinとして、シフト回路21_1のトランジスタT11は、この入力期間Tinにおいて、オンする。 The period during which the high-level start signal St is supplied is defined as the input period Tin, and the transistor T11 of the shift circuit 21_1 is turned on in the input period Tin.

トランジスタT11がオンすると、ノードAの電位Vaは、Highレベルとなり、トランジスタT13も、ゲートにHighレベルの信号が供給されてオンする。 When the transistor T11 is turned on, the potential Va of the node A becomes a high level, and the transistor T13 is also turned on when a high level signal is supplied to the gate.

トランジスタT13がオンすると、トランジスタT14,T15は、ダイオード接続されているために、電流が、電圧VHIのラインから、第2の端子P2、トランジスタT14,T15,T13の各ドレイン−ソース、第1の端子P1を経由して、電圧VLWのラインへと流れる。 When the transistor T13 is turned on, since the transistors T14 and T15 are diode-connected, the current flows from the voltage VHI line to the second terminal P2, the drain-sources of the transistors T14, T15, and T13, the first It flows to the line of the voltage VLW via the terminal P1.

電流がこのように流れて、ノードBの電位Vbは、図4に示すように、入力期間TinにおいてLowレベルになり、トランジスタT18はオフする。 As the current flows in this way, the potential Vb of the node B becomes the low level in the input period Tin as shown in FIG. 4, and the transistor T18 is turned off.

しかし、トランジスタT14,T15は、抵抗素子として機能し、流れる電流の電流量は、トランジスタT14,T15によって制限され、トランジスタT13の発熱量も低減される。また、トランジスタT14、T15のドレイン−ソース間に印加される電圧は、(VHI−VLW)/3となり、従来と比較して減少する。 However, the transistors T14 and T15 function as resistance elements, and the amount of flowing current is limited by the transistors T14 and T15, and the amount of heat generated by the transistor T13 is also reduced. Further, the voltage applied between the drain and source of the transistors T14 and T15 is (VHI−VLW) / 3, which is reduced as compared with the conventional case.

図4に示すように、入力期間Tin経過後、クロック信号CK1がHighレベルになる出力期間Toutにおいて、入力信号IN(1)がLowレベルとなり、トランジスタT11はオフする。 As shown in FIG. 4, after the elapse of the input period Tin, in the output period Tout in which the clock signal CK1 becomes High level, the input signal IN (1) becomes Low level and the transistor T11 is turned off.

ノードAの電位Vaは、トランジスタT11がオフしても、トランジスタT17,T18がオフしているため、Highレベルに保持されている。 Even if the transistor T11 is turned off, the potential Va of the node A is held at a high level because the transistors T17 and T18 are turned off.

この出力期間Toutにおいて、クロック信号CK1がHighレベルになると、キャパシタCx1のブートストラップ効果により、ノードAの電位Vaは、さらに上昇し、トランジスタT17は、確実にオンする。 In this output period Tout, when the clock signal CK1 becomes High level, the potential Va of the node A further rises due to the bootstrap effect of the capacitor Cx1, and the transistor T17 is reliably turned on.

トランジスタT17がオンすると、シフト回路21_1は、出力端子Poutから、Highレベルの出力信号OUT(1)を出力する。 When the transistor T17 is turned on, the shift circuit 21_1 outputs a high level output signal OUT (1) from the output terminal Pout.

このHighレベルの出力信号OUT(1)は、ゲートラインLg1に出力されるとともに、シフト回路21_2に、入力信号IN(2)として供給される。 The high level output signal OUT (1) is output to the gate line Lg1 and supplied to the shift circuit 21_2 as the input signal IN (2).

シフト回路21_2は、この入力信号IN(2)をクロック信号CK2に同期してシフトし、Highレベルの出力信号OUT(2)を出力する。 The shift circuit 21_2 shifts the input signal IN (2) in synchronization with the clock signal CK2, and outputs a high-level output signal OUT (2).

このHighレベルの出力信号OUT(2)は、Highレベルのリセット信号RST(1)として、シフト回路21_1のリセット端子Prstに供給される。 The high level output signal OUT (2) is supplied to the reset terminal Prst of the shift circuit 21_1 as the high level reset signal RST (1).

このHighレベルのリセット信号RST(1)が供給されると、トランジスタT12がオンする。トランジスタ12がオンすると、ノードAの電位VaはLowレベルに立ち下がる。

When this high level reset signal RST (1) is supplied, the transistor T12 is turned on. When the

ノードAの電位VaがLowレベルに立ち下がると、トランジスタT13がオフし、ノードBの電位VbはHighレベルとなる。 When the potential Va at the node A falls to the low level, the transistor T13 is turned off, and the potential Vb at the node B becomes the high level.

また、Highレベルのリセット信号RST(1)が供給されると、トランジスタT16もオンする。 When the high level reset signal RST (1) is supplied, the transistor T16 is also turned on.

第2の端子P2と第1の端子P1との間には、トランジスタT15が介挿されているため、トランジスタT16がなければ、トランジスタT15の寄生容量により、ノードBの電位Vbの立ち上がり速度は、従来と比較して、遅くなる。 Since the transistor T15 is interposed between the second terminal P2 and the first terminal P1, if the transistor T16 is not provided, the rising speed of the potential Vb of the node B is caused by the parasitic capacitance of the transistor T15. Compared to the conventional system, it becomes slower.

しかし、シフト回路21_1には、トランジスタT16が備えられ、トランジスタT16がオンすることにより、第2の端子P2とノードBとの間が短絡され、電位Vbの立ち上がり速度の遅れは解消され、ノードBの電位Vbは、素早くHighレベルとなる。 However, the shift circuit 21_1 includes the transistor T16. When the transistor T16 is turned on, the second terminal P2 and the node B are short-circuited, and the delay in the rising speed of the potential Vb is eliminated. The potential Vb immediately becomes High level.

ノードBの電位VbがHighレベルになることにより、トランジスタT18はオンし、出力信号OUT(1)は、Lowレベルに立ち下がる。 When the potential Vb of the node B becomes the high level, the transistor T18 is turned on, and the output signal OUT (1) falls to the low level.

同様に、シフト回路21_k(k=2〜n)は、それぞれ、クロック信号CK1,CK2に同期させて、シフト回路21_(k−1)から出力された出力信号OUT(k−1)を入力信号IN(k)として、この入力信号IN(k)をシフトする。そして、シフト回路21_kは、シフトした信号を出力信号OUT(k)として出力する。 Similarly, the shift circuit 21_k (k = 2 to n) receives the output signal OUT (k−1) output from the shift circuit 21_ (k−1) in synchronization with the clock signals CK1 and CK2, respectively. This input signal IN (k) is shifted as IN (k). Then, the shift circuit 21_k outputs the shifted signal as the output signal OUT (k).

ゲートドライバ12は、シフト回路21_1のHighレベルの出力信号OUT(1)をゲートラインLg1に出力する。画素回路11(1,1)〜11(m,1)の各トランジスタT1は、このHighレベルの出力信号OUT(1)によりオンする。

The

データドライバ14は、この期間において、データラインLd1〜Ldmを介して、ゲートドライバ12が選択した画素回路11(1,1)〜11(m,1)に階調信号Vdataを供給する。

During this period, the

画素回路11(1,1)〜11(m,1)の各キャパシタC1には、各トランジスタT1を介して、この階調信号Vdataが書き込まれる。 This gradation signal Vdata is written to each capacitor C1 of the pixel circuits 11 (1,1) to 11 (m, 1) via each transistor T1.

同様にして、ゲートドライバ12は、シフト回路21_2,・・・,21_nのHighレベルの出力信号OUT(2)〜OUT(n)を、順次、ゲートラインLg2,・・・,Lgnに出力する。

Similarly, the

ゲートラインLg2,・・・,Lgnに、順次、Highレベルの出力信号OUT(1)が出力されると、画素回路11(1,2)〜11(m,2),・・・,11(1,n)〜11(m,n)が選択される。 When the high level output signal OUT (1) is sequentially output to the gate lines Lg2,..., Lgn, the pixel circuits 11 (1, 2) to 11 (m, 2),. 1, n) to 11 (m, n) are selected.

データドライバ14は、供給された画像データに基づく階調信号Vdataを、それぞれ、データラインLd1〜Ldmに印加し、選択された画素回路11(1,2)〜11(m,2),・・・,11(1,n)〜11(m,n)の各キャパシタC1に階調信号Vdataを書き込む。

The

このようにして書き込み動作が完了すると、コントローラ15は、発光動作を制御する。

When the writing operation is completed in this way, the

アノードドライバ13は、電圧VH(=+15V)の信号Vsource(1)〜Vsource(n)を、アノードラインLa(1)〜La(n)に出力する。

The

アノードラインLa(1)〜La(n)の電圧がVHになると、各画素回路11(i,j)のトランジスタT2は、各キャパシタC1が保持した電圧をゲート電圧Vgsとして、このゲート電圧Vgsに対応する電流を有機EL素子OLED101に供給する。 When the voltage of the anode lines La (1) to La (n) becomes VH, the transistor T2 of each pixel circuit 11 (i, j) uses the voltage held by each capacitor C1 as the gate voltage Vgs, and the gate voltage Vgs. A corresponding current is supplied to the organic EL element OLED101.

そして、各有機EL素子OLED101は、この電流が流れることにより、この電流の電流値に対応する輝度で発光する。 And each organic EL element OLED101 light-emits with the brightness | luminance corresponding to the electric current value of this electric current, when this electric current flows.

以上説明したように、本実施形態によれば、インバータINVのトランジスタT14とノードBとの間にトランジスタT15が接続され、電圧VHIと電圧VLWとの間のバイアス電圧を分圧するようにした。 As described above, according to the present embodiment, the transistor T15 is connected between the transistor T14 of the inverter INV and the node B, and the bias voltage between the voltage VHI and the voltage VLW is divided.

従って、各トランジスタT13〜T15のバイアス電圧は分散されるため、入力期間Tinと出力期間Toutにおいて、トランジスタT14、T15の各々に印加されるバイアス電圧を従来の構成の場合に対してほぼ半減させることができ、電流を大幅に低減することができる。 Accordingly, since the bias voltage of each of the transistors T13 to T15 is dispersed, the bias voltage applied to each of the transistors T14 and T15 in the input period Tin and the output period Tout is almost halved compared to the conventional configuration. And the current can be greatly reduced.

また、このため、トランジスタT14、T15の劣化による閾値Vthシフトの発生を抑制することができる。 For this reason, occurrence of a threshold Vth shift due to deterioration of the transistors T14 and T15 can be suppressed.

また、トランジスタT14,T15と並列に、トランジスタT16が接続されることにより、トランジスタT15を介挿したことによるノードBの電位Vbの立ち上がり速度の遅れを防止することができる。 Further, by connecting the transistor T16 in parallel with the transistors T14 and T15, a delay in the rising speed of the potential Vb of the node B due to the insertion of the transistor T15 can be prevented.

<第2の実施形態>

次に、本発明の第2の実施形態に係るシフト回路の構成を図5に示す。

上記第1の実施形態では、シフト回路21_kにおいて、トランジスタT14のドレインに接続される第2の端子P2に一定の電圧値を有する電圧VHIを印加するようにした。しかし、インバータINVのトランジスタT14のドレインには、図4に示した出力期間Toutには電圧VHIが印加されていなくても、シフト回路21_kは実質的に同様に動作する。

<Second Embodiment>

Next, the configuration of the shift circuit according to the second embodiment of the present invention is shown in FIG.

In the first embodiment, in the shift circuit 21_k, the voltage VHI having a constant voltage value is applied to the second terminal P2 connected to the drain of the transistor T14. However, even if the voltage VHI is not applied to the drain of the transistor T14 of the inverter INV during the output period Tout shown in FIG. 4, the shift circuit 21_k operates substantially in the same manner.

そこで、本第2の実施形態は、図5に示すように、第2の端子P2に、電圧VHIに代えて、第3の端子P3に印加されるクロック信号(正相のクロック信号(第1のクロック信号)CK+とする)に対して逆相のクロック信号(第2のクロック信号)CK−を供給するようにしたものである。 Therefore, in the second embodiment, as shown in FIG. 5, a clock signal (positive phase clock signal (first phase) applied to the second terminal P2 instead of the voltage VHI is applied to the third terminal P3. The clock signal (second clock signal) CK− of the opposite phase is supplied to the clock signal CK +).

この場合、ゲートドライバ12は、図6に示すように、すべてのシフト回路21_1〜21_nに、クロック信号CK1,CK2を供給する。奇数段のシフト回路21_kには、クロック信号CK1,CK2が、それぞれ、正相及び逆相のクロック信号CK+,CK−として供給され、偶数段のシフト回路21_kには、クロック信号CK1,CK2が、それぞれ、逆相及び正相のクロック信号CK−,CK+として供給される。

In this case, the

ここで、本実施形態におけるシフト回路21_k及びシフトレジスタの動作は、図7に示すように、ノードCの電位であるVc以外は図4に示した動作と同じとなる。 Here, the operations of the shift circuit 21_k and the shift register in the present embodiment are the same as those shown in FIG. 4 except for Vc which is the potential of the node C, as shown in FIG.

ノードCの電位Vcは、第2の端子P2に逆相のクロック信号CK−が印加されるために、初段のシフト回路21_1においては、クロック信号CK2に対応して変化する。 Since the clock signal CK− having the opposite phase is applied to the second terminal P2, the potential Vc of the node C changes in response to the clock signal CK2 in the first-stage shift circuit 21_1.

このようにすることにより、電圧VHIを使用しないため、電圧VHIのラインの配線が不要となり、回路面積を縮小することができる。また、トランジスタT14、T15に印加されるバイアス電圧を低減することができるとともに、トランジスタT14、T15にバイアス電圧が印加される期間を入力期間Tinのみとし、出力期間ToutにはトランジスタT14、T15にバイアス電圧が印加されないため、バイアス電圧が印加される期間を短縮して、トランジスタT14、T15の劣化を更に抑制することができる。 By doing so, since the voltage VHI is not used, the wiring of the voltage VHI line becomes unnecessary, and the circuit area can be reduced. Further, the bias voltage applied to the transistors T14 and T15 can be reduced, the period during which the bias voltage is applied to the transistors T14 and T15 is limited to the input period Tin, and the transistors T14 and T15 are biased during the output period Tout. Since no voltage is applied, the period during which the bias voltage is applied can be shortened, and deterioration of the transistors T14 and T15 can be further suppressed.

さらに、第2の端子P2に逆相のクロック信号CK−を供給するようにしたことにより、出力期間Toutにおいて、インバータINVに電流が供給されなくなるため、消費電流を低減させることができる。 Further, by supplying the opposite phase clock signal CK− to the second terminal P2, no current is supplied to the inverter INV in the output period Tout, so that the current consumption can be reduced.

次に、本実施形態の変形例について説明する。上記図5に示した構成においては、第2の端子P2にトランジスタT16のドレインとトランジスタT14のドレインとが接続されていたが、図8に示すように、第2の端子P2にはトランジスタT16のドレインのみを接続し、第3の端子P3にトランジスタT13のドレインとトランジスタT17のドレインとを接続するようにしてもよい。 Next, a modification of this embodiment will be described. In the configuration shown in FIG. 5, the drain of the transistor T16 and the drain of the transistor T14 are connected to the second terminal P2. However, as shown in FIG. 8, the second terminal P2 has the drain of the transistor T16. Only the drain may be connected, and the drain of the transistor T13 and the drain of the transistor T17 may be connected to the third terminal P3.

ここで、本実施形態におけるシフト回路21_k及びシフトレジスタの動作も、図9に示すように、ノードB、Cの電位であるVb、Vc以外は図4に示した動作と同じとなる。 Here, the operations of the shift circuit 21_k and the shift register in the present embodiment are the same as those shown in FIG. 4 except for Vb and Vc which are the potentials of the nodes B and C, as shown in FIG.

スタート信号Stが供給されたときトランジスタT16はオフ状態であり、トランジスタT13、T14もオフ状態であるため、ノードBの電位Vbは、入力期間Tinに電圧VLW近いLowレベルになり、出力期間Toutにおいて、第3の端子P3にHighレベルのクロック信号が印加されて、そのLowレベルが上昇する。そして、ノードCの電位Vcは、このノードBの電位Vbの変化に応じた変化をする。 When the start signal St is supplied, the transistor T16 is in an off state, and the transistors T13 and T14 are also in an off state. Therefore, the potential Vb of the node B becomes a low level near the voltage VLW in the input period Tin, and in the output period Tout. A high level clock signal is applied to the third terminal P3, and its Low level rises. The potential Vc of the node C changes according to the change of the potential Vb of the node B.

この場合においても、電圧VHIを使用しないため、電圧VHIのラインの配線が不要となり、回路面積を縮小することができる。また、トランジスタT14、T15に印加されるバイアス電圧を低減することができるとともに、トランジスタT14、T15にバイアス電圧が印加される期間を出力期間Toutのみとし、入力期間TinにはトランジスタT14、T15にバイアス電圧が印加されないため、バイアス電圧が印加される期間を短縮して、トランジスタT14、T15の劣化を更に抑制することができる。 Also in this case, since the voltage VHI is not used, the wiring of the voltage VHI line becomes unnecessary, and the circuit area can be reduced. Further, the bias voltage applied to the transistors T14 and T15 can be reduced, and the period during which the bias voltage is applied to the transistors T14 and T15 is limited to the output period Tout, and the transistors T14 and T15 are biased during the input period Tin. Since no voltage is applied, the period during which the bias voltage is applied can be shortened, and deterioration of the transistors T14 and T15 can be further suppressed.

なお、上記実施形態では、電子機器を、有機EL素子を備えた表示装置として説明した、しかし、電子機器は、このものに限られるものではなく、発光素子を備えたものであれば、本実施形態に限定されるものではない。また、電子機器は、例えば、液晶素子を備えた液晶表示装置であってもよい。 In the above-described embodiment, the electronic device is described as a display device including an organic EL element. However, the electronic device is not limited to this, and the present embodiment can be used as long as the electronic device includes a light-emitting element. The form is not limited. The electronic device may be a liquid crystal display device including a liquid crystal element, for example.

1・・・表示装置、11・・・画素回路、12・・・ゲートドライバ、13・・・アノードドライバ、14・・・データドライバ、15・・・コントローラ、21_k(k;1〜n)・・・シフト回路、101・・・有機EL素子OLED、T1,T2,T11〜T18・・・トランジスタ、C1・・・キャパシタ、INV・・・インバータ

DESCRIPTION OF

Claims (6)

前記各シフト回路は、

前段の出力信号が入力信号として供給される入力端子と、次段の出力信号がリセット信号として供給されるリセット端子と、第1のノードと、を有し、前記入力端子に前記入力信号が供給されたときに前記第1のノードの電位を前記入力信号のレベルに従った電位に設定する入力回路と、

第2のノードと、第1の端子と、第2の端子と、を有し、前記第1のノードの電位が供給され、前記第2のノードの電位を、前記第1のノードの電位を反転した電位とするインバータ回路と、

前記出力信号を出力する出力端子と、第1のクロック信号が供給される第3の端子と、を有し、前記第1のノードの電位と前記第2のノードの電位とが供給され、前記出力信号の電位を、前記第1のクロック信号に基づく電位とする出力回路と、を備え、

前記インバータ回路は、

前記第1の端子と前記第2のノードとの間に電流路が接続され、制御端子に前記第1のノードの電位が供給される第1のトランジスタと、電流路の一端が前記第2のノードに接続される第2のトランジスタと、電流路の一端が前記第2のトランジスタの前記電流路の他端に接続され、電流路の他端が前記第2の端子又は前記第3の端子のいずれか一方に接続される第3のトランジスタと、を備えた、

ことを特徴とするシフトレジスタ。 A multi-stage shift register comprising a plurality of cascaded shift circuits,

Each of the shift circuits is

An input terminal to which the output signal of the previous stage is supplied as an input signal, a reset terminal to which the output signal of the next stage is supplied as a reset signal, and a first node, and the input signal is supplied to the input terminal An input circuit for setting the potential of the first node to a potential according to the level of the input signal when

A second node; a first terminal; and a second terminal, to which the potential of the first node is supplied, and the potential of the second node is set to the potential of the first node. An inverter circuit having an inverted potential;

An output terminal for outputting the output signal; and a third terminal to which a first clock signal is supplied, and the potential of the first node and the potential of the second node are supplied, An output circuit for setting the potential of the output signal to a potential based on the first clock signal,

The inverter circuit is

A current path is connected between the first terminal and the second node, and a potential of the first node is supplied to a control terminal, and one end of the current path is connected to the second node A second transistor connected to the node, and one end of a current path connected to the other end of the current path of the second transistor, and the other end of the current path connected to the second terminal or the third terminal. A third transistor connected to either one of

A shift register characterized by that.

ことを特徴とする請求項1又は2に記載のシフトレジスタ。 In the inverter circuit, one end of a current path is connected to the second node, the other end of the current path is connected to the second terminal, the reset signal is supplied to a control terminal, and the second circuit A fourth transistor for controlling the potential of the node;

The shift register according to claim 1 or 2, wherein

請求項1乃至5のいずれか1項に記載のシフトレジスタを含み、当該シフトレジスタに含まれる各シフト回路の出力信号を、行を選択する行選択信号として各行毎に供給し、前記複数の画素回路を行毎に選択する行選択ドライバを備えた、

ことを特徴とする電子機器。

A plurality of pixel circuits arranged in a matrix with light emitting elements;

6. The shift register according to claim 1, wherein an output signal of each shift circuit included in the shift register is supplied for each row as a row selection signal for selecting a row, and the plurality of pixels With a row selection driver that selects circuits by row

An electronic device characterized by that.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009087287A JP2010238323A (en) | 2009-03-31 | 2009-03-31 | Shift register and electronic device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009087287A JP2010238323A (en) | 2009-03-31 | 2009-03-31 | Shift register and electronic device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010238323A true JP2010238323A (en) | 2010-10-21 |

| JP2010238323A5 JP2010238323A5 (en) | 2011-11-17 |

Family

ID=43092508

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009087287A Pending JP2010238323A (en) | 2009-03-31 | 2009-03-31 | Shift register and electronic device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2010238323A (en) |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8912996B2 (en) | 2011-11-18 | 2014-12-16 | Samsung Display Co., Ltd. | Scan driver and driving method thereof |

| JP2015068978A (en) * | 2013-09-27 | 2015-04-13 | 株式会社ジャパンディスプレイ | Gate signal line drive circuit and display device |

| WO2015151798A1 (en) * | 2014-03-31 | 2015-10-08 | ソニー株式会社 | Mounting substrate and electronic device |

| US9653179B2 (en) | 2014-12-30 | 2017-05-16 | Shanghai Tianma AM-OLED Co., Ltd. | Shift register, driving method and gate driving circuit |

| JP2017120411A (en) * | 2015-12-30 | 2017-07-06 | エルジー ディスプレイ カンパニー リミテッド | Gate drive module and built-in gate panel |

| US10789906B2 (en) | 2015-01-27 | 2020-09-29 | Samsung Display Co., Ltd. | Gate driving circuit |

| US10971412B2 (en) | 2014-03-31 | 2021-04-06 | Sony Semiconductor Solutions Corporation | Mounting substrate and electronic apparatus |

| US11139248B2 (en) | 2014-03-31 | 2021-10-05 | Sony Semiconductor Solutions Corporation | Mounting substrate and electronic apparatus |

| US12354512B2 (en) | 2022-04-28 | 2025-07-08 | Beijing Boe Optoelectronics Technology Co., Ltd. | Driving circuit, driving method and display device |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004524639A (en) * | 2001-02-13 | 2004-08-12 | サムスン エレクトロニクス カンパニー リミテッド | Shift register and liquid crystal display device using the same |

| JP2007293995A (en) * | 2006-04-25 | 2007-11-08 | Mitsubishi Electric Corp | Shift register circuit and image display apparatus including the same |

| JP2008108374A (en) * | 2006-10-26 | 2008-05-08 | Mitsubishi Electric Corp | Shift register circuit and image display equipped therewith |

| JP2008140489A (en) * | 2006-12-04 | 2008-06-19 | Seiko Epson Corp | Shift register, scanning line driving circuit, data line driving circuit, electro-optical device, and electronic apparatus |

-

2009

- 2009-03-31 JP JP2009087287A patent/JP2010238323A/en active Pending

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004524639A (en) * | 2001-02-13 | 2004-08-12 | サムスン エレクトロニクス カンパニー リミテッド | Shift register and liquid crystal display device using the same |

| JP2007293995A (en) * | 2006-04-25 | 2007-11-08 | Mitsubishi Electric Corp | Shift register circuit and image display apparatus including the same |

| JP2008108374A (en) * | 2006-10-26 | 2008-05-08 | Mitsubishi Electric Corp | Shift register circuit and image display equipped therewith |

| JP2008140489A (en) * | 2006-12-04 | 2008-06-19 | Seiko Epson Corp | Shift register, scanning line driving circuit, data line driving circuit, electro-optical device, and electronic apparatus |

Cited By (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8912996B2 (en) | 2011-11-18 | 2014-12-16 | Samsung Display Co., Ltd. | Scan driver and driving method thereof |

| JP2015068978A (en) * | 2013-09-27 | 2015-04-13 | 株式会社ジャパンディスプレイ | Gate signal line drive circuit and display device |

| US10510286B2 (en) | 2014-03-31 | 2019-12-17 | Sony Semiconductor Solutions Corporation | Mounting substrate and electronic apparatus |

| WO2015151798A1 (en) * | 2014-03-31 | 2015-10-08 | ソニー株式会社 | Mounting substrate and electronic device |

| US12027429B2 (en) | 2014-03-31 | 2024-07-02 | Sony Semiconductor Solutions Corporation | Mounting substrate and electronic apparatus |

| US11139248B2 (en) | 2014-03-31 | 2021-10-05 | Sony Semiconductor Solutions Corporation | Mounting substrate and electronic apparatus |

| US10971412B2 (en) | 2014-03-31 | 2021-04-06 | Sony Semiconductor Solutions Corporation | Mounting substrate and electronic apparatus |

| US9653179B2 (en) | 2014-12-30 | 2017-05-16 | Shanghai Tianma AM-OLED Co., Ltd. | Shift register, driving method and gate driving circuit |

| US10789906B2 (en) | 2015-01-27 | 2020-09-29 | Samsung Display Co., Ltd. | Gate driving circuit |

| JP2019015994A (en) * | 2015-12-30 | 2019-01-31 | エルジー ディスプレイ カンパニー リミテッド | Gate drive module and built-in gate panel |

| US10170053B2 (en) | 2015-12-30 | 2019-01-01 | Lg Display Co., Ltd. | Gate driving module and gate-in-panel |

| KR20170080821A (en) * | 2015-12-30 | 2017-07-11 | 엘지디스플레이 주식회사 | Module for driving gate and gate in panel |

| KR102555084B1 (en) | 2015-12-30 | 2023-07-13 | 엘지디스플레이 주식회사 | Module for driving gate and gate in panel |

| JP2017120411A (en) * | 2015-12-30 | 2017-07-06 | エルジー ディスプレイ カンパニー リミテッド | Gate drive module and built-in gate panel |

| US12354512B2 (en) | 2022-04-28 | 2025-07-08 | Beijing Boe Optoelectronics Technology Co., Ltd. | Driving circuit, driving method and display device |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP3142099B1 (en) | Compensation pixel circuit and display device | |

| CN100479019C (en) | Scan driving ciruit and organic light emitting display using the same | |

| US8933865B2 (en) | Display device and drive method therefor | |

| JP5734403B2 (en) | Display device and driving method thereof | |

| JP5214030B2 (en) | Display device | |

| US20250148999A1 (en) | Electronic device | |

| CN109285504B (en) | Shifting register unit, driving method thereof and grid driving circuit | |

| CN105575327B (en) | A kind of image element circuit, its driving method and organic EL display panel | |

| CN109949739B (en) | Pixel circuit, driving method and display | |

| JP2010238323A (en) | Shift register and electronic device | |

| KR20130051986A (en) | Display device and method for driving same | |

| EP3151225A1 (en) | Shift circuit, shift resistor, and display device | |

| JP7092279B2 (en) | Array board row drive circuit | |

| JP5245678B2 (en) | Signal shift device, shift register, electronic device, and signal shift device driving method | |

| KR20140139757A (en) | Shift circuit, shift resistor and display | |

| JP2015060100A (en) | Display device and drive circuit | |

| JP2014153532A (en) | Display device and drive circuit | |

| JP2008083117A (en) | Display device | |

| JP4889205B2 (en) | Active matrix display device | |

| JP2014085648A (en) | Display device and drive circuit | |

| CN113643659A (en) | Organic Light Emitting Diode Display Device | |

| US11749225B2 (en) | Scanning signal line drive circuit and display device provided with same | |

| JP6013869B2 (en) | Driver circuit, display device, and electronic device | |

| JP2004126512A (en) | Display device and its driving method | |

| TWI780635B (en) | Display pannel and pixel circuit |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111003 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20111003 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130828 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130910 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131017 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140304 |