JP2010185982A - 暗号化装置、復号化装置及び記憶装置 - Google Patents

暗号化装置、復号化装置及び記憶装置 Download PDFInfo

- Publication number

- JP2010185982A JP2010185982A JP2009029022A JP2009029022A JP2010185982A JP 2010185982 A JP2010185982 A JP 2010185982A JP 2009029022 A JP2009029022 A JP 2009029022A JP 2009029022 A JP2009029022 A JP 2009029022A JP 2010185982 A JP2010185982 A JP 2010185982A

- Authority

- JP

- Japan

- Prior art keywords

- key

- encryption

- memory

- decryption

- extension

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/08—Key distribution or management, e.g. generation, sharing or updating, of cryptographic keys or passwords

- H04L9/0894—Escrow, recovery or storing of secret information, e.g. secret key escrow or cryptographic key storage

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/14—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols using a plurality of keys or algorithms

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L2209/00—Additional information or applications relating to cryptographic mechanisms or cryptographic arrangements for secret or secure communication H04L9/00

- H04L2209/24—Key scheduling, i.e. generating round keys or sub-keys for block encryption

Landscapes

- Engineering & Computer Science (AREA)

- Computer Security & Cryptography (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Storage Device Security (AREA)

Abstract

【課題】暗号鍵、復号鍵保持に要するメモリ容量を低減し、暗号鍵又は復号鍵の初期値設定の際のオーバーヘッドを低減する。

【解決手段】1つの暗号鍵を拡張して得られるN個の拡張鍵を順次データ処理に使用する暗号化装置において、鍵の初期値と対応するフラグを保持する第1のメモリと、命令が暗号化命令でありフラグが暗号鍵を示すと比較結果信号を出力する比較回路と、比較結果信号が入力されると暗号化命令及びトリガ信号に基づいて第1のメモリに保持された鍵を初期値として第2のメモリにロードするセレクタと、第2のメモリに保持された鍵に基づいて順次拡張鍵を計算してセレクタに入力する暗号化用拡張計算部を備え、セレクタは、第2のメモリへ鍵の初期値をロードする時以外は、暗号化命令に基づいて暗号化用拡張計算部で計算された拡張鍵を第2のメモリにロードすることで暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張するように構成する。

【選択図】図4

【解決手段】1つの暗号鍵を拡張して得られるN個の拡張鍵を順次データ処理に使用する暗号化装置において、鍵の初期値と対応するフラグを保持する第1のメモリと、命令が暗号化命令でありフラグが暗号鍵を示すと比較結果信号を出力する比較回路と、比較結果信号が入力されると暗号化命令及びトリガ信号に基づいて第1のメモリに保持された鍵を初期値として第2のメモリにロードするセレクタと、第2のメモリに保持された鍵に基づいて順次拡張鍵を計算してセレクタに入力する暗号化用拡張計算部を備え、セレクタは、第2のメモリへ鍵の初期値をロードする時以外は、暗号化命令に基づいて暗号化用拡張計算部で計算された拡張鍵を第2のメモリにロードすることで暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張するように構成する。

【選択図】図4

Description

本発明は、暗号化装置、復号化装置及び記憶装置に係り、特にAES(Advanced Encryption Standard)方式を用いる暗号化装置、復号化装置及び記憶装置に関する。

図1は、AES方式を用いる暗号化処理を説明する図である。AES方式を用いる暗号化処理では、暗号鍵スケジュールと呼ばれる、1つの暗号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用する。例えば、暗号鍵長が256ビットの場合、N=15個の拡張鍵を順次データ処理に使用する。暗号化を行う際には、このN個の拡張鍵を1番目からN番目までの順で使用する。

例えば、128ビットの平文又は暗号文に対する暗号化処理は、次のようなシーケンスで行われる。

E1: 256ビットの暗号鍵から128ビットの拡張鍵1を求める。

E2: 128ビットの平文と128ビットの拡張鍵1から1ラウンド(Round)完了時の128ビットのデータを計算する。

E3: 256ビットの暗号鍵若しくは128ビットの拡張鍵1から128ビットの拡張鍵2を求める。拡張鍵1及び拡張鍵2は、暗号鍵に相当する。

E4: 1ラウンド完了時の128ビットのデータと128ビットの拡張鍵2から2ラウンド目の128ビットのデータを計算する。

E5: 以下同様の処理をNラウンドが完了するまで繰り返し、Nラウンドが完了した時点の128ビットのデータが暗号文となる。

図2は、AES方式を用いる復号化処理を説明する図である。復号化を行う際には、暗号化の際とは逆にN個の拡張鍵をN番目から1番目の順で使用する。

例えば、128ビットの暗号文に対する復号化処理は、次のようなシーケンスで行われる。

D1: 256ビットの復号鍵、即ち、128ビットの拡張鍵Nと128ビットの拡張鍵N−1を求める。拡張鍵N及び拡張鍵N−1は、復号鍵に相当する。

D2: 128ビットの暗号文と128ビットの拡張鍵NからN−1ラウンド完了時の128ビットのデータを計算する。

D3: 128ビットの拡張鍵Nから128ビットの拡張鍵N−1を求める。

D4: N−1ラウンド完了時の128ビットのデータと128ビットの拡張鍵N−1からN−2ラウンド目の128ビットのデータを計算する。

D5: 以下同様の処理を0ラウンドが完了するまで繰り返し、0ラウンドが完了した時点の128ビットのデータが平文(復号文)となる。

このように、暗号化処理と復号化処理とでは、拡張鍵の初期値が異なる。このため、暗号化処理を実行しながら鍵拡張(所謂オン・ザ・フライ(On-The-Fly)鍵拡張)を行う際には、暗号化処理の前に拡張鍵を一旦初期化する必要がある。同様に、復号化処理を実行しながら鍵拡張を行う際には、復号化処理の前に拡張鍵を一旦初期化する必要がある。

一方、AES方式の暗号化及び復号化の処理方向は頻繁に入れ替わるため、CPU(Central Processing Unit)等のプロセッサが、暗号化、復号化の切り替わりの度に、初期値を設定する際のオーバーヘッドがないことが望ましい。又、暗号化のモード(Cipher Modes of Operation)によっては、暗号化や復号化に使用する初期ベクトル生成の際に暗号処理を行うため、1回の起動内で復号化、暗号化、復号化といった具合に連続して処理方向が入れ替わる場合もあり、この場合であっても初期値を設定する際のオーバーヘッドがないことが望ましい。

図3は、従来の暗号化及び復号化装置の一例を説明する図である。ここでは説明の便宜上、暗号用鍵及び復号鍵の鍵長が256ビットであるものとする。暗号化及び復号化装置は、図3に示す如き鍵拡張回路と、AES方式の暗号化処理及び復号化処理を行うAES方式のエンジン(図示せず)を有する。

先ず、CPU10が拡張鍵1と拡張鍵2をメモリ11に設定すると共に、拡張鍵N−1と拡張鍵Nをメモリ12に設定する。セレクタ13は、暗号化命令又は復号化命令に基づいてメモリ11又は12内の拡張鍵をセレクタ14へ選択出力する。セレクタ13は、暗号化処理を行う時にはCPU10からの暗号化命令に基づいて拡張鍵1と拡張鍵2(即ち、暗号鍵)をセレクタ14へ選択出力し、復号化処理を行う時にはCPU10からの復号化命令に基づいて拡張鍵N−1と拡張鍵N(即ち、復号鍵)をセレクタ14へ選択出力する。

セレクタ14は、暗号化命令及びメモリ15へ初期値のロードを指示するトリガ信号に基づいて暗号鍵を初期値としてメモリ15にロードし、復号化命令及びトリガ信号に基づいて復号鍵を初期値としてメモリ15にロードする。暗号化用拡張計算部16は、暗号化処理を行う際にはメモリ15内の暗号鍵に基づいて順次拡張鍵を計算する。復号化用拡張計算部17は、復号化処理を行う際にはメモリ15内の復号鍵に基づいて順次拡張鍵を計算する。セレクタ14は、メモリ15へ鍵の初期値をロードする時以外は、暗号化命令に基づいて暗号化用拡張計算部16で計算された拡張鍵をメモリ15にロードし、復号化命令に基づいて復号化用拡張計算部17で計算された拡張鍵をメモリ15にロードする。従って、暗号化処理を行う時には暗号鍵が拡張鍵1〜Nの順に拡張され、復号化処理を行う時には復号鍵が拡張鍵N〜1の順に拡張される。セレクタ14、メモリ15、暗号化用拡張計算部16及び復号化用拡張計算部17は、鍵拡張計算回路18を形成する。

AES方式のエンジン(図示せず)は、暗号化命令に基づいて、平文に対してメモリ15に格納された拡張鍵を用いて暗号化処理を行い暗号文を生成する。又、AES方式のエンジンは、復号化命令に基づいて、暗号文に対してメモリ15に格納された拡張鍵を用いて復号化処理を行い平文(復号文)を生成する。

従来の暗号化及び復号化装置では、鍵の初期値を設定する際のオーバーヘッドを小さくするため、CPU10が予め用意された暗号鍵と復号鍵の2つをメモリ11,12に設定後、データ暗号化処理又は復号化処理に合わせて鍵スケジュールを初期化し、暗号化処理又は復号化処理を行う。このため、1つの暗号鍵に対して暗号鍵用と復号鍵用の2つのメモリ11,12が必要となる。

又、CPU10が予め暗号鍵と復号鍵の2つを用意する方法では、単一のAES方式のエンジンを用いて複数の暗号鍵に対して夫々のデータの暗号化処理(又は、復号化処理)を行う暗号化及び復号化装置の場合、CPU10は暗号鍵の数分の暗号鍵及び復号鍵を用意する必要がある。このため、CPU10は、暗号鍵及び復号鍵を保持するのためにメモリ11,12等のメモリ中、比較的大きなメモリ容量を占有してしまう。更に、暗号鍵を変更する際には、暗号鍵と復号鍵の両方を変更する必要が生じるため、暗号鍵と復号鍵の初期値を設定する処理に時間がかかり、CPU10のオーバーヘッドが大きくなってしまう。

特表2007−500376号公報

特開2005−4048号公報

従来は、暗号鍵及び復号鍵を保持するのに要するメモリ容量を低減し、且つ、暗号鍵又は復号鍵の初期値を設定する際のプロセッサのオーバーヘッドを低減することが難しいという問題があった。

そこで、本発明は、暗号鍵及び復号鍵を保持するのに要するメモリ容量を低減し、且つ、暗号鍵又は復号鍵の初期値を設定する際のプロセッサのオーバーヘッドを低減可能な暗号化装置、復号化装置及び記憶装置を提供することを目的とする。

本発明の一観点によれば、1つの暗号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用する暗号化装置であって、鍵の初期値と対応するフラグを保持する第1のメモリと、命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に暗号化に関するもので、前記命令が暗号化命令であり前記フラグが暗号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、第2のメモリと、前記比較結果信号が入力されると、前記暗号化命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する暗号化用拡張計算部を備え、前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記暗号化命令に基づいて前記暗号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張する暗号化装置が提供される。

本発明の一観点によれば、1つの復号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用する復号化装置であって、鍵の初期値と対応するフラグを保持する第1のメモリと、命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に復号化に関するもので、前記命令が復号化命令であり前記フラグが復号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、第2のメモリと、前記比較結果信号が入力されると、前記復号化命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する復号化用拡張計算部を備え、前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記復号化命令に基づいて前記復号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第Nの拡張鍵〜第1の拡張鍵の順に拡張する復号化装置が提供される。

本発明の一観点によれば、データを記憶装置に記録し、前記記憶装置からデータを再生する制御を行う制御部と、1つの暗号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用し、前記記憶装置に記録するデータを暗号化し、前記記憶装置から再生されたデータを復号化する暗号化及び復号化装置を備え、前記暗号化及び復号化装置は、鍵の初期値と対応するフラグを保持する第1のメモリと、命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に暗号化に関するもので前記命令が暗号化命令であり前記フラグが暗号鍵を示すか、或いは、共に復号化に関するもので前記命令が復号化命令であり前記フラグが復号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、第2のメモリと、前記比較結果信号が入力されると、前記命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する暗号化用拡張計算部と、前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する復号化用拡張計算部を有し、前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記暗号化命令に基づいて前記暗号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張すると共に、前記復号化命令に基づいて前記復号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記復号鍵を第Nの拡張鍵〜第1の拡張鍵の順に拡張する記憶装置が提供される。

開示の暗号化装置、復号化装置及び記憶装置によれば、暗号鍵及び復号鍵を保持するのに要するメモリ容量を低減し、且つ、暗号鍵又は復号鍵の初期値を設定する際のプロセッサのオーバーヘッドを低減することが可能となる。

開示の暗号化装置、復号化装置及び記憶装置は、鍵の初期値と対応するフラグを保持する第1のメモリと、命令と第1のメモリに保持されたフラグが示す鍵が共に暗号化に関するもので命令が暗号化命令でありフラグが暗号鍵を示すか、或いは、共に復号化に関するもので命令が復号化命令でありフラグが復号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、第2のメモリと、比較結果信号が入力されると命令及びトリガ信号に基づいて第1のメモリに保持された鍵を初期値として第2のメモリにロードするセレクタと、第2のメモリに保持された鍵に基づいて順次拡張鍵を計算してセレクタに入力する暗号化用拡張計算部と、第2のメモリに保持された鍵に基づいて順次拡張鍵を計算してセレクタに入力する復号化用拡張計算部を有する。

セレクタは、第2のメモリへ鍵の初期値をロードする時以外は、暗号化命令に基づいて暗号化用拡張計算部で計算された拡張鍵を第2のメモリにロードすることで暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張すると共に、復号化命令に基づいて復号化用拡張計算部で計算された拡張鍵を第2のメモリにロードすることで復号鍵を第Nの拡張鍵〜第1の拡張鍵の順に拡張する。

これにより、暗号鍵及び復号鍵を保持するのに要するメモリ容量を低減し、且つ、暗号鍵又は復号鍵の初期値を設定する際のプロセッサのオーバーヘッドを低減可能となる。

以下に、本発明の暗号化装置、復号化装置及び記憶装置の各実施例を、図4以降と共に説明する。

図4は、本発明の一実施例における暗号化及び復号化装置を説明する図である。ここでは説明の便宜上、暗号用鍵及び復号鍵の鍵長が256ビットであるものとする。暗号化及び復号化装置は、図4に示す如き鍵拡張回路と、AES方式の暗号化処理及び復号化処理を行うAES方式のエンジン(図示せず)を有する。AES方式のエンジンについては後述する。

先ず、CPU20が拡張鍵1と拡張鍵2、即ち、暗号鍵の初期値をメモリ21に設定すると共に、メモリ21に設定された拡張鍵1と拡張鍵2が暗号鍵であることを示す1ビットのフラグをメモリ22に設定する。或いは、CPU20が拡張鍵N−1と拡張鍵N、即ち、復号鍵の初期値をメモリ21に設定すると共に、メモリ21に設定された拡張鍵N−1と拡張鍵Nが復号鍵であることを示す1ビットのフラグをメモリ22に設定する。メモリ21は鍵スケジュールの初期値を保持できる大きさを有するものであれば良く、又、メモリ22は1ビットのフラグを保持できる大きさのものであれば良い。メモリ21は、CPU20が設定した鍵スケジュールの初期値、若しくは、最後にAES方式のエンジンが使用した鍵スケジュールの初期値を保持し、メモリ22はメモリ21の状態(暗号鍵の初期値と復号鍵の初期値のどちらを保持しているか)を示すフラグを保持する。

暗号化処理は、CPU20が発行する暗号化命令に応答して開始される。又、復号化処理は、CPU20が発行する復号化命令に応答して開始される。CPU20が発行した暗号化命令又は復号化命令は、コントロール回路100に供給される。

コントロール回路100は、命令保持メモリ101、処理ブロック数カウンタ102、内部命令生成回路103、鍵拡張ラウンドカウンタ104及びトリガ信号生成回路29を有する。

命令保持メモリ101は、CPU20が発行した命令が暗号化命令であるか復号化命令であるかを認識できるように、CPU20が発行した命令を保持する。処理ブロック数カウンタ102は、CPU20が発行した命令に基づいて例えば128ビットの暗号化処理又は復号化処理が完了する度にインクリメントされることで、処理ブロックを0からMま(Mは2以上の自然数)でカウントするものであり、カウント値がMに達するとカウント値が0に初期化される。内部命令生成回路103は、処理ブロック数カウンタ102のカウント値が1からM−1までの場合は、命令保持メモリ101に保持された命令を実行し、処理ブロックカウンタ102のカウント値がMの場合は命令保持メモリ101に保持された命令と逆の命令を実行する1ビットの内部命令を生成する。

鍵拡張ラウンドカウンタ104は、拡張鍵1〜N(即ち、第1の拡張鍵〜第Nの拡張鍵)のラウンドをカウントする。トリガ信号生成回路29は、処理ブロック数カウンタ102のカウント値が0からM−1までの場合は、鍵拡張ラウンドカウンタ104でカウントされた鍵拡張のNラウンド毎、即ち、例えば128ビットの復号化処理の度に比較回路23の出力に応答してトリガ信号を生成して後述する鍵拡張計算回路28内のセレクタ24に出力される。一方、処理ブロック数カウンタ102のカウント値がMの場合は、トリガ信号生成回路29が生成するトリガ信号はマスクされてセレクタ24には出力されない。

比較回路23は、暗号化処理を行う時にはCPU20から命令保持メモリ101を介して得られる1ビットの暗号化命令とメモリ22に保持されたフラグが示す鍵が共に暗号化に関するものであると、比較したビットが一致することを示す1ビットの比較結果信号をセレクタ24へ出力する。又、比較回路23は、復号化処理を行う時にはCPU20から命令保持メモリ101を介して得られる1ビットの復号化命令とメモリ22に保持されたフラグが示す鍵が共に復号化に関するものであると、比較したビットが一致することを示す比較結果信号をセレクタ24へ出力する。

暗号化処理を行う時、セレクタ24は、一致を示す比較結果信号が入力されると、暗号化命令及びメモリ25へ初期値のロードを指示する1ビットのトリガ信号に基づいてメモリ21に保持された暗号鍵を初期値としてメモリ25にロードし、メモリ21,22の保持内容は変更されない。トリガ信号は、上記の如く比較回路23の出力に応答してトリガ信号生成回路29から出力される。暗号化用拡張計算部26は、暗号化処理を行う際にはメモリ25内の暗号鍵に基づいて順次拡張鍵1〜N(即ち、第1の拡張鍵〜第Nの拡張鍵)を計算する。セレクタ24は、メモリ25へ鍵の初期値をロードする時以外は、暗号化命令に基づいて暗号化用拡張計算部26で計算された拡張鍵をメモリ25にロードする。従って、暗号化処理を行う時には暗号鍵が拡張鍵1〜Nの順に拡張される。

復号化処理を行う時、セレクタ24は、一致を示す比較結果信号が入力されると、復号化命令及びトリガ信号に基づいて復号鍵を初期値としてメモリ25にロードし、メモリ21,22の保持内容は変更されない。復号化用拡張計算部27は、復号化処理を行う際にはメモリ25内の復号鍵に基づいて順次拡張鍵N〜1(即ち、第Nの拡張鍵〜第1の拡張鍵)を計算する。セレクタ24は、メモリ25へ鍵の初期値をロードする時以外は、復号化命令に基づいて復号化用拡張計算部27で計算された拡張鍵をメモリ25にロードする。従って、復号化処理を行う時には復号鍵が拡張鍵N〜1の順に拡張される。

セレクタ24、メモリ25、暗号化用拡張計算部26及び復号化用拡張計算部27は、鍵拡張計算回路28を形成する。

図3に示す従来の装置では、CPU10が暗号鍵と復号鍵の両方をメモリ11,12に設定していたのに対し、本実施例では、CPU20は暗号鍵又は復号鍵の一方と、鍵が暗号鍵であるか復号鍵であるかを示す1ビットのフラグをメモリ21,22設定すれば良いため、鍵の初期値を設定するための時間が従来の装置と比べて略半分になると共に、鍵の初期値を設定するメモリ11,12のメモリ容量も従来の装置のメモリ11,12と比べて約半分になる。

更に、比較回路23は、CPU20からの命令とメモリ22に保持されたフラグが示す鍵のうち、一方が暗号化に関するものであり他方が復号化に関するもので互いに異なるものであると、比較したビットが不一致であることを示す比較結果信号をセレクタ24へ出力する。

セレクタ24は、不一致を示す比較結果信号が入力されると、CPU20からの命令が暗号化命令であればトリガ信号に基づいてメモリ21に保持された復号鍵を初期値としてメモリ25にロードする。復号化用拡張計算部27は、メモリ25内の復号鍵に基づいて順次拡張鍵を計算し、復号鍵が拡張鍵N〜1の順に拡張されて暗号鍵が得られる。得られた暗号鍵は、メモリ25からメモリ21へ設定され、メモリ22へはメモリ21に設定された鍵が暗号鍵であることを示すフラグがCPU20から設定されることで、メモリ21,22の内容が暗号化処理用の内容に更新される。

セレクタ24は、不一致を示す比較結果信号が入力されると、CPU20からの命令が復号化命令であればトリガ信号に基づいてメモリ21に保持された暗号鍵を初期値としてメモリ25にロードする。暗号化用拡張計算部26は、メモリ25内の暗号鍵に基づいて順次拡張鍵を計算し、暗号鍵が拡張鍵1〜Nの順に拡張されて復号鍵が得られる。得られた復号鍵は、メモリ25からメモリ21へ設定され、メモリ22へはメモリ21に設定された鍵が復号鍵であることを示すフラグがCPU20から設定されることで、メモリ21,22の内容が復号化処理用の内容に更新される。

つまり、比較回路23での比較結果が不一致であると、メモリ22に保存されている鍵の初期値をメモリ25に設定し、暗号化用拡張計算部26又は復号化用拡張計算部27において鍵拡張を行って得られたメモリ25内の鍵の初期値をメモリ22に設定し、メモリ22に設定された鍵の初期値に対応するフラグをメモリ22に設定することでメモリ22の内容を更新する。このように、メモリ22のフラグの更新は、CPU20が設定する必要はなく、メモリ21の鍵の初期値を更新するタイミングで命令保持メモリ101を介して得られる1ビットの命令により自動的に行うことができる。

このように、本実施例では、CPU20からの命令とメモリ22に保持されたフラグが示す鍵のうち、一方が暗号化に関するものであり他方が復号化に関するもので互いに異なるものであると、鍵の初期値を設定するために暗号化用拡張計算部26又は復号化用拡張計算部27において一度鍵拡張を行う必要が生じるが、鍵長が256ビットの場合でも必要となる鍵拡張は14サイクルで完了可能である。周知の構成を有する暗号化用拡張計算部26及び周知の構成を有する復号化用拡張計算部27の演算速度は、いずれもCPU20と比べて高速であるため、このような鍵の初期値を設定のための鍵拡張はCPU20のオーバーヘッドとしては見えてこない。従って、鍵の初期値を設定するための鍵拡張によりCPU20のオーバーヘッドが従来の装置と比べて大きくなることはない。

AES方式のエンジン(図示せず)は、暗号化命令に基づいて、平文に対してメモリ25に格納された拡張鍵を用いて暗号化処理を行い暗号文を生成する。又、AES方式のエンジンは、復号化命令に基づいて、暗号文に対してメモリ25に格納された拡張鍵を用いて復号化処理を行い平文(復号文)を生成する。

尚、暗号化処理の直後に復号化処理を行う場合は、メモリ25に保持されている暗号化でN番目に使用された拡張鍵を次に行われる復号鍵の初期値として使用することにより、復号化処理のオーバーヘッドを低減可能である。同様に、復号化処理の直後に暗号化処理を行う場合は、メモリ25に保持されている復号化処理でN番目に使用された拡張鍵を次に行われる暗号鍵の初期値として使用することにより、暗号化処理のオーバーヘッドを低減可能である。

又、メモリ21,22は、別体のメモリである必要はなく、単一のメモリ内の異なるメモリ領域により形成されていても良い。又、暗号鍵又は復号鍵の初期値とフラグを、1つのデータとして扱うようにしても良い。メモリ21をCPU20からアクセス可能とすることで、CPU20は暗号鍵又は復号鍵を実暗号鍵ビット長+1ビット(フラグ)として扱うこともできる。この場合、CPU20及び鍵拡張計算回路28は共に、暗号鍵又は復号鍵(暗号化用の拡張鍵+1ビット、若しくは、復号化用の拡張鍵+1ビット)を暗号化用と復号化用の兼用の鍵として使用することができる。特に複数の暗号鍵を使用する暗号化及び復号化装置では、単一のAES方式のエンジンを用いて暗号化処理及び復号化処理を行う場合に、記憶しておく鍵が暗号鍵若しくは復号鍵のどちらか一方で良いため、鍵の初期値を設定するのに要するメモリ容量を従来に比べて低減可能であると共に、設定する鍵の初期値の鍵長も暗号鍵+1ビット又は復号鍵+1ビットで良いため、鍵の初期値を設定するためのオーバヘッドを従来に比べて小さくすることが可能である。

図5は、記憶装置を示すブロック図である。図5は、上記実施例が単一のAES方式のエンジンを用いる記憶装置に適用された場合を示す。図5に示す記憶装置30は、CPU20、メモリ31、セレクタ32、メモリ33、鍵拡張ブロック34、AES方式のエンジン(以下、単にAESエンジンと言う)35、ヘッド36及びディスク37を有する。

メモリ33は、図4に示すメモリ21,22に相当する。鍵拡張ブロック34は、図4に示す比較回路23、トリガ信号生成回路29及び鍵拡張計算回路28に相当するが、コントロール回路100の他の部分を含むものであっても良い。ヘッド36は、制御部として機能するCPU20の制御下で、ディスク37に情報を記録すると共に、ディスク37に記録された情報を再生する。ディスク37は、磁気ディスク、光ディスクや光磁気ディスク等の記録媒体であっても良い。ディスク37が例えば磁気ディスクの場合、ヘッド36は磁気ディスク上を所定の浮上量を維持しながら走査するよう移動及び制御されるが、ヘッド36の移動及び制御機構自体はHDD(Hard Disk Drive)の分野では周知であるため、その図示及び説明は省略する。又、ヘッド36及びディスク37の数は夫々複数であっても良い。

本実施例では、データの記録再生に使用される記憶装置は、ヘッド36とディスク37を有するディスク装置で形成されているが、記憶装置はヘッドを用いる装置に限定されず、フラッシュメモリ等の半導体記憶装置をデータの記録再生に使用しても良いことは言うまでもない。半導体記憶装置等をデータの記録再生に使用する場合も、データの記憶装置への記録及びデータの記憶装置からの再生は、制御部として機能するCPU20の制御下で行われる。

図5の例では、記憶装置30は3種類の鍵k1,k2,k3から鍵を選択可能であるが、選択可能な鍵の数は3種類に限定されるものではない。CPU20は、セレクタ32に鍵選択信号を出力することで、メモリ31に保持されている鍵k1,k2,k3と対応するフラグf1,f2,f3のうち選択された鍵と対応するフラグをメモリ33に設定する。鍵拡張ブロック34は、CPU20からの命令とメモリ33に保持されたフラグのビットが一致すると、トリガ信号生成回路29からのトリガ信号に基づいてメモリ33に保持された鍵を初期値としてメモリ25にロードする。メモリ33に保持された鍵が暗号鍵の場合は暗号化用拡張計算部26が順次拡張鍵1〜Nを計算し、復号鍵の場合は復号化用拡張計算部27が順次拡張鍵N〜1を計算する。

一方、鍵拡張ブロック34は、CPU20からの命令とメモリ33に保持されたフラグのビットが不一致であると、CPU20からの命令及びトリガ信号生成回路29からのトリガ信号に基づいてメモリ33に保持された鍵を初期値としてメモリ25にロードする。メモリ33に保持された鍵が復号鍵の場合は復号化用拡張計算部27が復号鍵に基づいて順次拡張鍵N〜1を計算し、暗号鍵の場合は暗号化用拡張計算部26が暗号鍵に基づいて順次拡張鍵1〜Nを計算する。これにより、得られた暗号鍵又は復号鍵は、メモリ25からメモリ33へ設定されると共に、メモリ33に設定された鍵に対応するフラグが設定されることで、メモリ33の内容が更新される。

AESエンジン35は、暗号化命令に基づいて、ホスト装置等の外部装置(図示せず)から記憶装置30に入力された平文に対して鍵拡張ブロック34内のメモリ25に格納された拡張鍵を用いて図1に示す如き暗号化処理を行い暗号文を生成する。生成された暗号文は、ヘッド36によりディスク37に記録される。又、AESエンジン35は、復号化命令に基づいて、ヘッド36によりディスク37から再生された暗号文に対して鍵拡張ブロック34内のメモリ25に格納された拡張鍵を用いて図2に示す如き復号化処理を行い平文(復号文)を生成する。生成された平文は、記憶装置30からホスト装置等の外部装置へ出力される。AESエンジン35自体は、周知の構成を有するものである。

記憶装置30がHDDの場合、暗号化処理及び復号化処理では同じ鍵を用いて例えば数メガビット(Mbit)分の連続処理が実行される。このような連続処理は、上記の如き暗号化処理及び復号化処理を繰り返し実行することにより実現される。

次に、本実施例における拡張鍵の生成シーケンスを、図6と共に説明する。図6は、拡張鍵の生成シーケンスを説明するフローチャートである。図6において、ステップS1,S2はCPU20により実行され、ステップS11〜S17は鍵拡張ブロック34により実行される。

CPU20では、ステップS1が暗号鍵又は復号鍵と対応するフラグをメモリ33に設定する。これにより、鍵拡張ブロック34では、ステップS11が暗号鍵又は復号鍵と対応するフラグがメモリ33に保持する。CPU20では、ステップS2で暗号化命令を発行して暗号化処理を開始するか、或いは、復号化命令を発行して復号化処理を開始する。鍵拡張ブロック34では、ステップS12がCPU20が発行した命令とメモリ33内のフラグを比較し、ステップS13が比較結果が一致するか否かを判定する。ステップS13の判定結果がYESであると処理はステップS14へ進み、NOであると処理はステップS16へ進む。

ステップS13の判定結果がYESであると、鍵拡張ブロック34では、ステップS14がトリガ信号生成回路29によりトリガ信号を生成し、このトリガ信号に応答してメモリ33に保持された鍵をメモリ25に保持し、CPU20からの命令が暗号化命令であれば暗号化用拡張計算部26で128ビットのデータの暗号化用拡張計算を行い、命令が復号化命令であれば復号化用拡張計算部27で128ビットのデータの復号化拡張計算を行う。この際、AESエンジン35では、各拡張鍵を用いてデータの暗号化又は復号化を行い、対応するラウンド完了時のデータを求める。鍵拡張ブロック34では、ステップS15が暗号化処理又は復号化処理をN回連続して行ったか否かを判定し、判定結果がNOであると処理はステップS14へ戻り、YESであると処理は終了する。

一方、ステップS13の判定結果がNOであると、鍵拡張ブロック34では、ステップS16がトリガ信号生成回路29によりトリガ信号を生成し、このトリガ信号に応答してメモリ33に保持された鍵をメモリ25に保持し、CPU20からの命令が暗号化命令であれば復号化用拡張計算部27で128ビットのデータの復号化用拡張計算を行い、命令が復号化命令であれば暗号化用拡張計算部26で128ビットのデータの暗号化用拡張計算を行う。又、ステップS16は、計算された暗号鍵又は復号鍵をメモリ33に保持すると共に、メモリ33に保持された暗号鍵又は復号鍵に対応するフラグをメモリ33に保持する。この際、AESエンジン35では、各拡張鍵を用いたデータの暗号化又は復号化を行わない。

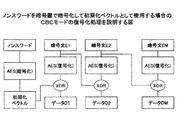

ところで、復号化処理の直後に一度暗号化処理を行うシーケンスの一例としては、ブロック・サイファー・モード・オブ・オペレーション(Block Cipher Modes of Operation)で用いられる場合がある。例えば、CBC(Cipher Block Chain)モードでは、ノンスワード(Nonce Word)を同じ鍵で暗号化した結果を初期化ベクトル(Initialization Vector)として使用する方法が推奨されている。初期化ベクトルとは、CBCモードを開始する際に最初のデータ処理に使用される初期値であり、128ビットのデータ処理の場合は初期値も128ビットである。この推奨されている方法を、HDDのようなセクタ単位に暗号化処理又は復号化処理を行い、連続セクタライトや連続セクタリードを行う記憶装置に適用し復号化を行う場合、セクタの最後の128ビットのデータの復号化後に、128ビットのノンスワードの暗号化を行って初期化ベクトルを生成し、次のセクタの先頭の128ビットのデータの復号化を行うという一連の処理を、CPU20の介在なしで連続して行うことが必要となる。一方、暗号化を行う場合は、初期化ベクトルの暗号化、セクタの暗号化を行うことになるため、AESは常に暗号化を行うことになる。暗号化の説明はここでは省略する。

次に、1セクタの処理を、1回のノンスワードの暗号化処理とM回の連続した復号化処理で行うものとしたときに、CPU20の介在なしにLセクタの処理を行う場合のシーケンスを図7と共に説明する。図7は、このようにCPU20の介在なしにLセクタの処理を行う場合のシーケンスを説明するフローチャートである。

図7において、ステップS21では、初期条件が設定される。初期条件が設定された状態では、メモリ33(又は、メモリ21,22)の内容は復号化用に初期化されており、図6のステップS13の判定結果がYES、或いは、ステップS16が完了している、この状態では、既に復号化が1回以上行われ、メモリ25には暗号化用の拡張鍵が保持されているものとする。ステップS22では、トリガ信号生成回路29からトリガ信号を出力せず、メモリ25の保持値をそのまま拡張鍵の初期値とし、初期化ベクトルを暗号化するために生成される内部命令に従い暗号化用拡張計算部26で暗号化用拡張計算による鍵拡張を行うと共に、AESエンジン35によるノンスワードの暗号化も同時に行う。ステップS23では、トリガ信号生成回路29からトリガ信号を出力し、拡張鍵の初期値をメモリ25に保持し、データを復号化するために生成される内部命令に従い復号化用拡張計算部27で復号化用拡張計算による鍵拡張を行うと共に、AESエンジン35によるデータの復号化も同時に行う。

上記の如く、内部命令は、処理ブロック数をカウントする処理ブロックカウンタ102のカウント値が0からM−1までの場合はCPU20が設定した復号化命令を実行し、カウント値がMの場合は暗号化命令を実行する。又、処理ブロックカウンタ102は、128ビットの暗号化処理又は復号化処理が完了する度にインクリメントされ、カウント値がMに達すると0に初期化される。トリガ信号生成回路29が生成するトリガ信号は、処理ブロック数カウンタ102の値が0からM−1までの場合は鍵拡張ラウンドカウンタ104でカウントされた鍵拡張のNラウンド毎、即ち、128ビットの復号化処理の度に比較回路23の出力に応答して出力される。処理ブロック数カウンタ102のカウント値がMの間は、トリガ信号生成回路29が生成するトリガ信号はマスクされて出力されない。

ステップS24では、AESエンジン35において復号化をM回行ったか否かを判定し、判定結果がNOであると処理はステップS23へ戻る。ステップS24の判定結果がYESであると、ステップS25では、AESエンジン35においてLセクタまでの処理が終了したか否かを判定し、判定結果がNOであると処理はステップS22へ戻る。ステップS25の判定結果がYESであると、処理は終了する。

次に、ブロック・サイファー・モード・オブ・オペレーションについて、図8〜図11と共に説明する。

一般的に、128ビット以上のデータを同じ暗号鍵で暗号化していくときには、ブロック・サイファー・モード・オブ・オペレーションという手法を用いる。良く使用されるモード(Mode)の一例としてCBCモードと呼ばれるノードがあり、CBCモードでは1セクタの処理は暗号化処理の場合は図8に示すシーケンスで行われ、復号化処理の場合は図9に示すシーケンスで行われる。

図8は、CBCモードの暗号化処理を説明する図である。図8において、データD1は、初期化ベクトルとの排他的論理和(XOR:eXclusive-OR)を取られてAES方式の暗号化を施され、暗号文E1が得られる。データD2は、暗号文E1とのXORを取られてAES方式の暗号化を施され、暗号文E2が得られる。以下同様の処理が行われ、最終的には、データDMは、暗号文EM−1とのXORを取られてAES方式の暗号化を施され、暗号文EMが得られる。

図9は、CBCモードの復号化処理を説明する図である。図9において、暗号文E1は、AES方式の復号化を施され、初期化ベクトルとのXORを取られてデータD1が得られる。暗号文E2は、AES方式の復号化を施され、暗号文E1とのXORを取られてデータD2が得られる。以下同様の処理が行われ、最終的には、暗号文EMは、AES方式の復号化を施され、暗号文EM−1とのXORを取られてデータDMが得られる。

又、推奨されている初期化ベクトルの生成方法の一例として、ノンスワードを暗号鍵で暗号化して使用する方法が挙げられる。この場合、CBCモードの1セクタの処理は暗号化処理の場合は図10に示すシーケンスで行われ、復号化処理の場合は図11に示すシーケンスで行われる。

図10は、ノンスワードを暗号鍵で暗号化して初期化ベクトルとして使用する場合のCBCモードの暗号化処理を説明する図である。図10において、ノンスワードは、AES方式の暗号化を施されて初期化ベクトルとされる。初期ベクトルは、図8の場合と同様に暗号化に使用される。

図11は、ノンスワードを暗号鍵で暗号化して初期化ベクトルとして使用する場合のCBCモードの復号化処理を説明する図である。図11において、ノンスワードは、AES方式の暗号化を施されて初期化ベクトルとされる。初期ベクトルは、図9の場合と同様に復号化に使用される。

以上の実施例を含む実施形態に関し、更に以下の付記を開示する。

(付記1)

1つの暗号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用する暗号化装置であって、

鍵の初期値と対応するフラグを保持する第1のメモリと、

命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に暗号化に関するもので、前記命令が暗号化命令であり前記フラグが暗号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、

第2のメモリと、

前記比較結果信号が入力されると、前記暗号化命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する暗号化用拡張計算部を備え、

前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記暗号化命令に基づいて前記暗号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張する、暗号化装置。

(付記2)

前記比較結果信号に基づいて前記トリガ信号を生成するトリガ信号生成回路を更に備えた、付記1記載の暗号化装置。

(付記3)

前記命令を発行すると共に、前記鍵の初期値と対応する前記フラグを第1のメモリに設定するプロセッサを更に備えた、付記1又は2記載の暗号化装置。

(付記4)

前記第1のメモリは、前記鍵の初期値を保持すると共に、保持する前記鍵の初期値を前記第1のセレクタへ出力するメモリと、前記フラグを保持すると共に、保持する前記フラグを前記比較回路へ出力するメモリを有する、付記1乃至3のいずれか1項記載の暗号化装置。

(付記5)

前記命令を発行すると共に、鍵の初期値と対応するフラグの対を複数第3のメモリに設定するプロセッサと、

前記プロセッサが発行する鍵選択信号に基づいて鍵の初期値と対応するフラグの対を1つ前記第1のメモリに設定する第2のセレクタを更に備えた、付記1又は2記載の暗号化装置。

(付記6)

前記第2のメモリに保持された前記第1の拡張鍵〜前記第Nの拡張鍵によりデータを暗号化するAES(Advanced Encryption Standard)方式のエンジンを更に備えた、付記1乃至5のいずれか1項記載の暗号化装置。

(付記7)

1つの復号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用する復号化装置であって、

鍵の初期値と対応するフラグを保持する第1のメモリと、

命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に復号化に関するもので、前記命令が復号化命令であり前記フラグが復号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、

第2のメモリと、

前記比較結果信号が入力されると、前記復号化命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する復号化用拡張計算部を備え、

前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記復号化命令に基づいて前記復号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第Nの拡張鍵〜第1の拡張鍵の順に拡張する、復号化装置。

(付記8)

前記比較結果信号に基づいて前記トリガ信号を生成するトリガ信号生成回路を更に備えた、付記7記載の復号化装置。

(付記9)

前記命令を発行すると共に、前記鍵の初期値と対応する前記フラグを第1のメモリに設定するプロセッサを更に備えた、付記7又は8記載の復号化装置。

(付記10)

前記第1のメモリは、前記鍵の初期値を保持すると共に、保持する前記鍵の初期値を前記第1のセレクタへ出力するメモリと、前記フラグを保持すると共に、保持する前記フラグを前記比較回路へ出力するメモリを有する、付記7乃至9のいずれか1項記載の復号化装置。

(付記11)

前記命令を発行すると共に、鍵の初期値と対応するフラグの対を複数第3のメモリに設定するプロセッサと、

前記プロセッサが発行する鍵選択信号に基づいて鍵の初期値と対応するフラグの対を1つ前記第1のメモリに設定する第2のセレクタを更に備えた、付記7又は8記載の復号化装置。

(付記12)

前記第2のメモリに保持された前記第Nの拡張鍵〜前記第1の拡張鍵によりデータを暗号化するAES(Advanced Encryption Standard)方式のエンジンを更に備えた、付記7乃至11のいずれか1項記載の暗号化装置。

(付記13)

データを記憶装置に記録し、前記記憶装置からデータを再生する制御を行う制御部と、

1つの暗号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用し、前記記憶装置に記録するデータを暗号化し、前記記憶装置から再生されたデータを復号化する暗号化及び復号化装置を備え、

前記暗号化及び復号化装置は、

鍵の初期値と対応するフラグを保持する第1のメモリと、

命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に暗号化に関するもので前記命令が暗号化命令であり前記フラグが暗号鍵を示すか、或いは、共に復号化に関するもので前記命令が復号化命令であり前記フラグが復号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、

第2のメモリと、

前記比較結果信号が入力されると、前記命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する暗号化用拡張計算部と、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する復号化用拡張計算部を有し、

前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記暗号化命令に基づいて前記暗号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張すると共に、前記復号化命令に基づいて前記復号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記復号鍵を第Nの拡張鍵〜第1の拡張鍵の順に拡張する、記憶装置。

(付記14)

前記暗号化及び復号化装置は、前記比較結果信号に基づいて前記トリガ信号を生成するトリガ信号生成回路を更に有する、付記13記載の記憶装置。

(付記15)

前記命令を発行すると共に、前記鍵の初期値と対応する前記フラグを第1のメモリに設定するプロセッサを更に備えた、付記13又は14記載の記憶装置。

(付記16)

前記第1のメモリは、前記鍵の初期値を保持すると共に、保持する前記鍵の初期値を前記第1のセレクタへ出力するメモリと、前記フラグを保持すると共に、保持する前記フラグを前記比較回路へ出力するメモリを有する、付記13乃至15のいずれか1項記載の記憶装置。

(付記17)

前記命令を発行すると共に、鍵の初期値と対応するフラグの対を複数第3のメモリに設定するプロセッサと、

前記プロセッサが発行する鍵選択信号に基づいて鍵の初期値と対応するフラグの対を1つ前記第1のメモリに設定する第2のセレクタを更に備えた、付記13又は14記載の記憶装置。

(付記18)

前記第2のメモリに保持された前記第1の拡張鍵〜前記第Nの拡張鍵によりデータを暗号化すると共に、前記第2のメモリに保持された前記第Nの拡張鍵〜前記第1の拡張鍵によりデータを復号化するAES(Advanced Encryption Standard)方式のエンジンを更に備えた、付記13乃至17のいずれか1項記載の記憶装置。

(付記19)

前記比較回路での比較結果が不一致であると、前記第1のメモリに保存されている鍵の初期値を前記第2のメモリに設定し、前記暗号化用拡張計算部又は前記復号化用拡張計算部において鍵拡張を行って得られた前記第2のメモリ内の鍵の初期値を前記第1のメモリに設定し、前記第1のメモリに設定された鍵の初期値に対応するフラグを前記第1のメモリに設定することで前記第1のメモリの内容を更新する、付記15又は17記載の記憶装置。

(付記20)

1つの暗号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用する暗号化及び復号化装置であって、

鍵の初期値と対応するフラグを保持する第1のメモリと、

命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に暗号化に関するもので前記命令が暗号化命令であり前記フラグが暗号鍵を示すか、或いは、共に復号化に関するもので前記命令が復号化命令であり前記フラグが復号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、

第2のメモリと、

前記比較結果信号が入力されると、前記命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する暗号化用拡張計算部と、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する復号化用拡張計算部を備え、

前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記暗号化命令に基づいて前記暗号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張すると共に、前記復号化命令に基づいて前記復号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記復号鍵を第Nの拡張鍵〜第1の拡張鍵の順に拡張する、暗号化及び復号化装置。

(付記1)

1つの暗号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用する暗号化装置であって、

鍵の初期値と対応するフラグを保持する第1のメモリと、

命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に暗号化に関するもので、前記命令が暗号化命令であり前記フラグが暗号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、

第2のメモリと、

前記比較結果信号が入力されると、前記暗号化命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する暗号化用拡張計算部を備え、

前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記暗号化命令に基づいて前記暗号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張する、暗号化装置。

(付記2)

前記比較結果信号に基づいて前記トリガ信号を生成するトリガ信号生成回路を更に備えた、付記1記載の暗号化装置。

(付記3)

前記命令を発行すると共に、前記鍵の初期値と対応する前記フラグを第1のメモリに設定するプロセッサを更に備えた、付記1又は2記載の暗号化装置。

(付記4)

前記第1のメモリは、前記鍵の初期値を保持すると共に、保持する前記鍵の初期値を前記第1のセレクタへ出力するメモリと、前記フラグを保持すると共に、保持する前記フラグを前記比較回路へ出力するメモリを有する、付記1乃至3のいずれか1項記載の暗号化装置。

(付記5)

前記命令を発行すると共に、鍵の初期値と対応するフラグの対を複数第3のメモリに設定するプロセッサと、

前記プロセッサが発行する鍵選択信号に基づいて鍵の初期値と対応するフラグの対を1つ前記第1のメモリに設定する第2のセレクタを更に備えた、付記1又は2記載の暗号化装置。

(付記6)

前記第2のメモリに保持された前記第1の拡張鍵〜前記第Nの拡張鍵によりデータを暗号化するAES(Advanced Encryption Standard)方式のエンジンを更に備えた、付記1乃至5のいずれか1項記載の暗号化装置。

(付記7)

1つの復号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用する復号化装置であって、

鍵の初期値と対応するフラグを保持する第1のメモリと、

命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に復号化に関するもので、前記命令が復号化命令であり前記フラグが復号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、

第2のメモリと、

前記比較結果信号が入力されると、前記復号化命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する復号化用拡張計算部を備え、

前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記復号化命令に基づいて前記復号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第Nの拡張鍵〜第1の拡張鍵の順に拡張する、復号化装置。

(付記8)

前記比較結果信号に基づいて前記トリガ信号を生成するトリガ信号生成回路を更に備えた、付記7記載の復号化装置。

(付記9)

前記命令を発行すると共に、前記鍵の初期値と対応する前記フラグを第1のメモリに設定するプロセッサを更に備えた、付記7又は8記載の復号化装置。

(付記10)

前記第1のメモリは、前記鍵の初期値を保持すると共に、保持する前記鍵の初期値を前記第1のセレクタへ出力するメモリと、前記フラグを保持すると共に、保持する前記フラグを前記比較回路へ出力するメモリを有する、付記7乃至9のいずれか1項記載の復号化装置。

(付記11)

前記命令を発行すると共に、鍵の初期値と対応するフラグの対を複数第3のメモリに設定するプロセッサと、

前記プロセッサが発行する鍵選択信号に基づいて鍵の初期値と対応するフラグの対を1つ前記第1のメモリに設定する第2のセレクタを更に備えた、付記7又は8記載の復号化装置。

(付記12)

前記第2のメモリに保持された前記第Nの拡張鍵〜前記第1の拡張鍵によりデータを暗号化するAES(Advanced Encryption Standard)方式のエンジンを更に備えた、付記7乃至11のいずれか1項記載の暗号化装置。

(付記13)

データを記憶装置に記録し、前記記憶装置からデータを再生する制御を行う制御部と、

1つの暗号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用し、前記記憶装置に記録するデータを暗号化し、前記記憶装置から再生されたデータを復号化する暗号化及び復号化装置を備え、

前記暗号化及び復号化装置は、

鍵の初期値と対応するフラグを保持する第1のメモリと、

命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に暗号化に関するもので前記命令が暗号化命令であり前記フラグが暗号鍵を示すか、或いは、共に復号化に関するもので前記命令が復号化命令であり前記フラグが復号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、

第2のメモリと、

前記比較結果信号が入力されると、前記命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する暗号化用拡張計算部と、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する復号化用拡張計算部を有し、

前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記暗号化命令に基づいて前記暗号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張すると共に、前記復号化命令に基づいて前記復号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記復号鍵を第Nの拡張鍵〜第1の拡張鍵の順に拡張する、記憶装置。

(付記14)

前記暗号化及び復号化装置は、前記比較結果信号に基づいて前記トリガ信号を生成するトリガ信号生成回路を更に有する、付記13記載の記憶装置。

(付記15)

前記命令を発行すると共に、前記鍵の初期値と対応する前記フラグを第1のメモリに設定するプロセッサを更に備えた、付記13又は14記載の記憶装置。

(付記16)

前記第1のメモリは、前記鍵の初期値を保持すると共に、保持する前記鍵の初期値を前記第1のセレクタへ出力するメモリと、前記フラグを保持すると共に、保持する前記フラグを前記比較回路へ出力するメモリを有する、付記13乃至15のいずれか1項記載の記憶装置。

(付記17)

前記命令を発行すると共に、鍵の初期値と対応するフラグの対を複数第3のメモリに設定するプロセッサと、

前記プロセッサが発行する鍵選択信号に基づいて鍵の初期値と対応するフラグの対を1つ前記第1のメモリに設定する第2のセレクタを更に備えた、付記13又は14記載の記憶装置。

(付記18)

前記第2のメモリに保持された前記第1の拡張鍵〜前記第Nの拡張鍵によりデータを暗号化すると共に、前記第2のメモリに保持された前記第Nの拡張鍵〜前記第1の拡張鍵によりデータを復号化するAES(Advanced Encryption Standard)方式のエンジンを更に備えた、付記13乃至17のいずれか1項記載の記憶装置。

(付記19)

前記比較回路での比較結果が不一致であると、前記第1のメモリに保存されている鍵の初期値を前記第2のメモリに設定し、前記暗号化用拡張計算部又は前記復号化用拡張計算部において鍵拡張を行って得られた前記第2のメモリ内の鍵の初期値を前記第1のメモリに設定し、前記第1のメモリに設定された鍵の初期値に対応するフラグを前記第1のメモリに設定することで前記第1のメモリの内容を更新する、付記15又は17記載の記憶装置。

(付記20)

1つの暗号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用する暗号化及び復号化装置であって、

鍵の初期値と対応するフラグを保持する第1のメモリと、

命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に暗号化に関するもので前記命令が暗号化命令であり前記フラグが暗号鍵を示すか、或いは、共に復号化に関するもので前記命令が復号化命令であり前記フラグが復号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、

第2のメモリと、

前記比較結果信号が入力されると、前記命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する暗号化用拡張計算部と、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する復号化用拡張計算部を備え、

前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記暗号化命令に基づいて前記暗号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張すると共に、前記復号化命令に基づいて前記復号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記復号鍵を第Nの拡張鍵〜第1の拡張鍵の順に拡張する、暗号化及び復号化装置。

以上、本発明を実施例により説明したが、本発明は上記実施例に限定されるものではなく、本発明の範囲内で種々の変形及び改良が可能であることは言うまでもない。

20 CPU

21,22,25,31,33 メモリ

23 比較回路

24,32 セレクタ

26 暗号化用拡張計算部

27 復号化用拡張計算部

28 鍵拡張計算回路

29 トリガ信号生成回路

34 鍵拡張ブロック

35 AESエンジン

36 ヘッド

37 ディスク

100 コントロール回路

101 命令保持メモリ

102 処理ブロック数カウンタ

103 内部命令生成回路

104 鍵拡張ラウンドカウンタ

21,22,25,31,33 メモリ

23 比較回路

24,32 セレクタ

26 暗号化用拡張計算部

27 復号化用拡張計算部

28 鍵拡張計算回路

29 トリガ信号生成回路

34 鍵拡張ブロック

35 AESエンジン

36 ヘッド

37 ディスク

100 コントロール回路

101 命令保持メモリ

102 処理ブロック数カウンタ

103 内部命令生成回路

104 鍵拡張ラウンドカウンタ

Claims (6)

- 1つの暗号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用する暗号化装置であって、

鍵の初期値と対応するフラグを保持する第1のメモリと、

命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に暗号化に関するもので、前記命令が暗号化命令であり前記フラグが暗号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、

第2のメモリと、

前記比較結果信号が入力されると、前記暗号化命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する暗号化用拡張計算部を備え、

前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記暗号化命令に基づいて前記暗号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張する、暗号化装置。 - 1つの復号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用する復号化装置であって、

鍵の初期値と対応するフラグを保持する第1のメモリと、

命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に復号化に関するもので、前記命令が復号化命令であり前記フラグが復号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、

第2のメモリと、

前記比較結果信号が入力されると、前記復号化命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する復号化用拡張計算部を備え、

前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記復号化命令に基づいて前記復号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第Nの拡張鍵〜第1の拡張鍵の順に拡張する、復号化装置。 - データを記憶装置に記録し、前記記憶装置からデータを再生する制御を行う制御部と、

1つの暗号鍵を拡張して得られるN(Nは2以上の自然数)個の拡張鍵を順次データ処理に使用し、前記記憶装置に記録するデータを暗号化し、前記記憶装置から再生されたデータを復号化する暗号化及び復号化装置を備え、

前記暗号化及び復号化装置は、

鍵の初期値と対応するフラグを保持する第1のメモリと、

命令と、前記第1のメモリに保持された前記フラグが示す鍵が共に暗号化に関するもので前記命令が暗号化命令であり前記フラグが暗号鍵を示すか、或いは、共に復号化に関するもので前記命令が復号化命令であり前記フラグが復号鍵を示すと、比較結果が一致することを示す比較結果信号を出力する比較回路と、

第2のメモリと、

前記比較結果信号が入力されると、前記命令及びトリガ信号に基づいて前記第1のメモリに保持された前記鍵を初期値として前記第2のメモリにロードする第1のセレクタと、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する暗号化用拡張計算部と、

前記第2のメモリに保持された鍵に基づいて順次拡張鍵を計算して前記第1のセレクタに入力する復号化用拡張計算部を有し、

前記第1のセレクタは、前記第2のメモリへ鍵の初期値をロードする時以外は、前記暗号化命令に基づいて前記暗号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記暗号鍵を第1の拡張鍵〜第Nの拡張鍵の順に拡張すると共に、前記復号化命令に基づいて前記復号化用拡張計算部で計算された拡張鍵を前記第2のメモリにロードすることで前記復号鍵を第Nの拡張鍵〜第1の拡張鍵の順に拡張する、記憶装置。 - 前記暗号化及び復号化装置は、前記比較結果信号に基づいて前記トリガ信号を生成するトリガ信号生成回路を更に有する、請求項3記載の記憶装置。

- 前記命令を発行すると共に、鍵の初期値と対応するフラグの対を複数第3のメモリに設定するプロセッサと、

前記プロセッサが発行する鍵選択信号に基づいて鍵の初期値と対応するフラグの対を1つ前記第1のメモリに設定する第2のセレクタを更に備えた、請求項3又は4記載の記憶装置。 - 前記比較回路での比較結果が不一致であると、前記第1のメモリに保存されている鍵の初期値を前記第2のメモリに設定し、前記暗号化用拡張計算部又は前記復号化用拡張計算部において鍵拡張を行って得られた前記第2のメモリ内の鍵の初期値を前記第1のメモリに設定し、前記第1のメモリに設定された鍵の初期値に対応するフラグを前記第1のメモリに設定することで前記第1のメモリの内容を更新する、請求項5記載の記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009029022A JP2010185982A (ja) | 2009-02-10 | 2009-02-10 | 暗号化装置、復号化装置及び記憶装置 |

| US12/702,184 US20100202608A1 (en) | 2009-02-10 | 2010-02-08 | Encryption device, decryption device, and storage device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009029022A JP2010185982A (ja) | 2009-02-10 | 2009-02-10 | 暗号化装置、復号化装置及び記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010185982A true JP2010185982A (ja) | 2010-08-26 |

| JP2010185982A5 JP2010185982A5 (ja) | 2010-10-28 |

Family

ID=42540443

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009029022A Pending JP2010185982A (ja) | 2009-02-10 | 2009-02-10 | 暗号化装置、復号化装置及び記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20100202608A1 (ja) |

| JP (1) | JP2010185982A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012168274A (ja) * | 2011-02-10 | 2012-09-06 | Dainippon Printing Co Ltd | 暗号化方法、復号方法、暗号化装置、復号装置及び暗号化/復号システム |

| KR101593160B1 (ko) * | 2014-04-22 | 2016-02-15 | 한국전자통신연구원 | 트리거 신호 생성 장치 및 그 방법 |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9779220B1 (en) * | 2012-09-28 | 2017-10-03 | EMC IP Holding Company LLC | Obscuring data using on-the-fly retokenizable tokens |

| US9787470B2 (en) * | 2013-12-12 | 2017-10-10 | Samsung Electronics Co., Ltd. | Method and apparatus of joint security advanced LDPC cryptcoding |

| KR102227263B1 (ko) * | 2013-12-31 | 2021-03-15 | 삼성전자주식회사 | 보안 부트 변경 변경시스템, 방법 및 이 변경시스템을 구비한 전자장치 |

| US10050645B2 (en) * | 2014-01-30 | 2018-08-14 | Hewlett Packard Enterprise Development Lp | Joint encryption and error correction encoding |

| KR102541321B1 (ko) * | 2014-07-11 | 2023-06-08 | 삼성전자주식회사 | 공동 보안 어드벤스드 ldpc 암호화 코딩 방법 및 장치 |

| KR102376506B1 (ko) * | 2014-10-20 | 2022-03-18 | 삼성전자주식회사 | 암복호화기, 암복호화기를 포함하는 전자 장치 및 암복호화기의 동작 방법 |

| US9774443B2 (en) * | 2015-03-04 | 2017-09-26 | Apple Inc. | Computing key-schedules of the AES for use in white boxes |

| CN108777611B (zh) * | 2018-05-11 | 2021-06-18 | 吉林大学 | 基于双密钥流密码的双向链表顺序加密解密方法 |

| JP7034870B2 (ja) * | 2018-09-19 | 2022-03-14 | 株式会社東芝 | 認証装置 |

| US11689361B1 (en) * | 2020-11-09 | 2023-06-27 | Xilinx, Inc. | Distributed key expansion |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10229361A (ja) * | 1996-12-06 | 1998-08-25 | Korea Electron Telecommun | オン−ボード遠隔命令装置 |

| JP2000332743A (ja) * | 1999-05-18 | 2000-11-30 | Sony Corp | 受信装置および方法、並びに媒体 |

| JP2001077805A (ja) * | 1999-04-07 | 2001-03-23 | Sony Corp | セキュリティ装置、メモリ装置、データ処理装置および方法 |

| JP2003085155A (ja) * | 2001-09-12 | 2003-03-20 | Sony Corp | データ処理装置 |

| JP2003288009A (ja) * | 2002-03-28 | 2003-10-10 | Seiko Epson Corp | 暗号装置及びデータ転送制御装置 |

| JP2005099984A (ja) * | 2003-09-24 | 2005-04-14 | Toshiba Corp | オンチップマルチコア型耐タンパプロセッサ |

| JP2005109869A (ja) * | 2003-09-30 | 2005-04-21 | Matsushita Electric Ind Co Ltd | 暗号鍵管理方法 |

| JP2006171598A (ja) * | 2004-12-20 | 2006-06-29 | Matsushita Electric Ind Co Ltd | Aesの並列暗復号処理装置 |

| JP2006527412A (ja) * | 2003-06-12 | 2006-11-30 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | データを暗号化および/または復号化するプロセッサとこのプロセッサを使用してデータを暗号化および/または復号化する方法 |

| JP2007333854A (ja) * | 2006-06-13 | 2007-12-27 | New Japan Radio Co Ltd | 乱数発生回路 |

-

2009

- 2009-02-10 JP JP2009029022A patent/JP2010185982A/ja active Pending

-

2010

- 2010-02-08 US US12/702,184 patent/US20100202608A1/en not_active Abandoned

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10229361A (ja) * | 1996-12-06 | 1998-08-25 | Korea Electron Telecommun | オン−ボード遠隔命令装置 |

| JP2001077805A (ja) * | 1999-04-07 | 2001-03-23 | Sony Corp | セキュリティ装置、メモリ装置、データ処理装置および方法 |

| JP2000332743A (ja) * | 1999-05-18 | 2000-11-30 | Sony Corp | 受信装置および方法、並びに媒体 |

| JP2003085155A (ja) * | 2001-09-12 | 2003-03-20 | Sony Corp | データ処理装置 |

| JP2003288009A (ja) * | 2002-03-28 | 2003-10-10 | Seiko Epson Corp | 暗号装置及びデータ転送制御装置 |

| JP2006527412A (ja) * | 2003-06-12 | 2006-11-30 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | データを暗号化および/または復号化するプロセッサとこのプロセッサを使用してデータを暗号化および/または復号化する方法 |

| JP2005099984A (ja) * | 2003-09-24 | 2005-04-14 | Toshiba Corp | オンチップマルチコア型耐タンパプロセッサ |

| JP2005109869A (ja) * | 2003-09-30 | 2005-04-21 | Matsushita Electric Ind Co Ltd | 暗号鍵管理方法 |

| JP2006171598A (ja) * | 2004-12-20 | 2006-06-29 | Matsushita Electric Ind Co Ltd | Aesの並列暗復号処理装置 |

| JP2007333854A (ja) * | 2006-06-13 | 2007-12-27 | New Japan Radio Co Ltd | 乱数発生回路 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012168274A (ja) * | 2011-02-10 | 2012-09-06 | Dainippon Printing Co Ltd | 暗号化方法、復号方法、暗号化装置、復号装置及び暗号化/復号システム |

| KR101593160B1 (ko) * | 2014-04-22 | 2016-02-15 | 한국전자통신연구원 | 트리거 신호 생성 장치 및 그 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100202608A1 (en) | 2010-08-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2010185982A (ja) | 暗号化装置、復号化装置及び記憶装置 | |

| US11563556B2 (en) | Architecture and instruction set for implementing advanced encryption standard (AES) | |

| US8942374B2 (en) | Encryption device | |

| US20110311048A1 (en) | Cryptographic operation apparatus, storage apparatus, and cryptographic operation method | |

| US20160261406A1 (en) | Performing AES Encryption Or Decryption In Multiple Modes With A Single Instruction | |

| JP2008058831A (ja) | 暗号処理装置、および暗号処理方法、並びにコンピュータ・プログラム | |

| US20120069993A1 (en) | Cryptographic apparatus and memory system | |

| CN116488794B (zh) | 基于fpga的高速sm4密码模组实现方法及装置 | |

| US8995666B2 (en) | Key scheduling device and key scheduling method | |

| US20150058639A1 (en) | Encryption processing device and storage device | |

| US20100027781A1 (en) | Method and apparatus for enhancing performance of data encryption standard (des) encryption/decryption | |

| US7386124B2 (en) | Block encoding method and block encoding/decoding circuit | |

| JP2010129128A (ja) | 記憶装置及びデータ書き込み方法 | |

| Noi | Implementation of XTS-GOST 28147-89 with Pipeline Structure on FPGA | |

| JPH08163120A (ja) | 暗号化回路 | |

| JP2008283463A (ja) | 暗号処理装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100914 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100914 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110111 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110628 |