JP2010141079A - Method of manufacturing semiconductor device - Google Patents

Method of manufacturing semiconductor device Download PDFInfo

- Publication number

- JP2010141079A JP2010141079A JP2008315297A JP2008315297A JP2010141079A JP 2010141079 A JP2010141079 A JP 2010141079A JP 2008315297 A JP2008315297 A JP 2008315297A JP 2008315297 A JP2008315297 A JP 2008315297A JP 2010141079 A JP2010141079 A JP 2010141079A

- Authority

- JP

- Japan

- Prior art keywords

- film

- single crystal

- gas

- constituent element

- crystal silicon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/24—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials using chemical vapour deposition [CVD]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/201—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates the substrates comprising an insulating layer on a semiconductor body, e.g. SOI

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D88/00—Three-dimensional [3D] integrated devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D88/00—Three-dimensional [3D] integrated devices

- H10D88/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/27—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials using selective deposition, e.g. simultaneous growth of monocrystalline and non-monocrystalline semiconductor materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/34—Deposited materials, e.g. layers

- H10P14/3402—Deposited materials, e.g. layers characterised by the chemical composition

- H10P14/3404—Deposited materials, e.g. layers characterised by the chemical composition being Group IVA materials

- H10P14/3411—Silicon, silicon germanium or germanium

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P72/00—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof

- H10P72/30—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for conveying, e.g. between different workstations

- H10P72/33—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for conveying, e.g. between different workstations into and out of processing chamber

- H10P72/3312—Vertical transfer of a batch of workpieces

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/38—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials characterised by treatments done after the formation of the materials

- H10P14/3802—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

Landscapes

- Recrystallisation Techniques (AREA)

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

【課題】横方向固相エピタキシャル成長法において単結晶膜成膜工程に要する時間を短縮し、半導体装置の製造を短時間で行う。

【解決手段】単結晶シリコン部403及び絶縁膜401が表面において露出したウエハ200を、構成元素としてSiを含むガスの雰囲気中に曝露し、単結晶シリコン部403及び絶縁膜401の上にアモルファスのシリコン膜402を成膜する成膜工程と、成膜工程後に、シリコン膜402を加熱して、単結晶シリコン部403を基にしてシリコン膜402を単結晶化させる加熱工程と、加熱工程後に、ウエハ200を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、単結晶化した部分を残留させつつ、単結晶化しなかった部分を除去する選択成長工程と、を含む半導体装置の製造方法であって、ウエハ200に対して、成膜工程、加熱工程及び選択成長工程を繰り返す。

【選択図】図4In a lateral solid phase epitaxial growth method, a time required for a single crystal film forming step is reduced, and a semiconductor device is manufactured in a short time.

A wafer 200 having a single crystal silicon portion 403 and an insulating film 401 exposed on the surface is exposed to a gas atmosphere containing Si as a constituent element, and an amorphous material is formed on the single crystal silicon portion 403 and the insulating film 401. A film forming process for forming the silicon film 402, a heating process for heating the silicon film 402 after the film forming process to single-crystallize the silicon film 402 based on the single crystal silicon portion 403, and a heating process, A selective growth step in which the wafer 200 is exposed to a mixed atmosphere of a gas containing Si as a constituent element and a gas containing Cl as a constituent element, and the portion that has not been single-crystallized is removed while the single-crystallized portion remains; In which the film forming process, the heating process, and the selective growth process are repeated for the wafer 200.

[Selection] Figure 4

Description

本発明は、半導体装置の製造方法に関する。 The present invention relates to a method for manufacturing a semiconductor device.

SOI(Silicon on Insulator)構造を用いたLSI(Large Scale Integration)が盛んに研究されている。これは寄生容量の低減による動作速度の高速化や、素子間分離が簡単なため高集積化しやすい等の利点があるためである。

SOI構造を形成する方法として、SIMOX(Separation by Implanted Oxygen)に代表される表面単結晶分離法が有名である。これは表面単結晶シリコン層を保存しつつ内部に絶縁膜を形成する方法である。

ここで、SOI構造を形成する方法として、横方向固相エピタキシャル成長法が注目され始めている。これは表面の一部又は全部に絶縁膜を形成したシリコン基板を用いて、絶縁膜上の横方向エピタキシャル成長により単結晶シリコン膜を形成する方法である。その方法としては、(1)部分的に絶縁膜を形成したシリコン基板上にアモルファスのシリコンを成膜する、(2)約500〜700℃で熱処理すると、シリコン開口部を種として絶縁膜上のアモルファスシリコンが単結晶化していく、(3)長時間熱処理することで絶縁膜上のアモルファスシリコンが全て単結晶化する、というものである。

この方法によると絶縁膜の表面全体に単結晶シリコン膜が形成するので、さらにその上にも同様の繰り返しにより3次元的に回路を集積化することが可能となり、構造設計の自由度が増す利点がある。

LSI (Large Scale Integration) using an SOI (Silicon on Insulator) structure has been actively studied. This is because there are advantages such as an increase in operation speed due to reduction of parasitic capacitance and easy integration due to simple isolation between elements.

As a method for forming an SOI structure, a surface single crystal separation method represented by SIMOX (Separation by Implanted Oxygen) is well known. This is a method of forming an insulating film inside while preserving the surface single crystal silicon layer.

Here, as a method for forming an SOI structure, a lateral solid phase epitaxial growth method has begun to attract attention. This is a method of forming a single crystal silicon film by lateral epitaxial growth on an insulating film using a silicon substrate having an insulating film formed on part or all of the surface. (1) Amorphous silicon is formed on a silicon substrate partially formed with an insulating film. (2) When heat treatment is performed at about 500 to 700 ° C., the silicon opening is used as a seed on the insulating film. Amorphous silicon is single-crystallized. (3) The amorphous silicon on the insulating film is all single-crystallized by heat treatment for a long time.

According to this method, since the single crystal silicon film is formed on the entire surface of the insulating film, it is possible to integrate the circuit three-dimensionally by repeating the same on the surface, and the advantage of increasing the degree of freedom in structural design. There is.

しかし上記(1)の工程を高温で行うと、アモルファスシリコン膜と絶縁膜との界面に微結晶粒が形成され、これによりアモルファスシリコンが単結晶化せず多結晶化してしまう。そこで、微結晶粒を形成させないためには上記(1)の工程を低温で行う必要があるが、低温で処理するとアモルファスシリコンの成膜速度が遅くなり、半導体装置の製造にかかる時間が長くなるという問題がある。 However, when the step (1) is performed at a high temperature, fine crystal grains are formed at the interface between the amorphous silicon film and the insulating film, and the amorphous silicon is not single-crystallized but polycrystallized. Therefore, in order not to form microcrystal grains, it is necessary to perform the step (1) at a low temperature. However, if the processing is performed at a low temperature, the film formation rate of amorphous silicon is slowed down, and the time required for manufacturing the semiconductor device is increased. There is a problem.

そこで本発明の課題は、横方向選択エピタキシャル成長法を用いて、単結晶化のための熱処理の際に多結晶となってしまった部分のみを除去し、再度アモルファスシリコン成膜及び熱処理を実施することにより基板上に形成された絶縁膜を単結晶膜により短時間で覆えるようにすることである。 Therefore, an object of the present invention is to remove only the portion that has become polycrystalline during the heat treatment for single crystallization by using the lateral selective epitaxial growth method, and perform amorphous silicon film formation and heat treatment again. Thus, the insulating film formed on the substrate can be covered with the single crystal film in a short time.

以上の課題を解決するために、本発明によれば、

単結晶シリコン部及び絶縁部が表面において露出した複数の基板を所定の間隔で積層状に保持し、構成元素としてSiを含むガスの雰囲気中に曝露し、前記単結晶シリコン部及び前記絶縁部の上にアモルファスのシリコン膜を成膜する成膜工程と、

前記成膜工程後に、前記シリコン膜を加熱して、前記単結晶シリコン部を基にして前記アモルファスのシリコン膜を単結晶化させる加熱工程と、

前記加熱工程後に、前記基板を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、前記単結晶化した部分を残留させつつ、前記絶縁部の上の単結晶化しなかった部分を除去する選択成長工程と、を含み、

前記基板に対して、前記成膜工程、前記加熱工程及び前記選択成長工程を繰り返すことを特徴とする半導体装置の製造方法が提供される。

In order to solve the above problems, according to the present invention,

A plurality of substrates in which the single crystal silicon part and the insulating part are exposed on the surface are held in a laminated form at a predetermined interval, and are exposed to a gas atmosphere containing Si as a constituent element, and the single crystal silicon part and the insulating part A film forming process for forming an amorphous silicon film on the surface;

A heating step of heating the silicon film after the film forming step to single crystallize the amorphous silicon film based on the single crystal silicon portion;

After the heating step, the substrate is exposed to a mixed atmosphere of a gas containing Si as a constituent element and a gas containing Cl as a constituent element, and the single crystal on the insulating portion is left while the single crystallized portion remains. And a selective growth step for removing a portion that has not been converted,

There is provided a method for manufacturing a semiconductor device, wherein the film forming step, the heating step, and the selective growth step are repeated for the substrate.

本発明によれば、成膜工程で微結晶粒が形成され、加熱工程で多結晶膜が成長しても、その後の選択成長工程で単結晶部以外の多結晶シリコン等を除去できる。これにより成膜工程を高温で行うことができるため成膜速度が向上し、半導体装置の製造を短時間で行うことができる。 According to the present invention, even if microcrystalline grains are formed in the film forming process and the polycrystalline film is grown in the heating process, polycrystalline silicon other than the single crystal portion can be removed in the subsequent selective growth process. Accordingly, since the film formation process can be performed at a high temperature, the film formation speed is improved, and the semiconductor device can be manufactured in a short time.

発明者等は、減圧CVD装置を用い、基板表面に単結晶シリコンを選択成長させる方法について以下に示す特性を発見した。

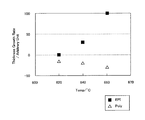

単結晶シリコン部及び多結晶シリコン部が表面において露出した基板を収容した処理室を620〜660℃の温度範囲に設定し、希釈ガスとともに構成元素としてSiを含むガスを全流量に対し4%、構成元素としてClを含むガスを全流量に対し1%導入することで、多結晶シリコン部のみを除去することができる。多結晶シリコン部は当該温度範囲内で高温にする程エッチング量を大きくすることができ、単結晶シリコン部については当該温度範囲内において温度を高くするほど膜が厚く成長する。この性質を示したグラフを図1に示している。図1は、処理室内の温度が620,640,660℃の場合のそれぞれにおける、単結晶シリコン膜及び多結晶シリコン膜の膜厚成長速度の値をプロットした図である。また、図1は構成元素としてSiを含むガスとしてSiH4(例えば40sccm)、構成元素としてClを含むガスとしてCl2(例えば10sccm)、希釈ガスとしてH2(例えば1000sccm)を用いた場合の図である。横軸は処理室内の温度(℃)を示しており、縦軸は成長速度(任意単位)を示している。また、黒のプロットは単結晶シリコン膜の成長速度、白のプロットは多結晶シリコン膜の成長速度を示している。

処理温度が620℃であるとき、単結晶膜の成長速度の値はゼロ、多結晶膜の成長速度の値はマイナスを示している。成長速度がゼロのときは膜厚に変化がないことを示しており、成長速度の値がマイナスのときは膜がエッチングされたことを示している。処理温度が640℃であると、単結晶シリコン膜は露出Si基板の開口部により厚く成長し、Si開口部以外の絶縁膜上への多結晶シリコン膜のエッチング量はより大きくなっている。処理温度が660℃であると、単結晶シリコン膜の成長速度は更に向上し、多結晶シリコン膜のエッチング量は更に大きくなる。従って、620〜660℃の温度範囲内では、多結晶シリコン膜がマイナス成長であり、設定温度が高くなるにつれて単結晶シリコン膜の成長速度が漸増するとともに多結晶シリコン膜の膜厚が漸減する。従って、この特性を利用して単結晶シリコン膜を選択成長させることができる。なお、シリコンゲルマニウムについても同様と推測される。

The inventors have discovered the following characteristics of a method for selectively growing single crystal silicon on a substrate surface using a low pressure CVD apparatus.

A processing chamber containing a substrate having a single crystal silicon portion and a polycrystalline silicon portion exposed on the surface is set to a temperature range of 620 to 660 ° C., and a gas containing Si as a constituent element together with a dilution gas is 4% of the total flow rate, By introducing a gas containing Cl as a constituent element at 1% with respect to the total flow rate, only the polycrystalline silicon portion can be removed. The etching amount of the polycrystalline silicon part can be increased as the temperature is increased within the temperature range, and the film grows thicker as the temperature is increased within the temperature range of the single crystal silicon part. A graph showing this property is shown in FIG. FIG. 1 is a graph plotting the values of the film growth rate of the single crystal silicon film and the polycrystalline silicon film when the temperature in the processing chamber is 620, 640, and 660 ° C., respectively. Also, SiH 4 (e.g. 40 sccm) as the gas 1 containing Si as a constituent element, Cl 2 as the gas containing Cl as a constituent element (e.g. 10 sccm), illustrates a case of using the H 2 (e.g., 1000 sccm) as a diluent gas It is. The horizontal axis indicates the temperature (° C.) in the processing chamber, and the vertical axis indicates the growth rate (arbitrary unit). The black plot indicates the growth rate of the single crystal silicon film, and the white plot indicates the growth rate of the polycrystalline silicon film.

When the processing temperature is 620 ° C., the growth rate value of the single crystal film is zero, and the growth rate value of the polycrystalline film is negative. When the growth rate is zero, it indicates that there is no change in the film thickness, and when the value of the growth rate is negative, it indicates that the film is etched. When the processing temperature is 640 ° C., the single crystal silicon film grows thicker through the opening of the exposed Si substrate, and the etching amount of the polycrystalline silicon film on the insulating film other than the Si opening is larger. When the processing temperature is 660 ° C., the growth rate of the single crystal silicon film is further improved, and the etching amount of the polycrystalline silicon film is further increased. Therefore, within the temperature range of 620 to 660 ° C., the polycrystalline silicon film is negatively grown. As the set temperature increases, the growth rate of the single crystal silicon film gradually increases and the thickness of the polycrystalline silicon film gradually decreases. Therefore, a single crystal silicon film can be selectively grown using this characteristic. The same applies to silicon germanium.

以下、図面を参照しながら上述の特性を利用した実施形態について詳細に説明する。 Hereinafter, embodiments using the above-described characteristics will be described in detail with reference to the drawings.

<第1の実施の形態>

本発明の第1の実施の形態について説明する。

<First Embodiment>

A first embodiment of the present invention will be described.

本実施形態に係る基板処理装置は、半導体装置集積回路(IC(Integrated Circuits))の製造に使用される半導体製造装置の一例として構成されているものである。下記の説明では、基板処理装置の一例として、基板に対し熱処理等を行う縦型の装置を使用した場合について述べる。 The substrate processing apparatus according to the present embodiment is configured as an example of a semiconductor manufacturing apparatus used for manufacturing a semiconductor device integrated circuit (IC (Integrated Circuits)). In the following description, a case where a vertical apparatus that performs heat treatment or the like on a substrate is used as an example of the substrate processing apparatus will be described.

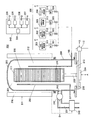

図2は、本発明の実施形態における基板処理装置101の概略構成図である。

FIG. 2 is a schematic configuration diagram of the

図2に示す通り基板処理装置101は、ガス供給系300、移載機106、カセット110、処理炉202、ボート217、コントローラ240、真空排気装置246及びロードロック室140等を備える。

As shown in FIG. 2, the

基板処理装置101内には複数のカセット110が収容されており、カセット110は、複数のウエハ200を水平姿勢に整列させた状態で保持している。ウエハ200は、円盤状に形成されている。

A plurality of

移載機106は、ウエハ200をカセット110からボート217へ移載したり、ボート217からカセット110へ移載したりするためのものであり、ウエハ200をピックアップすることができるように構成されている。即ち、移載機106はウエハ200をボート217に対し装填(ウエハチャージング)及び脱装(ウエハディスチャージング)が可能となっている。ボート217は、成膜処理開始前は処理炉202の真下に位置するロードロック室140内に収容されている。ロードロック室140の側壁には蓋141が設けられ、移載機106は蓋141を介してウエハチャージング及びウエハディスチャージングを行う。

The

処理炉202はヒータ206及びアウターチューブ205等を有する。アウターチューブ205の周囲にヒータ206が設けられており、アウターチューブ205を加熱することができるようになっている。更に処理炉202には、各種処理ガスを供給するガス供給系300及び内部を真空排気する真空排気装置246が接続されている。処理炉202の詳細については後述する。

The

コントローラ240は基板処理装置101の各種動作を制御する。

The

図3は、基板処理装置101の処理炉202の概略構成図であり、縦断面図として示されている。なお、図3はウエハ200及びボート217が処理室201内に搬入された後の図である。図3を参照して処理炉202について説明する。

FIG. 3 is a schematic configuration diagram of the

図2でも示したように、処理炉202は加熱機構としてのヒータ206を有する。ヒータ206は円筒形状であり、ヒータ素線とその周囲に設けられた断熱材より構成され、図示しない保持体に支持されることにより垂直に据え付けられている。

As shown in FIG. 2, the

ヒータ206の内側には、ヒータ206と同心円状にアウターチューブ205が配設されている。アウターチューブ205は、石英(SiO2)、炭化シリコン(SiC)その他の耐熱性材料からなる。アウターチューブ205は円筒形状に形成されており、アウターチューブ205の上端が閉塞し、下端が開口している。

An

アウターチューブ205の下方には、マニホールド209が設けられている。マニホールド209はステンレスその他の金属材料からなる。マニホールド209が円筒形状に設けられ、マニホールド209の上端及び下端が開口している。

マニホールド209の径がアウターチューブ205の径に等しく、マニホールド209の上端がアウターチューブ205の下端に連結され、アウターチューブ205がマニホールド209に支持されている。マニホールド209とアウターチューブ205との間にはシール部材としてのOリングが設けられている。マニホールド209が図示しない保持体に支持されることにより、アウターチューブ205は垂直に据え付けられた状態となっている。

A manifold 209 is provided below the

The diameter of the manifold 209 is equal to the diameter of the

アウターチューブ205とマニホールド209により反応容器が形成されている。そして、反応容器内の処理室201が、アウターチューブ205の中空212と、マニホールド209の中空であってアウターチューブ205とマニホールド209の接続部分よりも下側の下部空間213とに分けられる。

A reaction vessel is formed by the

マニホールド209の下方には、マニホールド209の下端開口を気密に閉塞可能な炉口蓋体としてのシールキャップ219が設けられている。シールキャップ219はステンレスその他の金属からなり、円盤状に形成されている。シールキャップ219の上面には、マニホールド209の下端と当接するシール部材としてのOリングが設けられている。シールキャップ219には、回転機構254が設けられている。回転機構254の回転軸255はシールキャップ219を貫通してボート217に接続されている。回転機構254は、ボート217を回転させることでウエハ200を回転させるように構成されている。シールキャップ219は、処理炉202の外側に設けられた昇降機構としての図示しない昇降モータ248によって垂直方向に昇降される。これによりボート217を処理室201に対し搬入搬出することが可能となっている。回転機構254及びボートエレベータ115には、駆動制御部237が電気的に接続されており、所望の動作をするよう所望のタイミングにて制御するように構成されている。

Below the manifold 209, a

基板保持具としてのボート217は、石英、炭化シリコンその他の耐熱性材料からなり、複数枚(例えば50〜150枚程度)のウエハ200を水平姿勢でかつ互いに中心を揃えた状態で整列させて多段に保持するように構成されている。なおボート217の下部には、石英、炭化シリコンその他の耐熱性材料からなる円板形状をした断熱部材としての断熱板216が水平姿勢で多段に複数枚配置されており、ヒータ206からの熱がマニホールド209側に伝わりにくくなるよう構成されている。

A

また、アウターチューブ205の内部には温度センサ263が設けられている。

ヒータ206と温度センサ263には、電気的に温度制御部238が接続されており、温度センサ263により検出された温度情報に基づきヒータ206への通電具合を調整することにより処理室201内の温度が所望の温度分布となるよう所望のタイミングにて制御するように構成されている。

A

A

ガス供給管165がマニホールド209に設けられている。ガス供給管165はマニホールド209の外からマニホールド209を貫通して、処理室201内まで配管されている。ガス供給管165の下流側端部がノズルになっている。

A

ガス供給管165の下流側端部が中空212内にある。ガス供給管165の上流側がバルブ321〜324に接続されている。バルブ321はMFC(マスフローコントローラ)311を介してSi系原料ガス供給源301に接続されている。同様に、バルブ322はMFC312を介してGe系原料ガス供給源302に接続されている。バルブ323はMFC313を介して希釈ガス供給源303に接続されている。バルブ324はMFC314を介してエッチングガス供給源304に接続されている。

The downstream end of the

Si系原料ガス供給源301には、モノシランガス(SiH4)、Si2H6、Si3H8、SiCl4、SiHCl3、SiH2Cl2その他の構成元素としてSiを含むガスが封入されている。Ge系原料ガス供給源302には、モノゲルマンガス(GeH4)、GeCl4その他の構成元素としてGeを含むガスが封入されている。希釈ガス供給源303には、水素ガス、ヘリウムガス、アルゴンガスその他の希釈ガスが封入されている。エッチングガス供給源304には、塩素ガス、塩化水素ガスその他の構成元素としてClを含むガスが封入されている。

A Si-based source

MFC311〜314は、それに流れるガスの流量を検出するとともに、流量を調節するガス流量制御装置である。

The

MFC311〜314及びバルブ321〜324にはガス流量制御部235が電気的に接続されており、供給するガスの流量が所望の流量となるよう所望のタイミングにて制御するように構成されている。

A gas flow

マニホールド209にガス排気管231が設けられ、このガス排気管231が下部空間213に通じている。ガス排気管231の下流側には、圧力検出器としての圧力センサ243及び圧力調整器としてのAPCバルブ242を介して、真空ポンプ等の真空排気装置246が接続されている。圧力センサ243及びAPCバルブ242には、圧力制御部236が電気的に接続されており、圧力センサ243により検出された圧力に基づいてAPCバルブ242の開度を調節することにより、処理室201内の圧力が所望の圧力となるように所望のタイミングにて制御するよう構成されている。

A

ガス流量制御部235、圧力制御部236、駆動制御部237、温度制御部238は、操作部、入出力部をも構成し、基板処理装置101全体を制御する主制御部239に電気的に接続されている。これら、ガス流量制御部235、圧力制御部236、駆動制御部237、温度制御部238、主制御部239は、コントローラ240として構成されている。

The gas flow

次に、上記構成に係る基板処理装置101の主な動作とともに、図2〜図4を参照して基板上への単結晶シリコン膜製造方法及び半導体装置の製造方法について説明する。図4はウエハ200の一部断面拡大図であり、ウエハ200の表面及び絶縁膜401が全て単結晶膜で覆われるまでの工程図である。

Next, together with main operations of the

工場内搬送装置(図示略)によって複数のカセット110が基板処理装置101内に搬入されると、移載機106はウエハ200をカセット110からボート217に装填(ウエハチャージング)する。ボート217にウエハ200を受け渡した移載機106は、カセット110に戻り後続のウエハ200をボート217に装填する。

ウエハ200は単結晶シリコンで構成され、その表面には絶縁膜401が部分的に形成されている。絶縁膜401の間には、ウエハ200の表面の一部が露出し、その露出した部分が単結晶シリコン部403である。

When a plurality of

The

予め指定された枚数のウエハ200がボート217に装填(ウエハチャージング)されると、コントローラ240が駆動制御部237によりボートエレベータ115を上昇動作させる。そうすると、ウエハ200群を保持したボート217がボートエレベータ115の上昇動作により処理炉202内に搬入(ボートローディング)され、マニホールド209の下端の開口がシールキャップ219によって閉塞される。そして、コントローラ240が駆動制御部237によりボートエレベータ115を作動させる。

When a predetermined number of

続いて、コントローラ240が圧力制御部236により真空排気装置246を動作させると、処理室201内が所望の圧力(真空度)となるように真空排気装置246によって真空排気される。この際、処理室201内の圧力は圧力センサ243で測定され、この測定された圧力に基づきAPCバルブ242がコントローラ240の圧力制御部236によりフィードバック制御される。

また、コントローラ240が温度制御部238によりヒータ206を発熱させると、処理室201内が所望の温度となるようにヒータ206によって加熱される。この際、処理室201内が530〜580℃となるように温度センサ263が検出した温度情報に基づきヒータ206への通電具合がコントローラ240の温度制御部238によってフィードバック制御される。

続いて、コントローラ240が駆動制御部237によって回転機構254の回転を開始させる。回転機構254により、ボート217が回転されることでウエハ200が回転される。

Subsequently, when the

Further, when the

Subsequently, the

そして、コントローラ240がガス流量制御部235によってMFC311,313の設定流量を所定の流量に設定した後、バルブ321,323を開く。そうすると、Si系原料ガス及び希釈ガスがガス供給管165を流通して処理室201内に導入され、ウエハ200がSi系原料ガス及び希釈ガスに曝露される。Si系原料ガスが処理室201内を通過する際にウエハ200と接触することによりウエハ200の表面にアモルファスのシリコン膜402が堆積する。絶縁膜401を含むウエハ200の表面全体がアモルファスのシリコン膜402で覆われる(成膜工程a)。

予め設定された時間が経過すると、コントローラ240はバルブ321,323を閉じる。

Then, after the

When a preset time has elapsed, the

コントローラ240は温度制御部238によって、ヒータ206の設定温度を500〜700℃に設定し、温度センサ263が検出した温度情報に基づきヒータ206への通電具合がコントローラ240の温度制御部238によってフィードバック制御される。このヒータ206の昇温処理により処理室201が加熱されるとともに、ウエハ200及びアモルファスのシリコン膜402が加熱される。アモルファスのシリコン膜402が加熱されると、アモルファスのシリコン膜402が多結晶化する。ところが、アモルファスのシリコン膜402はウエハ200の単結晶構造を種として単結晶シリコン部403に重なった部分から単結晶化していく。そのため、単結晶化した部分(以下、単結晶化部)404は絶縁膜401の縁を越えて絶縁膜401の上にも広がり(横方向エピタキシャル成長)、多結晶化した部分(以下、多結晶化部)405が絶縁膜401の中央部にある(加熱工程b)。

これにより、絶縁膜401の縁部分の一部が単結晶化部404で覆われる。

The

Thereby, a part of the edge portion of the insulating

予め設定された時間が経過すると、コントローラ240はヒータ206の設定温度を620〜660℃に設定する。コントローラ240が温度センサ263による検出温度が620〜660℃に達したことを認識したら、MFC311の設定流量を全流量の4%となるよう設定し、MFC314の設定流量を全流量の1%となるよう設定し、MFC313の設定流量を全流量の95%となるように設定した後、バルブ321,323,324を開く。これによりSi系原料ガス、希釈ガス及びエッチングガスがガス供給管165を流通して処理室201内に導入され、ウエハ200がこれに曝露される。Si系原料ガス及びエッチングガスが処理室201内を通過する際にウエハ200の表面と接触することにより多結晶化部405がエッチングされ、単結晶化部404は残留したままである(選択成長工程c)。なお、選択成長工程において単結晶化部404が残留していれば、単結晶化部404が成長してもよい。

予め設定された時間が経過すると、コントローラ240はバルブ321〜324を閉じる。

When a preset time has elapsed, the

When a preset time has elapsed, the

以後、上述の成膜工程、加熱工程、選択成長工程を繰り返し(工程d〜h)、その繰り返しを絶縁膜401を含むウエハ200の表面全体が単結晶膜で覆われるまで行う(工程h)。

Thereafter, the above-described film formation process, heating process, and selective growth process are repeated (processes d to h), and the process is repeated until the entire surface of the

つまり、2回目の成膜工程において、再度Si系原料ガス及び希釈ガスを処理室201内に導入し、ウエハ200がSi系原料ガス及び希釈ガスに曝露されることでウエハ200の表面上にアモルファスのシリコン膜402が堆積する(工程d)。

That is, in the second film formation process, the Si-based source gas and the dilution gas are again introduced into the

2回目の加熱工程において、処理室201の温度を所定温度にし、ウエハ200を加熱すると、アモルファスのシリコン膜402の一部(絶縁膜401の上の部分)が多結晶化して多結晶化部405となる。1回目の成膜工程で形成された単結晶化部404と重なった部分は単結晶化部404を種として横方向エピタキシャル成長し、単結晶化部404が大きくなる。そのため、絶縁膜401の単結晶化部404に覆われた部分がさらに大きくなり、絶縁膜401の表面の一部分を除いてほぼ全体が単結晶化部404に覆われた状態となる(工程e)。

In the second heating step, when the temperature of the

2回目の選択成長工程において、処理室201の温度を所定温度にするとともに、Si系原料ガスを全流量の4%、エッチングガスを全流量の1%、希釈ガスを全流量の95%として処理室201内に導入し、ウエハ200をこれに曝露する。これにより単結晶化部404を残し多結晶化部405がエッチングされる(工程f)。

In the second selective growth step, the temperature of the

3回目の成膜工程において、Si系原料ガス及び希釈ガスを処理室201内に導入し、ウエハ200をこれに曝露することでアモルファスのシリコン膜402を堆積させる(工程g)。

In the third film formation process, Si-based source gas and dilution gas are introduced into the

3回目の加熱工程において、処理室内の温度を所定の温度にし、ウエハ200を加熱することで、アモルファスのシリコン膜402が単結晶化部404を種として単結晶化され、単結晶化部404が横方向エピタキシャル成長する。これにより絶縁膜401全体が単結晶化部404によって覆われる(工程h)。

In the third heating step, the temperature in the processing chamber is set to a predetermined temperature and the

絶縁膜401の全体が単結晶化部404によって覆われたら、コントローラ240はヒータ206による加熱を停止する。またコントローラ240は真空排気装置246を停止するとともに、不活性ガス供給源(図示略)から供給される不活性ガスを処理室201内に導入する。これにより、処理室201内が不活性ガスで置換されると共に、処理室201内の圧力が常圧に復帰される。

When the entire insulating

続いて、コントローラ240が駆動制御部237により回転機構254を停止させるとともにボートエレベータ115を下降動作させる。シールキャップ219及びボート217がボートエレベータ115の下降動作により下降されて、マニホールド209の下端が開口されるとともに、ウエハ200を保持したボート217が処理室201からロードロック室140に搬出(ボートアンローディング)される。続いて移載機106により、蓋141を介して処理済ウエハ200がボート217からカセット110に移載される。処理済ウエハ200が載置されたカセット110は、工場内搬送装置(図示略)によって基板処理装置101から取り出される。

Subsequently, the

なお、本実施形態は絶縁膜401上に単結晶シリコンを成長させる方法について示しているが、単結晶シリコンでなく単結晶シリコンゲルマニウムを成長させるものとしてもよい。その場合には、単結晶シリコンゲルマニウム部及び絶縁膜が露出したウエハを用い、Si系原料ガスと同時にGe系原料ガスを供給することにより単結晶シリコンゲルマニウムを成長させる。その場合には、ガス供給源としてGe系原料ガス供給源302を用い、供給流量をMFC312により調節し、バルブ322を介して処理室201内にゲルマンガスを導入する。

また、本実施形態では絶縁膜401を完全に単結晶化部404で覆うまでに、シリコン成膜工程を3回、加熱工程を3回、選択成長工程を2回行っているが、この回数に限らず、絶縁膜401の表面全体が単結晶化部404で覆われればこの回数より少なくてもよいし多くてもよい。この回数はデバイスのサイズにもよるが、1.5μm程度/回として全工程を2〜3回程度繰り返すことが好ましい。表面全体が単結晶で覆われることはさらなる表面へのパターン形成を行うために必要な技術である。

また、本実施形態のように全ての処理を同一の処理炉で行ってもよいが、成膜工程と、加熱工程及び選択成長処理は、反応炉を分けて実施してもよい。反応炉を分けると時間短縮になり、効率が良い。

Note that although this embodiment shows a method of growing single crystal silicon on the insulating

In this embodiment, the silicon film formation process is performed three times, the heating process is performed three times, and the selective growth process is performed twice until the insulating

Moreover, although all the processes may be performed in the same processing furnace as in the present embodiment, the film forming process, the heating process, and the selective growth process may be performed separately in the reaction furnace. Separation of reactors reduces time and increases efficiency.

以上に示された本発明の実施形態によれば、単結晶シリコンを成長させるとともに多結晶シリコンを除去するエピタキシャル選択成長を行うことができる。これにより、成膜工程及び加熱工程において生じた多結晶シリコン部を選択成長工程により除去できるので、高温でアモルファスシリコンの成膜処理を行うことができる。成膜処理を高温で行うことで、成膜処理における成膜速度が向上する。従って、半導体装置の製造にかかる時間を短縮化することができる。

また、各工程を複数回繰り返すことで基板表面全体に均一な膜厚で単結晶膜を形成することができると考えられ、単結晶膜上に積層状に回路パターンを形成することができる。

According to the embodiment of the present invention described above, it is possible to perform epitaxial selective growth in which single crystal silicon is grown and polycrystalline silicon is removed. Thereby, since the polycrystalline silicon portion generated in the film forming process and the heating process can be removed by the selective growth process, the amorphous silicon film forming process can be performed at a high temperature. By performing the film forming process at a high temperature, the film forming speed in the film forming process is improved. Therefore, the time required for manufacturing the semiconductor device can be shortened.

Further, it is considered that a single crystal film can be formed with a uniform film thickness on the entire substrate surface by repeating each step a plurality of times, and a circuit pattern can be formed in a laminated form on the single crystal film.

<第2の実施の形態>

次に、本発明の第2の実施の形態について説明する。

第2の実施形態においても第1の実施形態と同様の基板処理装置を使用する。

<Second Embodiment>

Next, a second embodiment of the present invention will be described.

Also in the second embodiment, the same substrate processing apparatus as in the first embodiment is used.

図5は半導体回路層を積層していく3次元LSI製造プロセスの工程図である。 FIG. 5 is a process diagram of a three-dimensional LSI manufacturing process in which semiconductor circuit layers are stacked.

回路基板420の最上層の半導体回路層430においては、単結晶のシリコン部423の一部にホウ素化合物、リン化合物その他ドープ材がドープされ、そのドープ部分がドレイン・ソース422となり、ドレイン・ソース422の間の部分の上に絶縁膜を介して半導体膜425がパターニングされ、更に、半導体膜425及びドレイン・ソース422の上にメタル421がパターニングされている。回路基板420は処理室201内に収容される。

工程iに示す回路基板420はメタル421及び単結晶シリコン部423の一部が表面に露出している。まず、この回路基板420のメタル421を覆うようにして絶縁膜426が形成される(工程j)。このとき単結晶シリコン部423の一部は絶縁膜426に覆われずに露出した状態のままである。従って回路基板420の表面には、絶縁膜426及び単結晶シリコン部423の一部のみが露出していることとなる。

In the uppermost

In the

処理室201を所定温度に設定するとともに、処理室201内にSi系原料ガス及び希釈ガスを導入し、回路基板420をこれに曝露する。そうすると、回路基板420の表面にアモルファスのシリコン膜427が形成する。アモルファスのシリコン膜427によって絶縁膜426及び単結晶シリコン部423が覆われる(工程k)。

While the

処理室201を所定温度に設定し、回路基板420を加熱処理すると、アモルファスのシリコン膜427が多結晶化し、多結晶化部429となる。一方、シリコン膜427の単結晶シリコン部423に重なった部分は横方向エピタキシャル成長し、単結晶化部428となる。そのため、単結晶化部428は絶縁膜426の一部を覆い、それ以外の部分を多結晶化部429が覆う(工程m)。

When the

処理室を所定の温度に設定するとともに、処理室201内にSi系原料ガス、希釈ガス及びエッチングガスを導入し、回路基板420をこれに曝露する。これにより単結晶化部404を残しつつ、多結晶化部429のみがエッチングされる(工程n)。

While the processing chamber is set to a predetermined temperature, Si-based source gas, dilution gas, and etching gas are introduced into the

2回目の成膜工程において、処理室201内を所定温度に設定した上で、処理室201内にSi系原料ガスを導入し、アモルファスのシリコン膜427を形成する。アモルファスのシリコン膜427は回路基板420の表面全体を覆う(工程p)。

In the second deposition step, the inside of the

2回目の加熱工程において、処理室201内を所定温度に設定し、回路基板420を加熱すると、アモルファスのシリコン膜427の一部が多結晶化し多結晶化部429となる(工程q)。アモルファスのシリコン膜427の一部は1回目の成膜工程で形成された単結晶化部428と重なった部分から横方向エピタキシャル成長し、単結晶化部428となる。よって単結晶化部428が絶縁膜426を覆う範囲が拡大し、それ以外の部分を多結晶化部429が覆う。

In the second heating process, when the inside of the

2回目の選択成長工程において、処理室201内を所定温度にし、処理室201内にSi系原料ガス、希釈ガス及びエッチングガスを導入することで、回路基板420の単結晶化部428を残しつつ多結晶化部429のみがエッチングされる(工程r)。

In the second selective growth step, the inside of the

3回目の成膜工程において、処理室201内を所定温度にした上で、処理室201内にSi系原料ガス及び希釈ガスを導入し、アモルファスのシリコン膜427を形成する(工程s)。

In the third film formation step, the inside of the

3回目の加熱工程において、回路基板420を加熱処理するとアモルファスのシリコン膜427が全て横方向エピタキシャル成長し、絶縁膜426全体が単結晶化部428で覆われる(工程t)。

In the third heating step, when the

以上のようにして絶縁膜426を単結晶シリコン膜428で覆った回路基板420には、更に半導体回路をパターニングすることができる。この方法によりLSIをより高密度に集積化することが可能である。

なお、本実施形態は単結晶シリコン膜を成長させてLSIを集積化するものであったが、Si系原料ガスと同時にGe系原料ガスを導入し単結晶シリコンゲルマニウム膜を成長させてもよい。

また、本実施形態では成膜工程を3回、加熱工程を3回、選択成長工程を2回行っているが、各工程の回数はこれに限られず、絶縁膜の表面全体を単結晶シリコン膜で覆うことができればこれより少なくてもよいし多くてもよい。

A semiconductor circuit can be further patterned on the

In this embodiment, the single crystal silicon film is grown to integrate the LSI. However, the Ge based source gas may be introduced simultaneously with the Si based source gas to grow the single crystal silicon germanium film.

In this embodiment, the film forming process is performed three times, the heating process is performed three times, and the selective growth process is performed twice. However, the number of times of each process is not limited to this, and the entire surface of the insulating film is formed on the single crystal silicon film. If it can be covered with, it may be less or more than this.

以上、本発明の好ましい実施形態を説明したが、本発明の好ましい第1の態様によれば、

単結晶シリコン部及び絶縁部が表面において露出した複数の基板を所定の間隔で積層状に保持し、構成元素としてSiを含むガスの雰囲気中に曝露し、前記単結晶シリコン部及び前記絶縁部の上にアモルファスのシリコン膜を成膜する成膜工程と、

前記成膜工程後に、前記シリコン膜を加熱して、前記単結晶シリコン部を基にして前記アモルファスのシリコン膜を単結晶化させる加熱工程と、

前記加熱工程後に、前記基板を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、前記単結晶化した部分を残留させつつ、前記絶縁部の上の単結晶化しなかった部分を除去する選択成長工程と、を含み、

前記基板に対して、前記成膜工程、前記加熱工程及び前記選択成長工程を繰り返すことを特徴とする半導体装置の製造方法が提供される。

While preferred embodiments of the present invention have been described above, according to a preferred first aspect of the present invention,

A plurality of substrates in which the single crystal silicon part and the insulating part are exposed on the surface are held in a laminated form at a predetermined interval, and are exposed to a gas atmosphere containing Si as a constituent element, and the single crystal silicon part and the insulating part A film forming process for forming an amorphous silicon film on the surface;

A heating step of heating the silicon film after the film forming step to single crystallize the amorphous silicon film based on the single crystal silicon portion;

After the heating step, the substrate is exposed to a mixed atmosphere of a gas containing Si as a constituent element and a gas containing Cl as a constituent element, and the single crystal on the insulating portion is left while the single crystallized portion remains. And a selective growth step for removing a portion that has not been converted,

There is provided a method for manufacturing a semiconductor device, wherein the film forming step, the heating step, and the selective growth step are repeated for the substrate.

好ましくは、前記第1の態様において、

前記基板に対して、前記成膜工程、前記加熱工程及び前記選択成長工程を繰り返している際に、前記加熱工程において前記絶縁部全体が単結晶シリコンによって覆われたら、その繰り返しを終了する。

Preferably, in the first aspect,

When the film formation step, the heating step, and the selective growth step are repeated for the substrate, if the entire insulating portion is covered with single crystal silicon in the heating step, the repetition is finished.

好ましくは、前記第1の態様において、

前記選択成長工程において、前記混合雰囲気は前記構成元素としてSiを含むガスと前記構成元素としてClを含むガスの割合が4:1であり、その温度は620℃以上である。

Preferably, in the first aspect,

In the selective growth step, the ratio of the gas containing Si as the constituent element to the gas containing Cl as the constituent element is 4: 1 in the mixed atmosphere, and the temperature is 620 ° C. or more.

好ましくは、前記第1の態様において、

前記選択成長工程において、前記混合雰囲気は前記構成元素としてSiを含むガスが4%、前記構成元素としてClを含むガスが1%、希釈ガスが95%の割合であり、その温度は620〜660℃の範囲内である。

Preferably, in the first aspect,

In the selective growth step, the mixed atmosphere has a ratio of 4% of a gas containing Si as the constituent element, 1% of a gas containing Cl as the constituent element, and 95% of a dilution gas, and its temperature is 620 to 660. Within the range of ° C.

好ましくは、前記第1の態様において、

前記構成元素としてSiを含むガスはSiH4であり、前記構成元素としてClを含むガスはCl2である。

Preferably, in the first aspect,

The gas containing Si as the constituent element is SiH 4 , and the gas containing Cl as the constituent element is Cl 2 .

本発明の好ましい第2の態様によれば、

単結晶シリコン部及び絶縁部が表面において露出した複数の基板を所定の間隔で積層状に保持し、構成元素としてSiを含むガスの雰囲気中に曝露し、前記単結晶シリコン部及び前記絶縁部の上にアモルファスのシリコン膜を成膜する成膜工程と、

前記成膜工程後に、前記シリコン膜を加熱して、前記単結晶シリコン部を基にして前記アモルファスのシリコン膜を単結晶化させる加熱工程と、

前記加熱工程後に、前記基板を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、前記単結晶化した部分を残留させつつ、前記絶縁部の上の単結晶化しなかった部分を除去する選択成長工程と、を含み、

前記基板に対して、前記成膜工程、前記加熱工程及び前記選択成長工程を繰り返すことを特徴とする単結晶シリコン膜の製造方法が提供される。

According to a preferred second aspect of the invention,

A plurality of substrates in which the single crystal silicon part and the insulating part are exposed on the surface are held in a laminated form at a predetermined interval, and are exposed to a gas atmosphere containing Si as a constituent element, and the single crystal silicon part and the insulating part A film forming process for forming an amorphous silicon film on the surface;

A heating step of heating the silicon film after the film forming step to single crystallize the amorphous silicon film based on the single crystal silicon portion;

After the heating step, the substrate is exposed to a mixed atmosphere of a gas containing Si as a constituent element and a gas containing Cl as a constituent element, and the single crystal on the insulating portion is left while the single crystallized portion remains. And a selective growth step for removing a portion that has not been converted,

There is provided a method for producing a single crystal silicon film, wherein the film forming step, the heating step, and the selective growth step are repeated for the substrate.

好ましくは、前記第2の態様において、

前記基板に対して、前記成膜工程、前記加熱工程及び前記選択成長工程を繰り返している際に、前記加熱工程において前記絶縁部全体が単結晶シリコンによって覆われたら、その繰り返しを終了する。

Preferably, in the second aspect,

When the film formation step, the heating step, and the selective growth step are repeated for the substrate, if the entire insulating portion is covered with single crystal silicon in the heating step, the repetition is finished.

好ましくは、前記第2の態様において、

前記選択成長工程において、前記混合雰囲気は前記構成元素としてSiを含むガスと前記構成元素としてClを含むガスの割合が4:1であり、その温度は620℃以上である。

Preferably, in the second aspect,

In the selective growth step, the ratio of the gas containing Si as the constituent element to the gas containing Cl as the constituent element is 4: 1 in the mixed atmosphere, and the temperature is 620 ° C. or more.

好ましくは、前記第2の態様において、

前記選択成長工程において、前記混合雰囲気は前記構成元素としてSiを含むガスが4%、前記構成元素としてClを含むガスが1%、希釈ガスが95%の割合であり、その温度は620〜660℃の範囲内である。

Preferably, in the second aspect,

In the selective growth step, the mixed atmosphere has a ratio of 4% of a gas containing Si as the constituent element, 1% of a gas containing Cl as the constituent element, and 95% of a dilution gas, and its temperature is 620 to 660. Within the range of ° C.

好ましくは、前記第2の態様において、

前記構成元素としてSiを含むガスはSiH4であり、前記構成元素としてClを含むガスはCl2である。

Preferably, in the second aspect,

The gas containing Si as the constituent element is SiH 4 , and the gas containing Cl as the constituent element is Cl 2 .

本発明の好ましい第3の態様によれば、

単結晶シリコンゲルマニウム部及び絶縁部が表面において露出した複数の基板を所定の間隔で積層状に保持し、構成元素としてSiを含むガス及び構成元素としてGeを含むガスの混合雰囲気中に曝露し、前記単結晶シリコンゲルマニウム部及び前記絶縁部の上にアモルファスのシリコンゲルマニウム膜を成膜する成膜工程と、

前記成膜工程後に、前記シリコンゲルマニウム膜を加熱して、前記単結晶シリコンゲルマニウム部を基にして前記アモルファスのシリコンゲルマニウム膜を単結晶化させる加熱工程と、

前記加熱工程後に、前記基板を構成元素としてSiを含むガス、構成元素としてGeを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、前記単結晶化した部分を残留させつつ、前記絶縁部の上の単結晶化しなかった部分を除去する選択成長工程と、を含み、

前記基板に対して、前記成膜工程、前記加熱工程及び前記選択成長工程を繰り返すことを特徴とする半導体装置の製造方法が提供される。

According to a preferred third aspect of the invention,

A plurality of substrates having a single crystal silicon germanium portion and an insulating portion exposed on the surface are held in a laminated form at a predetermined interval, and exposed to a mixed atmosphere of a gas containing Si as a constituent element and a gas containing Ge as a constituent element, A film forming step of forming an amorphous silicon germanium film on the single crystal silicon germanium part and the insulating part;

After the film forming step, heating the silicon germanium film, and heating the single crystal silicon germanium part based on the amorphous silicon germanium film,

After the heating step, the substrate is exposed to a mixed atmosphere of a gas containing Si as a constituent element, a gas containing Ge as a constituent element and a gas containing Cl as a constituent element, and the single crystallized portion remains, And a selective growth step of removing a portion that has not been monocrystallized on the insulating portion,

There is provided a method for manufacturing a semiconductor device, wherein the film forming step, the heating step, and the selective growth step are repeated for the substrate.

好ましくは、前記第3の態様において、

前記基板に対して、前記成膜工程、前記加熱工程及び前記選択成長工程を繰り返している際に、前記加熱工程において前記絶縁部全体が単結晶シリコンゲルマニウムによって覆われたら、その繰り返しを終了する。

Preferably, in the third aspect,

When the film forming step, the heating step, and the selective growth step are repeated for the substrate, if the entire insulating portion is covered with single crystal silicon germanium in the heating step, the repetition is finished.

好ましくは、前記第3の態様において、

前記構成元素としてSiを含むガスはSiH4であり、前記構成元素としてGeを含むガスはGeH4であり、前記構成元素としてClを含むガスはCl2である。

Preferably, in the third aspect,

The gas containing Si as the constituent element is SiH 4 , the gas containing Ge as the constituent element is GeH 4 , and the gas containing Cl as the constituent element is Cl 2 .

本発明の好ましい第4の態様によれば、

単結晶シリコンゲルマニウム部及び絶縁部が表面において露出した複数の基板を所定の間隔で積層状に保持し、構成元素としてSiを含むガス及び構成元素としてGeを含むガスの混合雰囲気中に曝露し、前記単結晶シリコンゲルマニウム部及び前記絶縁部の上にアモルファスのシリコンゲルマニウム膜を成膜する成膜工程と、

前記成膜工程後に、前記シリコンゲルマニウム膜を加熱して、前記単結晶シリコンゲルマニウム部を基にして前記アモルファスのシリコンゲルマニウム膜を単結晶化させる加熱工程と、

前記加熱工程後に、前記基板を構成元素としてSiを含むガス、構成元素としてGeを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、前記単結晶化した部分を残留させつつ、前記絶縁部の上の単結晶化しなかった部分を除去する選択成長工程と、を含み、

前記基板に対して、前記成膜工程、前記加熱工程及び前記選択成長工程を繰り返すことを特徴とする単結晶シリコンゲルマニウム膜の製造方法が提供される。

According to a preferred fourth aspect of the invention,

A plurality of substrates having a single crystal silicon germanium portion and an insulating portion exposed on the surface are held in a laminated form at a predetermined interval, and exposed to a mixed atmosphere of a gas containing Si as a constituent element and a gas containing Ge as a constituent element, A film forming step of forming an amorphous silicon germanium film on the single crystal silicon germanium part and the insulating part;

After the film forming step, heating the silicon germanium film, and heating the single crystal silicon germanium part based on the amorphous silicon germanium film,

After the heating step, the substrate is exposed to a mixed atmosphere of a gas containing Si as a constituent element, a gas containing Ge as a constituent element and a gas containing Cl as a constituent element, and the single crystallized portion remains, And a selective growth step of removing a portion that has not been monocrystallized on the insulating portion,

There is provided a method for producing a single crystal silicon germanium film, wherein the film forming step, the heating step, and the selective growth step are repeated on the substrate.

好ましくは、前記第4の態様において、

前記基板に対して、前記成膜工程、前記加熱工程及び前記選択成長工程を繰り返している際に、前記加熱工程において前記絶縁部全体が単結晶シリコンゲルマニウムによって覆われたら、その繰り返しを終了する。

Preferably, in the fourth aspect,

When the film forming step, the heating step, and the selective growth step are repeated for the substrate, if the entire insulating portion is covered with single crystal silicon germanium in the heating step, the repetition is finished.

好ましくは、前記第4の態様において、

前記構成元素としてSiを含むガスはSiH4であり、前記構成元素としてGeを含むガスはGeH4であり、前記構成元素としてClを含むガスはCl2である。

Preferably, in the fourth aspect,

The gas containing Si as the constituent element is SiH 4 , the gas containing Ge as the constituent element is GeH 4 , and the gas containing Cl as the constituent element is Cl 2 .

101 基板処理装置

165 ガス供給管

200 基板

201 処理室

205 アウターチューブ

206 ヒータ

240 コントローラ

263 温度センサ

300 ガス供給系

301 Si系原料ガス供給源

302 Ge系原料ガス供給源

303 希釈ガス供給源

304 エッチングガス供給源

311〜314 MFC

321〜324 バルブ

401 絶縁部

402 シリコン膜

403 単結晶シリコン部

404 単結晶化部

405 多結晶化部

101

321 to 324

Claims (2)

前記成膜工程後に、前記シリコン膜を加熱して、前記単結晶シリコン部を基にして前記アモルファスのシリコン膜を単結晶化させる加熱工程と、

前記加熱工程後に、前記基板を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、前記単結晶化した部分を残留させつつ、前記絶縁部の上の単結晶化しなかった部分を除去する選択成長工程と、を含み、

前記基板に対して、前記成膜工程、前記加熱工程及び前記選択成長工程を繰り返すことを特徴とする半導体装置の製造方法。 A plurality of substrates in which the single crystal silicon part and the insulating part are exposed on the surface are held in a laminated form at a predetermined interval, and are exposed to a gas atmosphere containing Si as a constituent element, and the single crystal silicon part and the insulating part A film forming process for forming an amorphous silicon film on the surface;

A heating step of heating the silicon film after the film forming step to single crystallize the amorphous silicon film based on the single crystal silicon portion;

After the heating step, the substrate is exposed to a mixed atmosphere of a gas containing Si as a constituent element and a gas containing Cl as a constituent element, and the single crystal on the insulating portion is left while the single crystallized portion remains. And a selective growth step for removing a portion that has not been converted,

A method of manufacturing a semiconductor device, wherein the film forming step, the heating step, and the selective growth step are repeated for the substrate.

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008315297A JP2010141079A (en) | 2008-12-11 | 2008-12-11 | Method of manufacturing semiconductor device |

| PCT/JP2009/006013 WO2010067517A1 (en) | 2008-12-11 | 2009-11-11 | Method for manufacturing semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008315297A JP2010141079A (en) | 2008-12-11 | 2008-12-11 | Method of manufacturing semiconductor device |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010141079A true JP2010141079A (en) | 2010-06-24 |

Family

ID=42242515

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008315297A Pending JP2010141079A (en) | 2008-12-11 | 2008-12-11 | Method of manufacturing semiconductor device |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP2010141079A (en) |

| WO (1) | WO2010067517A1 (en) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013089671A (en) * | 2011-10-14 | 2013-05-13 | Japan Steel Works Ltd:The | Laser processing apparatus |

| JP2013258188A (en) * | 2012-06-11 | 2013-12-26 | Hitachi Kokusai Electric Inc | Method for processing substrate, method for manufacturing semiconductor device, and substrate processing device |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6022781B2 (en) * | 2012-03-16 | 2016-11-09 | 猛英 白土 | Semiconductor device and manufacturing method thereof |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| IN157312B (en) * | 1982-01-12 | 1986-03-01 | Rca Corp | |

| JPS60152018A (en) * | 1984-01-20 | 1985-08-10 | Agency Of Ind Science & Technol | Manufacture of semiconductor thin film crystal layer |

| JPS6476718A (en) * | 1987-09-17 | 1989-03-22 | Nec Corp | Formation of thin film |

| JP2755653B2 (en) * | 1988-06-15 | 1998-05-20 | 三洋電機株式会社 | Method of forming SOI structure |

| JPH02153523A (en) * | 1988-12-05 | 1990-06-13 | Sharp Corp | Method of forming semiconductor substrate |

| JP2715734B2 (en) * | 1991-09-20 | 1998-02-18 | 日本電気株式会社 | SOI forming method |

| JP2910382B2 (en) * | 1992-03-09 | 1999-06-23 | 日本電気株式会社 | Method for manufacturing semiconductor device |

| JPH0992621A (en) * | 1995-09-28 | 1997-04-04 | Oki Electric Ind Co Ltd | Method for selective growth of semiconductor thin film |

| US7682940B2 (en) * | 2004-12-01 | 2010-03-23 | Applied Materials, Inc. | Use of Cl2 and/or HCl during silicon epitaxial film formation |

-

2008

- 2008-12-11 JP JP2008315297A patent/JP2010141079A/en active Pending

-

2009

- 2009-11-11 WO PCT/JP2009/006013 patent/WO2010067517A1/en not_active Ceased

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013089671A (en) * | 2011-10-14 | 2013-05-13 | Japan Steel Works Ltd:The | Laser processing apparatus |

| JP2013258188A (en) * | 2012-06-11 | 2013-12-26 | Hitachi Kokusai Electric Inc | Method for processing substrate, method for manufacturing semiconductor device, and substrate processing device |

| US20130344689A1 (en) * | 2012-06-11 | 2013-12-26 | Hitachi Kokusai Electric, Inc. | Method for processing substrate, method for manufacturing semiconductor device, and substrate processing apparatus |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2010067517A1 (en) | 2010-06-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7851379B2 (en) | Substrate processing method and substrate processing apparatus | |

| KR102072270B1 (en) | Method of growing crystal in recess and processing apparatus used therefor | |

| US10840094B2 (en) | Method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| US9997354B2 (en) | Method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| US10090152B2 (en) | Method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| US11075114B2 (en) | Method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| US8071477B2 (en) | Method of manufacturing semiconductor device and substrate processing apparatus | |

| US10262872B2 (en) | Method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| US11164744B2 (en) | Method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| US10529560B2 (en) | Method of manufacturing semiconductor device, substrate processing apparatus and recording medium | |

| TW202123322A (en) | Method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| JP2010141079A (en) | Method of manufacturing semiconductor device | |

| JP2017162850A (en) | Method of filling recess and processing apparatus | |

| US20240222117A1 (en) | Method of processing substrate, method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| TW202347500A (en) | Substrate processing method, semiconductor device manufacturing method, program and substrate processing device | |

| KR20220138808A (en) | Method and apparatus of forming silicon film | |

| JP2010147142A (en) | Method for manufacturing semiconductor, and apparatus | |

| CN111048416A (en) | Deposition method of polycrystalline silicon film |