JP2010074724A - プリディストータ - Google Patents

プリディストータ Download PDFInfo

- Publication number

- JP2010074724A JP2010074724A JP2008242436A JP2008242436A JP2010074724A JP 2010074724 A JP2010074724 A JP 2010074724A JP 2008242436 A JP2008242436 A JP 2008242436A JP 2008242436 A JP2008242436 A JP 2008242436A JP 2010074724 A JP2010074724 A JP 2010074724A

- Authority

- JP

- Japan

- Prior art keywords

- distortion compensation

- signal

- distortion

- coefficient

- compensation

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Amplifiers (AREA)

- Transmitters (AREA)

Abstract

【解決手段】プリディストータ301は、所定の基準に基づく歪補償値で入力信号Xを歪補償した予歪補償信号Aを被補償回路401へ出力する歪補償部11と、互いに異なるサンプリングポイントで入力信号Xを取り込んだ複数の入力サンプリング信号及び前記サンプリングポイントで被補償回路401からの出力信号Yを取り込んだ複数の出力サンプリング信号から前記基準の更新量を算出し、歪補償部11に前記基準を更新させる制御部13と、を備える。

【選択図】図3

Description

図3は本実施形態のプリディストータ301の構成を説明するブロック図である。プリディストータ301は、所定の基準に基づく歪補償値で入力信号Xを歪補償した予歪補償信号Aを被補償回路401へ出力する歪補償部11と、互いに異なるサンプリングポイントで予歪補償信号Aを取り込んだ複数の予歪サンプリング信号及び同じサンプリングポイントで被補償回路401からの出力信号Yを取り込んだ複数の出力サンプリング信号から前記基準の更新量を算出し、歪補償部11に前記基準を更新させる制御部13と、を備える。例えば、被補償回路401は信号増幅器である。また、歪補償部11が保有する基準とは歪補償多項式の係数もしくはルックアップテーブルのテーブル値であるが、以下では歪補償多項式の係数として説明する。

複数の増幅器で構成された増幅器は、図1のようにモデル化できる。入力信号Xを周期Tsでサンプリングした離散時間信号をx(nTs)とし、出力信号Yを周期Tsでサンプリングした離散時間信号をy(nTs)とし、表記を簡単にするためにそれぞれをx(n),y(n)で表すこととする。また、x(n)及びy(n)は実数成分と虚数成分を持つ複素数信号であり、x(n)及びy(n)に対する乗算及び加算は、それぞれ複素乗算及び複素加算を示すものとする。すなわち、先に説明した図2および3においては歪補償部11と被補償回路401との間には図示しない直交変調器、D/A変換器、およびアップコンバータがあり、被補償回路401と制御部の間には図示しないダウンコンバータ、A/D変換器、および直交復調器がある。このとき、増幅器を構成する要素増幅器513の歪特性を表す歪特性多項式をそれぞれ

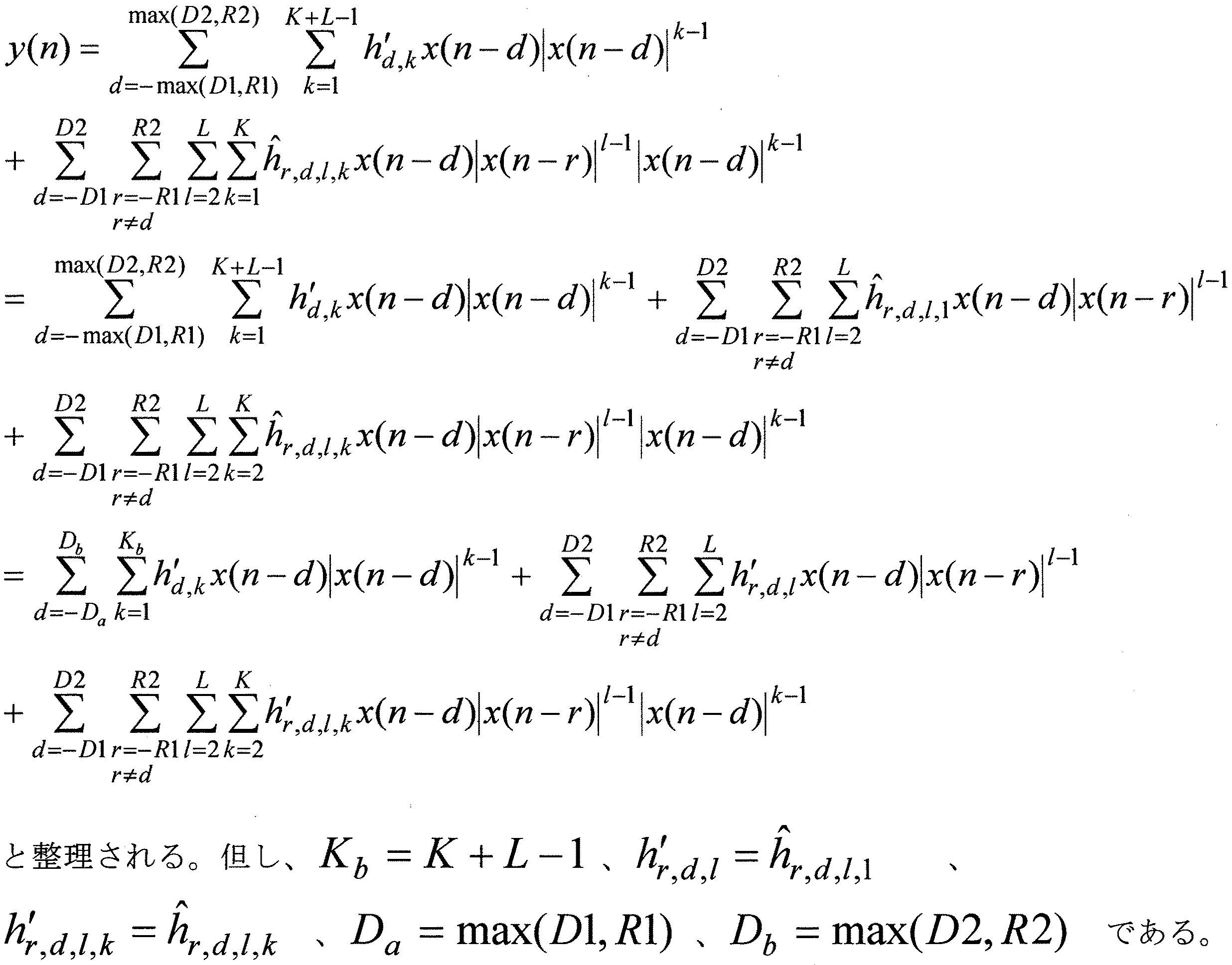

次に、図1のモデルに基づいた増幅装置の歪補償方法について説明する。増幅装置全体の入出力信号の関係は

ここで、数式10を利用して歪補償多項式の係数を求める方法について説明する。但し、ここでは、表現の簡単のためにDa=0、R1=0、D1=0とおく。複素数係数w’d,k、w’r,d,l、及びw’r,d,l,kをすべて並べた係数のベクトルを

歪補償多項式の係数を1回で正確に求めるには、想定している入力信号の振幅(または電力)の全てを網羅するような信号を実際に増幅装置に入力した際の入力信号と、入力信号に対応する出力信号の組を用いて歪補償多項式の係数を最小二乗法を用いて算出する必要があり、計算量が膨大なものとなる問題がある。すなわち、歪補償多項式の係数を正確に算出するには、サンプリングした入力信号と出力信号を非常に多く用いる必要がある。

また、行xn(i)を構成するベクトルx1n(i)、x2n(i)およびx3n(i)はそれぞれ数式26、数式27及び数式28で表せる。

また、行yn(i)を構成するベクトルy1n(i)、y2n(i)およびy3n(i)はそれぞれ数式30、数式31及び数式32で表せる。

本発明は、制御部13が取得する2つのサンプリング信号を被補償回路401へ入力する予歪補償信号Aと被補償回路401から出力する出力信号Yとから取得することで、制御部13における数式33の計算を省略し、歪補償多項式の係数の更新に必要な計算量、メモリ量、および計算時間を大幅に減らすものである。

2N(Q+1)+(Q+1)

に比例した量のメモリ量が必要だったのが、本発明により、

N+N(Q+1)+(Q+1)

に比例した量のメモリ量となり、NQに比例したメモリ量を減らせることができる。

11:歪補償部

13:制御部

401:被補償回路

511:遅延素子

512−j:振幅値関数(jは自然数)

513:要素増幅器

514:複素乗算器

515:積算器

X:入力信号

Y:出力信号

A:予歪補償信号

Claims (1)

- 所定の基準に基づく歪補償値で入力信号を歪補償した予歪補償信号を被補償回路へ出力する歪補償部と、

互いに異なるサンプリングポイントで前記予歪補償信号を取り込んだ複数の予歪サンプリング信号及び前記サンプリングポイントで前記被補償回路からの出力信号を取り込んだ複数の出力サンプリング信号から前記基準の更新量を算出し、前記歪補償部に前記基準を更新させる制御部と、

を備えるプリディストータ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008242436A JP5221260B2 (ja) | 2008-09-22 | 2008-09-22 | プリディストータ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008242436A JP5221260B2 (ja) | 2008-09-22 | 2008-09-22 | プリディストータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010074724A true JP2010074724A (ja) | 2010-04-02 |

| JP5221260B2 JP5221260B2 (ja) | 2013-06-26 |

Family

ID=42206056

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008242436A Active JP5221260B2 (ja) | 2008-09-22 | 2008-09-22 | プリディストータ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5221260B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2023122772A (ja) * | 2022-02-24 | 2023-09-05 | 日本無線株式会社 | 歪補償装置 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007037110A (ja) * | 2005-07-21 | 2007-02-08 | Alcatel | 適応型デジタルプリディストーションシステム |

| JP2009213113A (ja) * | 2008-03-05 | 2009-09-17 | Fujitsu Ltd | 非線形システム逆特性同定装置及びその方法、電力増幅装置及び電力増幅器のプリディストータ |

| JP2012500572A (ja) * | 2008-08-29 | 2012-01-05 | ザイリンクス インコーポレイテッド | 電力増幅器における歪みを低減するための方法および回路 |

-

2008

- 2008-09-22 JP JP2008242436A patent/JP5221260B2/ja active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007037110A (ja) * | 2005-07-21 | 2007-02-08 | Alcatel | 適応型デジタルプリディストーションシステム |

| JP2009213113A (ja) * | 2008-03-05 | 2009-09-17 | Fujitsu Ltd | 非線形システム逆特性同定装置及びその方法、電力増幅装置及び電力増幅器のプリディストータ |

| JP2012500572A (ja) * | 2008-08-29 | 2012-01-05 | ザイリンクス インコーポレイテッド | 電力増幅器における歪みを低減するための方法および回路 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2023122772A (ja) * | 2022-02-24 | 2023-09-05 | 日本無線株式会社 | 歪補償装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5221260B2 (ja) | 2013-06-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5120178B2 (ja) | 非線形システム逆特性同定装置及びその方法、電力増幅装置及び電力増幅器のプリディストータ | |

| EP1560329B1 (en) | Digital predistorter using power series model | |

| US6801086B1 (en) | Adaptive digital pre-distortion using amplifier model that incorporates frequency-dependent non-linearities | |

| KR101679230B1 (ko) | 전력증폭기의 비선형 특성을 보상하는 다항식 디지털 전치왜곡 장치 및 그 방법 | |

| JP5753272B2 (ja) | タップ出力の正規化を伴う非線形モデル | |

| CN103299542B (zh) | 用于数字预失真器的正交基函数集 | |

| CN100477500C (zh) | 功率放大器预失真器及其包括该预失真器的基站 | |

| KR101789924B1 (ko) | 적응형 디지털 전치 왜곡을 위한 디바이스 및 방법 | |

| KR101386239B1 (ko) | 비선형 왜곡의 보상을 위한 전치 왜곡 장치 및 방법 | |

| JP4909261B2 (ja) | 電力増幅器におけるモデルに基づく歪み低減 | |

| US8218676B2 (en) | System and method for training pre-inverse of nonlinear system | |

| CN100530944C (zh) | 功率放大器预失真器的训练方法及其基站 | |

| JP5299958B2 (ja) | プリディストータ | |

| JP5160344B2 (ja) | プリディストータ | |

| JP5221260B2 (ja) | プリディストータ | |

| JP5238461B2 (ja) | プリディストータ | |

| JP5290698B2 (ja) | プリディストータ | |

| JP5260335B2 (ja) | プリディストータ | |

| KR100991494B1 (ko) | 디지털 전치왜곡 방법 및 그 장치 | |

| KR20120054369A (ko) | 메모리 다항식 모델을 이용하는 전치 왜곡 장치, 그것의 전치 왜곡 방법, 및 전치 왜곡 장치를 포함하는 시스템 | |

| JP5115979B2 (ja) | プリディストータ | |

| WO2018109862A1 (ja) | 電力増幅回路 | |

| JP2011228999A (ja) | 増幅回路及び無線通信装置 | |

| TW202404253A (zh) | 補償功率放大器失真的方法以及系統 | |

| JP2013132009A (ja) | 歪補償器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110920 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120906 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120911 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121109 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121211 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130207 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130305 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130307 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160315 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5221260 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |