JP2010051113A - 二次電池の充電回路、その充電制御方法及びその充電回路を備えた電源回路 - Google Patents

二次電池の充電回路、その充電制御方法及びその充電回路を備えた電源回路 Download PDFInfo

- Publication number

- JP2010051113A JP2010051113A JP2008214087A JP2008214087A JP2010051113A JP 2010051113 A JP2010051113 A JP 2010051113A JP 2008214087 A JP2008214087 A JP 2008214087A JP 2008214087 A JP2008214087 A JP 2008214087A JP 2010051113 A JP2010051113 A JP 2010051113A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- charging

- current

- output terminal

- secondary battery

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E60/00—Enabling technologies; Technologies with a potential or indirect contribution to GHG emissions mitigation

- Y02E60/10—Energy storage using batteries

Landscapes

- Charge And Discharge Circuits For Batteries Or The Like (AREA)

- Secondary Cells (AREA)

Abstract

【解決手段】充電回路3の動作を停止させず、充電完了後は切り換えスイッチSW1を制御して演算増幅回路12の入力電圧Vsが基準電圧Vs4になるようにし、出力端子BATTの電圧Vbatを、再充電電圧V3よりも小さく、リセット電圧Vrstよりも大きい電圧V4に設定するようにして、二次電池Batが接続されていない場合に負荷10への負荷電流が急激に増加したときでも、負荷10にリセットがかかることを防止することができるようにした。

【選択図】図1

Description

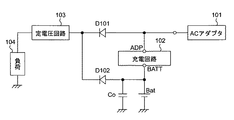

図3では、ACアダプタ101が機器に接続されている場合は、ACアダプタ101によって充電回路102に電力が供給され、充電回路102は二次電池Batの充電を行う。充電回路102は、二次電池Batの電圧や充電電流等を検出して、二次電池Batが満充電になった場合は二次電池Batへの充電を停止する。また、ACアダプタ101の出力電圧は、通常、二次電池Batの電圧よりも大きいため、ダイオードD101がオンしてACアダプタ101の出力電圧が定電圧回路103に入力される。なお、ダイオードD102は、ダイオードD101を介して出力されているACアダプタ101の電圧で二次電池Batが充電されないようにするための逆流防止用ダイオードをなす。定電圧回路103は、入力された電圧を負荷104の動作に適した電圧に変換して出力する。

次に、ACアダプタ101が接続されていない場合は、ダイオードD102がオンして、二次電池Batの電圧が定電圧回路103に入力される。この場合、ダイオードD101は、ACアダプタ101側に二次電池Batから電力供給ができないようにするための逆流防止用ダイオードをなす。

定電圧回路103の出力電圧は一定であるから、負荷104へ出力する負荷電流が同じであれば、定電圧回路103の消費電力は入力電圧が大きいほど大きくなる。通常、ACアダプタ101の出力電圧の方が二次電池Batの電圧よりも大きいため、ACアダプタ101を使用したときの方が定電圧回路103の消費電力は大きくなる。すなわち、図3の構成では、定電圧回路103内で使用されている電圧制御用トランジスタ(図示せず)のトランジスタサイズを、ACアダプタ101の出力電圧に合わせて大きくする必要があり、コストアップの要因になっていた。

図4では、ACアダプタ101が機器に接続されている場合は、ACアダプタ101から充電回路102に電力が供給され、充電回路102によって二次電池Batが充電される。また、充電回路102は、出力端子BATTが定電圧回路103の入力端にも接続されているため、定電圧回路103を介して負荷104へも電力を供給する。

しかし、図4のような構成では、二次電池Batが取り外された状態で、ACアダプタ101だけで作動させようとした場合に、次に説明するような問題が発生していた。

二次電池Batが装着されている場合の動作について説明する。

図5において、時刻t1以前は充電回路102の動作が停止しており、負荷104への電力供給は二次電池Batから行われている。このため、二次電池Batの電圧が次第に低下する。

時刻t5以前では充電回路102の動作が停止しており、負荷104への電力供給はコンデンサCoから行われているため、BATT端子電圧が次第に低下する。

時刻t5でBATT端子電圧が再充電電圧V3以下になると、充電回路102は動作を開始する。充電回路102にはソフトスタート回路が設けられており、充電回路102の出力電流は、時間Tsをかけて徐々増加する。このため、BATT端子電圧は、時間Tsが経過した時刻t6から上昇を始める。なお、時刻t6におけるBATT端子電圧は、負荷電流が小さいために再充電電圧V3よりも僅かに低下した値になっているが、リセット電圧Vrstよりも大きいため特に問題はない。

制御電極に入力された制御信号に応じて、前記二次電池への充電電流の供給制御を行う充電電流制御用トランジスタと、

前記充電電流の電流値を検出する電流検出回路部と、

前記出力端子の電圧を検出する電圧検出回路部と、

前記電圧検出回路部で検出された電圧が所定の満充電電圧になるように前記充電電流制御用トランジスタを動作制御して定電圧充電を行う制御回路部と、

を備え、

前記制御回路部は、前記出力端子の電圧が前記満充電電圧よりも小さい所定の再充電電圧以下に低下すると前記充電電流制御用トランジスタをオンさせて前記充電電流の供給を開始させ、前記電流検出回路部で検出された充電電流と前記電圧検出回路部で検出された電圧から、前記二次電池の充電が完了したと判定すると、前記出力端子の電圧が前記再充電電圧よりも小さく且つ前記二次電池に接続される負荷が動作可能な電圧以上である所定値になるように前記充電電流制御用トランジスタの動作制御を行うものである。

前記充電電流の電流値を検出する電流検出回路部と、

前記二次電池が接続される出力端子の電圧を検出する電圧検出回路部と、

を備え、

入力端子に入力された電圧を電源にして前記出力端子に接続された前記二次電池の充電を行う充電回路の充電制御方法において、

前記出力端子の電圧が所定の再充電電圧以下に低下すると前記充電電流制御用トランジスタをオンさせて前記充電電流の供給を開始させ、

前記電圧検出回路部で検出された電圧が前記再充電電圧よりも大きい所定の満充電電圧になるように前記充電電流制御用トランジスタを動作制御して定電圧充電を行い、

前記電流検出回路部で検出された充電電流と前記電圧検出回路部で検出された電圧から、前記二次電池の充電が完了したと判定すると、前記出力端子の電圧が前記再充電電圧よりも小さく且つ前記二次電池に接続される負荷が動作可能な電圧以上である所定値になるように前記充電電流制御用トランジスタの動作制御を行うようにした。

前記請求項1から請求項6のいずれかに記載の充電回路と、

該充電回路の前記出力端子に接続され、該充電回路によって充電が行われる二次電池と、

前記充電回路における前記出力端子の電圧を所定の定電圧に変換して前記負荷に供給する定電圧回路と、

を備えるようにした。

第1の実施の形態.

図1は、本発明の第1の実施の形態における充電回路を備えた電源回路の構成例を示した図である。

図1において、電源回路1は、ACアダプタ2、二次電池Bat、二次電池Batの充電を行う充電回路3、二次電池Batの電圧又は充電回路3の出力電圧を所定の定電圧に変換して負荷10に出力する定電圧回路4及びコンデンサCoを備えている。

充電回路3において、入力端子ADPと出力端子BATTとの間に充電電流制御用トランジスタM1が接続され、出力端子BATTと接地電圧GNDとの間に抵抗R2及びR3が直列に接続されている。抵抗R2及びR3は出力端子BATTの電圧Vbatを分圧して分圧電圧Vbを生成し、演算増幅回路12の非反転入力端と充電制御回路13にそれぞれ出力する。

i1=K×Vs5/r1………………(1)

但し、出力電流ioutが電流i1未満の場合は、演算増幅回路11は、出力信号をハイレベルにしてPMOSトランジスタM3をオフさせて遮断状態にするため、充電制御には関わらなくなる。

V1=Vs1×(r2+r3)/r3………………(2)

V4=Vs4×(r2+r3)/r3………………(3)

図2において、二次電池Batが接続されている場合について説明する。

時刻t1以前は、切り換えスイッチSW1の共通端子Cは端子Bに接続されている。このような状態では、演算増幅回路12の反転入力端には基準電圧Vs4が入力されるため、演算増幅回路12は、出力端子BATTの電圧Vbatが電圧V4になるように充電電流制御用トランジスタM1を制御する。しかし、このとき出力端子BATTの電圧Vbatは、電圧V4よりも大きい再充電電圧V3以上になっているため、演算増幅回路12の出力信号はハイレベルになり、充電電流制御用トランジスタM1とPMOSトランジスタM2はそれぞれオフして遮断状態になる。

また、演算増幅回路12の反転入力端に基準電圧Vs1が入力されると、演算増幅回路12において、反転入力端の電圧が非反転入力端に入力された分圧電圧Vbよりも大きくなる。このことから、演算増幅回路12の出力信号はローレベルになり、充電電流制御用トランジスタM1とPMOSトランジスタM2がそれぞれオンする。

演算増幅回路12の反転入力端に基準電圧Vs4が入力されると、演算増幅回路12の出力信号はハイレベルになり、充電電流制御用トランジスタM1とPMOSトランジスタM2はそれぞれオフする。このため、ACアダプタ2から出力端子BATTへの電力供給が停止し、この状態は前述した時刻t1以前の状態と同じである。時刻t3以後は、負荷10への負荷電流が二次電池Batから供給されるため、出力端子BATTの電圧Vbatが次第に低下し、以降前記のような動作が繰り返し行われる。

時刻t4以前は切り換えスイッチSW1の共通端子Cが端子Bに接続されており、前記した時刻t1以前とまったく同じ動作が行われる。但し、二次電池Batが接続されていないため、負荷10への電力供給はコンデンサCoから行われており、出力端子BATTの電圧Vbatの低下速度は速くなる。

時刻t4で、出力端子BATTの電圧Vbatが再充電電圧V3以下になると、充電制御回路13は、切り換えスイッチSW1に対して、共通端子Cの接続を端子Aに切り換えさせる。すると、演算増幅回路12の反転入力端には基準電圧Vs1が入力され、出力端子BATTの電圧Vbatの設定値が前記(2)式で示したような満充電電圧V1に変更される。

遅延時間Tdが経過した時刻t8で、演算増幅回路12の入力電圧Vsが基準電圧Vs1に切り換わると、出力端子BATTの電圧Vbatは満充電電圧V1まで上昇する。電圧Vbatが満充電電圧V1に達した後も、出力電流ioutが充電完了電流i2以上であるため、演算増幅回路12を中心に構成された定電圧充電を行う回路が定電圧回路として作動し続ける。

また、定電圧回路4に満充電電圧V1以上の電圧が入力されないようにすることができ、定電圧回路4内の電圧制御用トランジスタのトランジスタサイズを小さくすることができる。

更に、電源効率を低下させる逆流防止用のダイオードを使用する必要がないため、電源効率が向上させることができる。

2 ACアダプタ

3 充電回路

4 定電圧回路

10 負荷

11,12 演算増幅回路

13 充電制御回路

14〜16 基準電圧発生回路

Bat 二次電池

Co コンデンサ

M1 充電電流制御用トランジスタ

M2,M3 PMOSトランジスタ

R1〜R4 抵抗

SW1 切り換えスイッチ

Claims (9)

- 入力端子に入力された電圧を電源にして出力端子に接続された二次電池の充電を行う充電回路において、

制御電極に入力された制御信号に応じて、前記二次電池への充電電流の供給制御を行う充電電流制御用トランジスタと、

前記充電電流の電流値を検出する電流検出回路部と、

前記出力端子の電圧を検出する電圧検出回路部と、

前記電圧検出回路部で検出された電圧が所定の満充電電圧になるように前記充電電流制御用トランジスタを動作制御して定電圧充電を行う制御回路部と、

を備え、

前記制御回路部は、前記出力端子の電圧が前記満充電電圧よりも小さい所定の再充電電圧以下に低下すると前記充電電流制御用トランジスタをオンさせて前記充電電流の供給を開始させ、前記電流検出回路部で検出された充電電流と前記電圧検出回路部で検出された電圧から、前記二次電池の充電が完了したと判定すると、前記出力端子の電圧が前記再充電電圧よりも小さく且つ前記二次電池に接続される負荷が動作可能な電圧以上である所定値になるように前記充電電流制御用トランジスタの動作制御を行うことを特徴とする充電回路。 - 前記制御回路部は、前記出力端子の電圧が前記再充電電圧以下に低下すると、前記出力端子の電圧が前記満充電電圧になるように前記充電電流制御用トランジスタの動作制御を行うことを特徴とする請求項1記載の充電回路。

- 前記電圧検出回路部は、前記出力端子の電圧に比例した比例電圧を生成して出力し、前記制御回路部は、該比例電圧が設定した基準電圧になるように前記充電電流制御用トランジスタの動作制御を行い、前記二次電池の充電が完了したと判定すると、前記出力端子の電圧が前記所定値になるように前記基準電圧の設定値を変えて前記充電電流制御用トランジスタの動作制御を行うことを特徴とする請求項1又は2記載の充電回路。

- 前記制御回路部は、前記出力端子の電圧が前記再充電電圧以下に低下したことを検出すると、前記出力端子の電圧が前記満充電電圧になるように前記基準電圧の設定値を変えて前記充電電流制御用トランジスタの動作制御を行うことを特徴とする請求項3記載の充電回路。

- 前記制御回路部は、前記出力端子の電圧が、前記再充電電圧よりも大きく且つ前記満充電電圧よりも小さい所定の充電完了電圧以上になると共に、前記充電電流が所定の電流値未満になると、前記二次電池の充電が完了したと判定することを特徴とする請求項1、2、3又は4記載の充電回路。

- 前記電流検出回路部は、検出した前記充電電流を電圧に変換して出力し、前記制御回路部は、前記二次電池の充電を開始すると、該電流検出回路部から出力された電圧が所定の電圧になるように前記充電電流制御用トランジスタを動作制御して定電流充電を行った後、前記定電圧充電を行うことを特徴とする請求項1、2、3、4又は5記載の充電回路。

- 制御電極に入力された制御信号に応じて、二次電池への充電電流の供給制御を行う充電電流制御用トランジスタと、

前記充電電流の電流値を検出する電流検出回路部と、

前記二次電池が接続される出力端子の電圧を検出する電圧検出回路部と、

を備え、

入力端子に入力された電圧を電源にして前記出力端子に接続された前記二次電池の充電を行う充電回路の充電制御方法において、

前記出力端子の電圧が所定の再充電電圧以下に低下すると前記充電電流制御用トランジスタをオンさせて前記充電電流の供給を開始させ、

前記電圧検出回路部で検出された電圧が前記再充電電圧よりも大きい所定の満充電電圧になるように前記充電電流制御用トランジスタを動作制御して定電圧充電を行い、

前記電流検出回路部で検出された充電電流と前記電圧検出回路部で検出された電圧から、前記二次電池の充電が完了したと判定すると、前記出力端子の電圧が前記再充電電圧よりも小さく且つ前記二次電池に接続される負荷が動作可能な電圧以上である所定値になるように前記充電電流制御用トランジスタの動作制御を行うことを特徴とする充電回路の充電制御方法。 - 前記出力端子の電圧が前記再充電電圧以下に低下すると、前記出力端子の電圧が前記満充電電圧になるように前記充電電流制御用トランジスタの動作制御を行うことを特徴とする請求項7記載の充電回路の充電制御方法。

- 負荷に電源電圧を供給する電源回路において、

前記請求項1から請求項6のいずれかに記載の充電回路と、

該充電回路の前記出力端子に接続され、該充電回路によって充電が行われる二次電池と、

前記充電回路における前記出力端子の電圧を所定の定電圧に変換して前記負荷に供給する定電圧回路と、

を備えることを特徴とする電源回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008214087A JP5233503B2 (ja) | 2008-08-22 | 2008-08-22 | 二次電池の充電回路、その充電制御方法及びその充電回路を備えた電源回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008214087A JP5233503B2 (ja) | 2008-08-22 | 2008-08-22 | 二次電池の充電回路、その充電制御方法及びその充電回路を備えた電源回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010051113A true JP2010051113A (ja) | 2010-03-04 |

| JP5233503B2 JP5233503B2 (ja) | 2013-07-10 |

Family

ID=42067721

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008214087A Expired - Fee Related JP5233503B2 (ja) | 2008-08-22 | 2008-08-22 | 二次電池の充電回路、その充電制御方法及びその充電回路を備えた電源回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5233503B2 (ja) |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0161838U (ja) * | 1987-10-14 | 1989-04-20 | ||

| JP2000166102A (ja) * | 1998-11-20 | 2000-06-16 | Yamatake Corp | バックアップ方法およびバックアップ装置 |

| JP2006158103A (ja) * | 2004-11-30 | 2006-06-15 | Matsushita Electric Ind Co Ltd | 充電器 |

-

2008

- 2008-08-22 JP JP2008214087A patent/JP5233503B2/ja not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0161838U (ja) * | 1987-10-14 | 1989-04-20 | ||

| JP2000166102A (ja) * | 1998-11-20 | 2000-06-16 | Yamatake Corp | バックアップ方法およびバックアップ装置 |

| JP2006158103A (ja) * | 2004-11-30 | 2006-06-15 | Matsushita Electric Ind Co Ltd | 充電器 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5233503B2 (ja) | 2013-07-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6614388B1 (ja) | 二次電池保護回路、二次電池保護装置、電池パック及び二次電池保護回路の制御方法 | |

| US8242747B2 (en) | Charging control circuit capable of constant current charging | |

| JP5422917B2 (ja) | 充電制御用半導体集積回路および充電装置 | |

| KR100941044B1 (ko) | 과전압 보호 회로 및 전자 장치 | |

| JP2002330549A (ja) | 充放電制御回路と充電式電源装置 | |

| JP3710469B1 (ja) | 電源装置、及び携帯機器 | |

| JP2007221872A (ja) | 二次電池の充電回路、二次電池の充電回路における電源切換方法及び電源装置 | |

| JP2013055759A (ja) | 半導体集積回路、保護回路及び電池パック | |

| JP5999987B2 (ja) | パワーパス回路 | |

| JP2007252116A (ja) | パルス充電装置 | |

| JP2012135197A (ja) | チャージポンプシステムを制御するための回路および方法 | |

| CN101202466A (zh) | 充电装置 | |

| TWI418111B (zh) | 電池充電系統和方法以及移動設備 | |

| JP2004113000A (ja) | 充放電制御回路と充電式電源装置 | |

| US6864664B2 (en) | Circuit for charging supplemental battery in portable electronic device | |

| JP2008026947A (ja) | ボルテージレギュレータ | |

| JP2010279177A (ja) | バッテリ充電回路 | |

| JP2008004038A (ja) | ボルテージレギュレータ | |

| JP4655850B2 (ja) | 電源供給制御回路 | |

| JP4673252B2 (ja) | 電池充電回路、携帯電子機器、及び半導体集積回路 | |

| JP2005080491A (ja) | 電源装置 | |

| JP2012173063A (ja) | 複合デバイスシステム | |

| JP2005295683A (ja) | 携帯端末装置 | |

| JP5233503B2 (ja) | 二次電池の充電回路、その充電制御方法及びその充電回路を備えた電源回路 | |

| JP2000152510A (ja) | 充放電制御回路と充電式電源装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110613 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130220 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130226 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130311 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160405 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |