JP2007088401A - Substrate processing device, substrate processing method, program, and record medium recorded therewith - Google Patents

Substrate processing device, substrate processing method, program, and record medium recorded therewith Download PDFInfo

- Publication number

- JP2007088401A JP2007088401A JP2005349556A JP2005349556A JP2007088401A JP 2007088401 A JP2007088401 A JP 2007088401A JP 2005349556 A JP2005349556 A JP 2005349556A JP 2005349556 A JP2005349556 A JP 2005349556A JP 2007088401 A JP2007088401 A JP 2007088401A

- Authority

- JP

- Japan

- Prior art keywords

- processing

- substrate

- film

- measurement

- chamber

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/54—Apparatus specially adapted for continuous coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02041—Cleaning

- H01L21/02043—Cleaning before device manufacture, i.e. Begin-Of-Line process

- H01L21/02046—Dry cleaning only

- H01L21/02049—Dry cleaning only with gaseous HF

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02041—Cleaning

- H01L21/02057—Cleaning during device manufacture

- H01L21/0206—Cleaning during device manufacture during, before or after processing of insulating layers

- H01L21/02063—Cleaning during device manufacture during, before or after processing of insulating layers the processing being the formation of vias or contact holes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/67155—Apparatus for manufacturing or treating in a plurality of work-stations

- H01L21/67184—Apparatus for manufacturing or treating in a plurality of work-stations characterized by the presence of more than one transfer chamber

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/677—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for conveying, e.g. between different workstations

- H01L21/67739—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for conveying, e.g. between different workstations into and out of processing chamber

- H01L21/67745—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for conveying, e.g. between different workstations into and out of processing chamber characterized by movements or sequence of movements of transfer devices

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Cleaning Or Drying Semiconductors (AREA)

- Materials Engineering (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Chemical Vapour Deposition (AREA)

- General Chemical & Material Sciences (AREA)

- Drying Of Semiconductors (AREA)

- Formation Of Insulating Films (AREA)

Abstract

Description

本発明は,基板処理装置,基板処理方法,プログラム,プログラムを記録した記録媒体に関する。 The present invention relates to a substrate processing apparatus, a substrate processing method, a program, and a recording medium recording the program.

一般に,半導体デバイスの製造工程においては,半導体ウエハ(以下,単に「ウエハ」とも称する。)に対して各種の薄膜の成膜処理,酸化拡散処理,アニール処理,エッチング処理等が順次繰り返して施される。例えば薄膜に関しても,半導体ウエハ上に多層に形成される場合がある。このような各種処理を行う基板処理装置として,例えば連続して処理を行うことができる複数の処理室を1つの搬送室に共通に連結してなる,いわゆるクラスタ型の基板処理装置がある(例えば特許文献1参照)。この基板処理装置では,ウエハを各処理室間にいわば渡り歩くようにして搬送しつつ,その都度必要な処理を各処理室にて連続的に且つ効率的に行うようになっている。 In general, in a semiconductor device manufacturing process, various types of thin film deposition processing, oxidation diffusion processing, annealing processing, etching processing, and the like are sequentially performed on a semiconductor wafer (hereinafter simply referred to as “wafer”). The For example, a thin film may be formed in multiple layers on a semiconductor wafer. As such a substrate processing apparatus for performing various processes, for example, there is a so-called cluster type substrate processing apparatus in which a plurality of processing chambers capable of performing consecutive processing are commonly connected to one transfer chamber (for example, Patent Document 1). In this substrate processing apparatus, a wafer is transferred so as to walk between processing chambers, and necessary processing is continuously and efficiently performed in each processing chamber each time.

ところで,ウエハ上には,パーティクル,金属,有機物,吸着分子等の表面被膜等のコンタミネーション,自然酸化膜(Silicon Native Oxide)などが付着するので,成膜処理などを実行する前に,このような自然酸化膜などの付着物を除去することが必要となる。 By the way, since contamination such as particles, metals, organic substances, surface coatings such as adsorbed molecules, and native oxide film (Silicon Native Oxide) adhere to the wafer, it is necessary to do this before performing the film forming process. It is necessary to remove deposits such as a natural oxide film.

このため,従来は,例えば基板処理装置外でウエハを希フッ酸(DHF)等を利用したウエット洗浄によって自然酸化膜を除去した上で,洗浄されたウエハを基板処理装置内に取込んで成膜処理を実行するようにしていた。 For this reason, conventionally, for example, after the natural oxide film is removed by wet cleaning using, for example, dilute hydrofluoric acid (DHF) outside the substrate processing apparatus, the cleaned wafer is taken into the substrate processing apparatus. A membrane treatment was to be performed.

しかしながら,基板処理装置外でウエハ上の自然酸化膜を除去したとしても,成膜処理などを施すためにウエハを基板処理装置内に取込むときにウエハ表面が大気に露出されるので,ウエハ表面には新たに自然酸化膜が発生する虞がある。こうして発生した自然酸化膜の膜厚によっては,その後に形成される半導体デバイスの特性に大きく影響する。例えばウエハ表面に膜厚0.5nm以上の自然酸化膜が新たに形成されると,例えば膜厚65nm以下のゲート絶縁膜を形成する場合に大きな問題となる。 However, even if the natural oxide film on the wafer is removed outside the substrate processing apparatus, the wafer surface is exposed to the atmosphere when the wafer is taken into the substrate processing apparatus in order to perform a film forming process. In some cases, a natural oxide film may be newly generated. Depending on the thickness of the natural oxide film thus generated, the characteristics of the semiconductor device formed thereafter are greatly affected. For example, when a natural oxide film having a film thickness of 0.5 nm or more is newly formed on the wafer surface, it becomes a serious problem when a gate insulating film having a film thickness of 65 nm or less is formed.

また,上記ウエット洗浄によればウエハ表面の自然酸化膜は除去されるものの,ウエハ表面に新たにウォータマーク(例えばウエハの搬送又は乾燥中に水滴を介して局所的に形成されたシリコン酸化膜(SiO2)など)が発生する虞がある。すなわち,DHF洗浄液によりウエハ表面の自然酸化膜が除去されるので下地シリコンが露出してウエハ表面は疎水性となり,ウエハをDHF洗浄液から引き上げたときに表面に水滴が残留する。この水滴はスピン乾燥後にウォータマークとなり得る。このようなウォータマークは,洗浄処理後に実行される成膜処理などにおいて阻害要素となって半導体デバイスの特性を劣化させる虞がある。 In addition, although the natural oxide film on the wafer surface is removed by the above wet cleaning, a new watermark (for example, a silicon oxide film locally formed on the wafer surface via water droplets during the transfer or drying of the wafer ( (SiO 2 ) and the like) may occur. That is, since the natural oxide film on the wafer surface is removed by the DHF cleaning liquid, the underlying silicon is exposed, the wafer surface becomes hydrophobic, and water droplets remain on the surface when the wafer is pulled up from the DHF cleaning liquid. This water droplet can become a watermark after spin drying. Such a watermark may be an impediment factor in a film forming process performed after the cleaning process, and may deteriorate the characteristics of the semiconductor device.

この点,ウォータマークや自然酸化膜の発生を抑えるために,ウエット洗浄後の乾燥工程にイソプロピルアルコール(IPA)を用いる方法もある(例えば特許文献2参照)。ところが,IPA乾燥後のウエハ表面にはIPA分子(炭素等の有機物)が残留する場合がある。このIPA分子は例えばゲート酸化膜特性に悪影響を与える虞がある。(K. MOTAI, T. Itoga, and T. Irie, Extended Abstruct of 1997,International Conference onSolidState Devices and Materials, Hamamatsu, pp.24-25(1997)参照)。 In this regard, in order to suppress the generation of watermarks and natural oxide films, there is a method using isopropyl alcohol (IPA) in the drying process after wet cleaning (see, for example, Patent Document 2). However, IPA molecules (organic matter such as carbon) may remain on the wafer surface after IPA drying. This IPA molecule may adversely affect the gate oxide film characteristics, for example. (See K. MOTAI, T. Itoga, and T. Irie, Extended Abstruct of 1997, International Conference on Solid State Devices and Materials, Hamamatsu, pp. 24-25 (1997)).

そこで,近年では,上記ウエット洗浄方法によらずに,プラズマを用いたドライ洗浄方法によってウエハ上の自然酸化膜を除去するものも知られている。このドライ洗浄方法としては,例えば水素ガスとアルゴンガスを用いて誘導結合プラズマを形成することにより,ウエハ上の自然酸化膜を除去するものがある(例えば特許文献3参照)。このようなドライ洗浄方法によれば,ウエット洗浄方法による洗浄液などの水成分を用いないので,ウォータマークが発生することなく,自然酸化膜を除去することができる。 Therefore, in recent years, there has been known a method of removing a natural oxide film on a wafer by a dry cleaning method using plasma, instead of the wet cleaning method. As this dry cleaning method, for example, there is a method of removing a natural oxide film on a wafer by forming inductively coupled plasma using hydrogen gas and argon gas (see, for example, Patent Document 3). According to such a dry cleaning method, since a water component such as a cleaning solution by a wet cleaning method is not used, a natural oxide film can be removed without generating a watermark.

しかしながら,ドライ洗浄方法をプラズマ処理によって行うと,ウエハにプラズマ起因のチャージアップダメージを負わせてしまう虞がある。このようなダメージを残したままウエハ上に半導体デバイスを生成すると,例えばゲート絶縁膜の破壊などが起って,半導体デバイスの特性が劣化するなどの問題がある。 However, when the dry cleaning method is performed by plasma processing, there is a risk that charge-up damage due to plasma may be caused to the wafer. If a semiconductor device is generated on a wafer with such damage remaining, there is a problem that the characteristics of the semiconductor device deteriorate due to, for example, destruction of a gate insulating film.

ところで,ウエハ上の膜厚やパーティクルを測定することによって,実際にウエハ上の自然酸化膜などの付着物が除去されたか否かについて検査を行うことができれば,次の成膜処理によって成膜される膜質の均一性を確保することができるなど利点も多い。 By the way, if the film thickness and particles on the wafer can be measured to check whether or not deposits such as a natural oxide film on the wafer have actually been removed, the film is formed by the following film forming process. There are many advantages such as ensuring uniformity of film quality.

しかしながら,従来のパーティクル測定装置(例えば特許文献4参照)や膜厚測定装置(特許文献5参照)では,ウエハ上の自然酸化膜などの付着物を除去してから連続してウエハ上の膜厚やパーティクルを測定を行うことができない。上記ウエット洗浄などを基板処理装置外で実行する場合には,上記のような測定装置にウエハを搬入する際に大気に露出しなければならないので,この場合にもウエハ表面には新たに自然酸化膜が発生する虞がある。 However, in the conventional particle measuring device (see, for example, Patent Document 4) and film thickness measuring device (see, Patent Document 5), the film thickness on the wafer is continuously removed after removing deposits such as a natural oxide film on the wafer. And particles cannot be measured. When the wet cleaning is performed outside the substrate processing apparatus, it must be exposed to the atmosphere when the wafer is loaded into the measurement apparatus as described above. There is a risk of film formation.

そこで,本発明は,このような問題に鑑みてなされたもので,その目的とするところは,水成分を用いず且つプラズマを用いずに基板上の自然酸化膜を含む付着物を除去し,その後に基板を大気に露出することなく,測定処理,成膜処理などを連続して実行することができる基板処理装置等を提供することにある。 Therefore, the present invention has been made in view of such problems, and its object is to remove deposits including a natural oxide film on a substrate without using a water component and without using plasma, It is an object of the present invention to provide a substrate processing apparatus or the like that can continuously perform measurement processing, film formation processing, and the like without exposing the substrate to the atmosphere.

上記課題を解決するために,本発明のある観点によれば,被処理基板に所定の処理を施す複数の処理室と,これらの処理室に共通に連結され,前記各処理室に対して前記被処理基板の搬出入を行う共通搬送室とを備える基板処理装置であって,前記複数の処理室は,前記被処理基板上に付着した自然酸化膜を含む付着物をプラズマによらないガス成分との化学反応と熱処理によって除去するための付着物除去処理室と,前記被処理基板上に成膜処理を施すための成膜処理室と,前記被処理基板上の測定処理を行うための測定処理室とを含むことを特徴とする基板処理装置が提供される。この場合,上記付着物除去処理室は,例えば前記被処理基板上の前記付着物とガス成分とを化学反応させて生成物を生成するための生成物生成処理室と,前記被処理基板上に形成された前記付着物の生成物を熱処理により除去するための生成物除去処理室との2つの処理室により構成される。また,上記成膜処理室は,例えば前記被処理基板に第1膜を成膜する第1膜成膜処理室と,前記第1膜上に第2膜を成膜する第2膜成膜処理室との2つの処理室により構成される。 In order to solve the above-described problems, according to one aspect of the present invention, a plurality of processing chambers for performing a predetermined process on a substrate to be processed and a common connection to these processing chambers, A substrate processing apparatus comprising a common transfer chamber for carrying in and out of a substrate to be processed, wherein the plurality of processing chambers are configured to remove deposits including a natural oxide film deposited on the substrate to be processed from gas components that do not depend on plasma. A deposit removal processing chamber for removing by chemical reaction and heat treatment, a film forming chamber for performing a film forming process on the substrate to be processed, and a measurement for performing a measurement process on the substrate to be processed A substrate processing apparatus including a processing chamber is provided. In this case, the deposit removal processing chamber includes, for example, a product generation processing chamber for generating a product by chemically reacting the deposit on the substrate to be processed and a gas component, and a substrate on the substrate to be processed. It is comprised by two process chambers with the product removal process chamber for removing the formed product of the said deposit | attachment by heat processing. The film formation chamber includes, for example, a first film formation chamber that forms a first film on the substrate to be processed, and a second film formation process that forms a second film on the first film. It consists of two processing chambers with a chamber.

このような本発明によれば,自然酸化膜を含む付着物をプラズマによらないガス成分との化学反応と熱処理によって除去するので,ウエット洗浄のような水成分を用いないため,被処理基板上にウォータマークなどが発生することを防止することができる。また,プラズマを用いないため,被処理基板にプラズマ起因のチャージアップダメージを負わせることを防止することができる。また,基板処理装置内で付着物除去処理の後に測定処理,成膜処理を連続して実行することができるので,成膜処理前に被処理基板上に自然酸化膜が新たに形成されることを防止することができる。このように,自然酸化膜を含む付着物を確実に除去することができるので,次の成膜処理によって被処理基板に形成される膜の密着性をより向上させることができ,強度もより向上させることができる。 According to the present invention, the deposit containing the natural oxide film is removed by a chemical reaction with a gas component that does not depend on plasma and heat treatment, so that no water component such as wet cleaning is used. It is possible to prevent the occurrence of a watermark or the like. Further, since plasma is not used, it is possible to prevent the substrate to be processed from being charged with damage due to plasma. In addition, since the measurement process and the film formation process can be continuously performed after the deposit removal process in the substrate processing apparatus, a natural oxide film is newly formed on the substrate to be processed before the film formation process. Can be prevented. As described above, the deposit including the natural oxide film can be surely removed, so that the adhesion of the film formed on the substrate to be processed can be further improved by the next film forming process, and the strength is further improved. Can be made.

また,上記測定処理室は,例えば前記被処理基板上の膜厚を測定する膜厚測定部と,前記被処理基板上のパーティクルを測定するパーティクル測定部とを備える。これにより,1つの測定処理室で,膜厚とパーティクルの両方を測定することができるので,スループットを向上させることができる。また,上記測定処理室は,さらに前記被処理基板の表面画像を撮像し,認識するための画像処理部を備えてもよい。これにより,被処理基板表面のパターンマッチングなどを行うことができるので,例えば膜厚やパーティクルを測定する被処理基板上の測定ポイントを特定することができる。 The measurement processing chamber includes, for example, a film thickness measuring unit that measures the film thickness on the substrate to be processed and a particle measuring unit that measures particles on the substrate to be processed. Thereby, since both a film thickness and a particle can be measured in one measurement processing chamber, the throughput can be improved. The measurement processing chamber may further include an image processing unit for capturing and recognizing a surface image of the substrate to be processed. Thereby, since pattern matching of the surface of the substrate to be processed can be performed, for example, a measurement point on the substrate to be processed for measuring a film thickness or particles can be specified.

上記課題を解決するために,本発明の別の観点によれば,被処理基板に所定の処理を施す複数の処理室と,これらの処理室に共通に連結される共通搬送室と,この共通搬送室内に設けられた前記被処理基板を搬送するための搬送機構とをそれぞれ備える複数の真空処理装置をパス部を介してそれぞれ連結してなる基板処理装置であって,前記複数の処理室は,前記被処理基板上に付着した自然酸化膜を含む付着物をプラズマによらないガス成分との化学反応と熱処理によって除去するための付着物除去処理室と,前記被処理基板上に成膜処理を施すための成膜処理室と,前記被処理基板上の測定処理を行うための測定処理室とを含むことを特徴とする基板処理装置が提供される。この場合,上記付着物除去処理室は,例えば前記被処理基板上の前記付着物とガス成分とを化学反応させて生成物を生成するための生成物生成処理室と,前記被処理基板上に形成された前記付着物の生成物を熱処理により除去するための生成物除去処理室との2つの処理室により構成される。また,上記成膜処理室は,例えば前記被処理基板に第1膜を成膜する第1膜成膜処理室と,前記第1膜上に第2膜を成膜する第2膜成膜処理室との2つの処理室により構成される。 In order to solve the above problems, according to another aspect of the present invention, a plurality of processing chambers for performing a predetermined process on a substrate to be processed, a common transfer chamber connected in common to these processing chambers, and this common A substrate processing apparatus comprising: a plurality of vacuum processing apparatuses each having a transport mechanism for transporting the target substrate provided in a transport chamber; , A deposit removing treatment chamber for removing deposits including a natural oxide film deposited on the substrate to be processed by a chemical reaction with a gas component that does not depend on plasma and heat treatment; and a film forming process on the substrate to be treated There is provided a substrate processing apparatus including a film formation processing chamber for performing a measurement process and a measurement processing chamber for performing a measurement process on the substrate to be processed. In this case, the deposit removal processing chamber includes, for example, a product generation processing chamber for generating a product by chemically reacting the deposit on the substrate to be processed and a gas component, and a substrate on the substrate to be processed. It is comprised by two process chambers with the product removal process chamber for removing the formed product of the said deposit | attachment by heat processing. The film formation chamber includes, for example, a first film formation chamber that forms a first film on the substrate to be processed, and a second film formation process that forms a second film on the first film. It consists of two processing chambers with a chamber.

このような本発明によっても,自然酸化膜を含む付着物をプラズマによらないガス成分との化学反応と熱処理によって除去するので,ウォータマークなどが発生せず,チャージアップダメージもなく,さらに自然酸化膜が新たに形成されることもない。このように,自然酸化膜を含む付着物を確実に除去することができるので,次の成膜処理によって被処理基板に形成される膜の密着性をより向上させることができ,強度もより向上させることができる。 Also according to the present invention, deposits including a natural oxide film are removed by a chemical reaction with a gas component that does not depend on plasma and heat treatment, so that no watermark is generated, no charge-up damage is caused, and further natural oxidation is achieved. A film is not newly formed. As described above, the deposit including the natural oxide film can be surely removed, so that the adhesion of the film formed on the substrate to be processed can be further improved by the next film forming process, and the strength is further improved. Can be made.

なお,上記成膜処理室は,前記被処理基板に第1膜を成膜する第1膜成膜処理室と,前記第1膜上に第2膜を成膜する第2膜成膜処理室とから構成される2つの処理室の組を複数含むようにしてもよい。これにより,例えば複数組の成膜処理装置で並列して成膜処理を実行することができるので,装置全体のスループットを大幅に向上させることができる。 The film formation chamber includes a first film formation chamber for forming a first film on the substrate to be processed and a second film formation chamber for forming a second film on the first film. A plurality of sets of two processing chambers may be included. As a result, for example, film forming processes can be performed in parallel by a plurality of sets of film forming processing apparatuses, so that the throughput of the entire apparatus can be greatly improved.

また,上記付着物除去処理室で処理される被処理基板は,例えばコンタクトホール又はビアホールが形成された被処理基板であり,前記成膜処理室は,例えば前記被処理基板に形成されたコンタクトホール又はビアホールの内側に第1バリア層を成膜する第1バリア層成膜処理室と,前記第1バリア層の上側に第2バリア層を成膜する第2バリア層成膜処理室とにより構成される。これによれば,被処理基板に形成されたコンタクトホール又はビアホールに付着した自然酸化膜などの付着物を確実に除去した上で,第1バリア層,第2バリア層を成膜することができるので,これらの密着性をより向上させることができ,強度もより向上させることができる。 Further, the substrate to be processed in the deposit removal processing chamber is, for example, a substrate to be processed in which a contact hole or a via hole is formed, and the film formation processing chamber is, for example, a contact hole formed in the substrate to be processed. Alternatively, the first barrier layer film forming process chamber for forming the first barrier layer inside the via hole and the second barrier layer film forming process chamber for forming the second barrier layer above the first barrier layer are configured. Is done. According to this, the first barrier layer and the second barrier layer can be formed after reliably removing deposits such as a natural oxide film adhering to the contact hole or via hole formed in the substrate to be processed. Therefore, these adhesiveness can be improved more and intensity | strength can also be improved more.

また,上記付着物除去処理室で処理される被処理基板は,例えばシリコン基板であり,前記成膜処理室は,前記被処理基板上に酸素ラジカルによってベース酸化膜層を成膜するベース酸化膜層成膜処理室と,前記ベース酸化膜層が形成された被処理基板に高誘電体ゲート酸化膜を成膜する高誘電体ゲート酸化膜成膜処理室とにより構成される。これによれば,シリコン基板に付着した自然酸化膜などの付着物を確実に除去した上で,ベース酸化膜層,高誘電体ゲート酸化膜を成膜することができるので,これらの密着性をより向上させることができ,強度もより向上させることができる。 Further, the substrate to be processed in the deposit removal processing chamber is, for example, a silicon substrate, and the film formation processing chamber is a base oxide film that forms a base oxide film layer on the substrate to be processed by oxygen radicals. A layer deposition processing chamber and a high dielectric gate oxide film deposition processing chamber for depositing a high dielectric gate oxide film on the substrate to be processed on which the base oxide film layer is formed. According to this, the base oxide film layer and the high dielectric gate oxide film can be formed after reliably removing the deposits such as the natural oxide film attached to the silicon substrate. The strength can be further improved.

上記課題を解決するために,本発明の別の観点によれば,前記被処理基板上に付着した自然酸化膜を含む付着物をプラズマによらないガス成分との化学反応と熱処理によって除去する付着物除去処理ステップと,前記付着物除去処理後に,前記被処理基板上の測定処理を行う測定処理ステップと,前記測定処理後に,前記被処理基板上に成膜処理を施す成膜処理ステップとを有することを特徴とする基板処理方法が提供される。この場合,上記付着物除去処理ステップは,例えば前記被処理基板上の前記付着物とガス成分とを化学反応させて生成物を生成するステップと,前記被処理基板上に形成された前記付着物の生成物を熱処理により除去するステップとを有する。また,上記成膜処理ステップは,例えば前記被処理基板に第1膜を成膜するステップと,前記第1膜上に第2膜を成膜するステップとを有する。 In order to solve the above-described problems, according to another aspect of the present invention, the deposit including the natural oxide film deposited on the substrate to be processed is removed by a chemical reaction with a gas component that does not depend on plasma and a heat treatment. A deposit removal processing step, a measurement processing step for performing measurement processing on the substrate to be processed after the deposit removal processing, and a film deposition processing step for performing film deposition processing on the substrate to be processed after the measurement processing. A substrate processing method is provided. In this case, the deposit removal processing step includes, for example, a step of chemically reacting the deposit on the substrate to be processed and a gas component to generate a product, and the deposit formed on the substrate to be processed. Removing the product by heat treatment. Further, the film forming process step includes, for example, a step of forming a first film on the substrate to be processed and a step of forming a second film on the first film.

このような本発明によれば,付着物除去処理(生成物生成処理,生成物除去処理)と,測定処理と,成膜処理とを連続実行することにより,自然酸化膜を含む付着物を確実に除去することができるので,次の成膜処理によって被処理基板に形成される膜の密着性をより向上させることができ,強度もより向上させることができる。 According to the present invention as described above, the deposit including the natural oxide film can be reliably obtained by continuously executing the deposit removal process (product generation process, product removal process), the measurement process, and the film formation process. Therefore, the adhesion of the film formed on the substrate to be processed can be further improved by the next film forming process, and the strength can be further improved.

また,上記測定処理ステップは,例えば付着物除去処理が適正に実行されたか否かを検査するための測定を行う。この場合,上記測定処理ステップは,前記被処理基板上において前記付着物除去処理が施された表面の膜厚測定を行うステップと,前記付着物除去処理が施された表面の付着物測定を行うステップとを1つの測定処理室内で実行することが好ましい。このように,膜厚とパーティクルとの両方を測定することによって,被処理基板上から自然酸化膜を含む付着物が除去されたか否かを確実に検査することができる。 Moreover, the said measurement process step performs the measurement for test | inspecting whether the deposit | attachment removal process was performed appropriately, for example. In this case, the measurement processing step includes a step of measuring the film thickness of the surface on which the deposit removal process has been performed on the substrate to be processed, and a measurement of the deposit on the surface on which the deposit removal process has been performed. Preferably, the steps are performed in one measurement processing chamber. In this way, by measuring both the film thickness and the particles, it is possible to reliably inspect whether or not the deposits including the natural oxide film have been removed from the substrate to be processed.

また,上記測定処理ステップは,さらに前記膜厚測定ステップと前記パーティクル測定ステップにより測定された測定結果に基づいて,前記付着物除去処理を実行するためのプロセスレシピを補正するようにしてもよい。これにより,実際の処理結果に応じた付着物除去処理ステップを実行することができるため,被処理基板上から自然酸化膜を含む付着物を確実に除去することができる。 The measurement processing step may further correct a process recipe for executing the deposit removal process based on the measurement results measured by the film thickness measurement step and the particle measurement step. Thereby, since the deposit removal processing step according to the actual processing result can be executed, deposits including the natural oxide film can be reliably removed from the substrate to be processed.

また,上記測定処理ステップは,さらに前記膜厚測定ステップと前記パーティクル測定ステップにより測定された測定結果に基づいて,次の前記成膜処理ステップを実行するか否かを判断するようにしてもよい。この場合,例えば前記膜厚測定ステップと前記パーティクル測定ステップにより測定された測定結果が許容範囲内にあれば,次の前記成膜処理ステップを実行可能と判断し,許容範囲になければ次の前記成膜処理ステップを実行不可能と判断するようにしてもよい。これにより,常に被処理基板上の自然酸化膜を含む付着物が除去された状態で次の成膜処理ステップを実行することができるので,被処理基板上に成膜された膜質の均一性を確保することができる。 The measurement processing step may further determine whether or not to execute the next film formation processing step based on the measurement results measured by the film thickness measurement step and the particle measurement step. . In this case, for example, if the measurement results measured by the film thickness measurement step and the particle measurement step are within an allowable range, it is determined that the next film forming process step can be performed. You may make it judge that the film-forming process step cannot be performed. As a result, the next film forming process step can be executed in a state where the deposits including the natural oxide film on the substrate to be processed are always removed, so that the uniformity of the film quality formed on the substrate to be processed can be improved. Can be secured.

また,上記測定処理ステップは,前記付着物除去処理が適正に実行されたか否かを検査するための測定と,次の前記成膜処理が施される下地膜の膜厚測定とを行うようにしてもよい。この場合,上記測定処理ステップは,前記被処理基板上において前記付着物除去処理が施された表面の膜厚測定及び前記成膜処理が施される下地膜の膜厚測定を行うステップと,前記付着物除去処理が施された表面の付着物測定を行うステップとを1つの測定処理室内で実行することが好ましい。これによれば,付着物除去処理が適正に実行されたか否かを検査するための膜厚測定と,次の成膜処理が施される下地膜の膜厚測定とを同時に実行できるので,測定処理にかかる時間を大幅に短縮することができる。 In the measurement processing step, measurement for inspecting whether or not the deposit removal process has been performed properly and measurement of the thickness of the underlying film on which the next film formation process is performed are performed. May be. In this case, the measurement processing step includes a step of measuring a film thickness of the surface on which the deposit removal process is performed on the substrate to be processed and a film thickness measurement of a base film on which the film formation process is performed, It is preferable to perform the step of measuring the deposit on the surface subjected to the deposit removing process in one measurement processing chamber. According to this, the film thickness measurement for inspecting whether or not the deposit removal process has been properly executed and the film thickness measurement of the base film to be subjected to the next film formation process can be performed simultaneously. Processing time can be greatly reduced.

上記課題を解決するために,本発明の別の観点によれば,前記被処理基板上に付着した自然酸化膜を含む付着物をプラズマによらないガス成分との化学反応と熱処理によって除去する付着物除去処理ステップと,前記付着物除去処理後に,前記被処理基板上に成膜処理を施す成膜処理ステップと,前記成膜処理後に,前記被処理基板上の測定処理を行う測定処理ステップとを有することを特徴とする基板処理方法が提供される。この場合,上記測定処理ステップは,例えば前記成膜処理により形成された膜の膜厚測定を行うステップを有する。これにより,成膜後の状態についても検査することができる。 In order to solve the above-described problems, according to another aspect of the present invention, the deposit including the natural oxide film deposited on the substrate to be processed is removed by a chemical reaction with a gas component that does not depend on plasma and a heat treatment. A deposit removal process step, a deposition process step for performing a deposition process on the target substrate after the deposit removal process, and a measurement process step for performing a measurement process on the target substrate after the deposition process; A substrate processing method is provided. In this case, the measurement processing step includes, for example, a step of measuring a film thickness of the film formed by the film forming process. Thereby, the state after film formation can also be inspected.

また,上記測定処理ステップは,さらに前記膜厚測定ステップにより測定された測定結果に基づいて,前記成膜処理を実行するためのプロセスレシピを補正するようにしてもよい。これにより,以降の被処理基板に対して常に適正な成膜処理を実行させることができる。 In the measurement process step, a process recipe for executing the film formation process may be corrected based on the measurement result measured in the film thickness measurement step. Thereby, it is possible to always execute an appropriate film forming process on the subsequent substrates to be processed.

上記課題を解決するために,本発明の別の観点によれば,前記被処理基板上の測定処理を行う測定処理ステップと,前記測定処理後に,前記被処理基板上に付着した自然酸化膜を含む付着物をプラズマによらないガス成分との化学反応と熱処理によって除去する付着物除去処理ステップと,前記付着物除去処理後に,前記被処理基板上に成膜処理を施す成膜処理ステップとを有することを特徴とする基板処理方法が提供される。このように,被処理基板の測定処理は,付着物除去処理前に行うようにしてもよい。 In order to solve the above problems, according to another aspect of the present invention, a measurement processing step for performing a measurement process on the substrate to be processed, and a natural oxide film adhering to the substrate to be processed after the measurement process are provided. A deposit removal treatment step for removing the deposits by a chemical reaction with a gas component that does not depend on plasma and heat treatment; and a film deposition treatment step for performing a film deposition process on the substrate to be processed after the deposit removal treatment. A substrate processing method is provided. As described above, the measurement processing of the substrate to be processed may be performed before the deposit removal processing.

上記課題を解決するために,本発明の別の観点によれば,コンピュータに,前記被処理基板上に付着した自然酸化膜を含む付着物をプラズマによらないガス成分との化学反応と熱処理によって除去する付着物除去処理ステップと,前記被処理基板上の測定処理を行う測定処理ステップと,前記付着物が除去された前記被処理基板上に成膜処理を施す成膜処理ステップとを実行させるためのプログラムが提供される。 In order to solve the above-described problems, according to another aspect of the present invention, a computer includes a deposit including a natural oxide film deposited on the substrate to be processed by a chemical reaction with a gas component that does not depend on plasma and a heat treatment. An adhesion removing process step to be removed; a measurement processing step for performing a measurement process on the substrate to be processed; and a film forming process step for performing a film forming process on the substrate to be processed from which the deposit has been removed. A program is provided.

上記課題を解決するために,本発明の別の観点によれば,コンピュータに,前記被処理基板上に付着した自然酸化膜を含む付着物をプラズマによらないガス成分との化学反応と熱処理によって除去する付着物除去処理ステップと,前記被処理基板上の測定処理を行う測定処理ステップと,前記付着物が除去された前記被処理基板上に成膜処理を施す成膜処理ステップとを実行させるためのプログラムを記録したコンピュータ読み取り可能な記録媒体が提供される。 In order to solve the above-described problems, according to another aspect of the present invention, a computer includes a deposit including a natural oxide film deposited on the substrate to be processed by a chemical reaction with a gas component that does not depend on plasma and a heat treatment. An adhesion removing process step to be removed; a measurement processing step for performing a measurement process on the substrate to be processed; and a film forming process step for performing a film forming process on the substrate to be processed from which the deposit has been removed. A computer-readable recording medium on which a program for recording is recorded is provided.

このようなプログラム又は記録媒体に記録されたプログラムによれば,本発明にかかる付着物除去処理(生成物生成処理,生成物除去処理)と,測定処理と,成膜処理とを連続実行することができる。これにより,自然酸化膜を含む付着物を確実に除去することができるので,次の成膜処理によって被処理基板に形成される膜の密着性をより向上させることができ,強度もより向上させることができる。 According to such a program or a program recorded on a recording medium, the deposit removal processing (product generation processing, product removal processing), measurement processing, and film formation processing according to the present invention are continuously executed. Can do. As a result, the deposits including the natural oxide film can be surely removed, so that the adhesion of the film formed on the substrate to be processed by the next film forming process can be further improved and the strength can be further improved. be able to.

以上説明したように本発明によれば,自然酸化膜を含む付着物をプラズマによらないガス成分との化学反応と熱処理によって除去した上で,測定処理,成膜処理を連続して実行することができるので,水成分を用いず且つプラズマを用いずに基板上の自然酸化膜を含む付着物を除去し,その後に基板を大気に露出することなく,成膜処理などを連続して実行することができる。このため,ウォータマークなどが発生せず,チャージアップダメージもなく,さらに自然酸化膜が新たに形成されることもなく,自然酸化膜を含む付着物を確実に除去することができる。従って,次の成膜処理によって被処理基板に形成される膜の密着性をより向上させることができ,強度もより向上させることができる。 As described above, according to the present invention, the deposit including the natural oxide film is removed by the chemical reaction with the gas component that does not depend on the plasma and the heat treatment, and then the measurement process and the film forming process are continuously performed. Therefore, it is possible to remove deposits including a natural oxide film on the substrate without using water components and without using plasma, and then continuously perform film formation without exposing the substrate to the atmosphere. be able to. For this reason, a watermark or the like is not generated, there is no charge-up damage, and a natural oxide film is not newly formed, and the deposits including the natural oxide film can be reliably removed. Therefore, the adhesion of the film formed on the substrate to be processed by the next film formation process can be further improved, and the strength can be further improved.

以下に添付図面を参照しながら,本発明の好適な実施の形態について詳細に説明する。なお,本明細書及び図面において,実質的に同一の機能構成を有する構成要素については,同一の符号を付することにより重複説明を省略する。 Hereinafter, preferred embodiments of the present invention will be described in detail with reference to the accompanying drawings. In the present specification and drawings, components having substantially the same functional configuration are denoted by the same reference numerals, and redundant description is omitted.

(第1実施形態にかかる基板処理装置の構成例)

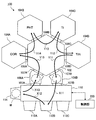

先ず,本発明の第1実施形態にかかる基板処理装置の構成例を図面を参照しながら説明する。図1は第1実施形態にかかる基板処理装置の1例を示す概略構成図である。図1に示すように,この基板処理装置100は,略多角形状(例えば六角形状)に形成された1つ共通搬送室102と,真空引き可能に構成された複数(例えば4つ)の処理室104A〜104Dとを備える真空処理装置を有する。

(Configuration Example of Substrate Processing Apparatus According to First Embodiment)

First, a configuration example of a substrate processing apparatus according to a first embodiment of the present invention will be described with reference to the drawings. FIG. 1 is a schematic configuration diagram illustrating an example of a substrate processing apparatus according to the first embodiment. As shown in FIG. 1, this

各処理室104A〜104Dは共通搬送室102の周囲にそれぞれゲートバルブ106A〜106Dを介して連結している。また,各処理室104A〜104Dには被処理基板例えば半導体ウエハ(以下,単に「ウエハ」とも称する。)Wを載置する載置台105A〜105Dが設けられている。各処理室104A〜104Dはそれぞれ載置台105A〜105Dに載置されたウエハWに対して所定の処理を施し得るようになっている。

The

共通搬送室102には,真空引き可能に構成された2つのロードロック室108A,108Bを介して略長方形状の搬入側搬送室110が連結されている。ロードロック室108A,108Bと共通搬送室102及び搬入側搬送室110との連結部にはそれぞれゲートバルブ107A,107Bが介在している。

The

上記搬入側搬送室110には,ウエハWを複数枚収容できるカセットを載置する例えば3つの導入ポート112A〜112C及びウエハWを回転してこの偏心量を光学的に求めて位置合わせを行うオリエンタ114が連結されている。

In the carry-in

搬入側搬送室110内には,ウエハWを保持する2つのピック116A,116Bを有して屈伸,旋回,昇降及び直線移動可能に構成された搬入側搬送機構116が設けられている。また,共通搬送室102内には,ウエハWを保持する2つのピック118A,118Bを有して屈伸及び旋回可能になされた搬送機構118が設けられている。基板処理装置100には,制御部200が接続されており,この制御部200により基板処理装置100の各部が制御されるようになっている。

In the carry-in

なお,共通搬送室102と2つのロードロック室の内のいずれか一方,例えばロードロック室108Aとの連結部の搬送口109AはウエハWを共通搬送室102内へ専用に搬入する搬入口として用いられ,他方のロードロック室108Bとの連結部の搬送口109BはウエハWを共通搬送室102から外へ専用に搬出する搬出口として用いられる。

It should be noted that one of the

(ウエハ処理の具体例)

本実施形態にかかる基板処理装置100は,ウエハ上の付着物(例えばコンタミネーションや自然酸化膜など)をプラズマによらないガス成分との化学反応と熱処理によって除去する付着物除去処理と,この付着物除去処理が施されたウエハ上に所定の薄膜を形成する成膜処理とを連続して実行する。

(Specific example of wafer processing)

The

(付着物除去処理)

先ず,成膜処理の前処理として実行する付着物除去処理について詳細に説明する。本実施形態では,水成分を用いず且つプラズマを用いない付着物除去処理を実行する。この付着物除去処理は,例えばウエハに付着した自然酸化膜を含む付着物とガス成分とを化学反応させて生成物を生成する生成物生成処理と,ウエハ上に生成された生成物を熱処理により除去する生成物除去処理との2段階の処理によって構成される。

(Adherent removal processing)

First, the deposit removal process executed as a pre-process of the film forming process will be described in detail. In this embodiment, the deposit removal process is performed without using water components and without using plasma. This deposit removal processing includes, for example, a product generation process that generates a product by chemically reacting a deposit including a natural oxide film attached to a wafer and a gas component, and a product generated on the wafer by heat treatment. It consists of a two-stage process including a product removal process to be removed.

生成物生成処理は例えばCOR(Chemical Oxide Removal)処理であり,生成物除去処理は例えばPHT(Post Heat Treatment)処理である。COR処理は,ウエハ上に付着した付着物例えば自然酸化膜などの酸化膜と例えばアンモニア(NH3)ガス及び弗化水素(HF)ガスなどのガス分子とを化学反応させて生成物(主に(NH4)2SiF6)を生成する処理である。PHT処理は,COR処理が施されたウエハを加熱して,COR処理の化学反応によってウエハ上に生成した生成物を気化(昇華)させてウエハから除去する処理である。 The product generation process is, for example, a COR (Chemical Oxide Removal) process, and the product removal process is, for example, a PHT (Post Heat Treatment) process. The COR processing is performed by chemically reacting an oxide film such as a natural oxide film deposited on a wafer with gas molecules such as ammonia (NH 3 ) gas and hydrogen fluoride (HF) gas. This is a process for generating (NH 4 ) 2 SiF 6 ). The PHT process is a process in which a wafer subjected to the COR process is heated to vaporize (sublimate) a product generated on the wafer by a chemical reaction of the COR process and remove it from the wafer.

このように,COR処理及びPHT処理,特にCOR処理は水成分を用いず且つプラズマを用いずにウエハの自然酸化膜などの付着物を除去することができるため,プラズマレスエッチング処理及びドライクリーニング処理(乾燥洗浄処理)に相当する。 As described above, the COR process and the PHT process, particularly the COR process, can remove deposits such as a natural oxide film on the wafer without using a water component and without using a plasma. This corresponds to (dry cleaning treatment).

例えばCOR処理及びPHT処理においてアンモニアガス及び弗化水素ガスを反応ガスとして用いることにより,以下の化学反応を利用して自然酸化膜などの付着物を除去する。 For example, by using ammonia gas and hydrogen fluoride gas as reaction gases in COR processing and PHT processing, deposits such as a natural oxide film are removed using the following chemical reaction.

[COR処理の化学反応式]

SiO2+4HF → SiF4+2H2O↑

SiF4+2NH3+2HF → (NH4)2SiF6

[Chem chemical reaction formula]

SiO 2 + 4HF → SiF 4 + 2H 2 O ↑

SiF 4 + 2NH 3 + 2HF → (NH 4 ) 2 SiF 6

[PHT処理の化学反応式]

(NH4)2SiF6 → SiF4↑+2NH3↑+2HF↑

[Chemical reaction formula of PHT treatment]

(NH 4 ) 2 SiF 6 → SiF 4 ↑ + 2NH 3 ↑ + 2HF ↑

上述した化学反応を利用したCOR処理及びPHT処理は,以下の特性を有する。なお,PHT処理においては,N2及びH2も若干量発生する。 The COR process and the PHT process using the chemical reaction described above have the following characteristics. In the PHT process, a small amount of N 2 and H 2 is also generated.

[COR処理及びPHT処理の特性]

(1)熱酸化膜の選択比(除去速度)が高い。具体的にはCOR処理及びPHT処理は,熱酸化膜の選択比が高い一方,ポリシリコンの選択比が低い。従って,熱酸化膜であるSiO2膜からなる絶縁膜の表層やSiO2膜と同様の特性を有する疑似SiO2層又はシリコン表層の自然酸化膜及びウォータマークを効率よく除去することができる。

[Characteristics of COR processing and PHT processing]

(1) The thermal oxide film has a high selectivity (removal rate). Specifically, in the COR process and the PHT process, the selectivity of the thermal oxide film is high, while the selectivity of polysilicon is low. Therefore, the surface layer of the insulating film made of the SiO 2 film, which is a thermal oxide film, and the natural oxide film and watermark on the pseudo-SiO 2 layer or silicon surface layer having the same characteristics as the SiO 2 film can be efficiently removed.

(2)表層や疑似SiO2層が除去された絶縁膜の表面における自然酸化膜の成長速度が遅い。具体的にはウェットエッチングによって表面が露出したウエハの表面においては,厚さ3オングストロームの自然酸化膜の成長時間が略10分であるのに対して,COR処理及びPHT処理によって表面が露出したウエハの表面においては,厚さ3オングストロームの自然酸化膜の成長時間は略2時間以上である。従って,COR処理及びPHT処理による洗浄工程では,ウォータマークが新たに発生することはなく,さらに洗浄工程後の時間経過による自然酸化膜の成長も抑制されるので,半導体デバイスの信頼性を向上させることができる。 (2) The growth rate of the natural oxide film on the surface of the insulating film from which the surface layer and the pseudo SiO 2 layer are removed is slow. Specifically, on the surface of a wafer whose surface is exposed by wet etching, the growth time of a natural oxide film having a thickness of 3 angstroms is about 10 minutes, whereas the wafer whose surface is exposed by COR processing and PHT processing. On the surface, the growth time of a natural oxide film having a thickness of 3 angstroms is approximately 2 hours or more. Therefore, in the cleaning process by the COR process and the PHT process, a new watermark is not generated, and the growth of the natural oxide film with the passage of time after the cleaning process is suppressed, so that the reliability of the semiconductor device is improved. be able to.

(3)ドライ環境において反応が進行する。具体的にはCOR処理において水を反応に用いることはない。またCOR処理によって水分子が発生したとしても,COR処理は略真空状態で行われるため,水分子は気体状態で発生する。従って,水分子が液体状態でウエハに付着することはないので,ウエハの表面にウォータマーク等が発生することはない。またPHT処理は高温下で行われるため,ウエハの表面にウォータマーク等が発生することはなく,表面が露出したウエハの表面にOH基が配されることもない。従って,ウエハの表面が不動態化(passivate)されて親水性になることがないので,ウエハの表面は吸湿することもないため,半導体デバイスの配線信頼性の低下を防止することができる。 (3) The reaction proceeds in a dry environment. Specifically, water is not used for the reaction in the COR treatment. Further, even if water molecules are generated by the COR process, the COR process is performed in a substantially vacuum state, so that the water molecules are generated in a gas state. Accordingly, since water molecules do not adhere to the wafer in a liquid state, a watermark or the like is not generated on the surface of the wafer. Further, since the PHT process is performed at a high temperature, a watermark or the like is not generated on the surface of the wafer, and OH groups are not arranged on the surface of the wafer where the surface is exposed. Therefore, since the surface of the wafer is not passivated and becomes hydrophilic, the surface of the wafer does not absorb moisture, thereby preventing a reduction in wiring reliability of the semiconductor device.

(4)生成物(錯体)の生成量は所定時間が経過すると緩和する。具体的には所定時間が経過すると,それ以降はウォータマークをアンモニアガス及び弗化水素ガスの混合気体に暴露し続けても,生成物の生成量は増加しない。また生成物の生成量は,混合気体の圧力,体積流量比等の混合気体のパラメータによって決定される。従って,ウォータマークの除去量の制御を容易に行うことができる。 (4) The production amount of the product (complex) is relaxed after a predetermined time. Specifically, after a predetermined time has elapsed, the amount of product produced does not increase even if the watermark is continuously exposed to a mixed gas of ammonia gas and hydrogen fluoride gas. The amount of product produced is determined by the parameters of the gas mixture, such as the pressure of the gas mixture and the volumetric flow ratio. Therefore, it is possible to easily control the removal amount of the watermark.

(5)パーティクルの発生が非常に少ない。具体的には例えば2000枚のウエハにおける自然酸化膜の除去を実行しても,処理室内や処理室の内壁等にパーティクルの付着がほとんど観察されない。従って半導体デバイスにおいてパーティクルを介した配線の短絡等が発生することがなく,半導体デバイスの信頼性を向上させることができる。 (5) Generation of particles is very small. Specifically, for example, even when the natural oxide film is removed from 2000 wafers, adhesion of particles is hardly observed on the processing chamber or the inner wall of the processing chamber. Therefore, there is no occurrence of a short circuit of wiring via particles in the semiconductor device, and the reliability of the semiconductor device can be improved.

(成膜処理)

次に,成膜処理について説明する。ここでは,成膜処理としてウエハに形成されたコンタクトホール又はビアホールの内側に例えば第1膜としてのTi系膜及び第2膜としてのTiN系膜の2層構造のバリア層を成膜する成膜処理を実行する。このような成膜処理を実行する前に,上述したような水成分を用いず且つプラズマを用いない付着物除去処理を実行することにより,膜の密着性,強度を向上させることができる。また,本実施形態にかかる付着物除去処理ではプラズマを用いないため,ウエハの下地膜にプラズマ起因のチャージアップダメージを負わせることを防止することができるので,ダメージのない配線加工を行うことができ,また良好なコンタクト抵抗を有する膜を成膜することができる。

(Deposition process)

Next, the film forming process will be described. Here, as a film formation process, a barrier layer having a two-layer structure, for example, a Ti film as a first film and a TiN film as a second film is formed inside a contact hole or via hole formed on a wafer. Execute the process. Before performing such a film forming process, the adhesion removal and the strength of the film can be improved by executing the deposit removing process without using a water component and without using plasma as described above. In addition, since the deposit removal process according to the present embodiment does not use plasma, it is possible to prevent charge-up damage caused by plasma from being applied to the underlying film of the wafer, so that wiring processing without damage can be performed. In addition, a film having good contact resistance can be formed.

半導体デバイスの製造においては,最近の高密度化および高集積化の要請に対応して,回路構成を多層配線構造にする傾向にある。このため,下層の半導体デバイスと上層の配線層との接続部であるコンタクトホールや,上下の配線層同士の接続部であるビアホールなどの層間の電気的接続のための埋め込み技術が重要になっている。このようなコンタクトホールやビアホールの埋め込みには,一般的にAl(アルミニウム)やW(タングステン),あるいはこれらを主体とする合金が用いられる。このような金属や合金と下層のシリコン(Si)基板やポリシリコン(poly−Si)層とのコンタクトを形成するために,これらの埋め込みに先立ってコンタクトホールやビアホールの内側にTi系膜(例えばTi膜)とTiN系膜(例えばTiN膜)を成膜することが行われている。 In the manufacture of semiconductor devices, the circuit configuration tends to be a multilayer wiring structure in response to the recent demand for higher density and higher integration. For this reason, an embedding technique for electrical connection between layers such as a contact hole which is a connection portion between a lower semiconductor device and an upper wiring layer and a via hole which is a connection portion between upper and lower wiring layers becomes important. Yes. In general, Al (aluminum), W (tungsten), or an alloy mainly composed of these is used for filling such contact holes and via holes. In order to form a contact between such a metal or alloy and the underlying silicon (Si) substrate or polysilicon (poly-Si) layer, a Ti-based film (for example, inside the contact hole or via hole prior to filling them) A TiN film) and a TiN-based film (for example, a TiN film) are formed.

これらの膜の成膜には,デバイスの微細化および高集積化が進んでも電気抵抗が増加せず良質な膜を形成することができ,しかもステップカバレッジを良好にすることができるCVD(Chemical Vapor Deposition:化学気相成長)法が用いられている。そして,例えばTiCl4を反応ガスとしてCVD法によりTi膜を成膜することにより下地のシリコン基板と反応させてコンタクトホールの底のシリコン拡散層上に自己整合的にTiSi2を選択成長させ,良好なオーミック抵抗を得ている。 These films can be formed by CVD (Chemical Vapor), which is capable of forming high-quality films without increasing the electrical resistance even when device miniaturization and high integration are advanced, and also providing good step coverage. Deposition (chemical vapor deposition) method is used. Then, for example, a Ti film is formed by a CVD method using TiCl 4 as a reaction gas to react with the underlying silicon substrate to selectively grow TiSi 2 in a self-aligned manner on the silicon diffusion layer at the bottom of the contact hole. Ohmic resistance is obtained.

このようなCVD−Ti膜を成膜する場合,反応ガスとしては上述したようにTiCl4ガスが一般的に用いられ,還元ガスとしてH2ガス等が用いられる。このTiCl4ガスの結合エネルギーはかなり高く,熱エネルギー単独では1200℃程度の高温でなければ分解しないので,プラズマエネルギーを併用するプラズマCVD法によって,通常,プロセス温度650℃程度で成膜を行っている。 When such a CVD-Ti film is formed, TiCl 4 gas is generally used as the reaction gas as described above, and H 2 gas or the like is used as the reducing gas. The binding energy of this TiCl 4 gas is quite high, and thermal energy alone does not decompose unless it is a high temperature of about 1200 ° C. Therefore, a film is usually formed at a process temperature of about 650 ° C. by plasma CVD using plasma energy. Yes.

一方,このようなメタル成膜においては,良好なコンタクト抵抗を得るために,成膜処理に先立って,下地の上に形成された自然酸化膜を除去する処理が施される。このような自然酸化膜の除去は一般的に希弗酸により行われてきたが,水素ガスとアルゴンガスを用いて誘導結合プラズマを形成することにより,自然酸化膜を除去するものもある。 On the other hand, in such metal film formation, in order to obtain good contact resistance, a process of removing a natural oxide film formed on the base is performed prior to the film formation process. Such removal of the natural oxide film has been generally carried out with dilute hydrofluoric acid, but there is also a method of removing the natural oxide film by forming inductively coupled plasma using hydrogen gas and argon gas.

しかしながら,従来のプラズマCVD法でTi膜を成膜すると,粒径が不均一なTiSi2結晶が形成される傾向がある。すなわち,従来はTiSi2膜の成膜に先立ってアルゴンプラズマを用いたドライ洗浄によって自然酸化膜除去を行っていたので,Si拡散層表面がダメージを受けて不均一にアモルファス化しており,その状態でプラズマCVDでTi膜を成膜すると,形成されるTiSi2結晶が一層不均一になってしまう。そして,このような不均一な状態のTiSi2結晶は比較的疎に存在するため,比抵抗が高いとともにTiSi2膜と下地との接触が不均一となる。したがって,コンタクト抵抗が増加してしまう。 However, when a Ti film is formed by a conventional plasma CVD method, TiSi 2 crystals having a non-uniform grain size tend to be formed. In other words, since the natural oxide film was removed by dry cleaning using argon plasma prior to the formation of the TiSi 2 film, the Si diffusion layer surface was damaged and became non-uniformly amorphous. When a Ti film is formed by plasma CVD, the TiSi 2 crystal to be formed becomes more uneven. Since such a non-uniform TiSi 2 crystal exists relatively sparsely, the specific resistance is high and the contact between the TiSi 2 film and the base becomes non-uniform. Therefore, the contact resistance increases.

この点,本実施形態では,前処理として水成分を用いず且つプラズマを用いない付着物除去処理(例えばCOR処理及びPHT処理)によって,ウエハ上に形成されたコンタクトホール又はビアホール内の自然酸化膜を除去した上で,Ti系膜及びTiN系膜を成膜する。これにより,Ti系膜及びTiN系膜を成膜する前の下地にプラズマ起因のチャージアップダメージを負わせることを防止することができるので,プラズマCVD法でTi膜を成膜しても,ダメージのない配線加工を行うことができ,また良好なコンタクト抵抗を有する膜を成膜することができる。また,Ti系膜及びTiN系膜の各膜の密着性,強度も向上させることができる。 In this respect, in the present embodiment, the natural oxide film in the contact hole or via hole formed on the wafer by the deposit removal process (for example, the COR process and the PHT process) that does not use the water component and does not use the plasma as the pretreatment. Then, a Ti film and a TiN film are formed. As a result, it is possible to prevent the plasma base charge-up damage from being applied to the base before the Ti-based film and TiN-based film are formed. Wiring can be performed without any problem, and a film having good contact resistance can be formed. In addition, the adhesion and strength of each of the Ti film and the TiN film can be improved.

ここで,第1膜成膜処理としてのTi系膜成膜処理の具体例を説明する。Ti系膜成膜処理としては,例えば上述したようにプラズマCVDによりTi膜を成膜するCVD−Ti膜成膜処理を行う。CVD−Ti膜成膜処理は例えばTiCl4ガスの供給とArガスの供給とH2ガスの供給とプラズマ発生とを同時期に行う工程と,NH3ガスの供給とArガスの供給とH2ガスの供給とプラズマ発生とを同時期に行う工程とによって,CVD−Ti膜を成膜する。この場合,温度は650℃に設定する。 Here, a specific example of the Ti-based film forming process as the first film forming process will be described. As the Ti-based film forming process, for example, as described above, a CVD-Ti film forming process for forming a Ti film by plasma CVD is performed. The CVD-Ti film forming process includes, for example, a process of supplying TiCl 4 gas, Ar gas, H 2 gas, and generating plasma at the same time, supplying NH 3 gas, supplying Ar gas, and H 2. A CVD-Ti film is formed by a process of supplying gas and generating plasma at the same time. In this case, the temperature is set to 650 ° C.

なお,Ti系膜成膜処理としては,上記に限られるものではなく,上記650℃よりも低温の400℃〜450℃に設定してプラズマCVDによりTi膜を成膜するSFD(Sequential Flow Deposition)−Ti膜成膜処理を実行してもよい。SFD−Ti膜成膜処理は例えばTiCl4ガスの供給とArガスの供給とH2ガスの供給とプラズマ発生とを同時期に行ってTiCl4ガスの供給を止める工程を複数回繰返した後に,NH3ガスの供給とArガスの供給とH2ガスの供給とプラズマ発生とを同時期に行う工程を行うことによって,SFD−Ti膜を成膜する。 The Ti-based film forming process is not limited to the above, and SFD (Sequential Flow Deposition) is used to form a Ti film by plasma CVD at a temperature lower than 650 ° C., which is set to 400 ° C. to 450 ° C. A Ti film forming process may be executed. In the SFD-Ti film forming process, for example, a TiCl 4 gas supply, an Ar gas supply, a H 2 gas supply, and a plasma generation are performed at the same time to stop the supply of TiCl 4 gas a plurality of times. An SFD-Ti film is formed by performing a process of supplying NH 3 gas, Ar gas, H 2 gas, and generating plasma at the same time.

さらに,他のTi膜成膜処理として,原子層堆積(ALD:Atomic Layered Deposition)の手法を用いたALD−Ti膜成膜処理を実行してもよい。ALD−Ti膜成膜処理としては,例えばTiCl4ガスを供給した後に,Arガスの供給とH2ガスの供給とプラズマ生成とを行う工程を複数回繰返した後に,NH3ガスの供給とArガスの供給とH2ガスの供給とプラズマ発生とを同時期に行う工程を行うことによって,ALD−Ti膜を成膜する。 Further, as another Ti film forming process, an ALD-Ti film forming process using an atomic layer deposition (ALD) technique may be executed. As the ALD-Ti film forming process, for example, after supplying TiCl 4 gas, the process of supplying Ar gas, supplying H 2 gas, and generating plasma is repeated a plurality of times, then supplying NH 3 gas and Ar An ALD-Ti film is formed by performing a process of supplying gas, supplying H 2 gas, and generating plasma at the same time.

また,TiCl4ガスの供給とTiCl4ガスの供給とArガスの供給とプラズマ生成を同時期に行った後にH2ガスの供給を供給する工程を複数回繰返した後,NH3ガスの供給とArガスの供給とH2ガスの供給とプラズマ発生とを同時期に行う工程を行うことによって,ALD−Ti膜を成膜するようにしてもよい。 Further, after repeating several times the step of supplying the supply of the H 2 gas supply and plasma generation supply and Ar gas supply and TiCl 4 gas TiCl 4 gas after the same time, the supply of NH 3 gas The ALD-Ti film may be formed by performing a process of supplying Ar gas, supplying H 2 gas, and generating plasma at the same time.

さらに,TiCl4ガスの供給とTiCl4ガスの供給とArガスの供給とプラズマ生成を同時期に行った後にH2ガスの供給とArガスの供給とプラズマ発生を同時期に行う工程を複数回繰返した後,NH3ガスの供給とArガスの供給とH2ガスの供給とプラズマ発生とを同時期に行う工程を行うことによって,ALD−Ti膜を成膜するようにしてもよい。 Further, a plurality of steps for supplying the plasma generation supply and Ar gas of the H 2 gas at the same time times after the supply and plasma generation supply and Ar gas supply and TiCl 4 gas TiCl 4 gas at the same time After repeating, an ALD-Ti film may be formed by performing a process of supplying NH 3 gas, Ar gas, H 2 gas, and generating plasma at the same time.

次に,第2膜成膜処理としてのTiN系膜成膜処理は,例えば上述したようにTiCl4ガス,NH3ガスを反応ガスとして用い,設定温度を500〜610℃に設定として,プラズマCVDによりTi膜を成膜する。 Next, the TiN-based film forming process as the second film forming process is performed by using, for example, plasma CVD with TiCl 4 gas and NH 3 gas as reaction gases and a set temperature of 500 to 610 ° C. as described above. A Ti film is formed by the above.

(処理室の構成例)

次に,上記のような処理を実行するための基板処理装置100における処理室の構成例を説明する。本実施形態にかかる基板処理装置100は,上述したようにウエハ上の自然酸化膜などの付着物を,水成分を用いず且つプラズマによらないガス成分との化学反応と熱処理によって除去する付着物除去処理と,この付着物除去処理が施されたウエハ上に所定の薄膜を形成する成膜処理とを連続して実行する。

(Configuration example of processing chamber)

Next, a configuration example of a processing chamber in the

このため,処理室104A〜104Dのうち少なくとも2つの処理室の一方を付着物除去処理室として構成し,他方の処理室を成膜処理室として構成する。また,付着物除去処理は上述したように複数段階の処理を連続して実行するようにしてもよく,この場合には付着物除去処理室を複数の処理室で構成してもよい。具体的には上述したような生成物生成処理(例えばCOR処理)と,生成物除去処理(例えばPHT処理)との2段階の処理によって行う場合には処理室104A〜104Dのうちの2つの処理室を付着物除去処理室として構成する。この場合,一方の処理室を生成物生成処理室として構成し,他方の処理室を生成物除去処理室として構成する。

For this reason, one of at least two processing chambers among the

また成膜処理は異なる膜を連続して成膜するようにしてもよく,この場合には成膜処理室を複数の処理室で構成してもよい。具体的には第1膜(例えばTi系膜)と,第2膜(例えばTiN系膜)を連続して成膜する場合には処理室104A〜104Dのうちの2つの処理室を成膜処理室として構成する。この場合,一方の処理室を第1膜を成膜する第1膜成膜処理室として構成し,他方の処理室を第2膜を成膜する第2膜成膜処理室として構成する。このように,基板処理装置100によって実行される付着物除去処理と成膜処理の内容に応じて各処理室104A〜104Dの構成が決定される。

In the film forming process, different films may be successively formed. In this case, the film forming process chamber may be composed of a plurality of process chambers. Specifically, in the case where a first film (for example, a Ti-based film) and a second film (for example, a TiN-based film) are continuously formed, two of the

ここで,例えばコンタクトホール又はビアホールが形成されたウエハWを基板処理装置100に導入し,このウエハWに対して上述したような付着物除去処理としてのCOR処理,PHT処理を連続して実行した後,成膜処理としてのTi膜成膜処理,TiN膜成膜処理を連続して実行する場合の基板処理装置100における処理室の構成例を図2に示す。

Here, for example, a wafer W in which contact holes or via holes are formed is introduced into the

図2に示す構成例は,処理室104A,104B,104C,104DをそれぞれCOR処理室,PHT処理室,Ti膜成膜処理室,TiN膜成膜処理室として構成したものである。各処理室104A〜104Dにおける処理はそれぞれ,後述する制御部200のEC(装置制御部)300に設けられるプログラムデータ記憶手段360に記憶されたプロセス処理プログラム364に基づいて実行される。すなわち,EC300のCPU310はプロセス処理プログラム364から必要な処理プログラムを読出し,処理データ記憶手段370に記憶されるプロセス処理情報(例えばプロセスレシピ情報)374から必要な情報を読み出して各処理を実行する。なお,制御部200の構成の詳細は後述する。

In the configuration example shown in FIG. 2, the

(基板搬送処理の具体例)

次に,図2に示すような構成の基板処理装置100におけるウエハWの搬送処理について説明する。ウエハWに対する各処理室104A〜104Dにおける処理の順序が上記の順序で行われるので,ウエハWの搬送経路は図2に示す実線矢印のようになる。このようなウエハ搬送処理は,制御部200のEC(装置制御部)300に設けられる後述のプログラムデータ記憶手段360に記憶された搬送処理プログラム362に基づいて実行される。すなわち,EC300のCPU310は処理データ記憶手段370に記憶される搬送処理情報(例えば搬送経路情報)372から必要な情報を読み出して搬送処理プログラム362を実行することによって,ウエハの搬送処理を実行する。

(Specific example of substrate transfer processing)

Next, the wafer W transfer process in the

ここでは一例として中央の導入ポート112Bに設置したカセット(キャリアも含む)から例えばコンタクトホール又はビアホールが形成された処理前ウエハWが取り出されるものとし,また2つのロードロック室108A,108Bのうちのいずれか一方のロードロック室,例えばロードロック室108Aを処理前ウエハWの搬入用に用い,他方のロードロック室108Bを処理済ウエハWの搬出用に用いる。今,各処理室104A〜104D内にはそれぞれウエハWが収容されてそれぞれの処理が終了しているか,又はほぼ終了しかけているものとする。

Here, as an example, it is assumed that, for example, a pre-process wafer W in which a contact hole or a via hole is formed is taken out from a cassette (including a carrier) installed in the

先ず,搬入側搬送室110内の搬送処理について説明する。ロードロック室108B内には,処理室104Dでの処理が終了した処理済のウエハWが収容されているものとすると,この処理済ウエハWは,搬入側搬送機構116により搬送経路X11に示すように中央の導入ポート112Bへ搬送して収容される。

First, the transfer process in the carry-in

また,中央の導入ポート112Bに収容されている処理前のウエハWは,搬入側搬送機構116により搬送経路X12に示すようにオリエンタ114へ搬送され,ここでウエハWの位置合わせをした後に,再度搬入側搬送機構116により搬送経路X13に示すように位置合わせ後のウエハWを他方のロードロック室108A内へ収容し,待機させておく。以上の操作が,ウエハWの処理が進む毎に繰り返し行われる。

The unprocessed wafer W accommodated in the

次に,共通搬送室102内でのウエハの搬送処理について説明する。先ず,搬送機構118により処理室104Dに収容されている処理済のウエハWを取りに行き,搬送経路Y11に示すようにこれを空き状態のロードロック室108B内に置く。次いで,搬送機構118により処理室104C内に収容されている処理済のウエハWを取りに行き,搬送経路Y12に示すようにこれを空き状態の処理室104D内へ搬入して置き,処理室104D内での処理を開始する。

Next, wafer transfer processing in the

続いて,搬送機構118により処理室104Bに収容されている処理済のウエハWを取りに行き,搬送経路Y13に示すようにこれを空き状態の処理室104C内へ搬入して置き,処理室104C内での処理を開始する。次いで,搬送機構118により処理室104A内に収容されている処理済のウエハWを取りに行き,搬送経路Y14に示すようにこれを空き状態の処理室104B内へ搬入して置き,処理室104B内での処理を開始する。

Subsequently, the processed wafer W accommodated in the

続いて,ロードロック室108A内で待機していた処理前のウエハWを搬送機構118によって取りに行き,搬送経路Y15に示すようにこれを上記空き状態の処理室104A内へ搬入して置き,この処理室104A内での処理を開始する。なお,ウエハWの搬出入の際には,各ゲートバルブ106A〜106D,107A,107Bのうち,ウエハWの搬出入に必要なゲートバルブを開閉操作する。そして,各処理室104A〜104DにてウエハWの処理が完了する毎に上記の操作が繰り返し行われることになる。

Subsequently, the unprocessed wafer W waiting in the

こうして,コンタクトホール又はビアホールが形成された処理前のウエハWに対して処理室104A〜処理室104DにてそれぞれCOR処理,PHT処理,Ti膜成膜処理,TiN膜成膜処理が連続して施される。従って,ウエハWのコンタクトホール又はビアホールの内壁には,COR処理及びPHT処理によって自然酸化膜などの付着物が除去された状態で,Ti膜成膜処理及びTiN膜成膜処理によってTi膜及びTiN膜のバリア層が成膜される。

In this way, the COR process, the PHT process, the Ti film forming process, and the TiN film forming process are successively performed in the

これにより,膜の密着性,強度が向上するのみならず,ウエハの下地膜にプラズマ起因のチャージアップダメージを負わせることを防止することができるので,ダメージのない配線加工を行うことができ,また良好なコンタクト抵抗を有する膜を成膜することができる。 As a result, not only the adhesion and strength of the film are improved, but also it is possible to prevent the charge-up damage caused by the plasma from being applied to the underlying film of the wafer, so that wiring processing without damage can be performed. In addition, a film having good contact resistance can be formed.

なお,上記各処理室104A〜104Dの構成は図2に示すものに限られるものではない。例えば各処理室104A〜104Dのうちのどの処理室をCOR処理室,PHT処理室,Ti膜成膜処理室,TiN膜成膜処理室として構成してもよい。従って,ウエハの搬送順序も,各処理室104A〜104DのうちのCOR処理室,PHT処理室,Ti膜成膜処理室,TiN膜成膜処理室の順に搬送すれば,必ずしも各処理室104A〜104Dの順でなくてもよい。

The configuration of each of the

(制御部の構成例)

基板処理装置100の制御部200の構成例を図面を参照しながら説明する。図3は,制御部(システムコントローラ)200の構成を示すブロック図である。図3に示すように,制御部200は,装置制御部(EC:Equipment Controller)300と,複数のモジュール制御部(MC:Module Controller)230A,230B,230C…と,EC300と各MC230A,230B,230C…とをそれぞれ接続するスイッチングハブ(HUB)220とを備える。

(Configuration example of control unit)

A configuration example of the

制御部200は,EC300から例えばLAN(Local Area Network)202を介して基板処理装置100が設置される工場全体の製造工程を管理するMES(Manufacturing Execution System)204に接続されている。MES204は例えばコンピュータにより構成される。MES204は,制御部200と連携して工場における工程に関するリアルタイム情報を基幹業務システム(図示しない)にフィードバックするとともに,工場全体の負担等を考慮して工程に関する判断を行う。

The

EC300は,MC230A,230B,230C…を統括して基板処理装置100全体の動作を制御する主制御部(マスタ制御部)を構成する。スイッチングハブ220は,EC300からの制御信号に応じてEC300の接続先としてのMC230A,230B,230C…を切換える。

The

各MC230A,230B,230C…はそれぞれ,基板処理装置100の共通搬送室102,処理室104A〜104D,ロードロック室108A,108B,搬送室110,オリエンタ114等の各モジュールの動作を制御する副制御部(スレーブ制御部)を構成する。各MC230A,230B,230C…はそれぞれ,DIST(Distribution)ボード234A,234B,234C…によって例えばGHOSTネットワーク206を介して各I/O(入出力)モジュール236A,236B,236C…に接続される。GHOSTネットワーク206は,EC300が有するMCボードに搭載されたGHOST(General High-Speed Optimum Scalable Transceiver)と称されるLSIによって実現されるネットワークである。GHOSTネットワーク206には最大で31個のI/Oモジュールを接続することができる。なお,GHOSTネットワーク206ではMCがマスタに相当し,I/Oモジュールがスレーブに相当する。

Each of the

各I/Oモジュール236A,236B,236C…はそれぞれ,処理室104A〜104Dなどの各モジュールの各構成要素(以下,「エンドデバイス」と称する。)に接続された複数のI/O部238A,238B,238C…からなり,各エンドデバイスへの制御信号及び各エンドデバイスからの出力信号の伝達を行う。例えば処理室104のエンドデバイスとしては,処理室104内に導入されるガスの流量を制御するマスフローコントローラ,処理室104からの排気を制御するAPCバルブなどが挙げられる。

Each of the I /

各GHOSTネットワーク206には,I/O部238A,238B,238C…におけるデジタル信号,アナログ信号,シリアル信号の入出力を制御するI/Oボード(図示しない)も接続される。

Also connected to each

ここで,図3に示すEC300の構成例を図面を参照しながら説明する。図4はEC300の構成例を示すブロック図である。図4に示すように,EC300はEC本体を構成するCPU(中央処理装置)310,CPU310が行う各種データ処理のために使用されるメモリエリア等を設けたRAM(ランダム・アクセス・メモリ)320,操作画面や選択画面などを表示する液晶ディスプレイなどで構成される表示手段330,オペレータによるプロセスレシピの入力や編集など種々のデータの入力及び所定の記憶媒体へのプロセスレシピやプロセス・ログの出力など種々のデータの出力などを行うことができる入出力手段340,基板処理装置100に漏電等の異常が発生した際に報知する警報器(例えばブザー)などの報知手段350を備える。

Here, a configuration example of the

また,EC300は,基板処理装置100の種々の処理を実行するための処理プログラムを記憶するプログラムデータ記憶手段360,処理プログラムを実行するために必要な情報(データ)が記憶される処理データ記憶手段370を備える。プログラムデータ記憶手段360,処理データ記憶手段370は例えばハードディスク(HDD)などの記憶領域に構築される。CPU310は必要に応じてプログラムデータ記憶手段360,処理データ記憶手段370から必要なプログラム,データ等を読み出して,各種の処理プログラムを実行する。

The

上記CPU310と,RAM320,表示手段330,入出力手段340,報知手段350,プログラムデータ記憶手段360,処理データ記憶手段370等とは,制御バス,データバス等のバスラインにより接続されている。このバスラインには,上記スイッチングハブ220なども接続されている。

The

ここで,上述したような構成の制御部200による基板処理装置100の制御例について説明する。各処理室104A〜104Dにおいて,例えばウエハWに上述したようなCOR処理,PHT処理,Ti膜成膜処理,TiN膜成膜処理などのプロセス処理を施す場合には,EC300のCPU310はプログラムデータ記憶手段360のプロセス処理プログラム364から実行する処理プログラムを読出し,処理データ記憶手段370のプロセス処理情報374から実行する処理のプロセスレシピの処理情報に基づいて各処理を実行する。すなわち,CPU310は,各処理プログラムに応じてスイッチングハブ220及び処理室104A〜104Dを制御するそれぞれのMC230,GHOSTネットワーク206及びI/Oモジュール236におけるI/O部238を介して,所望のエンドデバイスに制御信号を送信することによって各処理を実行する。

Here, a control example of the

具体的には例えばCOR処理室として構成される処理室104Aにおいて,ウエハWにCOR処理を施す場合には,CPU310が処理室104Aのガス導入系のマスフローコントローラ(例えばアンモニアガス供給管及び弗化水素ガス供給管のマスフローコントローラ)に制御信号を送信することによって処理室104Aにおけるアンモニアガス及び弗化水素ガスの体積流量比を所望の値に調節し,排気系の真空ポンプ(例えばTMP)及び圧力調整バルブ(例えばAPCバルブ)に制御信号を送信することによって処理室104A内の圧力を所望の値に調整する。このとき,圧力計が処理室104A内の圧力値を出力信号としてEC300のCPU310に送信し,CPU300は送信された処理室104A内の圧力値に基づいて,アンモニアガス供給管と弗化水素ガス供給管のマスフローコントローラ,APCバルブやTMPの制御パラメータを決定する。

Specifically, for example, in the

また,PHT処理室として構成される処理室104Bにおいて,ウエハWにPHT処理を施す場合には,CPU310が処理室104Bのガス供給系のマスフローコントローラ(例えば窒素ガス供給管のマスフローコントローラ)及び排気系の圧力調整バルブ(例えばAPCバルブ)に制御信号を送信することによって処理室104B内の圧力を所望の値に調整する。そして,ステージヒータに制御信号を送信することによってウエハWの温度を所望の温度に調整する。このとき,圧力計が処理室104B内の圧力値を出力信号としてEC300のCPU310に送信し,CPU310は送信された処理室104B内の圧力値に基づいて,窒素ガス供給管のMFCやAPCバルブ69の制御パラメータを決定する。

Further, in the

このような図3に示す制御部(システムコントローラ)200では,複数のエンドデバイスがEC300に直接接続されることなく,その複数のエンドデバイスに接続されたI/O部がモジュール化されてI/Oモジュールを構成する。このI/OモジュールはMC及びスイッチングハブ220を介してEC300に接続されるため,通信系統を簡素化することができる。

In such a control unit (system controller) 200 shown in FIG. 3, a plurality of end devices are not directly connected to the

また,EC300のCPU310が送信する制御信号には,所望のエンドデバイスに接続されたI/O部のアドレス,及びそのI/O部を含むI/Oモジュールのアドレスが含まれているため,スイッチングハブ220は制御信号におけるI/Oモジュールのアドレスを参照し,MCのGHOSTが制御信号におけるI/O部のアドレスを参照することによって,スイッチングハブ220やMCがCPU310に制御信号の送信先の問い合わせを行う必要を無くすことができ,これにより,制御信号の円滑な伝達を実現することができる。

The control signal transmitted by the

このように,第1実施形態にかかる基板処理装置100では,成膜処理を行う前に,ウエハに付着した自然酸化膜などの付着物をプラズマを用いない付着物除去処理(例えばCOR処理及びPHT処理)を実行することによって除去した後,ウエハを大気に露出することなく連続して成膜処理を実行することができるため,膜の密着性,強度を向上させることができる。また,プラズマを用いないで自然酸化膜を除去できるので,ダメージのない配線加工を行うことができ,良好なコンタクト抵抗を有する膜を成膜することができる。

As described above, in the

なお,上記のようにコンタクトホール又はビアホールのバリア層を成膜する処理では,前工程としてCOR処理及びPHT処理を行うことが有効であることを説明したが,成膜処理としてはこれに限られるものではなく,以下のような他の成膜処理の前工程としてCOR処理及びPHT処理を行うようにしてもよい。 In the process of forming the contact hole or via hole barrier layer as described above, it has been described that the COR process and the PHT process are effective as the previous process, but the film forming process is not limited thereto. Instead, the COR process and the PHT process may be performed as a pre-process of another film forming process as described below.

(成膜処理の他の具体例)

ここで,本発明に適用可能な成膜処理の他の具体例について説明する。ここでは,前工程としてCOR処理及びPHT処理を行うことが有効な成膜処理として例えばMOSFETなどのMOSデバイスのゲート絶縁膜を高誘電体(High−K)材料により成膜する処理について説明する。

(Other specific examples of film forming process)

Here, another specific example of the film forming process applicable to the present invention will be described. Here, a process for forming a gate insulating film of a MOS device such as a MOSFET with a high dielectric (High-K) material will be described as a film forming process in which it is effective to perform the COR process and the PHT process as the previous process.

MOSデバイスのゲート絶縁膜は,微細化の進展により,近年ではシリコン酸化膜相当で1nm以下の厚さの膜が必要とされている。これは3〜4原子層の厚さに相当する。このくらい薄くなると,トンネル電流の増大,ゲート電極にドープした元素の拡散,信頼性の低下等により,シリコン酸化膜は使えないため,誘電率が高い膜(いわゆるHigh−K膜)の開発が非常な勢いで進められている。すなわち,ZrO2,HfO2などの遷移金属酸化膜,La2O3などの希土類酸化膜およびそれらのシリケートなどは,高い誘電率,高い熱的安定性,Si中の正孔と電子に対して高いエネルギー障壁を有することから,次世代のMOSFETなどのMOSデバイスにおけるゲート絶縁膜として精力的に研究されている。 With the progress of miniaturization, in recent years, a gate insulating film equivalent to a silicon oxide film having a thickness of 1 nm or less is required for a MOS device. This corresponds to a thickness of 3-4 atomic layers. At such a thin film, a silicon oxide film cannot be used due to an increase in tunneling current, diffusion of an element doped in the gate electrode, a decrease in reliability, etc., so development of a film having a high dielectric constant (so-called High-K film) It is proceeding at a rapid pace. That is, transition metal oxide films such as ZrO 2 and HfO 2 , rare earth oxide films such as La 2 O 3, and silicates thereof have high dielectric constant, high thermal stability, resistance to holes and electrons in Si. Since it has a high energy barrier, it has been energetically studied as a gate insulating film in MOS devices such as next-generation MOSFETs.

これらの高誘電率膜とSi基板との間には,シリケートからなる組成遷移層が形成され,シリケート層とSi基板の間にSiの中間酸化状態からなる組成遷移層が形成されてしまう。従って,これら組成遷移層が形成されることを防止するために,先に酸化防止層としてベース酸化膜(例えばSiO2膜)を成膜する必要がある。このようにベース酸化膜をシリケート層とSi基板に介在させることによってデバイス特性の劣化,つまり移動度の低下を防止する効果もある。 A composition transition layer made of silicate is formed between these high dielectric constant films and the Si substrate, and a composition transition layer made of an intermediate oxidation state of Si is formed between the silicate layer and the Si substrate. Therefore, in order to prevent these composition transition layers from being formed, it is necessary to form a base oxide film (for example, SiO 2 film) as an antioxidant layer first. Thus, by interposing the base oxide film between the silicate layer and the Si substrate, there is an effect of preventing deterioration of device characteristics, that is, reduction of mobility.

このような高誘電体(High−K)材料によるゲート絶縁膜の成膜に際しては原子層レベルでの制御が必要であるため,ゲート絶縁膜の成膜処理を実行する前に,プラズマを用いないドライクリーニングである付着物除去処理(例えばCOR処理及びPHT処理)を実行して自然酸化膜などの付着物を除去することによって,膜の密着性,強度を向上させることができる。 When forming a gate insulating film using such a high dielectric (High-K) material, it is necessary to control at the atomic layer level, so that plasma is not used before the gate insulating film forming process is performed. The adhesion and strength of the film can be improved by performing the deposit removal process (for example, COR process and PHT process), which is dry cleaning, to remove deposits such as a natural oxide film.

また,もしプラズマを用いて自然酸化膜を除去すれば,ゲート絶縁膜を成膜する下地にプラズマ励起のチャージアップダメージを負わせる虞がある。このように下地にダメージを残したままゲート酸化膜を成膜すると,そのダメージの程度によってはゲート酸化膜の破壊を招き,MOSデバイス自体の特性が劣化する虞がある。この点,本実施形態にかかる付着物除去処理(例えばCOR処理及びPHT処理)では,プラズマを用いないため,ゲート絶縁膜を成膜する下地にダメージを与えることもないので,MOSデバイスの特性が劣化することを防止することができる。 Further, if the natural oxide film is removed using plasma, there is a risk of causing charge-up damage due to plasma excitation to the base on which the gate insulating film is formed. If a gate oxide film is formed with damage on the underlying layer as described above, the gate oxide film may be destroyed depending on the degree of the damage, and the characteristics of the MOS device itself may be deteriorated. In this regard, in the deposit removal processing (for example, COR processing and PHT processing) according to the present embodiment, plasma is not used, and therefore, the substrate on which the gate insulating film is formed is not damaged. Deterioration can be prevented.

このような高誘電体(High−K)材料のゲート絶縁膜(高誘電体ゲート絶縁膜)を成膜する処理は,ウエハ上すなわちシリコン基板上に非常に薄い,好ましくは1nm以下の膜厚のSiO2膜などのベース酸化膜を成膜した後,High−K膜(例えばHfSiO2などのシリケート膜)を成膜する。なお,ベース酸化膜成膜処理は第1膜成膜処理に相当し,High−K膜成膜処理は第2膜成膜処理に相当する。 The process of forming such a high dielectric (High-K) gate insulating film (high dielectric gate insulating film) is very thin on the wafer, that is, on the silicon substrate, preferably with a film thickness of 1 nm or less. After forming a base oxide film such as a SiO 2 film, a High-K film (for example, a silicate film such as HfSiO 2 ) is formed. The base oxide film forming process corresponds to the first film forming process, and the High-K film forming process corresponds to the second film forming process.

ベース酸化膜成膜処理(第1膜成膜処理)は,例えば紫外光励起酸素ラジカルを使ったラジカル酸化処理によって行われる。具体的にはシリコン基板の紫外光励起ラジカル酸化処理により,2〜3分子層に相当する膜厚のベース酸化膜を安定に,再現性良く形成することができる。このように,酸素ラジカルによってシリコン基板上の表面にベース酸化膜として例えば略0.5nm程度のSiO2原子層を形成する。この場合の処理時間は例えば300秒である。 The base oxide film forming process (first film forming process) is performed by radical oxidation using, for example, ultraviolet light-excited oxygen radicals. Specifically, a base oxide film having a film thickness corresponding to 2 to 3 molecular layers can be stably formed with good reproducibility by ultraviolet light excited radical oxidation treatment of a silicon substrate. Thus, an SiO 2 atomic layer of about 0.5 nm, for example, is formed as a base oxide film on the surface of the silicon substrate by oxygen radicals. In this case, the processing time is, for example, 300 seconds.

High−K膜成膜処理(第2膜成膜処理)は,ベース酸化膜成膜処理によってベース酸化膜が形成されたウエハ上に,例えば有機金属化学気相堆積(MOCVD)法などにより金属酸化膜(例えばHfSiO2などのシリケート膜)を形成する。具体的には例えばベース酸化膜としてSiO2原子層が形成された基板を400〜600℃に加熱した状態で,基板上に原料ガスを導入すると,原料ガスが分解して基板上に例えばHfSiO2などのシリケート膜の薄膜が形成される。この場合の処理時間としては例えば343秒である。 The High-K film deposition process (second film deposition process) is performed by, for example, metal oxide chemical vapor deposition (MOCVD) on the wafer on which the base oxide film is formed by the base oxide film deposition process. A film (for example, a silicate film such as HfSiO 2 ) is formed. Specifically, for example, when a source gas is introduced onto a substrate on which a SiO 2 atomic layer as a base oxide film is heated to 400 to 600 ° C., the source gas is decomposed and, for example, HfSiO 2 is deposited on the substrate. A thin film of a silicate film such as is formed. The processing time in this case is, for example, 343 seconds.

(処理室の他の構成例)

次に,このような処理を実行するための基板処理装置100における処理室の構成例を説明する。本実施形態にかかる基板処理装置100は,COR処理,PHT処理,ベース酸化膜成膜処理(UV処理),High−K膜成膜処理(MOCVD処理)を連続して実行する。

(Other configuration examples of processing chamber)

Next, a configuration example of a processing chamber in the

このため,処理室104A〜104Dのうち少なくとも2つの処理室の一方をそれぞれCOR処理,PHT処理を実行する付着物除去処理室として構成し,他方の2つの処理室をそれぞれ酸化膜成膜処理(UV処理),High−K膜成膜処理(MOCVD処理)を実行する成膜処理室として構成する。

Therefore, one of at least two processing chambers among the

ここで,基板処理装置100における処理室104A,104B,104C,104DをそれぞれCOR処理室,PHT処理室,酸化膜成膜処理(UV処理)室,High−K膜成膜処理(MOCVD処理)室として構成した例を図5に示す。酸化膜成膜処理(UV処理)室,High−K膜成膜処理(MOCVD処理)室における処理については,それぞれ上述した制御部200のEC(装置制御部)300のプログラムデータ記憶手段360に記憶されたプロセス処理プログラム364に基づいて実行される。EC300のCPU310はプロセス処理プログラム364から必要な処理プログラムを読出し,処理データ記憶手段370に記憶されるプロセス処理情報(例えばプロセスレシピ情報)374から必要な情報を読み出して各処理を実行する。

Here, the

なお,各処理室104A〜104Dを図5に示すように構成した場合の基板処理装置100におけるウエハWの搬送処理については,図2に示す構成の場合と同様であるため,その詳細な説明を省略する。

The wafer W transfer process in the

(第2実施形態にかかる基板処理装置の構成例)

次に,第2実施形態にかかる基板処理装置の構成例を図面を参照しながら説明する。図6は第2実施形態にかかる基板処理装置の概略構成図である。図6に示すように,基板処理装置101は複数の処理室を接続する共通搬送室を備える真空処理装置を複数連結した構成である。このような構成の基板処理装置101においても本発明を適用することができる。

(Configuration Example of Substrate Processing Apparatus According to Second Embodiment)

Next, a configuration example of the substrate processing apparatus according to the second embodiment will be described with reference to the drawings. FIG. 6 is a schematic configuration diagram of a substrate processing apparatus according to the second embodiment. As shown in FIG. 6, the

図6に示す基板処理装置101は,図1に示す基板処理装置100における共通搬送室を第1共通搬送室102とすれば,この第1共通搬送室102と2つのロードロック室108A,108Bとの間に別の第2共通搬送室120を介在させた例である。この第2共通搬送室120は,略多角形(例えば変則的な七角形)に構成されており,2つの辺に各処理室104E,104Fをそれぞれゲートバルブ106E,106Fを介して連結している。なお,第1共通搬送室102とこれに接続される処理室(処理室104A〜104D)を備える真空処理装置は第1真空処理装置の1例を構成し,第2共通搬送室120とこれに接続される処理室(処理室104E,104F)を備える真空処理装置は第2真空処理装置の1例を構成する。

A

第1共通搬送室102と第2共通搬送室120との間には,両共通搬送室102,120を連通すると共にウエハWを一時的に保持するパス部122が連結されている。第1共通搬送室102と第2共通搬送室120との間でウエハを搬送する際には,このパス部122にウエハWを一時的に保持するようになっている。この場合,第1共通搬送室102の形状は,パス部122を連結するために変則的な七角形に成形されている。第1共通搬送室102とパス部122の接合部にはゲートバルブ126が設けられている。このゲートバルブ126を開閉することにより,両共通搬送室102,120間を連通及び遮断が可能となる。

Between the first

上記各処理室104E,104F内には,他の処理室104A〜104Dと同様にウエハWを保持する載置台105E,105Fがそれぞれ設けられる。また,第2共通搬送室120内には,第1共通搬送室102と同様に,2つのピック124A,124Bを有する屈伸及び旋回可能になされた搬送機構124が設けられている。第2共通搬送室120の搬送機構124は,第1共通搬送室102の搬送機構118の場合と同様な操作でウエハを効率的に搬送するようになっている。

In the

なお,第2共通搬送室120と2つのロードロック室の内のいずれか一方,例えばロードロック室108Aとの連結部の搬送口152AはウエハWを第2共通搬送室120内へ専用に搬入する搬入口として用いられ,他方のロードロック室108Bとの連結部の搬送口152BはウエハWを第2共通搬送室120から外へ専用に搬出する搬出口として用いられる。

Note that one of the second common transfer chamber 120 and the two load lock chambers, for example, the

(処理室の構成例)

次に,図6に示す基板処理装置101における処理室の構成例を説明する。第2実施形態にかかる基板処理装置101においても,ウエハ上の自然酸化膜などの付着物を水成分を用いず且つプラズマを用いずに除去する付着物除去処理と,この付着物除去処理が施されたウエハ上に所定の薄膜を形成する成膜処理とを連続して実行するように構成することができる。

(Configuration example of processing chamber)

Next, a configuration example of the processing chamber in the

処理室104A〜104Fのうち少なくとも2つの処理室の一方を付着物除去処理室として構成し,他方の2つの処理室を成膜処理室として構成する。また,付着物除去処理は上述したように複数段階の処理を連続して実行するようにしてもよく,この場合には付着物除去処理室を複数の処理室で構成してもよい。具体的には上述したような生成物生成処理(例えばCOR処理)と,生成物除去処理(例えばPHT処理)との2段階の処理によって行う場合には処理室104A〜104Fのうちの2つの処理室を付着物除去処理室として構成する。この場合,一方の処理室を生成物生成処理室として構成し,他方の処理室を生成物除去処理室として構成する。

One of at least two processing chambers among the

また成膜処理は異なる膜を連続して成膜するようにしてもよく,この場合には成膜処理室を複数の処理室で構成してもよい。具体的には第1膜(例えばTi系膜)と,第2膜(例えばTiN系膜)を連続して成膜する場合には処理室104A〜104Fのうちの2つの処理室を成膜処理室として構成する。この場合,一方の処理室を第1膜を成膜する第1膜成膜処理室として構成し,他方の処理室を第2膜を成膜する第2膜成膜処理室として構成する。このように,基板処理装置101によって実行される付着物除去処理と成膜処理の内容に応じて各処理室104A〜104Fの構成が決定される。

In the film forming process, different films may be successively formed. In this case, the film forming process chamber may be composed of a plurality of process chambers. Specifically, in the case where a first film (for example, a Ti-based film) and a second film (for example, a TiN-based film) are continuously formed, two of the

ここで,例えばコンタクトホール又はビアホールが形成されたウエハWを基板処理装置101に導入し,このウエハWに対して上述したような付着物除去処理としてのCOR処理,PHT処理を連続して実行した後,成膜処理としてのTi膜成膜処理,TiN膜成膜処理を連続して実行する場合の基板処理装置101における処理室の構成例を図7に示す。

Here, for example, a wafer W in which contact holes or via holes are formed is introduced into the

図7に示す構成例は,第1共通搬送室102に接続される処理室104A,104B,104C,104DをそれぞれCOR処理室,PHT処理室,Ti膜成膜処理室,TiN膜成膜処理室として構成したものである。