JP2005501313A - パーソナルコンピュータシステムにおいて裏口アクセス機構を閉鎖するための機構 - Google Patents

パーソナルコンピュータシステムにおいて裏口アクセス機構を閉鎖するための機構 Download PDFInfo

- Publication number

- JP2005501313A JP2005501313A JP2002589946A JP2002589946A JP2005501313A JP 2005501313 A JP2005501313 A JP 2005501313A JP 2002589946 A JP2002589946 A JP 2002589946A JP 2002589946 A JP2002589946 A JP 2002589946A JP 2005501313 A JP2005501313 A JP 2005501313A

- Authority

- JP

- Japan

- Prior art keywords

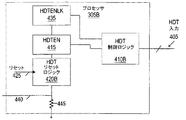

- enable

- hdt

- microcode

- control logic

- register

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/22—Microcontrol or microprogram arrangements

- G06F9/24—Loading of the microprogram

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Storage Device Security (AREA)

- Test And Diagnosis Of Digital Computers (AREA)

- Stored Programmes (AREA)

- Debugging And Monitoring (AREA)

- Executing Machine-Instructions (AREA)

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US85294201A | 2001-05-10 | 2001-05-10 | |

| US09/852,372 US7065654B1 (en) | 2001-05-10 | 2001-05-10 | Secure execution box |

| US09/853,226 US20030028781A1 (en) | 2001-05-10 | 2001-05-11 | Mechanism for closing back door access mechanisms in personal computer systems |

| PCT/US2002/011935 WO2002093336A2 (en) | 2001-05-10 | 2002-04-17 | Processor with protected test and debug mode |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005501313A true JP2005501313A (ja) | 2005-01-13 |

| JP2005501313A5 JP2005501313A5 (enExample) | 2006-01-05 |

Family

ID=27420360

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002589946A Pending JP2005501313A (ja) | 2001-05-10 | 2002-04-17 | パーソナルコンピュータシステムにおいて裏口アクセス機構を閉鎖するための機構 |

Country Status (9)

| Country | Link |

|---|---|

| US (1) | US20030028781A1 (enExample) |

| EP (1) | EP1410143B1 (enExample) |

| JP (1) | JP2005501313A (enExample) |

| KR (1) | KR20030094396A (enExample) |

| CN (1) | CN1520537A (enExample) |

| AU (1) | AU2002250591A1 (enExample) |

| DE (1) | DE60206924T2 (enExample) |

| TW (1) | TWI228889B (enExample) |

| WO (1) | WO2002093336A2 (enExample) |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20030097587A1 (en) * | 2001-11-01 | 2003-05-22 | Gulick Dale E. | Hardware interlock mechanism using a watchdog timer |

| US20040034872A1 (en) * | 2002-08-16 | 2004-02-19 | Peter Huyge | Method for triggering an event in an electronic device, and corresponding device |

| US7334123B2 (en) * | 2003-05-02 | 2008-02-19 | Advanced Micro Devices, Inc. | Computer system including a bus bridge for connection to a security services processor |

| JP4692826B2 (ja) * | 2003-07-28 | 2011-06-01 | ソニー株式会社 | 情報処理装置および方法、記録媒体、並びにプログラム |

| US7805614B2 (en) * | 2004-04-26 | 2010-09-28 | Northrop Grumman Corporation | Secure local or remote biometric(s) identity and privilege (BIOTOKEN) |

| US7552341B2 (en) * | 2004-09-01 | 2009-06-23 | Microsoft Corporation | Licensing the use of software on a particular CPU |

| JP4309361B2 (ja) * | 2005-03-14 | 2009-08-05 | パナソニック株式会社 | 電子機器制御システム及び制御信号送信装置 |

| JP4207050B2 (ja) * | 2005-06-27 | 2009-01-14 | コニカミノルタビジネステクノロジーズ株式会社 | 画像形成装置 |

| US7925815B1 (en) * | 2006-06-29 | 2011-04-12 | David Dunn | Modifications to increase computer system security |

| US8661265B1 (en) | 2006-06-29 | 2014-02-25 | David Dunn | Processor modifications to increase computer system security |

| US7610426B1 (en) * | 2006-12-22 | 2009-10-27 | Dunn David A | System management mode code modifications to increase computer system security |

| US8316414B2 (en) * | 2006-12-29 | 2012-11-20 | Intel Corporation | Reconfiguring a secure system |

| US20090109984A1 (en) * | 2007-10-31 | 2009-04-30 | Dell Products L.P. | Wireless device with flash cache and boot from dock |

| US9286232B2 (en) * | 2009-01-26 | 2016-03-15 | International Business Machines Corporation | Administering registered virtual addresses in a hybrid computing environment including maintaining a cache of ranges of currently registered virtual addresses |

| US20120117227A1 (en) * | 2010-11-10 | 2012-05-10 | Sony Corporation | Method and apparatus for obtaining feedback from a device |

| US20120185688A1 (en) * | 2011-01-13 | 2012-07-19 | Google Inc. | Processor mode locking |

| CN105788638A (zh) * | 2011-03-04 | 2016-07-20 | 瑞萨电子株式会社 | 半导体器件 |

| CN103984908B (zh) * | 2014-05-05 | 2017-03-08 | 上海新储集成电路有限公司 | 一种南桥芯片及其应用方法 |

| US10101928B2 (en) * | 2016-02-19 | 2018-10-16 | Dell Products L.P. | System and method for enhanced security and update of SMM to prevent malware injection |

| US10534936B2 (en) * | 2017-08-30 | 2020-01-14 | Dell Products, Lp | System and method for enabling and disabling of baseboard management controller configuration lockdown |

| US11354406B2 (en) | 2018-06-28 | 2022-06-07 | Intel Corporation | Physics-based approach for attack detection and localization in closed-loop controls for autonomous vehicles |

| TWI682301B (zh) * | 2018-11-19 | 2020-01-11 | 歐生全科技股份有限公司 | 多功能認證裝置與運作方法 |

| NO346155B1 (en) * | 2020-10-26 | 2022-03-28 | Kongsberg Defence & Aerospace As | Configuration authentication prior to enabling activation of a FPGA having volatile configuration-memory |

| US12292975B2 (en) * | 2022-03-28 | 2025-05-06 | Intel Corporation | Method, system and apparatus to prevent denial of service attacks on PCIe based computing devices |

| US12164348B2 (en) * | 2022-10-04 | 2024-12-10 | Nxp Usa, Inc. | Capturing of on-chip resets in an integrated circuit |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0855023A (ja) * | 1994-07-25 | 1996-02-27 | Motorola Inc | データ処理システムおよびその方法 |

| JP3461234B2 (ja) * | 1996-01-22 | 2003-10-27 | 株式会社東芝 | データ保護回路 |

| US6026016A (en) * | 1998-05-11 | 2000-02-15 | Intel Corporation | Methods and apparatus for hardware block locking in a nonvolatile memory |

| US6154819A (en) * | 1998-05-11 | 2000-11-28 | Intel Corporation | Apparatus and method using volatile lock and lock-down registers and for protecting memory blocks |

-

2001

- 2001-05-11 US US09/853,226 patent/US20030028781A1/en not_active Abandoned

-

2002

- 2002-04-17 EP EP02719514A patent/EP1410143B1/en not_active Expired - Lifetime

- 2002-04-17 WO PCT/US2002/011935 patent/WO2002093336A2/en not_active Ceased

- 2002-04-17 DE DE60206924T patent/DE60206924T2/de not_active Expired - Fee Related

- 2002-04-17 CN CNA028124928A patent/CN1520537A/zh active Pending

- 2002-04-17 KR KR10-2003-7014546A patent/KR20030094396A/ko not_active Withdrawn

- 2002-04-17 JP JP2002589946A patent/JP2005501313A/ja active Pending

- 2002-04-17 AU AU2002250591A patent/AU2002250591A1/en not_active Abandoned

- 2002-04-26 TW TW091108639A patent/TWI228889B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| DE60206924D1 (de) | 2005-12-01 |

| EP1410143A2 (en) | 2004-04-21 |

| KR20030094396A (ko) | 2003-12-11 |

| TWI228889B (en) | 2005-03-01 |

| DE60206924T2 (de) | 2006-07-27 |

| EP1410143B1 (en) | 2005-10-26 |

| CN1520537A (zh) | 2004-08-11 |

| US20030028781A1 (en) | 2003-02-06 |

| WO2002093336A2 (en) | 2002-11-21 |

| WO2002093336A3 (en) | 2004-02-12 |

| AU2002250591A1 (en) | 2002-11-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2005501313A (ja) | パーソナルコンピュータシステムにおいて裏口アクセス機構を閉鎖するための機構 | |

| US7149854B2 (en) | External locking mechanism for personal computer memory locations | |

| US11580264B2 (en) | Systems and methods for controlling access to secure debugging and profiling features of a computer system | |

| US7020772B2 (en) | Secure execution of program code | |

| US8533777B2 (en) | Mechanism to determine trust of out-of-band management agents | |

| US7010684B2 (en) | Method and apparatus for authenticating an open system application to a portable IC device | |

| CN101517549B (zh) | 数据处理设备和在数据处理设备中产生访问请求的方法 | |

| US6823451B1 (en) | Integrated circuit for security and manageability | |

| US20060036851A1 (en) | Method and apparatus for authenticating an open system application to a portable IC device | |

| US7003676B1 (en) | Locking mechanism override and disable for personal computer ROM access protection | |

| US7013484B1 (en) | Managing a secure environment using a chipset in isolated execution mode | |

| US6862641B1 (en) | Interruptable and re-enterable system management mode programming code | |

| WO1997049041A1 (en) | System for controlling access to a register mapped to an i/o address space of a computer system | |

| CN100530209C (zh) | 用于限制安全执行环境的硬件失败信息泄漏的系统和方法 | |

| JP2004504663A (ja) | 分離実行環境での複数の分離メモリへのアクセスの制御 | |

| US7013481B1 (en) | Attestation key memory device and bus | |

| US7216362B1 (en) | Enhanced security and manageability using secure storage in a personal computer system | |

| US7111176B1 (en) | Generating isolated bus cycles for isolated execution | |

| CN1659496A (zh) | 与令牌安全通信的方法和装置 | |

| US20140196154A1 (en) | Systems and methods for controlling access to secure debugging and profiling features of a computer system | |

| CN100354800C (zh) | 数据存取系统及其方法 | |

| CN101213556A (zh) | 评估令牌实现的计算机系统的机制 | |

| CN101118583A (zh) | 用于个人计算机存储器区域的外部锁固机构 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050330 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050606 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20081021 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090331 |