JP2005295526A - 画像符号化方法、画像符号化装置および画像符号化プログラム - Google Patents

画像符号化方法、画像符号化装置および画像符号化プログラム Download PDFInfo

- Publication number

- JP2005295526A JP2005295526A JP2005065288A JP2005065288A JP2005295526A JP 2005295526 A JP2005295526 A JP 2005295526A JP 2005065288 A JP2005065288 A JP 2005065288A JP 2005065288 A JP2005065288 A JP 2005065288A JP 2005295526 A JP2005295526 A JP 2005295526A

- Authority

- JP

- Japan

- Prior art keywords

- macroblock

- encoding

- macroblocks

- order

- decoding

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Compression Or Coding Systems Of Tv Signals (AREA)

- Compression, Expansion, Code Conversion, And Decoders (AREA)

Abstract

また、PMV(周囲のマクロブロックから求めた予測動きベクトル)を用いる符号化方法において、複数のマクロブロックに対する動きベクトル探索を並列化することを目的とする。

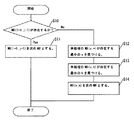

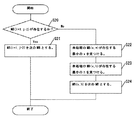

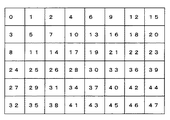

【解決手段】マクロブロック順序選択手段13がエンコードするマクロブロックを選択する。13は、現在マクロブロックと現在マクロブロックがイントラ予測あるいは動きベクトル探索で参照するマクロブロックの順序番号の差が2以上となるようにエンコードするマクロブロックの順序を選択する。選択されたマクロブロックに対して、イントラ予測、動き補償予測、動き法相モード選択、DCT、量子化、エントロピー符号化を行う。

【選択図】図1

Description

テレビジョン学会編「MPEG」オーム社、2001年、p.69-71. 祇園、他6名「リアルタイムMPEG2コーデック用DSP(VDSP2)」ナショナルテクニカルレポート、1994年、Vol.40、ナンバー6、p.122-128. ISO/IEC 13818-2, Information technology - Generic coding of moving pictures and associated audio information: Video. ITU-T H.264, Advanced video coding for generic audiovisual services. ITU-T T.81, Information technology - Digital compression and coding of continuous-tone still images - Requirements and guidelines. Joint Video Team (JVT) software, http://iphome.hhi.de/suehring/tml/index.htm Yu-Wen Huang, Tu-Chih Wang, Bing-Yu Hsieh and Liang-Gee Chen, "Hardware architecture design for variable block size motion estimation in MPEG-4 AVC/JVT/ITU-T H.264", IEEE Int Symp Circuits Syst, 2003 Vol 2, p.796-799, 2003. Gary J. Sullivan and Thomas Wiegand, "Rate-Distortion Optimization for Video Compression", IEEE Signal Processing Magazine, Nov 1998, p.74-90, 1998.

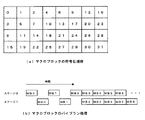

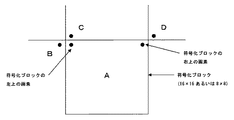

図1は本発明による画像符号化装置の基本構成である。従来の装置構成との相違はマクロブロック順序選択部13が追加されたことである。本実施の形態の目的は、H.264のイントラ16×16予測を用いる符号化方法の場合に、マクロブロックのパイプラン処理を容易にすることである。前述のように、イントラ16×16予測では現在マクロブロックの左、上、左上の3個のマクロブロックを予測に用いる。説明を簡単にするために、ピクチャ全体が1つのスライスであるとする(H.264の規格では可能)。H.264ではDCTの代わりにDCTを整数演算で近似した整数変換を用いるが、本発明の本質とは関係ないので、以下の説明ではDCTとする。

本実施の形態における画像符号化装置の基本構成は実施の形態1と同じである。実施の形態1と異なるのはマクロブロック順序選択部13の動作である。本実施の形態はH.264の4×4のイントラ予測を含む符号化方法であってもマクロブロックのパイプラン処理を可能とすることを目的とする。前述のように、イントラ4×4予測では現在マクロブロックの左、上、左上、右上の4個のマクロブロックを予測に用いる。

図2は本発明の実施の形態3における復号化装置の基本構成図である。従来の装置構成との差異はマクロブロック順序選択部39が存在することである。本実施の形態の目的は、イントラ16×16予測を含む符号化方法によって符号化されたストリームをマクロブロックのパイプラン処理によって復号することを容易にすることである。

本実施の形態はエンコーダにおいてH.264のスペーシャルダイレクトモードの予測を含む符号化方法であっても、マクロブロックのパイプラン処理を可能とすることを目的とする。スペーシャルダイレクトモードについては非特許文献4に述べられている。本実施の形態における画像符号化装置の基本構成は実施の形態1と同じである。実施の形態1と異なるのはマクロブロック順序選択部13の動作である。本実施の形態におけるマクロブロックのエンコード順序は実施の形態2と同じである。

図15は本発明の実施の形態5による静止画符号化装置の基本構成図である。本実施の形態が用いる静止画の符号化方法は非特許文献5のJPEGのベースラインプロファイルを修正したものである。具体的には、マクロブロック単位に符号化し、8×8サイズのDCT、量子化、変換係数のジグザグスキャン、可変長符号化により符号化するが、以下の2点がJPEGと異なる。

図16は本発明の実施の形態6による符号化装置のためのマクロブロック順序並び替え装置の基本構成図である。本装置の目的はマクロブロックの符号化順序とマクロブロックのストリームへの出力順序が異なる場合に、マクロブロックを並べ替えることである。符号化されたマクロブロックは本装置により順序を並び替えた後に出力される。

図17は本発明の実施の形態7による復号化装置のためのマクロブロック順序並び替え装置の基本構成図である。本装置の目的は、符号化ストリームの中のマクロブロックの格納順序とマクロブロックの復号順序が異なる場合に、マクロブロックを並べ替えることである。入力されたマクロブロックはエントロピー復号化された後、本装置により復号順序を選択されて復号される。

H.264の規格にはMBAFF(macroblock adaptive frame field)と呼ばれるマクロブロックの符号化方法がある。本実施の形態ではMBAFFを用いた符号化方法をパイプライン方式で処理する符号化装置について説明する。MBAFFについては非特許文献4に述べられている。MBAFFでエンコードする場合は、上下の2個のマクロブロックをペアにして、マクロブロックペアごとにフレームかフィールドかを選択することができる。マクロブックペアがフレームの場合は2個のマクロブロックを共にフレームとしてエンコードする。マクロブロックペアがフィールドの場合は2個のマクロブロックを共にフィールドとしてエンコードする。マクロブロックペアは上のマクロブロック、下のマクロブロックの順にエンコードする。

本実施の形態では動きベクトル探索とエンコードをパイプライン方式で処理する符号化装置について説明する。全体の構成は図1と同じである。

ここで、SAD(sum of absolute difference)は予測残差の絶対値の和、λはラグランジュパラメタと呼ばれる定数、Rは動きベクトルの符号量である。SADの代わりに残差に対してアダマール変換を行った後の絶対値の和であるSATDを用いることもある。JMエンコーダでは動きベクトルの符号量を小さくするために、規格の手順に基づいてPMVを求め、画像の予測誤差が小さくなると同時に動きベクトルとPMVの差分が小さくなるような動きベクトルを選択する(動きベクトル探索方法はH.264の規格には規定されておらず、エンコーダに任されている。PMVを求める手順はH.264の規格に規定されている。)。

本実施の形態では複数のマクロブロックに対する動きベクトル探索を並列に行い、さらに動きベクトル探索とエンコードをパイプライン方式で処理する符号化装置について説明する。全体の構成は図1と同じである。

本実施の形態による画像符号化装置は、動きベクトル探索を行う2個のMEユニットと動きベクトル探索以降のエンコード処理を行う1個のエンコードユニットを備える。図26は本実施の形態の説明図である。動きベクトル探索はエンコードと比較して計算量が大きいので、本実施の形態ではエンコードユニットの数より多くのMEユニットを備える。

本実施の形態による画像符号化装置は、動きベクトル探索を行う3個のMEユニットと動きベクトル探索以降のエンコード処理を行う1個のエンコードユニットを備える。図27は本実施の形態の説明図である。

11 フォーマット変換部

12 画面並び替え部

13 マクロブロック順序選択部

14 DCT部

15 量子化部

16 レート制御部

17 動きベクトル検出、イントラ予測部

18 動き補償モード選択部

19 逆量子化部

20 逆DCT部

21 エントロピー符号化部

22 バッファ

23 ビデオメモリ

30 バッファ

31 可変長復号化部

32 逆量子化部

33 逆DCT部

34 画面並び替え部

35 フォーマット変換部

36 D/A変換部

37 動き補償部

38 ビデオメモリ

39 マクロブロック順序選択部

50 A/D変換部

51 フォーマット変換部

52 画面並び替え部

53 DCT部

54 量子化部

55 可変長符号化部

56 バッファ

57 レート制御部

58 逆量子化部

59 逆DCT部

60 動きベクトル検出部

61 動き補償モード選択部

62 ビデオメモリ

70 バッファ

71 可変長復号化部

72 逆量子化部

73 逆DCT部

74 画面並び替え部

75 フォーマット変換部

76 D/A変換部

77 動き補償部

78 ビデオメモリ

80 予測部

81 残差計算部

82 DCT部

83 量子化部

84 ジグザグスキャン部

85 可変長符号化部

86 マクロブロック順序選択部

87 フレームメモリ

88 逆DCT部

89 逆量子化部

Claims (43)

- マクロブロックの符号化順序を選択するマクロブロック選択手段と、

動きベクトルを検出する動きベクトル検出手段と、

マクロブロックの符号化モードを選択する動き補償モード選択手段と、

動き補償の残差を変換する直交変換手段と、

直交変換後の係数を量子化する量子化手段と

量子化後の係数を符号化するエントロピー符号化手段と

を備えたことを特徴とする画像符号化装置。 - 前記マクロブロック選択手段は、

現在マクロブロックと現在マクロブロックがイントラ予測において参照する全てのマクロブロックの符号化の順序番号の差が2以上である

ことを特徴とする請求項1記載の画像符号化装置。 - 前記マクロブロック選択手段は、

現在マクロブロックの座標を(i、j)とするとき、座標(i+1、j−1)に未符号化マクロブロックが存在する場合、そのマクロブロックを次に符号化するマクロブロックとして選択する

ことを特徴とする請求項1記載の画像符号化装置。 - 前記マクロブロック選択手段は、

現在マクロブロックの座標を(i、j)とするとき、座標(i+1、j−2)に未符号化マクロブロックが存在する場合、そのマクロブロックを次に符号化するマクロブロックとして選択する

ことを特徴とする請求項1記載の画像符号化装置。 - 前記マクロブロック選択手段が選択したマクロブロックの符号化順序を示す情報を符号化ストリームに付加する

ことを特徴とする請求項1記載の画像符号化装置。 - 前記マクロブロック選択手段は、

現在マクロブロックと現在マクロブロックがスペーシャルダイレクトモード予測において参照する全てのマクロブロックの符号化の順序番号の差が2以上である

ことを特徴とする請求項1記載の画像符号化装置。 - マクロブロックの復号化順序を選択するマクロブロック選択手段と、

係数を復号化するエントロピー復号化手段と、

係数を逆量子化する逆量子化手段と、

直行変換の係数を復号する逆DCT手段と、

動きベクトルに基づいて動き補償を行う動き補償手段と

を備えたことを特徴とする画像復号化装置。 - 前記マクロブロック選択手段は、

現在マクロブロックと現在マクロブロックがイントラ予測において参照する全てのマクロブロックの復号化の順序番号の差が2以上である

ことを特徴とする請求項7記載の画像復号化装置。 - 前記マクロブロック選択手段は、

現在マクロブロックの座標を(i、j)とするとき、座標(i+1、j−1)に未復号化マクロブロックが存在する場合、そのマクロブロックを次に復号化するマクロブロックとして選択する

ことを特徴とする請求項7記載の画像復号化装置。 - 前記マクロブロック選択手段は、

現在マクロブロックの座標を(i、j)とするとき、座標(i+1、j−2)に未復号化マクロブロックが存在する場合、そのマクロブロックを次に復号化するマクロブロックとして選択する

ことを特徴とする請求項7記載の画像復号化装置。 - マクロブロックの符号化順序を選択するマクロブロック選択ステップと、

動きベクトルを検出する動きベクトル検出ステップと、

マクロブロックの符号化モードを選択する動き補償モード選択ステップと、

動き補償の残差を変換する直交変換ステップと、

直交変換後の係数を量子化する量子化ステップと

量子化後の係数を符号化するエントロピー符号化ステップと

を備えたことを特徴とする画像符号化方法。 - 前記マクロブロック選択ステップは、

現在マクロブロックと現在マクロブロックがイントラ予測において参照する全てのマクロブロックの符号化の順序番号の差が2以上である

ことを特徴とする請求項11記載の画像符号化方法。 - マクロブロックの復号化順序を選択するマクロブロック選択ステップと、

係数を復号化するエントロピー復号化ステップと、

係数を逆量子化する逆量子化ステップと、

直行変換の係数を復号する逆DCTステップと、

動きベクトルに基づいて動き補償を行う動き補償ステップと

を備えたことを特徴とする画像復号化方法。 - 前記マクロブロック選択ステップは、

現在マクロブロックと現在マクロブロックがイントラ予測において参照する全てのマクロブロックの復号化の順序番号の差が2以上である

ことを特徴とする請求項13記載の画像復号化方法。 - マクロブロックの符号化順序を選択するマクロブロック選択手段と、

イントラ予測を行う予測手段と、

イントラ予測の残差を求める残差計算手段と、

残差をブロック単位に変換する直交変換手段と、

直交変換後の係数を量子化する量子化手段と

量子化後の係数を符号化するエントロピー符号化手段と

を備えたことを特徴とする静止画符号化装置。 - 前記マクロブロック選択手段は、

現在マクロブロックと現在マクロブロックがイントラ予測において参照する全てのマクロブロックの符号化の順序番号の差が2以上である

ことを特徴とする請求項15記載の静止画符号化装置。 - マクロブロックの復号化順序を選択するマクロブロック選択手段と、

係数を復号化するエントロピー復号化手段と、

係数を逆量子化する逆量子化手段と、

直行変換の係数を復号する逆DCT手段と、

を備えたことを特徴とする静止画復号化装置。 - 前記マクロブロック選択手段は、

現在マクロブロックと現在マクロブロックがイントラ予測において参照する全てのマクロブロックの復号化の順序番号の差が2以上である

ことを特徴とする請求項17記載の静止画復号化装置。 - 現在マクロブロックの座標を(i、j)とするとき、座標(i+1、j−1)に未符号化マクロブロックあるいは未復号化マクロブロックが存在する場合、そのマクロブロックを次に符号化あるいは復号化するマクロブロックとして選択する

ことを特徴とするマクロブロック順序選択方法。 - 現在マクロブロックの座標を(i、j)とするとき、座標(i+1、j−2)に未符号化マクロブロックあるいは未復号化マクロブロックが存在する場合、そのマクロブロックを次に符号化あるいは復号化するマクロブロックとして選択する

ことを特徴とするマクロブロック順序選択方法。 - マクロブロックの符号化順序とマクロブロックの出力順序が異なることを特徴とする請求項1記載の画像符号化装置。

- 符号化マクロブロック格納領域とポインタテーブルと順序変換テーブルを備えたことを特徴とする符号化マクロブロック順序変換処理部。

- 請求項22の符号化マクロブロック順序変換処理部を備えたことを特徴とする請求項1記載の画像符号化装置。

- マクロブロックの入力順序とマクロブロックの復号化順序が異なることを特徴とする請求項7記載の画像復号化装置。

- 復号待ちマクロブロック格納領域とポインタテーブルと順序変換テーブルを備えたことを特徴とする復号化マクロブロック順序変換処理部。

- 請求項25の復号化マクロブロック順序変換処理部を備えたことを特徴とする請求項7記載の画像復号化装置。

- フレームを同じ大きさの小領域に分割して符号化する装置であって、前記小領域の符号化の順序と出力順序が異なることを特徴とする画像符号化装置。

- フレームを同じ大きさの小領域に分割して符号化されたデータを復号する装置であって、

前記符号化された小領域の入力順序と復号化の順序が異なることを特徴とする画像復号化装置。 - 前記マクロブロック選択手段は、

現在マクロブロックと現在マクロブロックに対するPMV(予測動きベクトル)を求めるときに参照する全てのマクロブロックの符号化の順序番号の差が2以上であることを特徴とする請求項1記載の画像符号化装置。 - 前記マクロブロック選択手段は、

現在マクロブロックの座標を(i、j)とするとき、座標(i+1、j−2)に未符号化マクロブロックが存在する場合、そのマクロブロックを次に符号化するマクロブロックとして選択することを特徴とする請求項29記載の画像符号化装置。 - 動きベクトル探索ユニットと動きベクトル探索以降の処理を行うエンコードユニットを備え、

動きベクトル探索と動きベクトル探索以降のエンコード処理をパイプライン処理することを特徴とする請求項29記載の画像符号化装置。 - マクロブロック単位に並列に動作することができる複数の動きベクトル探索ユニットと

1個あるいは複数個のエンコードユニットを備え、

複数のマクロブロックに対する動きベクトル探索を並列に行い、

動きベクトル探索とエンコードをパイプライン処理することを特徴とする請求項29記載の画像符号化装置。 - マクロブロックのエンコード処理を複数のステージで行い、

各ステージを別のユニットが実行し、

各ステージの処理をパイプライン処理することを特徴とする請求項29記載の画像符号化装置。 - 前記マクロブロック選択ステップは、

現在マクロブロックと現在マクロブロックに対するPMV(予測動きベクトル)を求めるときに参照する全てのマクロブロックの符号化の順序番号の差が2以上である

ことを特徴とする請求項11記載の画像符号化方法。 - 現在マクロブロックの処理が他の1個あるいは複数のマクロブロックのエンコード結果に依存し、

現在マクロブロックの処理を開始する前に現在マクロブロックが依存するマクロブロックの処理が完了している必要があるような符号化方法を用いる符号化装置であって、

現在マクロブロックと現在マクロブロックが依存する他のマクロブロックの符号化の順序番号の差が2以上である

ことを特徴とする画像符号化装置。 - 現在マクロブロックの処理が他の1個あるいは複数のマクロブロックのデコード結果に依存し、

現在マクロブロックの処理を開始する前に現在マクロブロックが依存するマクロブロックの処理が完了している必要があるような復号化方法を用いる復号化装置であって、

現在マクロブロックと現在マクロブロックが依存する他のマクロブロックの復号化の順序番号の差が2以上である

ことを特徴とする画像復号化装置。 - 現在マクロブロックの処理が他の1個あるいは複数のマクロブロックのエンコード結果に依存し、

現在マクロブロックの処理を開始する前に現在マクロブロックが依存するマクロブロックの処理が完了している必要があるような符号化方法において、

現在マクロブロックと現在マクロブロックが依存する他のマクロブロックの符号化の順序番号の差が2以上である

ことを特徴とする画像符号化方法。 - 現在マクロブロックの処理が他の1個あるいは複数のマクロブロックのデコード結果に依存し、

現在マクロブロックの処理を開始する前に現在マクロブロックが依存するマクロブロックの処理が完了している必要があるような復号化方法において、

現在マクロブロックと現在マクロブロックが依存する他のマクロブロックの復号化の順序番号の差が2以上である

ことを特徴とする画像復号化方法。 - 現在マクロブロックの処理が他の1個あるいは複数のマクロブロックのエンコード結果に依存し、

現在マクロブロックの処理を開始する前に現在マクロブロックが依存するマクロブロックの処理が完了している必要があるような符号化方法を用い、

現在マクロブロックと現在マクロブロックが依存する他のマクロブロックの符号化の順序番号の差が2以上である

ことを特徴とする画像符号化プログラム。 - 現在マクロブロックの処理が他の1個あるいは複数のマクロブロックのデコード結果に依存し、

現在マクロブロックの処理を開始する前に現在マクロブロックが依存するマクロブロックの処理が完了している必要があるような復号化方法を用い、

現在マクロブロックと現在マクロブロックが依存する他のマクロブロックの復号化の順序番号の差が2以上である

ことを特徴とする画像復号化プログラム。 - MBAFF(マクロブロック適応フレーム/フィールド)を含む符号化方法を用いる符号化装置であって、

上下の2個のマクロブロックをペアにし、マクロブロックペアに対して符号化順序を決めるとき、

現在マクロブロックペアの左、上、左上、右上のマクロブロックペアと現在マクロブロックペアの符号化の順序番号の差が2以上であることを特徴とする画像符号化装置。 - MBAFFを含む符号化方法を用いる符号化方法であって、

上下の2個のマクロブロックをペアにし、マクロブロックペアに対して符号化順序を決めるとき、

現在マクロブロックペアの左、上、左上、右上のマクロブロックペアと現在マクロブロックペアの符号化の順序番号の差が2以上であることを特徴とする画像符号化方法。 - MBAFFを含む符号化方法を用いる符号化方法であって、

上下の2個のマクロブロックをペアにし、マクロブロックペアに対して符号化順序を決めるとき、

現在マクロブロックペアの左、上、左上、右上のマクロブロックペアと現在マクロブロックペアの符号化の順序番号の差が2以上であることを特徴とする画像符号化プログラム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005065288A JP4577048B2 (ja) | 2004-03-11 | 2005-03-09 | 画像符号化方法、画像符号化装置および画像符号化プログラム |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004068595 | 2004-03-11 | ||

| JP2005065288A JP4577048B2 (ja) | 2004-03-11 | 2005-03-09 | 画像符号化方法、画像符号化装置および画像符号化プログラム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005295526A true JP2005295526A (ja) | 2005-10-20 |

| JP2005295526A5 JP2005295526A5 (ja) | 2008-04-24 |

| JP4577048B2 JP4577048B2 (ja) | 2010-11-10 |

Family

ID=35327903

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005065288A Expired - Fee Related JP4577048B2 (ja) | 2004-03-11 | 2005-03-09 | 画像符号化方法、画像符号化装置および画像符号化プログラム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4577048B2 (ja) |

Cited By (36)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006129284A (ja) * | 2004-10-29 | 2006-05-18 | Sony Corp | 符号化及び復号装置並びに符号化及び復号方法 |

| JP2006166459A (ja) * | 2004-12-09 | 2006-06-22 | Samsung Electronics Co Ltd | 動きベクタ演算装置及びその方法 |

| JP2007124409A (ja) * | 2005-10-28 | 2007-05-17 | Matsushita Electric Ind Co Ltd | 画像符号化装置 |

| WO2007055158A1 (ja) * | 2005-11-08 | 2007-05-18 | Matsushita Electric Industrial Co., Ltd. | 動画像符号化方法、動画像復号化方法および装置 |

| JP2007166192A (ja) * | 2005-12-13 | 2007-06-28 | Toshiba Corp | 情報処理装置、制御方法およびプログラム |

| JP2007531460A (ja) * | 2004-03-30 | 2007-11-01 | アップル インコーポレイテッド | 縮小サイズまたはフルサイズでの再生を動的に選択的に行うための複数の独立した符号化チェーンを備えるビデオ符号化システム |

| JP2007295423A (ja) * | 2006-04-27 | 2007-11-08 | Sony Corp | 画像データの処理装置、画像データの処理方法、画像データの処理方法のプログラム及び画像データの処理方法のプログラムを記録した記録媒体 |

| WO2007129433A1 (ja) * | 2006-04-17 | 2007-11-15 | Toshihiro Minami | 動画像符号化装置および動画像符号化方法 |

| JP2007306276A (ja) * | 2006-05-11 | 2007-11-22 | Nippon Telegr & Teleph Corp <Ntt> | 階層間予測方法,装置,プログラムおよびその記録媒体 |

| JP2007312427A (ja) * | 2006-04-17 | 2007-11-29 | Toshihiro Minami | 動画像符号化装置 |

| WO2007136088A1 (ja) * | 2006-05-24 | 2007-11-29 | Panasonic Corporation | 画像符号化装置、画像符号化方法、及び画像符号化用集積回路 |

| JP2008005545A (ja) * | 2006-04-17 | 2008-01-10 | Toshihiro Minami | 動画像符号化装置および動画像符号化方法 |

| JP2008042571A (ja) * | 2006-08-07 | 2008-02-21 | Renesas Technology Corp | 動画符号化と動画復号とのいずれかを実行する機能モジュールおよびそれを含む半導体集積回路 |

| JP2008048289A (ja) * | 2006-08-18 | 2008-02-28 | Fujitsu Ltd | フレーム間予測処理装置、画像符号化装置、及び画像復号化装置 |

| JP2008048199A (ja) * | 2006-08-17 | 2008-02-28 | Fujitsu Ltd | 動き予測処理装置、画像符号化装置および画像復号化装置 |

| WO2008111451A1 (ja) * | 2007-03-14 | 2008-09-18 | Nippon Telegraph And Telephone Corporation | 動きベクトル探索方法及び装置、そのプログラム並びにプログラムを記録した記録媒体 |

| JP2008271127A (ja) * | 2007-04-19 | 2008-11-06 | Nec Electronics Corp | 符号化装置 |

| US7460042B2 (en) | 2006-06-29 | 2008-12-02 | Kabushiki Kaisha Toshiba | Encoding circuit, decoding circuit, encoder circuit, decoder circuit, and CABAC processing method |

| JP2008294669A (ja) * | 2007-05-23 | 2008-12-04 | Toshiba Corp | 画像符号化装置 |

| JP2009510845A (ja) * | 2005-09-22 | 2009-03-12 | クゥアルコム・インコーポレイテッド | ビデオエンコードのための多次元近隣ブロック予測 |

| JP2009526499A (ja) * | 2006-02-09 | 2009-07-16 | クゥアルコム・インコーポレイテッド | ビデオ符号化 |

| JP2009290498A (ja) * | 2008-05-29 | 2009-12-10 | Renesas Technology Corp | 画像符号化装置及び画像符号化方法 |

| JP2011239074A (ja) * | 2010-05-07 | 2011-11-24 | Fujitsu Semiconductor Ltd | 動きベクトル生成回路及び動きベクトル生成方法 |

| WO2011161949A1 (ja) * | 2010-06-23 | 2011-12-29 | パナソニック株式会社 | 画像復号装置、画像復号方法、集積回路およびプログラム |

| US8144770B2 (en) | 2006-09-14 | 2012-03-27 | Electronics And Telecommunications Research Institute | Apparatus and method for encoding moving picture |

| US8265142B2 (en) | 2007-03-14 | 2012-09-11 | Nippon Telegraph And Telephone Corporation | Encoding bit-rate control method and apparatus, program therefor, and storage medium which stores the program |

| CN103155566A (zh) * | 2010-11-02 | 2013-06-12 | 松下电器产业株式会社 | 动态图像编码方法以及动态图像编码装置 |

| WO2014003367A1 (ko) * | 2012-06-26 | 2014-01-03 | 엘지전자 주식회사 | 영상 복호화 방법 및 이를 이용하는 장치 |

| JPWO2012046435A1 (ja) * | 2010-10-04 | 2014-02-24 | パナソニック株式会社 | 画像処理装置、画像符号化方法および画像処理方法 |

| US9161042B2 (en) | 2007-03-14 | 2015-10-13 | Nippon Telegraph And Telephone Corporation | Quantization control method and apparatus, program therefor, and storage medium which stores the program |

| JP2016136700A (ja) * | 2015-01-23 | 2016-07-28 | キヤノン株式会社 | 画像符号化装置、画像符号化方法及びプログラム |

| US9455739B2 (en) | 2007-03-14 | 2016-09-27 | Nippon Telegraph And Telephone Corporation | Code amount estimating method and apparatus, and program and storage medium therefor |

| US9723308B2 (en) | 2012-02-28 | 2017-08-01 | Panasonic Intellectual Property Management Co., Ltd. | Image processing apparatus and image processing method |

| JP2018535601A (ja) * | 2015-11-24 | 2018-11-29 | サムスン エレクトロニクス カンパニー リミテッド | 符号化順序符号化方法及びその装置、該復号方法及びその装置 |

| CN108989804A (zh) * | 2018-08-23 | 2018-12-11 | 杭州雄迈集成电路技术有限公司 | 图像的编码方法及装置 |

| DE102015114978B4 (de) | 2014-09-19 | 2023-09-21 | Imagination Technologies Limited | Datenkomprimierung |

-

2005

- 2005-03-09 JP JP2005065288A patent/JP4577048B2/ja not_active Expired - Fee Related

Non-Patent Citations (2)

| Title |

|---|

| CSNH199800303016, 祇園 雅弘 Masahiro Gion, "マルチメディア特集", National TECHNICAL REPORT 第40巻 第6号, 第40巻, p.122−128, 松下電器産業株式会社 * |

| JPN6009067374, 祇園 雅弘 Masahiro Gion, "マルチメディア特集", National TECHNICAL REPORT 第40巻 第6号, 第40巻, p.122−128, 松下電器産業株式会社 * |

Cited By (65)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007531460A (ja) * | 2004-03-30 | 2007-11-01 | アップル インコーポレイテッド | 縮小サイズまたはフルサイズでの再生を動的に選択的に行うための複数の独立した符号化チェーンを備えるビデオ符号化システム |

| US7881541B2 (en) * | 2004-10-29 | 2011-02-01 | Sony Corporation | Coding apparatus, decoding apparatus, coding method and decoding method |

| JP2006129284A (ja) * | 2004-10-29 | 2006-05-18 | Sony Corp | 符号化及び復号装置並びに符号化及び復号方法 |

| JP2006166459A (ja) * | 2004-12-09 | 2006-06-22 | Samsung Electronics Co Ltd | 動きベクタ演算装置及びその方法 |

| US8761259B2 (en) | 2005-09-22 | 2014-06-24 | Qualcomm Incorporated | Multi-dimensional neighboring block prediction for video encoding |

| JP2009510845A (ja) * | 2005-09-22 | 2009-03-12 | クゥアルコム・インコーポレイテッド | ビデオエンコードのための多次元近隣ブロック予測 |

| JP2007124409A (ja) * | 2005-10-28 | 2007-05-17 | Matsushita Electric Ind Co Ltd | 画像符号化装置 |

| US8059717B2 (en) | 2005-10-28 | 2011-11-15 | Panasonic Corporation | Image coding apparatus, method and program for intra prediction using specified H.264 prediction modes in specified scan order |

| US9137538B2 (en) | 2005-11-08 | 2015-09-15 | Panasonic Intellectual Property Corporation Of America | Moving picture coding method, moving picture decoding method, and apparatuses of the same |

| JP4927753B2 (ja) * | 2005-11-08 | 2012-05-09 | パナソニック株式会社 | 動画像符号化方法、動画像復号化方法、動画像符号化装置、動画像復号化装置、および半導体装置 |

| US8295351B2 (en) | 2005-11-08 | 2012-10-23 | Panasonic Corporation | Moving picture coding method, moving picture decoding method, and apparatuses of the same |

| WO2007055158A1 (ja) * | 2005-11-08 | 2007-05-18 | Matsushita Electric Industrial Co., Ltd. | 動画像符号化方法、動画像復号化方法および装置 |

| US10375401B2 (en) | 2005-11-08 | 2019-08-06 | Sun Patent Trust | Moving picture coding method, moving picture decoding method, and apparatuses of the same |

| US10104381B2 (en) | 2005-11-08 | 2018-10-16 | Sun Patent Trust | Moving picture coding method, moving picture decoding method, and apparatuses of the same |

| JP2007166192A (ja) * | 2005-12-13 | 2007-06-28 | Toshiba Corp | 情報処理装置、制御方法およびプログラム |

| JP2009526499A (ja) * | 2006-02-09 | 2009-07-16 | クゥアルコム・インコーポレイテッド | ビデオ符号化 |

| US8208548B2 (en) | 2006-02-09 | 2012-06-26 | Qualcomm Incorporated | Video encoding |

| JP2007312340A (ja) * | 2006-04-17 | 2007-11-29 | Toshihiro Minami | 動画像符号化装置 |

| JP2008005545A (ja) * | 2006-04-17 | 2008-01-10 | Toshihiro Minami | 動画像符号化装置および動画像符号化方法 |

| WO2007129433A1 (ja) * | 2006-04-17 | 2007-11-15 | Toshihiro Minami | 動画像符号化装置および動画像符号化方法 |

| JP2007312427A (ja) * | 2006-04-17 | 2007-11-29 | Toshihiro Minami | 動画像符号化装置 |

| US8279942B2 (en) | 2006-04-27 | 2012-10-02 | Sony Corporation | Image data processing apparatus, image data processing method, program for image data processing method, and recording medium recording program for image data processing method |

| JP2007295423A (ja) * | 2006-04-27 | 2007-11-08 | Sony Corp | 画像データの処理装置、画像データの処理方法、画像データの処理方法のプログラム及び画像データの処理方法のプログラムを記録した記録媒体 |

| JP2007306276A (ja) * | 2006-05-11 | 2007-11-22 | Nippon Telegr & Teleph Corp <Ntt> | 階層間予測方法,装置,プログラムおよびその記録媒体 |

| US9667972B2 (en) | 2006-05-24 | 2017-05-30 | Panasonic Intellectual Property Management Co., Ltd. | Image coding device, image coding method, and image coding integrated circuit |

| JP2013258732A (ja) * | 2006-05-24 | 2013-12-26 | Panasonic Corp | 画像符号化装置、画像符号化方法、及び画像符号化用集積回路 |

| WO2007136088A1 (ja) * | 2006-05-24 | 2007-11-29 | Panasonic Corporation | 画像符号化装置、画像符号化方法、及び画像符号化用集積回路 |

| US7460042B2 (en) | 2006-06-29 | 2008-12-02 | Kabushiki Kaisha Toshiba | Encoding circuit, decoding circuit, encoder circuit, decoder circuit, and CABAC processing method |

| JP2008042571A (ja) * | 2006-08-07 | 2008-02-21 | Renesas Technology Corp | 動画符号化と動画復号とのいずれかを実行する機能モジュールおよびそれを含む半導体集積回路 |

| JP2008048199A (ja) * | 2006-08-17 | 2008-02-28 | Fujitsu Ltd | 動き予測処理装置、画像符号化装置および画像復号化装置 |

| JP2008048289A (ja) * | 2006-08-18 | 2008-02-28 | Fujitsu Ltd | フレーム間予測処理装置、画像符号化装置、及び画像復号化装置 |

| US8144770B2 (en) | 2006-09-14 | 2012-03-27 | Electronics And Telecommunications Research Institute | Apparatus and method for encoding moving picture |

| WO2008111451A1 (ja) * | 2007-03-14 | 2008-09-18 | Nippon Telegraph And Telephone Corporation | 動きベクトル探索方法及び装置、そのプログラム並びにプログラムを記録した記録媒体 |

| US9161042B2 (en) | 2007-03-14 | 2015-10-13 | Nippon Telegraph And Telephone Corporation | Quantization control method and apparatus, program therefor, and storage medium which stores the program |

| US8265142B2 (en) | 2007-03-14 | 2012-09-11 | Nippon Telegraph And Telephone Corporation | Encoding bit-rate control method and apparatus, program therefor, and storage medium which stores the program |

| US8396130B2 (en) | 2007-03-14 | 2013-03-12 | Nippon Telegraph And Telephone Corporation | Motion vector search method and apparatus, program therefor, and storage medium which stores the program |

| US9455739B2 (en) | 2007-03-14 | 2016-09-27 | Nippon Telegraph And Telephone Corporation | Code amount estimating method and apparatus, and program and storage medium therefor |

| RU2420913C1 (ru) * | 2007-03-14 | 2011-06-10 | Ниппон Телеграф Энд Телефон Корпорейшн | Способ и устройство нахождения вектора движения, программа и носитель записи для хранения программы |

| CN101682775B (zh) * | 2007-03-14 | 2015-04-01 | 日本电信电话株式会社 | 运动矢量搜索方法和装置 |

| JPWO2008111451A1 (ja) * | 2007-03-14 | 2010-06-24 | 日本電信電話株式会社 | 動きベクトル探索方法及び装置、そのプログラム並びにプログラムを記録した記録媒体 |

| JP2008271127A (ja) * | 2007-04-19 | 2008-11-06 | Nec Electronics Corp | 符号化装置 |

| JP2008294669A (ja) * | 2007-05-23 | 2008-12-04 | Toshiba Corp | 画像符号化装置 |

| JP2009290498A (ja) * | 2008-05-29 | 2009-12-10 | Renesas Technology Corp | 画像符号化装置及び画像符号化方法 |

| JP2011239074A (ja) * | 2010-05-07 | 2011-11-24 | Fujitsu Semiconductor Ltd | 動きベクトル生成回路及び動きベクトル生成方法 |

| US10033997B2 (en) | 2010-06-23 | 2018-07-24 | Panasonic Intellectual Property Management Co., Ltd. | Image decoding apparatus, image decoding method, integrated circuit, and program |

| WO2011161949A1 (ja) * | 2010-06-23 | 2011-12-29 | パナソニック株式会社 | 画像復号装置、画像復号方法、集積回路およびプログラム |

| JPWO2012046435A1 (ja) * | 2010-10-04 | 2014-02-24 | パナソニック株式会社 | 画像処理装置、画像符号化方法および画像処理方法 |

| US9414059B2 (en) | 2010-10-04 | 2016-08-09 | Panasonic Intellectual Property Management Co., Ltd. | Image processing device, image coding method, and image processing method |

| CN103155566B (zh) * | 2010-11-02 | 2016-08-31 | 松下知识产权经营株式会社 | 动态图像编码方法以及动态图像编码装置 |

| CN103155566A (zh) * | 2010-11-02 | 2013-06-12 | 松下电器产业株式会社 | 动态图像编码方法以及动态图像编码装置 |

| US9723308B2 (en) | 2012-02-28 | 2017-08-01 | Panasonic Intellectual Property Management Co., Ltd. | Image processing apparatus and image processing method |

| WO2014003367A1 (ko) * | 2012-06-26 | 2014-01-03 | 엘지전자 주식회사 | 영상 복호화 방법 및 이를 이용하는 장치 |

| DE102015114978B4 (de) | 2014-09-19 | 2023-09-21 | Imagination Technologies Limited | Datenkomprimierung |

| JP2016136700A (ja) * | 2015-01-23 | 2016-07-28 | キヤノン株式会社 | 画像符号化装置、画像符号化方法及びプログラム |

| JP2021106424A (ja) * | 2015-11-24 | 2021-07-26 | サムスン エレクトロニクス カンパニー リミテッド | 符号化順序符号化方法及びその装置、該復号方法及びその装置 |

| US10979713B2 (en) | 2015-11-24 | 2021-04-13 | Samsung Electronics Co., Ltd. | Encoding sequence encoding method and device thereof, and decoding method and device thereof |

| US11089306B2 (en) | 2015-11-24 | 2021-08-10 | Samsung Electronics Co., Ltd. | Encoding sequence encoding method and device thereof, and decoding method and device thereof |

| JP7069379B2 (ja) | 2015-11-24 | 2022-05-17 | サムスン エレクトロニクス カンパニー リミテッド | 符号化順序符号化方法及びその装置、該復号方法及びその装置 |

| US11363269B2 (en) | 2015-11-24 | 2022-06-14 | Samsung Electronics Co., Ltd. | Encoding sequence encoding method and device thereof, and decoding method and device thereof |

| JP2022093628A (ja) * | 2015-11-24 | 2022-06-23 | サムスン エレクトロニクス カンパニー リミテッド | 符号化順序符号化方法及びその装置、該復号方法及びその装置 |

| JP7274022B2 (ja) | 2015-11-24 | 2023-05-15 | サムスン エレクトロニクス カンパニー リミテッド | 符号化順序符号化方法及びその装置、該復号方法及びその装置 |

| JP2018535601A (ja) * | 2015-11-24 | 2018-11-29 | サムスン エレクトロニクス カンパニー リミテッド | 符号化順序符号化方法及びその装置、該復号方法及びその装置 |

| US11812023B2 (en) | 2015-11-24 | 2023-11-07 | Samsung Electronics Co., Ltd. | Encoding sequence encoding method and device thereof, and decoding method and device thereof |

| CN108989804B (zh) * | 2018-08-23 | 2021-04-27 | 杭州雄迈集成电路技术股份有限公司 | 图像的编码方法及装置 |

| CN108989804A (zh) * | 2018-08-23 | 2018-12-11 | 杭州雄迈集成电路技术有限公司 | 图像的编码方法及装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4577048B2 (ja) | 2010-11-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4577048B2 (ja) | 画像符号化方法、画像符号化装置および画像符号化プログラム | |

| KR102518242B1 (ko) | 영상 정보 부호화 방법 및 복호화 방법 | |

| JP5049009B2 (ja) | マクロブロックフィールド/フレームコード化タイプ情報のためのビットプレーンコーディングおよびデコーディング | |

| US7688894B2 (en) | Scan patterns for interlaced video content | |

| JP5442568B2 (ja) | スキップマクロブロックコード化 | |

| JP5128794B2 (ja) | 映像のイントラ予測符号化及び復号化方法、並びに装置 | |

| JP5047995B2 (ja) | 映像のイントラ予測符号化、復号化方法及び装置 | |

| JP5219089B2 (ja) | 画像データの生成方法 | |

| JP2009094828A (ja) | 画像符号化装置及び画像符号化方法、画像復号化装置及び画像復号化方法 | |

| JP2010135864A (ja) | 画像符号化方法及び装置並びに画像復号化方法及び装置 | |

| JP5400798B2 (ja) | 動画像復号化方法及び装置、動画像符号化方法及び装置 | |

| CN101889405A (zh) | 用于执行运动估计的方法和装置 | |

| KR20100133006A (ko) | 동화상 부호화/복호화 방법 및 장치 | |

| KR20060109290A (ko) | 화상 복호 장치 및 화상 복호 방법과 화상 복호 프로그램 | |

| JPH07170520A (ja) | 映像信号の復合化方法 | |

| KR20200139116A (ko) | 영상 정보 부호화 방법 및 복호화 방법 | |

| JP2013125973A (ja) | 画像符号化方法,画像復号方法,画像符号化装置,画像復号装置,画像符号化プログラムおよび画像復号プログラム | |

| KR101496324B1 (ko) | 영상의 부호화, 복호화 방법 및 장치 | |

| CN104519367A (zh) | 视频解码处理装置及其操作方法 | |

| KR100677118B1 (ko) | 움직임 추정 방법 및 그 장치 | |

| JP2011010197A (ja) | 画像符号化装置及び画像復号装置 | |

| US8363722B2 (en) | Method and apparatus for hierarchical bi-directional intra-prediction in a video encoder | |

| KR19990063464A (ko) | 동화상 복호화 장치 및 동화상 복호화 방법 | |

| JP2007013298A (ja) | 画像符号化装置 | |

| JP5219062B2 (ja) | 画像データの生成方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080310 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080310 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20080414 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20091126 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091217 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100105 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100302 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100511 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100601 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100727 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100809 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130903 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4577048 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130903 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |