JP2005295216A - データ処理装置及びプログラム - Google Patents

データ処理装置及びプログラム Download PDFInfo

- Publication number

- JP2005295216A JP2005295216A JP2004107597A JP2004107597A JP2005295216A JP 2005295216 A JP2005295216 A JP 2005295216A JP 2004107597 A JP2004107597 A JP 2004107597A JP 2004107597 A JP2004107597 A JP 2004107597A JP 2005295216 A JP2005295216 A JP 2005295216A

- Authority

- JP

- Japan

- Prior art keywords

- bits

- bit string

- output

- bit

- input

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000012545 processing Methods 0.000 title claims abstract description 64

- 230000006870 function Effects 0.000 claims description 4

- 238000012217 deletion Methods 0.000 abstract description 74

- 230000037430 deletion Effects 0.000 abstract description 74

- 238000003780 insertion Methods 0.000 abstract description 73

- 230000037431 insertion Effects 0.000 abstract description 73

- 238000001514 detection method Methods 0.000 abstract description 43

- 238000000034 method Methods 0.000 description 91

- 230000005540 biological transmission Effects 0.000 description 10

- 238000010586 diagram Methods 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 5

- 230000002159 abnormal effect Effects 0.000 description 4

- 238000012966 insertion method Methods 0.000 description 4

- 238000012937 correction Methods 0.000 description 2

- 230000001360 synchronised effect Effects 0.000 description 2

- 230000007423 decrease Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 230000008520 organization Effects 0.000 description 1

- 238000013519 translation Methods 0.000 description 1

Images

Landscapes

- Communication Control (AREA)

Abstract

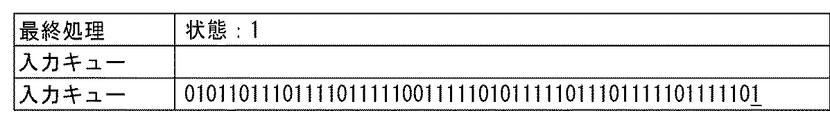

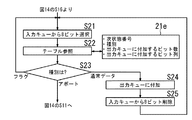

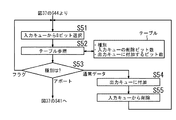

【解決手段】0挿入部12では、入力キュー記憶部12bに記憶されたデータを8ビット単位でバッファメモリ12c に読み込み、0挿入テーブル12eを検索して、0挿入処理を行い、0挿入処理を受けたデータをバッファメモリ12c から出力キュー記憶部12dへ送出する。入力キューから選択される所定数の入力ビット列は、その並びに関係なく処理され、出力キューに付加されるので、0挿入処理の処理回数は入力キュー記憶部12bから読み込まれる入力キューのビット列の並びとは無関係となる。0削除及びフラグ検出部21の処理についても同様である。

【選択図】 図1

Description

乃至51を参照しながら、特許文献1に開示されたビット・スタッフィング方法について説明する。

請求項2に係る発明は、入力キューから0削除を行い出力キューを生成するデータ処理装置であって、前記入力キューから所定ビット数毎にビット列を選択して入力ビット列とする手段と、前回の入力ビット列と前回の出力ビット列との差異に対応する状態データ、前記所定ビット数のビット列の並び、出力ビット列、及び次回の状態データの組合せが予め記憶されたテーブルを検索して、前記入力ビット列に対応する出力ビット列及び次回の状態データを読み出す手段と、前記出力ビット列を前記出力キューに付加する手段とを備えたことを特徴とするデータ処理装置である。

請求項3に係る発明は、入力キューに0挿入を行い出力キューを生成するデータ処理装置のコンピュータを、前記入力キューから所定ビット数毎にビット列を選択して入力ビット列とする手段と、前回の入力ビット列と前回の出力ビット列との差異に対応する状態データ、前記所定ビット数のビット列の並び、出力ビット列、及び次回の状態データの組合せが予め記憶されたテーブルを検索して、前記入力ビット列に対応する出力ビット列及び次回の状態データを読み出す手段と、前記出力ビット列を前記出力キューに付加する手段として機能させることを特徴とするプログラムである。

請求項4に係る発明は、入力キューから0削除を行い出力キューを生成するデータ処理装置のコンピュータを、前記入力キューから所定ビット数毎にビット列を選択して入力ビット列とする手段と、前回の入力ビット列と前回の出力ビット列との差異に対応する状態データ、前記所定ビット数のビット列の並び、出力ビット列、及び次回の状態データの組合せが予め記憶されたテーブルを検索して、前記入力ビット列に対応する出力ビット列及び次回の状態データを読み出す手段と、前記出力ビット列を前記出力キューに付加する手段として機能させることを特徴とするプログラムである。

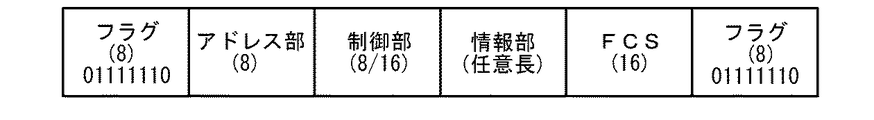

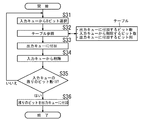

図1は本発明の実施形態に係る送信回路及び受信制御回路の構成を示すブロック図である。送信制御回路1は、FCS生成部11と、その出力側に接続された0挿入部12と、その出力側に接続されたフラグ生成部13とを備えている。受信制御回路2は、0削除及びフラグ検出部21と、その出力側に接続されたエラー検出部22とからなる。

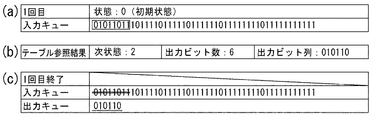

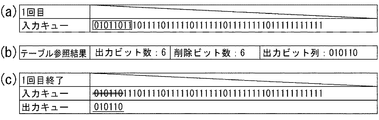

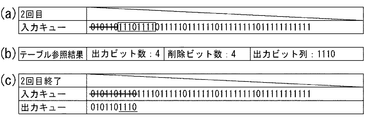

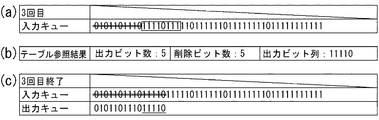

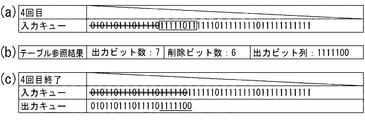

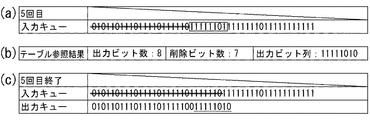

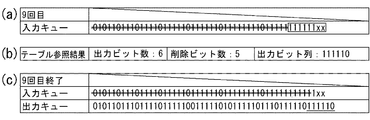

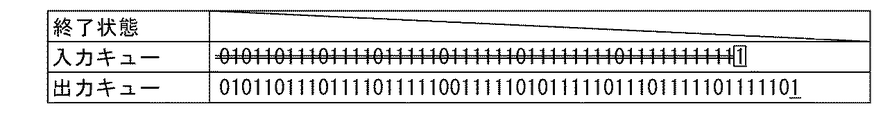

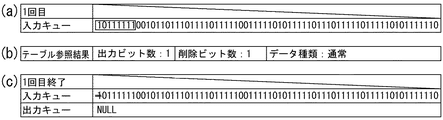

まず、0挿入テーブル12eの内容を説明する。本実施形態では、入力キュー記憶部12bから8ビットずつデータがバッファメモリ12cに読み込まれ、0挿入が必要な場合、つまり1が5個続いた場合には0挿入処理を受け、出力キュー記憶部12dへ送出される。また、入力キュー記憶部12bから例えば図28(a)に示した11101111が読み込まれた場合、出力キュー記憶部12dへ送出されるのは図28(c)と同様、1110となり、1111は送出されない。本実施形態では、この1111からなる残りビットを状態番号として保存し、次回に入力キュー記憶部12bから読み込まれる8ビットと同時に扱う。

[1]状態番号が0のテーブルの場合

下記(1)〜(4)の手順で作成する。

(1)対象とする8ビットについて、順にビットを調べ、0挿入が必要か否かを判定する。

・0挿入が必要か否かは1が5個連続しているか、途中で0が出現するかを確認する。

・1の連続数が5個未満の場合、そのまま取り出しビットの並びとすることができる。

・1の連続数が5個に達した場合、続けて0を挿入する事によってそれまで判定したビット列は、取り出しビットの並びとし、1の連続数も0から数え直す。

(ア)8ビット目が0で終了した状態(1の連続数が0)

(イ)8ビット目で1の連続数が5になり、0挿入をした直後の状態(1の連続数が0)

(ウ)8ビット目では1の連続数が1以上5未満であり、次の取り出しビットに影響を与える状態

残りビット無しの場合 → 次状態:0

残りビット1の場合 → 次状態番号:1

残りビット11の場合 → 次状態番号:2

残りビット111の場合 → 次状態番号:3

残りビット1111の場合 → 次状態番号:4

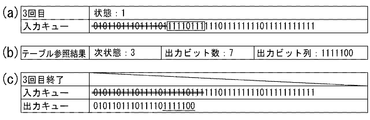

下記(1)〜(5)の手順で作成する。

(1)状態番号により、対象とする8ビットの前に以下のビットを加える。

状態番号:1→1+(対象とする8ビット)

状態番号:2→11+(対象とする8ビット)

状態番号:3→111+(対象とする8ビット)

状態番号:4→1111+(対象とする8ビット)

<判定の法則>

・0挿入が必要か否かは1が5個連続しているか、途中で0が出現するかを確認する。

・1の連続数が5個未満の場合、そのまま取り出しビットの並びとすることができる。

・1の連続数が5個に達した場合、続けて0を挿入する事によってそれまで判定したビット列は、取り出しビットの並びとし、1の連続数も0から数え直す。

(ア)最後のビットが0で終了した状態(1の連続数が0)

(イ)最後のビットで1の連続数が5になり、0挿入をした直後の状態(1の連続数が0)

(ウ)最後のビットでは1の連続数が1以上5未満であり、次の取り出しビットに影響を与える状態

残りビット無しの場合 → 次状態番号:0

残りビット1の場合 → 次状態番号:1

残りビット11の場合 → 次状態番号:2

残りビット111の場合 → 次状態番号:3

残りビット1111の場合 → 次状態番号:4

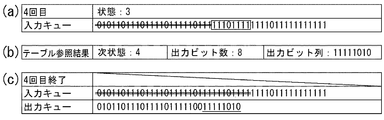

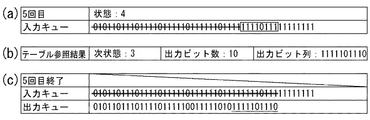

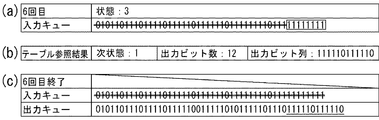

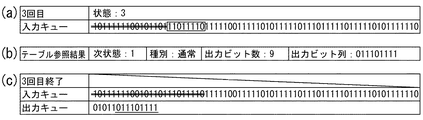

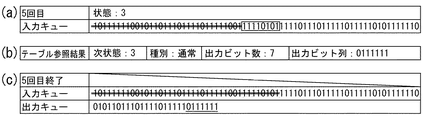

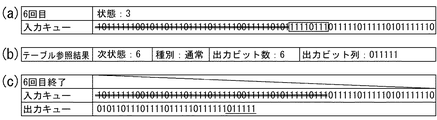

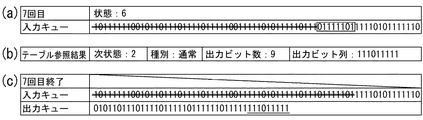

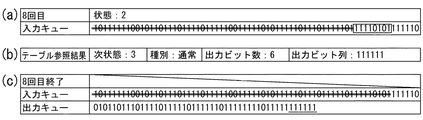

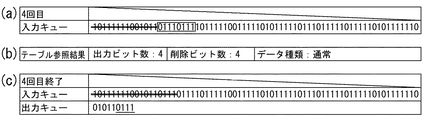

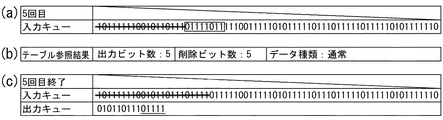

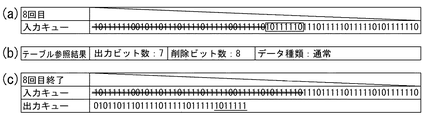

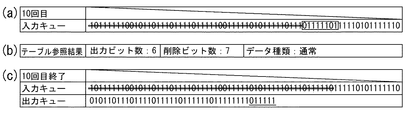

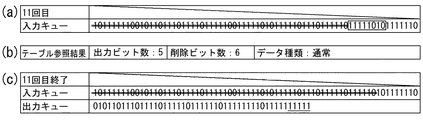

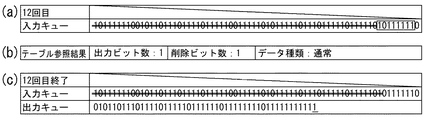

(1)状態2であるから、前回のビット列は11で終了した状態であり、これに10111101を合わせて判定ビット列は1110111101と考えることができる。

(2)(1)で作成したビット列について、0挿入の必要を考慮しながら、取り出しビットを作成すると、111011110+1と分割できる。

(3)よって、取り出しビットは、111011110、ビット数「9」を得る。残りの「1」については次状態に影響を与えるため、今回はデータを確定できず、次の状態を1とする。

(4)以上から、状態番号:2、入力ビット列:10111101の変換テーブルとして、

次状態番号:1 、出力ビット数:9、出力ビット列=111011110

が得られる。

[1]状態0のテーブルの場合

下記(1)〜(5)の手順により作成する。

<判定の法則>

・0挿入が必要か否かは1が5個連続しているか、途中で0が出現するかを確認する。

ただし、フラグの存在も考慮する為、1から始まる1の連続の場合と、0から始まる1の連続は区別する必要がある。

・1から始まる1の連続の場合で、1の連続数が5未満の場合、そのまま取り出しビットの並びとする。

・1から始まる1の連続の場合で、1の連続数が5個で次に続くビットが0の場合、その0を削除したものを取り出しビットの

の並びとする。

・1から始まる1の連続の場合で、1の連続数が6個になる場合、無効なデータであるので, 種別を「無効(アボート)」とする。

・0から始まる1の連続の場合で、1の連続数が5未満の場合、そのまま取り出しビットの並びとする。

・0から始まる1の連続の場合で、1の連続数が5個で次に続くビットが0の場合、その0を削除したものを取り出しビット

の並びとする。

・0から始まる1の連続の場合で、1の連続数が6個で次に続くビットが0の場合、そのビット並びはフラグをあらわすので、

種別を「フラグ」とする。このとき、フラグに該当する01111110の並びは取り出しビットには含めない。

・0から始まる1の連続の場合で、1の連続数が7個になる場合、無効なデータであるので、種別を「無効」とする。

(ア)8ビット目が0で終了した場合

(イ)7ビット目まで1が5個連続し、8ビット目の0を削除して終了した場合

(ウ)8ビット目では1の連続数が1以上6未満で有り、次の取り出しビットに処理が依存する場合

(エ)データ種別が「異常」な場合

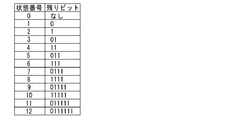

残りビットが0の場合→次状態番号:1

残りビットが1の場合→次状態番号:2

残りビットが01の場合→次状態番号:3

残りビットが11の場合→次状態番号:4

残りビットが011の場合→次状態番号:5

残りビットが111の場合→次状態番号:6

残りビットが0111の場合→次状態番号:7

残りビットが1111の場合→次状態番号:8

残りビットが01111の場合→次状態番号:9

残りビットが11111の場合→次状態番号:10

残りビットが011111の場合→次状態番号:11

残りビットが0111111の場合→次状態番号:12

(5)(エ)の状態の場合、データ種別を「異常」とする。

下記(1)〜(6)の手順により作成する。

(1)状態により、対象とする8ビットの前に以下のビットを加える。

状態番号:1→0+(対象とする8ビット)

状態番号:2→1+(対象とする8ビット)

状態番号:3→01+(対象とする8ビット)

状態番号:4→11+(対象とする8ビット)

状態番号:5→011+(対象とする8ビット)

状態番号:6→111+(対象とする8ビット)

状態番号:7→0111+(対象とする8ビット)

状態番号:8→1111+(対象とする8ビット)

状態番号:9→01111+(対象とする8ビット)

状態番号:10→11111+(対象とする8ビット)

状態番号:11→011111+(対象とする8ビット)

状態番号:12→0111111+(対象とする8ビット)

<判定の法則>

・0挿入が必要か否かは1が5個連続しているか、途中で0が出現するかを確認する。

ただし、フラグの存在も考慮する為、1から始まる1の連続と、0から始まる1の連続とは区別する必要がある。

・1から始まる1の連続の場合で、1の連続数が5未満の場合、そのまま取り出しビットの並びとする。

・1から始まる1の連続の場合で、1の連続数が5個で次に続くビットが0の場合、その0を削除したものを取り出しビットの並びとする。

・1から始まる1の連続の場合で、1の連続数が6個になる場合、無効なデータであるので、種別を「無効」とする。

・0から始まる1の連続の場合で、1の連続数が5未満の場合、そのまま取り出しビットの並びとする。

・0から始まる1の連続の場合で、1の連続数が5個で次に続くビットが0の場合、その0を削除したものを取り出しビット

の並びとする。

・0から始まる1の連続の場合で、1の連続数が6個で次に続くビットが0の場合、そのビット並びはフラグをあらわすので、

種別を「フラグ」とする。このとき、フラグに該当する01111110の並びは取り出しビットには含めない。

・0から始まる1の連続の場合で、1の連続数が7個になる場合、無効なデータであるので、種別を「無効」とする。

(ア)8ビット目が0で終了した場合

(イ)7ビット目まで1が5個連続し、8ビット目の0を削除して終了した場合

(ウ)8ビット目では1の連続数が1以上6未満で有り、次の取り出しビットに処理が依存する場合

(エ)データ種別が「異常」な場合

残りビットが0の場合→次状態番号:1

残りビットが1の場合→次状態番号:2

残りビットが01の場合→次状態番号:3

残りビットが11の場合→次状態番号:4

残りビットが011の場合→次状態番号:5

残りビットが111の場合→次状態番号:6

残りビットが0111の場合→次状態番号:7

残りビットが1111の場合→次状態番号:8

残りビットが01111の場合→次状態番号:9

残りビットが11111の場合→次状態番号:10

残りビットが011111の場合→次状態番号:11

残りビットが0111111の場合→次状態番号:12

(6)(エ)の状態の場合、データ種別を「異常」とする。

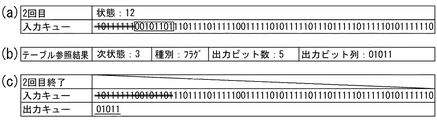

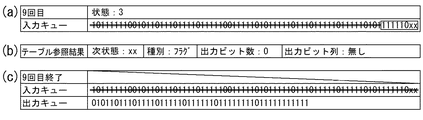

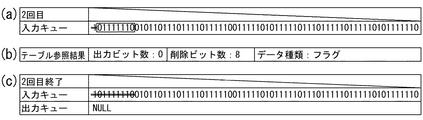

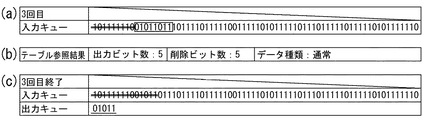

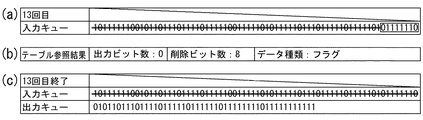

(1)状態番号:12であるから、前回のビット列は0111111で終了した状態であり、これに今回の00101101を合わせて判定ビット列は011111100101101と考えることができる。

(2) (1)で作成したビット列について、フラグの存在と0削除の必要を考慮しながら、取り出しビットを作成すると、01111110+01011+01に分割できる。よって、ひとつ目の01111110から種別はフラグ、取り出しビットは01011、ビット数5を得る。

残りの01については次状態に影響を与えるため、今回はデータを確定できず、次状態番号を3とする。

以上から、状態番号:12、入力ビット列:00101101」の変換テーブルとして、

次状態番号:3、出力ビット数:5、出力ビット列=111011110

が得られる。

Claims (4)

- 入力キューに0挿入を行い出力キューを生成するデータ処理装置であって、前記入力キューから所定ビット数毎にビット列を選択して入力ビット列とする手段と、前回の入力ビット列と前回の出力ビット列との差異に対応する状態データ、前記所定ビット数のビット列の並び、出力ビット列、及び次回の状態データの組合せが予め記憶されたテーブルを検索して、前記入力ビット列に対応する出力ビット列及び次回の状態データを読み出す手段と、前記出力ビット列を前記出力キューに付加する手段とを備えたことを特徴とするデータ処理装置。

- 入力キューから0削除を行い出力キューを生成するデータ処理装置であって、前記入力キューから所定ビット数毎にビット列を選択して入力ビット列とする手段と、前回の入力ビット列と前回の出力ビット列との差異に対応する状態データ、前記所定ビット数のビット列の並び、出力ビット列、及び次回の状態データの組合せが予め記憶されたテーブルを検索して、前記入力ビット列に対応する出力ビット列及び次回の状態データを読み出す手段と、前記出力ビット列を前記出力キューに付加する手段とを備えたことを特徴とするデータ処理装置。

- 入力キューに0挿入を行い出力キューを生成するデータ処理装置のコンピュータを、前記入力キューから所定ビット数毎にビット列を選択して入力ビット列とする手段と、前回の入力ビット列と前回の出力ビット列との差異に対応する状態データ、前記所定ビット数のビット列の並び、出力ビット列、及び次回の状態データの組合せが予め記憶されたテーブルを検索して、前記入力ビット列に対応する出力ビット列及び次回の状態データを読み出す手段と、前記出力ビット列を前記出力キューに付加する手段として機能させることを特徴とするプログラム。

- 入力キューから0削除を行い出力キューを生成するデータ処理装置のコンピュータを、前記入力キューから所定ビット数毎にビット列を選択して入力ビット列とする手段と、前回の入力ビット列と前回の出力ビット列との差異に対応する状態データ、前記所定ビット数のビット列の並び、出力ビット列、及び次回の状態データの組合せが予め記憶されたテーブルを検索して、前記入力ビット列に対応する出力ビット列及び次回の状態データを読み出す手段と、前記出力ビット列を前記出力キューに付加する手段として機能させることを特徴とするプログラム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004107597A JP4314479B2 (ja) | 2004-03-31 | 2004-03-31 | データ処理装置及びプログラム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004107597A JP4314479B2 (ja) | 2004-03-31 | 2004-03-31 | データ処理装置及びプログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005295216A true JP2005295216A (ja) | 2005-10-20 |

| JP4314479B2 JP4314479B2 (ja) | 2009-08-19 |

Family

ID=35327659

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004107597A Expired - Fee Related JP4314479B2 (ja) | 2004-03-31 | 2004-03-31 | データ処理装置及びプログラム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4314479B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009021941A (ja) * | 2007-07-13 | 2009-01-29 | Rohm Co Ltd | 情報通信端末、無線通信装置および無線通信ネットワーク |

| US8347160B2 (en) | 2007-07-13 | 2013-01-01 | Rohm Co., Ltd. | Information communication terminal, radio communication apparatus and radio communication network system capable of performing communication corresponding to purpose |

-

2004

- 2004-03-31 JP JP2004107597A patent/JP4314479B2/ja not_active Expired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009021941A (ja) * | 2007-07-13 | 2009-01-29 | Rohm Co Ltd | 情報通信端末、無線通信装置および無線通信ネットワーク |

| US8347160B2 (en) | 2007-07-13 | 2013-01-01 | Rohm Co., Ltd. | Information communication terminal, radio communication apparatus and radio communication network system capable of performing communication corresponding to purpose |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4314479B2 (ja) | 2009-08-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20110078153A1 (en) | Efficient retrieval of variable-length character string data | |

| US8532988B2 (en) | Searching for symbol string | |

| US8542137B2 (en) | Decoding encoded data | |

| JP4570509B2 (ja) | 読み生成装置、読み生成方法及びコンピュータプログラム | |

| CA2275391C (en) | File processing method, data processing device, and storage medium | |

| JP4314479B2 (ja) | データ処理装置及びプログラム | |

| US6433709B1 (en) | Decoding method and decoding apparatus for variable length code words, and computer readable recording medium for storing decoding program for variable length code words | |

| JP4356495B2 (ja) | データ処理装置及びプログラム | |

| JP4314478B2 (ja) | データ処理装置及びプログラム | |

| JP3725443B2 (ja) | Unicodeテキストを混合コードページに変換する方法およびシステム | |

| JP5853531B2 (ja) | 情報処理装置及び情報処理プログラム | |

| CN117709298B (zh) | 一种双字符流的扫描方法、电子设备、存储介质及系统 | |

| JP2005130490A (ja) | ソフトウェアによる偽同期コード保護(fsp)の復号化 | |

| JP4304146B2 (ja) | 辞書登録装置、辞書登録方法および辞書登録プログラム | |

| JPH09246988A (ja) | 復号装置及びその方法 | |

| CN114329105B (zh) | 字符串检测方法和装置 | |

| JPH09246989A (ja) | 復号装置及びその方法 | |

| JP2010140404A (ja) | 識別子短縮表示プログラム,識別子短縮表示装置および識別子短縮表示方法 | |

| JP2023143001A (ja) | 情報処理装置及びプログラム | |

| JP4329493B2 (ja) | 辞書データ圧縮装置、電子辞書装置及びプログラム | |

| US6954155B2 (en) | Data compression method and processor | |

| JP4061283B2 (ja) | 字句をデータに変換する装置、方法及びプログラム | |

| JP2918380B2 (ja) | 文字認識結果の後処理方法 | |

| JP2006031331A (ja) | プログラム変換実行計算機、及び、プログラム変換実行方法、プログラム | |

| JP2005267359A (ja) | 論理検証装置およびテストプログラムの補完方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20051031 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061030 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090416 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090422 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090505 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4314479 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120529 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120529 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130529 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130529 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |