JP2005294565A - 不揮発性半導体記憶装置およびこの不揮発性半導体記憶装置を含む半導体装置 - Google Patents

不揮発性半導体記憶装置およびこの不揮発性半導体記憶装置を含む半導体装置 Download PDFInfo

- Publication number

- JP2005294565A JP2005294565A JP2004108053A JP2004108053A JP2005294565A JP 2005294565 A JP2005294565 A JP 2005294565A JP 2004108053 A JP2004108053 A JP 2004108053A JP 2004108053 A JP2004108053 A JP 2004108053A JP 2005294565 A JP2005294565 A JP 2005294565A

- Authority

- JP

- Japan

- Prior art keywords

- memory device

- semiconductor memory

- gate electrode

- insulating film

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/024—Manufacture or treatment of FETs having insulated gates [IGFET] of fin field-effect transistors [FinFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/62—Fin field-effect transistors [FinFET]

Landscapes

- Read Only Memory (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

- Thin Film Transistor (AREA)

Abstract

【課題】

多値を記憶可能な従来の不揮発性半導体記憶装置において不可避であった、しきい値電圧のバラツキに起因する電源電圧の下限の問題を解決する。その結果、十分な低電源電圧下における動作が可能かつ多値記憶可能な、低消費電力の高性能な不揮発性半導体記憶装置およびこの不揮発性半導体記憶装置を含む半導体装置を提供する。

【解決手段】

書き込み電圧条件ないし消去電圧条件の異なる素子を並列接続することにより、2種類のしきい値を用いるのみで1ビットを超える多値の記憶可能な不揮発性半導体記憶装置を実現する。このことにより従来不可避であった、しきい値電圧のバラツキに起因する電源電圧の下限は存在しなくなり、十分な低電源電圧下の動作が可能となる。その結果、低消費電力かつ多値記憶可能な、高性能な不揮発性半導体記憶装置が実現される。

【選択図】 図1

多値を記憶可能な従来の不揮発性半導体記憶装置において不可避であった、しきい値電圧のバラツキに起因する電源電圧の下限の問題を解決する。その結果、十分な低電源電圧下における動作が可能かつ多値記憶可能な、低消費電力の高性能な不揮発性半導体記憶装置およびこの不揮発性半導体記憶装置を含む半導体装置を提供する。

【解決手段】

書き込み電圧条件ないし消去電圧条件の異なる素子を並列接続することにより、2種類のしきい値を用いるのみで1ビットを超える多値の記憶可能な不揮発性半導体記憶装置を実現する。このことにより従来不可避であった、しきい値電圧のバラツキに起因する電源電圧の下限は存在しなくなり、十分な低電源電圧下の動作が可能となる。その結果、低消費電力かつ多値記憶可能な、高性能な不揮発性半導体記憶装置が実現される。

【選択図】 図1

Description

本発明は、半導体装置に係り、更に詳しくは不揮発性半導体記憶装置に関する。

従来の不揮発性半導体記憶装置として、例えば、N型半導体基板にP型ウエル領域が形成され、このP型ウエル領域内に複数のメモリ素子が配列されたものが知られている。

前記メモリ素子は、内部に電荷を蓄積させる浮遊ゲートもしくは界面に電荷を蓄積させる酸化膜/窒化膜の積層膜(以下、電荷蓄積層と呼ぶ)と、この電荷蓄積層上に中間絶縁膜を介して積層形成された制御ゲート電極からなる積層形ゲート電極およびこのゲート電極を挟むように形成されたN型のソース・ドレイン領域を備える。電荷蓄積層への電荷の注入或いは電荷蓄積層からの電荷の放出は、前記半導体基板上に形成されたトンネル絶縁膜を介して行われる。

上述した従来の不揮発性半導体記憶装置においては、制御ゲート電極ないしソース・ドレイン領域の電位等を調節することで電荷蓄積層に電荷を注入ないし電荷蓄積層から電荷を放出させることによって浮遊ゲート電極中の電荷の量を調節し、それによって素子のしきい値電圧を変えることで情報の記憶を行っていた。この方法で情報の記憶を行う場合に、しきい値電圧が十分に高い状態と十分に低い状態との二つの状態のみを用いて1ビットのみの情報を記憶するのであれば良いが、しきい値電圧に2種類以上の値を取らせる(つまり浮遊ゲート電極中の電荷量に2種類以上の値を取らせる)ことによって1ビットを超える多値の情報を記憶しようとすると、しきい値のバラツキを十分に小さい値に収める必要がある。

一つの例として2ビットの情報を記憶する場合を考えると、しきい値電圧の値は2×2=4通りの値が必要となる。最も低いしきい値電圧は負の値としてその状態にある素子は常時オンとなる様にし、最も高いしきい値電圧は電源電圧よりも高い値としてその状態にある素子は常時オフとなる様にした場合でもゼロと電源電圧との間に2種類のしきい値電圧が収まる必要がある。それ故、電源電圧(VDDとする)としきい値電圧のバラツキ(VTHとする)とは、VDD>2×VTHと言う関係を満たす必要が在る。

ここでVTHの具体的な値はベリファイ機能を持たせない場合で2.3V(非特許文献1)、ベリファイ機能を持たせた場合で0.5V(非特許文献2)程度の値が報告されている。

従って、仮にベリファイ機能を持たせたとしてもVDDは0.5V×2 =1.0V程度より低い値に設定することは不可能である。ここでは2ビットの情報を記憶する場合を考えたが、更に大きな量の情報を記憶させる場合には更に多くの種類のしきい値電圧が必要となるので電源電圧の下限は更に高い値となる。それ故、このことは低消費電力化の要求に伴う低電源電圧化の大きな障害となっている。

Masayuki Ichige他 "A novel self-aligned shallow trench isolation cell for 90 nm 4Gbit NAND Flash EEPROMs", in Technical Digest of 2003 VLSI Technology pp.89-90 Osama Khouri他 "Program and Verify Word-Line Voltage Regulator for Multilevel Flash Memories", in Analog Integrated Circuits and Signal Processing, vol. 34 (2003) pp.119-131

Masayuki Ichige他 "A novel self-aligned shallow trench isolation cell for 90 nm 4Gbit NAND Flash EEPROMs", in Technical Digest of 2003 VLSI Technology pp.89-90 Osama Khouri他 "Program and Verify Word-Line Voltage Regulator for Multilevel Flash Memories", in Analog Integrated Circuits and Signal Processing, vol. 34 (2003) pp.119-131

本発明は、上記問題点を解決するためになされたもので、その目的はしきい値電圧のバラツキに起因する電源電圧の下限に対する制約を取り除き、低い電源電圧下でも動作が可能で且つ1ビットを超える多値の情報が記憶可能な、低消費電力の高性能な不揮発性半導体記憶装置およびこの不揮発性半導体記憶装置を含む半導体装置を提供することにある。

上記課題を解決するために、本発明では、半導体基板中に形成されたソース・ドレイン領域と、前記ソース・ドレイン領域間の前記半導体基板上に第一の絶縁膜を介して形成された第一のゲート電極と、前記第一のゲート電極上に第二の絶縁膜を介して形成された第二のゲート電極と、を備える素子が少なくとも二つ形成され、且つ前記二つの素子の書き込み電圧条件ないし消去電圧条件の少なくとも一方が前記素子毎に異なる値であり、且つ前記素子のソース領域同士、ドレイン領域同士がそれぞれ電気的に結合され、且つ前記素子の第二のゲート電極同士も電気的に結合されていることを特徴とする不揮発性半導体記憶装置を提供する。

本発明によれば、しきい値電圧のバラツキに起因する電源電圧の下限に対する制約を取り除き、低い電源電圧下でも動作可能で、且つ1ビットを超える多値の情報が記憶可能な、低消費電力で高性能な不揮発性半導体記憶装置およびこの不揮発性半導体記憶装置を含む半導体装置が得られる。

前記目的を達成するために本発明は、トンネルゲート絶縁膜と電荷蓄積層(浮遊ゲート電極などないし酸化膜/窒化膜の積層膜など)と中間絶縁膜(インターポリ絶縁膜等)と制御ゲート電極とからなる積層のゲート構造を持つ素子における、電荷蓄積層への電荷の注入の起こる制御ゲート電極ないしソース・ドレイン領域の電圧条件(本明細書中では「書き込み電圧条件」と言う)、ないし浮遊ゲート電極からの電荷の放出の起こる制御ゲート電極ないしソース・ドレイン領域の電圧条件(本明細書中では「消去電圧条件」と言う)を異なる値に調整した素子を少なくとも二つ形成し、それらの素子のソース領域同士、ドレイン領域同士、制御ゲート電極同士を各々電気的に結合した素子を提供する。

ここで電荷蓄積層への電荷の注入ないし電荷蓄積層からの電荷の放出はトンネルゲート絶縁膜を貫くトンネル電流等を用いて行うので、制御ゲート電極ないしソース・ドレイン領域の電圧条件をある特定の条件とした場合には電流が流れ、別のある特定の条件とした場合には電流は流れないと言う様に不連続に変わるものではないが、その電流の値が予め定めておいた特定の値となる電圧条件を「書き込み電圧条件」ないし「消去電圧条件」と定義すると、これらの「書き込み電圧条件」ないし「消去電圧条件」は明確に定義される。

本発明の実施例による不揮発性半導体記憶装置においては、複数の素子が並列に接続されているので各々の素子のしきい値電圧は二通りの値しか取れないとしても、それらの素子を流れる電流の総和は、各々の素子のしきい値電圧の組み合わせによって様々な値を取ることが可能となり、それに伴って共通であるところのソース領域とドレイン領域との間を流れる電流は様々な値を取る。

本発明の実施例による不揮発性半導体記憶装置においては、各々の素子のしきい値電圧の値は二通りで十分であるので、それらの値を例えば電源電圧よりも十分に高い値とゼロよりも十分に低い値とに設定しておけば、しきい値電圧のバラツキと全く独立に電源電圧の値を設定することが可能となる。

それ故、従来の不揮発性半導体記憶装置においては存在していた電源電圧の下限に対する制約は無くなり、1ビットを超える多値の情報が記憶可能であり且つ電源電圧を十分に低く設定することが可能となる。

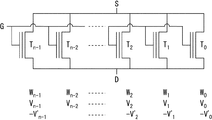

図1の等価回路図は、本発明の実施例である半導体記憶素子を示している。

この素子はトンネルゲート絶縁膜と浮遊ゲート電極とインターポリ絶縁膜と制御ゲート電極とからなる積層のゲート構造を持つnヶの素子(図の右の方に在る素子から順にT0、T1、‥Tn-1と呼ぶことにする)が並列に接続され、これらの素子のソース領域同士、ドレイン領域同士、制御ゲート電極同士が電気的に結合されており、全体として一つの素子を形成している。

この素子において各Tj(0≦j≦n−1)の浮遊ゲート電極に電荷が蓄えられているか否かによって、それらのしきい値電圧は高い値(VTH,H)か低い値(VTH,L)かのいずれかの値を取る。その状態で、共通であるところの制御ゲート電極の端子(図中のGの端子)にVTH,HとVTH,Lとの間の電圧を印加すると、しきい値電圧がVTH,Lである素子はオン状態となるが、しきい値電圧がVTH,Hである素子はオフ状態となるので、共通であるところのソース端子(図中のSの端子)と共通であるところのドレイン端子(図中のDの端子)との間を流れる電流は、しきい値電圧がVTH,Lである素子の幅の総和に比例する。

ここで各Tj(0≦j≦n−1)はNMOSであるとし、その各々に対してソース・ドレインを接地した場合に書き込み電圧条件を満たす制御ゲート電圧をVj(0≦j≦n−1)とし、Vj-1<Vj(1≦j≦n−1)が成り立つとする。浮遊ゲート電極には電子が蓄えられるものとすると、浮遊ゲート電極に電荷が蓄えられている場合にしきい値電圧は高い値(VTH,H)となり、電荷が蓄えられていない場合にしきい値電圧は低い値(VTH,L)となる。先ずSとDとを接地した状態でGに十分に低い電圧を印加すると各Tj(0≦j≦n−1)の浮遊ゲート電極中の電子は放電されるので、浮遊ゲート電極は電荷が蓄えられていない状態となる。この状態では全てのTj(0≦j≦n−1)のしきい値電圧はVTH,Lである。この状態で図中のSを接地してDにプラスの電圧を印加した状態でGにVTH,HとVTH,Lとの間の電圧を印加すると、全てのTj(0≦j≦n−1)はオン状態となるので図中のSとDとの間を流れる電流はWj(0≦j≦n−1)の総和に比例する。ここにWj(0≦j≦n−1)は各々Tj(0≦j≦n−1)の幅である。次にSとDとを接地した状態でGにVk-1とVk(1≦k≦n−1)との間の電圧を印加すると、Tj(0≦j≦k−1)の浮遊ゲート電極には電荷が注入されるのでそれらの素子のしきい値電圧はVTH,Hに変化するが、Tj(k≦j≦n−1)の浮遊ゲート電極には電荷が注入されないのでそれらの素子のしきい値電圧はVTH,Lのままである。それ故、Sを接地してDにプラスの電圧を印加した状態でGにVTH,HとVTH,Lとの間の電圧を印加すると、Tj(k≦j≦n−1)のみがオン状態となるのでSとDとの間を流れる電流はWj(k≦j≦n−1)の総和に比例する。またSとDとを接地した状態でGにVn-1よりも高い電圧を印加すると、全てのTj(0≦j≦n−1)の浮遊ゲート電極に電荷が注入されるので全ての素子のしきい値電圧はVTH,Hに変化する。それ故、Sを接地してDにプラスの電圧を印加した状態でGにVTH,HとVTH,Lとの間の電圧を印加するといずれのTj(0≦j≦n−1)もオフ状態となるのでSとDとの間を流れる電流はゼロである。この様にしてSを接地してDにプラスの電圧を印加した状態でGにVTH,HとVTH,Lとの間の電圧を印加した状態でSとDとの間を流れる電流を測定すれば各Tj(0≦j≦n−1)の浮遊ゲート電極に蓄えられている電荷の状態に応じて電流の値が異なるので、それらの電荷の状態を識別することが可能である。ここでn≧2とすると上の方法で、「いずれのTj(j=0,1) の浮遊ゲートにも電荷が蓄えられていない」、「T0の浮遊ゲートにのみ電荷が蓄えられている」、「いずれのTj(j=0,1)の浮遊ゲートにも電荷が蓄えられている」、の少なくとも3通りの異なる状態が存在する。それ故、この様にして1ビットを超える多値を記憶することの可能な不揮発性半導体記憶装置が実現される。ここに用いた例においては各Tj(0≦j≦n−1)に対してソース・ドレインを接地した場合に書き込み電圧条件を満たす制御ゲート電圧をVj(0≦j≦n−1)とし、それらに対してVj-1<Vj(1≦j≦n−1)が成り立つとしたが、Vj(0≦j≦n−1)の大小関係がこの様な順であることは本質的ではなく、本質的なのはVj(0≦j≦n−1)の値が相互に異なることである。

なお、ここでは各Tj(0≦j≦n−1)に対してソース・ドレインを接地した場合に書き込み電圧条件を満たす制御ゲート電圧が全て異なるとしたが、各Tj(0≦j≦n−1)に対してソース・ドレインを接地した場合に消去電圧条件を満たす制御ゲート電圧が全て異なるとしてもよい。例えば、それらを各Tj(0≦j≦n−1)に対して各々―V'j(0≦j≦n−1)とし、―V'j-1>―V'j(1≦j≦n−1)が成り立つとする。

先ずSとDとを接地した状態でGに十分に高い電圧を印加すると各Tj(0≦j≦n−1)の浮遊ゲート電極にはいずれも電子が注入されるので、浮遊ゲート電極は電荷が蓄えらた状態となる。この状態では全てのTj(0≦j≦n-1)のしきい値電圧はVTH,Hである。この状態でSを接地してDにプラスの電圧を印加した状態でGにVTH,HとVTH,Lとの間の電圧を印加すると、全てのTj(0≦j≦n−1)はオフ状態となるのでSとDとの間を流れる電流はゼロとなる。次にSとDとを接地した状態でGに―V'k-1と―V'k(1≦k≦n−1)との間の電圧を印加すると、Tj(0≦j≦k−1)の浮遊ゲート電極の電荷は放出されるのでそれらの素子のしきい値電圧はVTH,Lに変化するが、Tj(k≦j≦n−1)の浮遊ゲート電極の電荷は放出されないのでそれらの素子のしきい値電圧はVTH,Hのままである。それ故、Sを接地してDにプラスの電圧を印加した状態でGにVTH,HとVTH,Lとの間の電圧を印加すると、Tj(0≦j≦k−1)のみがオン状態となるのでSとDとの間を流れる電流はWj(0≦j≦k−1)の総和に比例する。またSとDとを接地した状態でGに―V'n-1よりも低い電圧を印加すると、全てのTj(0≦j≦n−1)の浮遊ゲート電極の電荷が放出されるので全ての素子のしきい値電圧はVTH,Lに変化する。それ故、Sを接地してDにプラスの電圧を印加した状態でGにVTH,HとVTH,Lとの間の電圧を印加するといずれのTj(0≦j≦n−1)もオン状態となるのでSとDとの間を流れる電流はWj(0≦j≦n−1)の総和に比例する。この様にしてSを接地してDにプラスの電圧を印加した状態でGにVTH,HとVTH,Lとの間の電圧を印加した状態でSとDとの間を流れる電流を測定すれば各Tj(0≦j≦n−1)の浮遊ゲート電極に蓄えられている電荷の状態に応じて電流の値が異なるので、この場合にもそれらの電荷の状態を識別することが可能である。ここに用いた例においては各Tj(0≦j≦n−1)に対してソース・ドレインを接地した場合に消去電圧条件を満たす制御ゲート電圧を―V'j(0≦j≦n−1)とし、―V'j-1>―V'j(1≦j≦n−1)が成り立つとしたが、―V'j(0≦j≦n−1)の大小関係がこの様な順であることは本質的ではなく、本質的なのは―V'j (0≦j≦n−1)の値が相互に異なることである。

別の例として、各Tj(0≦j≦n−1)に対してソース・ドレインを接地した場合に書き込み電圧条件を満たす制御ゲート電圧をVj(0≦j≦n−1)とし、Vj-1<Vj(1≦j≦n−1)が成り立つとする。そして各Tj(0≦j≦n−1)に対してソース・ドレインを接地した場合に消去電圧条件を満たす制御ゲート電圧を―V'j (0≦j≦n−1)とし、―V'j-1>―V'j (1≦j≦n−1)が成り立つとする。

この様にしておくと以下に説明する様にSとDとGとの3つの端子に印加する電圧を調節することで各Tj(0≦j≦n−1)のしきい値電圧を独立にVTH,HとVTH,Lとに調節することが可能となる。ここでaj(0≦j≦n−1)を0または1のみの値を取る量として、aj(0≦j≦n−1)をTjのしきい値電圧がVTH,Hであればaj=0、Tjのしきい値電圧がVTH,Lであればaj=1と定義する。この状態でSを接地してDにプラスの電圧を印加した状態でGにVTH,HとVTH,Lとの間の電圧を印加すると、しきい値電圧がVTH,LであるTj(0≦j≦n−1)はオン状態になるが、しきい値電圧がVTH,HであるTj(0≦j≦n−1)はオフ状態になるのでSとDとの間を流れる電流はaj×Wj(0≦j≦n−1)の総和に比例する。殊に各aj(0≦j≦n−1) に対する0または1の全ての可能な割り振り方(全部で2n通り存在する)に対してaj×Wj(0≦j≦n−1)の総和が尽く異なる値となる様にWj(1≦j≦n−1)の値を調節した場合を考えると、この総和の値は各Tj(0≦j≦n−1)に対するVTH,HとVTH,Lとの全ての可能な割り振り方(全部で2n通り存在する)に対して尽く異なる値となる。それ故、この不揮発性半導体記憶装置においては2n通りの異なる状態が記憶可能となる。

すなわちnビットの情報が記憶可能となる。各aj(0≦j≦n−1)に対する0または1の全ての可能な割り振り方(全部で2n通り存在する)に対してaj×Wj(0≦j≦n−1)の総和が尽く異なる値となる様なWj(0≦j≦n−1)の値の取り方としては例えばWj(2j(0≦j≦n−1)と取ることが可能である。

この場合にはSを接地してDにプラスの電圧を印加した状態でGにVTH,HとVTH,Lとの間の電圧を印加することによってSとDとの間を流れる電流はan-1an-2・・・a1a0に依り2進法表示された値に比例する。

各aj(0≦j≦n−1)に対する0または1の全ての可能な割り振り方(全部で2n通り存在する)に対してaj×Wj(0≦j≦n−1)の総和が尽く異なる値となる様なWj(0≦j≦n−1)の値の取り方がWj(2j(0≦j≦n−1)に限るものでは無いことは無論である。

しかしこの様にとるとSとDとの間を流れる電流はan-1an-2・・・a1a0に依り2進法表示された値に比例するのでその出力信号は等間隔となり、信号の処理が容易になると言う利点がある。なお、Wj(2j(0≦j≦n−1)と取る場合にもWj(0≦j≦n−1)の順序は任意でよい。

続いて、各Tj(0≦j≦n−1)のしきい値電圧を独立にVTH,HとVTH,Lとに調節する方法に関して説明する。先ずSとDとを接地した状態でGに十分に低い電圧を印加すると各Tj(0≦j≦n−1)の浮遊ゲート電極中の電子は放電されるので、浮遊ゲート電極は電荷が蓄えられていない状態となる。この状態では全てのTj(0≦j≦n−1)のしきい値電圧はVTH,Lである。ここでaj(0≦j≦n−1)をTjの設定したいしきい値電圧がVTH,Hであればaj=0、Tjの設定したいしきい値電圧がVTH,Lであればaj=1と定義する。先ずaj(0≦j≦n−1)をjの大きい者から順に見て行き、初めてaj=0となるjをkとする。SとDとを接地した状態でGにVkとVk+1との間の電圧を印加する。但しj=n−1の場合にはSとDとを接地した状態でGにVn-1よりも高い電圧を印加する。その様なjが存在しない場合にはGには電圧を印加しない。すると、Tj(0≦j≦k)の浮遊ゲート電極には電荷が注入されるのでそれらの素子のしきい値電圧はVTH,Hに変化するが、Tj(k+1≦j≦n−1)の浮遊ゲート電極には電荷が注入されないのでそれらの素子のしきい値電圧はVTH,Lのままである。

次にaj(0≦j≦k−1)をjの大きい者から順に見て行き、初めてaj=1となるjをmとする。SとDとを接地した状態でGに―V'mと―V'm+1との間の電圧を印加すると、Tj(0≦j≦m)の浮遊ゲート電極の電荷は放出されるのでそれらの素子のしきい値電圧はVTH,Lに変化するが、Tj(m+1≦j≦k)の浮遊ゲート電極の電荷は放出されないのでそれらの素子のしきい値電圧はVTH,Hのままである。同様にして条件を満たすjが存在しなくなるまで、この手続きを繰り返すと各Tj(0≦j≦n―1)のしきい値電圧は全て設定したい値となる。

この様にして各Tj(0≦j≦n―1)のしきい値電圧を独立にVTH,HとVTH,Lとに調節することが可能となる。なおここでは、各Tj(0≦j≦n―1)の浮遊ゲート電極にはいずれも電荷が蓄えられていない、すなわちしきい値電圧は全てVTH,Lである、場合を初期に実現するものとして説明したが、各Tj(0≦j≦n―1)の浮遊ゲート電極にはいずれも電荷がたくわえられている、すなわちしきい値電圧は全てVTH,Hである、場合を初期に実現する場合も同様にして各Tj(0≦j≦n―1)のしきい値電圧を独立にVTH,HとVTH,Lとに調節することが可能である。

n=3且つT2のしきい値電圧=VTH,H、T1のしきい値電圧=VTH,L、T0のしきい値電圧=VTH,Hに設定する場合を例に取って説明する。

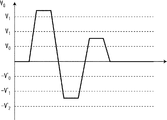

先ずSとDとを接地した状態でGに十分に低い電圧を印加すると各Tj(0≦j≦2)の浮遊ゲート電極中の電子は放電されるので、浮遊ゲート電極は電荷が蓄えられていない状態となる。この状態では全てのTj(0≦j≦2)のしきい値電圧はVTH,Lである。図1中のGの端子に印加する電圧VGのこの状態以降の時間変化を模式的に図2に示す。上に記したaj(0≦j≦2)の定義に従うとa2=0、a1=1、a0=0である。

先ずaj(0≦j≦2)をjの大きい者から順に見て行くと、初めてaj=0となるjは2であるのでSとDとを接地した状態でGにV2よりも高い電圧を印加する。すると、V2>V1>V0と設定してあるので全てのTj(0≦j≦2)の浮遊ゲート電極には電荷が注入され、しきい値電圧はVTH,Hに変化する。次にaj(0≦j≦1)をjの大きい者から順に見て行くと、初めてaj=1となるjは1であるのでSとDとを接地した状態でGに―V'1と―V'2との間の電圧を印加する。すると、―V'2<―V'1<―V'0と設定してあるのでTj(0≦j≦1)の浮遊ゲート電極の電荷は放出されるのでそれらの素子のしきい値電圧はVTH,Lに変化するが、T2の浮遊ゲート電極の電荷は放出されないのでしきい値電圧はVTH,Hのままである。残ったa0を見ると0であるのでSとDとを接地した状態でGにV0とV1との間の電圧を印加する。すると、V2>V1>V0と設定してあるのでT0の浮遊ゲート電極には電荷が注入されるのでしきい値電圧はVTH,Hに変化するが、Tj(1≦j≦2)の浮遊ゲート電極には電荷が注入されないのでしきい値電圧は変化しない。この様にしてT2のしきい値電圧=VTH,H、T1のしきい値電圧=VTH,L、T0のしきい値電圧=VTH,Hに設定される。

この様にして、上に説明した何れの場合にもSとDとGとの3つの端子に印加する電圧を調節するのみで1ビットを越える情報を記憶し、また読み出すことが可能となる。従来の不揮発性半導体記憶装置においても複数のセルを用いれば、いくらでも大きな量の情報を記憶することは可能であるが、その場合には多数の端子に対する電圧の制御が必要となる。それに対して本発明の不揮発性半導体記憶装置においては3つの端子に印加する電圧を調節するのみで1ビットを越える多値の情報を記憶することが可能になると言う利点が在る。

初めの2つの例で説明したように「各Tj(0≦j≦n−1)に対してソース・ドレインを接地した場合に書き込み電圧条件を満たす制御ゲート電圧をVj(0≦j≦n−1)とし、Vj(0≦j≦n−1)が相互に異なること」または「各Tj(0≦j≦n−1)に対してソース・ドレインを接地した場合に消去電圧条件を満たす制御ゲート電圧を―V'j (0≦j≦n−1)とし、―V'j (0≦j≦n−1)が相互に異なること」のみを要求して、それらのいずれかの間である様な電圧を制御ゲートに印加することで一部の素子の浮遊ゲート電極に対してのみ電荷の注入ないし放出を行うことで1ビットを超える多値を記憶する場合には、浮遊ゲート電極に対する電荷の充電ないし放電が制御ゲート電極に対する一度の電圧印加の操作のみで済み、操作が簡略化されるという利点がある。

一方、3つ目の例で説明した様に、「各Tj(0≦j≦n−1)に対してソース・ドレインを接地した場合に書き込み電圧条件を満たす制御ゲート電圧を各Vj(0≦j≦n−1)とし、各Vj(0≦j≦n−1)が相互に異なること」と「各Tj(0≦j≦n−1)」に対してソース・ドレインを接地した場合に消去電圧条件を満たす制御ゲート電圧を―V'j (0≦j≦n−1)とし、―V'j (0≦j≦n−1)が相互に異なること」とのいずれも満たされている場合には、浮遊ゲート電極の各々に対して電荷が存在するか否かを独立に調節することが可能となり、その結果として本発明の不揮発性半導体記憶装置はより多くの情報を記憶することが可能となると言う利点がある。更に加えて「aj(0≦j≦n−1)を0または1のみの値を取る量として各aj(0≦j≦n−1)に対する0または1の全ての可能な割り振り方(全部で2n通り存在する)に対してaj×Wj(0≦j≦n−1)の総和が尽く異なる値となること」と言う条件もまた満たされている場合には、浮遊ゲート電極の各々に対して電荷が存在するか否かの全てを識別することが可能となり、その結果として素子がnヶである場合にnビットの情報が記憶可能となる、すなわち一つの不揮発性半導体記憶装置に記憶可能な情報量が更に大きくなると言う利点がある。

以上の例ではソース・ドレイン領域を接地した状態で制御ゲート電極に印加する電圧を調節することで浮遊ゲート電極への電化の注入や放出を行ったが、このことは本質ではなく、例えばゲート電極を接地してソースないしドレイン領域に電圧を印加することで行ってもよいし、例えばチャネルに電流を流して高いエネルギーのキャリアを発生させることで行ってもよい。本質的なのは上に記した各Tj(0≦j≦n−1)に対する書き込み電圧条件ないし消去電圧条件が異なることである。

また、上に示した例では素子の書き込み電圧条件ないし消去電圧条件ないし素子の幅が素子の並んでいる順に従って単調に変化するとしたが、このことは本質ではなく異なる順序であっても良い。但し、各素子の浮遊ゲート電極に電荷の蓄積されている状態と蓄積されていない状態とを独立に制御することが可能である為には、書き込み電圧条件の高低の順と消去電圧条件の高低の順とは逆になっている必要がある。

なお、書き込み電圧条件ないし消去電圧条件を素子により異ならせることは例えばトンネルゲート絶縁膜厚を素子毎に変えることに依り可能である。殊に制御ゲート電極とソース・ドレイン領域との間に電位差を設けることに依り、制御ゲート電極と浮遊ゲート電極との間の容量結合を利用して浮遊ゲート電極とソース・ドレイン領域との間に電位差を設けてファウラー・ノルドハイム‐トンネリングによって電子がトンネルゲート絶縁膜を貫くことを利用して、浮遊ゲート電極への電荷の注入及び放出を行う場合には、トンネルゲート絶縁膜厚を素子毎に変えることで書き込み電圧条件や消去電圧条件を容易に変えることができる。そして、例えばメサ分離SOI素子、トライゲート素子、パイゲート素子、オメガゲート素子、ゲート‐オール‐アラウンド素子、縦型構造素子等の様にチャネルの形成される半導体領域とゲート絶縁膜との界面が少なくとも二つの面よりなる場合には面の境界を成す稜の近傍において絶縁膜中の電場は極めて強くなり且つ絶縁膜の厚さと共に急激に変化するので、チャネルの形成される領域が少なくとも二つの面よりなる場合にはトンネルゲート絶縁膜厚を素子毎に変えることで書き込み電圧条件や消去電圧条件を更に容易に変えることができると考えられる。

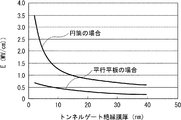

このことを調べる為にチャネルの稜の近傍を図3に模式的に示す様に円筒で近似してトンネルゲート絶縁膜中の電場のトンネルゲート絶縁膜厚に対する依存性を調べた。なお図3には計算に用いた構造の1/4のみを示してある。図3中の10は半導体基板ないしソース・ドレインを想定した導体領域で半径は10nmとした。11はトンネルゲート絶縁膜を想定した絶縁膜であり、厚さを様々に変えて、この領域中での電場の最大値を求めた。絶縁膜11中で電場が最大となるのは10の導体領域との界面においてである。なお11の材質はSiO2を想定して誘電率は3.9とした。12は浮遊ゲート電極を想定した導体領域であり、厚さは100 nmとした。13はインターポリ膜を想定した絶縁膜であり、いずれも厚さが5 nmのSiO2/Si3N4/SiO2の積層構造を想定し、三層の誘電率は各々3.9、7.8、3.9とした。そして14は制御ゲート電極を想定した導体領域である。10と14との間の電位差を1 Vとした場合の、11の厚さに対する11中の電場の最大値の依存性を図4に示す。なお図4には図3に示した構造と等しい厚さと誘電率との平板を積層した平行平板の構造における、トンネルゲート絶縁膜を想定した絶縁膜中の電場をも示してある。図4を見ると円筒構造の場合には平行平板構造の場合と比べてトンネルゲート絶縁膜厚に対する絶縁膜中の電場強度の依存性が極めて大きいことが判る。

すなわちチャネルが稜を持つ構造の稜の近傍におけるトンネルゲート絶縁膜中の電場強度は、トンネルゲート絶縁膜厚を変えることで大きく変化する。なお、ここに結果を示した計算においては10と14との間の電位差を1Vとしたが、この電位差と電場強度とは比例するので、10と14との間の電位差を異なる値に設定したとしてもチャネルが稜を持つ構造においては、トンネルゲート絶縁膜厚を変えることで稜の近傍におけるトンネルゲート絶縁膜中の電場強度は大きく変化する。従って、チャネルが稜を持つ構造においてはトンネルゲート絶縁膜厚を変えることで素子の書き込み電圧条件や消去電圧条件を容易に変えることが可能であることが判る。このことは今回の検討で新たに得られた知見である。

また、上に示した例では素子の幅を異なった値に設定することで電流値を素子毎に異なる値としたが、このことは本質的ではなく、チャネル領域への不純物の注入条件や各ゲート絶縁膜の厚さ等、他の条件を素子毎に異ならせることによって電流値を素子毎に異なる値としてもよい。更に複数の条件を素子毎に異ならせることによってもよい。但し、素子の幅を素子毎に異ならせることによって電流の値を異ならせるのであれば、リソグラフィー工程に用いるマスクをその様にデザインしておけば良いので工程が簡略になると言う利点がある。またトンネルゲート絶縁膜厚を素子毎に異ならせることによって電流の値を異ならせるのであれば、上に記した様に書き込み電圧条件や消去電圧条件をも同時に異ならせることが可能となると言う別の利点が得られる。

本発明の実施例による不揮発性半導体記憶装置においては、従来の不揮発性半導体記憶装置と異なり、しきい値電圧はVTH,HとVTH,Lとの2種類の値のみで十分である。それ故、VTH,Hは電源電圧よりも十分に高い値に設定し、VTH,Lは電源電圧よりも十分に低い値に設定すれば、しきい値電圧のバラツキとは独立に電源電圧を設定することが可能となる。従って従来の不揮発性半導体記憶装置と異なり、電源電圧に対する下限は存在せず、十分に電源電圧を低く設定することが可能となる。それ故、消費電力が低く且つ1ビットを超える多値の記憶可能な高性能の不揮発性半導体記憶装置が実現される。

以下図面を用いて本発明の実施形態を詳細に説明する。なお本発明は以下の実施形態に限定されるものではなく、種々変更して用いることができる。

(実施例1)

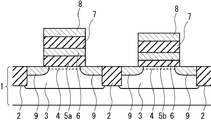

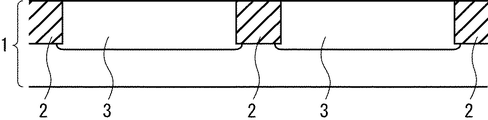

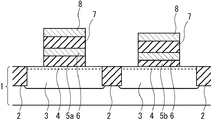

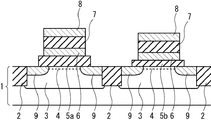

図5は本発明の実施例1による不揮発性半導体記憶装置の断面を示す模式図である。

図5は本発明の実施例1による不揮発性半導体記憶装置の断面を示す模式図である。

本実施例ではNチャネルの場合を例に取って示す。不純物の導電型を逆にすればPチャネルの場合にもまったく同様であり、また光蝕刻法等の方法を用いて半導体基板内の特定の領域にのみ不純物を注入する等の方法を用いれば相補型の場合も全く同様の効果が得られる。

この不揮発性半導体記憶装置は半導体基板1上に形成されており、異なる素子の間は素子分離領域2に依り隔てられている。半導体基板領域1の内部にはBイオン注入に依りウエル領域3が形成される。そしてウエル領域3の内にチャネル形成領域4が在り、その上にSiO2によるトンネルゲート絶縁膜5が形成され、その上に多結晶シリコンによる浮遊ゲート電極6が形成される。浮遊ゲート電極6の上にはSiO2とSi3N4とSiO2との積層より成るインターポリ絶縁膜7が形成され、その上に多結晶シリコンによる制御ゲート電極8が形成される。

ここで、トンネルゲート絶縁膜5a、5bの厚さは素子により異なった厚さとしてある。そしてウエル領域3中には浮遊ゲート電極6ないし制御ゲート電極8を挟む様にAsイオン注入によってソース・ドレイン領域9が形成されている。なお、この図においては配線金属、制御ゲート電極8ないしソース・ドレイン領域9に対して配線金属を結合させるためのコンタクト領域、層間絶縁膜、等は省略してあるが、各々の素子に対して浮遊ゲート電極6ないし制御ゲート電極8を挟むソース・ドレイン領域9の内の一方をソース、他方をドレインとするとソース同士、ドレイン同士、制御ゲート電極8同士は各々電気的に結合される。

ここに示す不揮発性半導体記憶装置は素子によりトンネルゲート絶縁膜の厚さが異なるので、書き込み電圧条件ないし消去電圧条件が素子により異なる。そして素子の紙面に垂直方向の長さ、すなわち幅、が素子により異なる。その結果として上に説明した様に低電源電圧下でも動作が可能であり且つ1ビットを超える多値を記憶することの可能な低消費電力動作の高性能の不揮発性半導体記憶装置が実現される。

なお、ここでは説明の都合上、チャネルを流れる電流の主方向に平行に二つの素子が並んでいるように描いてあるが、このことは本質的ではなく素子相互の相対的な位置関係はどのようであっても良い。但し、ソース同士、ドレイン同士、制御ゲート同士を電気的に結合する配線の配置を考えると、図6に模式的に示された平面図に記載されたようにチャネルを流れる電流の主方向に垂直に素子が並んでいる場合は、制御ゲート電極を一体の構造で形成可能となる等、配線が簡単になるという利点がある。また、ここでは素子が二つの場合を示しているが、このことは本質ではなく素子が三つ以上である場合も同様である。

次に本発明の実施例による不揮発性半導体記憶装置の製造方法について以下、説明する。

先ず図7に示すように、半導体基板1に対し例えばB(硼素)イオンを100KeV、

2.0×1012cm-2で注入し、その後、例えば1050℃、30秒の熱工程を施すことによりウエル領域3を形成する。続いて例えばRIE法(反応性イオンエッチング法)等の異方性エッチングを施すことにより、チャネルの形成される半導体領域以外の領域に溝を形成し、前記溝を例えばSiO2等の絶縁材料で埋め込むことにより素子分離領域2を形成する。

先ず図7に示すように、半導体基板1に対し例えばB(硼素)イオンを100KeV、

2.0×1012cm-2で注入し、その後、例えば1050℃、30秒の熱工程を施すことによりウエル領域3を形成する。続いて例えばRIE法(反応性イオンエッチング法)等の異方性エッチングを施すことにより、チャネルの形成される半導体領域以外の領域に溝を形成し、前記溝を例えばSiO2等の絶縁材料で埋め込むことにより素子分離領域2を形成する。

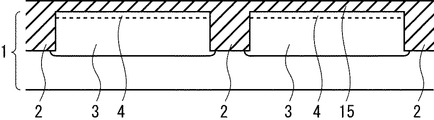

次に図8に示す様に、例えばBイオンを注入することにより、所望のしきい値電圧が得られるようにチャネル形成領域4の表面近傍における不純物の濃度を調節する。続いて例えば800℃の酸化雰囲気に半導体基板を曝すことにより半導体基板表面に例えば厚さ7 nmのSiO2膜15を形成する。

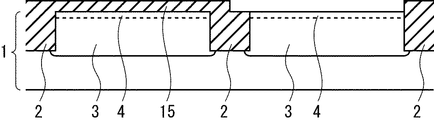

次に図9に示す様に、例えば弗化水素酸等の薬液処理等の方法を用いることにより、薄いトンネルゲート絶縁膜を形成したい素子領域上のSiO2膜15を除去する。

次に図10に示す様に、例えば800℃の酸化雰囲気に半導体基板を曝すことにより、半導体基板表面に例えば厚さ10nmのSiO2膜を形成し、場所により厚さの異なるSiO2膜15aを形成する。図10においては、左側の素子領域のSiO2膜の膜厚の方が右側の素子領域のSiO2膜の膜厚よりも厚く形成されている。

次に図11に示す様に、例えばCVD法(化学的気相成長法)等の方法を用いることにより、例えば厚さ100nmの例えばP(リン)を含有する多結晶シリコン膜16を形成する。

次に図12に示す様に、例えばCVD法等の方法により、全面に例えば厚さ5nmの酸化シリコン膜を堆積し、続いて全面に例えば厚さ5nmの窒化シリコン膜を堆積し、更に続いて全面に例えば厚さ5nmの酸化シリコン膜を堆積することによりSiO2/Si3N4/SiO2積層絶縁膜17を形成する。

次に図13に示すように、例えばCVD法等の方法により、例えば厚さ200nmの例えばP(リン)を含有する多結晶シリコン膜を形成する。続いて例えばRIE法等の方法を用いることに依り、前記厚さ200nmの多結晶シリコン膜、SiO2/Si3N4/SiO2積層絶縁膜17、厚さ100nmの多結晶シリコン膜16、SiO2膜15aを加工して、制御ゲート電極8及びインターポリ膜7及び浮遊ゲート電極6及びトンネルゲート絶縁膜5a、5bを形成する。

次に、例えばAs(砒素)イオンを30KeV、5.0×1015cm-2で注入する。そして熱工程によりソース・ドレイン領域9を形成して、図5に示す不揮発性半導体記憶装置が形成される。以後は通常の層間絶縁膜形成工程、配線孔開孔工程、配線工程等を経て半導体装置が形成される。

本実施例においてはN型の場合を例に取って示したが、不純物の導電型を逆にすればP型の場合にも、そして光蝕刻法等の方法を用いて基板内の特定の領域にのみ不純物を導入すれば相補型の場合に対しても同様である。また、それらを一部として含む半導体装置にも用いることができる。

また、不揮発性半導体記憶装置の他に、電界効果トランジスターやバイポーラー型トランジスターや単一電子トランジスター等の他の能動素子、ないしは抵抗体やダイオードやインダクターやキャパシター等の受動素子、ないしは例えば強誘電体を用いた素子や磁性体を用いた素子をも含む半導体装置の一部として不揮発性半導体記憶装置を形成する場合にも用いることができる。OEIC(オプト‐エレクトリカル‐インテグレーテッド‐サーキット)やMEMS(マイクロ‐エレクトロ‐メカニカル‐システム)の一部として不揮発性半導体記憶装置を形成する場合もまた同様である。また、それらの素子が複数の面に渡って形成されていてもよい。

また、不揮発性半導体記憶装置の他に、電界効果トランジスターやバイポーラー型トランジスターや単一電子トランジスター等の他の能動素子、ないしは抵抗体やダイオードやインダクターやキャパシター等の受動素子、ないしは例えば強誘電体を用いた素子や磁性体を用いた素子をも含む半導体装置の一部として不揮発性半導体記憶装置を形成する場合にも用いることができる。OEIC(オプト‐エレクトリカル‐インテグレーテッド‐サーキット)やMEMS(マイクロ‐エレクトロ‐メカニカル‐システム)の一部として不揮発性半導体記憶装置を形成する場合もまた同様である。また、それらの素子が複数の面に渡って形成されていてもよい。

また、本実施例では平面構造の素子を例に取って説明したが、メサ分離SOI素子、ゲート‐オール‐アラウンド型素子、パイゲート素子、オメガゲート素子、縦型構造素子、フィン型構造素子(FINFET)などに対しても同様の効果が得られる。これらの素子の場合にはチャネル領域の不純物濃度を極めて低く設定することが可能になるため、キャリアの高い移動度を実現することが可能になるという利点がある。

また、本実施例では、N型半導体層を形成するための不純物としてはAsないしPを、P型半導体層を形成するための不純物としてはBを用いたが、N型半導体層を形成するための不純物として他のV族不純物を用いる、ないしはP型半導体層を形成するための不純物として他のIII族不純物を用いてもよい。また、III族やV族の不純物の導入はそれらを含む化合物の形で行ってもよい。

また、本実施例では、不純物の導入(「は」を補って下さい。)イオン注入を用いて行ったが、イオン注入以外の例えば固相拡散や気相拡散等の方法を用いて行ってもよい。また、不純物を含有する半導体を堆積するないしは成長させる等の方法を用いてもよい。

また、本実施例では素子分離領域の形成はトレンチ素子分離法を用いて行ったが、例えば局所酸化法ないしはメサ分離法等の他の方法を用いて行ってもよい。

また、本実施例では、ウエルを形成するための不純物導入とは別の工程でしきい値電圧を調節するための不純物導入を行っているが、これらを同一の工程で導入してもよい。このようにすると工程の短縮が図られるという利点がある。また、本実施例の様にするとしきい値電圧を所望の値に設定しやすくなるという利点が得られる。

また、本実施例では、シングルドレイン構造の素子を示したが、シングルドレイン構造以外の例えばエクステンション構造ないしLDD(ライトリードープト ソース・ドレイン)構造やGDD(グレイデッドディフーズド ソース・ドレイン)構造等の構造の素子を構築したとしてもよい。またハロー構造ないしポケット構造等の素子を用いてもよい。これらの様な構造とすると素子の短チャネル効果に対する耐性が向上するので好ましい。

また、本実施例では、ソース・ドレイン領域の形成をゲート電極ないしゲート絶縁膜の加工の後に行っているが、これらの順序は本質ではなく、逆の順序で行ってもよい。ゲート電極ないしゲート絶縁膜の材質によっては熱工程を施すことが好ましくない場合がある。その様な場合にはソース・ドレイン領域への不純物の導入ないし活性化の熱工程をゲート電極ないしゲート絶縁膜の加工に先立って行うことが好ましい。

また、本実施例では、制御ゲート電極も浮遊ゲート電極も多結晶シリコンを用いて形成しているが、例えばW(タングステン)等の金属を用いて形成してもよい。また単結晶シリコンや非晶質シリコン等の半導体、ないしは必ずしも高融点とは限らない金属、金属を含む化合物等、ないしはそれらの積層等で形成してもよい。金属ないし金属を含む化合物でゲート電極を形成するとゲート電極の抵抗が抑制されるので素子の高速動作が得られ、好ましい。また金属でゲートを形成すると酸化反応が進みにくいので、ゲート絶縁膜ないしインターポリ膜とゲート電極との界面の制御性が良いと言う利点もある。また、ゲート電極の少なくとも一部に多結晶シリコン等の半導体を用いると仕事関数の制御が容易であるので素子のしきい値電圧の調節が容易になるという別の利点がある。

また、本実施例では、ゲート電極の形成はゲート電極材料を堆積した後に異方性エッチングを施すという方法で形成しているが、例えばダマシンプロセス等のような埋め込み等の方法を用いてゲート電極を形成してもよい。ゲート電極の形成に先立ってソース・ドレイン領域を形成する場合には、ダマシンプロセスを用いるとソース・ドレイン領域とゲート電極とが自己整合的に形成されるので好ましい。

また、本実施例では、素子を流れる電流の主方向に測ったゲート電極の長さは、ゲート電極の上部も下部も等しいが、このことは本質的ではない。例えばゲート電極の上部を測った長さの方が下部を測った長さよりも長いアルファベットの「T」字の様な形であってもよい。この場合にはゲート抵抗を低減することができるという他の利点も得られる。

また、本実施例では明記していないが、配線の為の金属層の形成は例えばスパッタ法等を用いて行ってもよいし、堆積法等の方法を用いて行ってもよい。また、金属の選択成長等の方法を用いてもよいし、ダマシン法等の方法を用いてもよい。また、配線金属の材料は例えばSiを含有するAl等を用いても、例えばCu等の金属を用いてもよい。殊にCuは抵抗率が低いので好ましい。

また、本実施例では、シリサイド工程には言及しなかったが、ソース・ドレイン領域上にシリサイド層を形成してもよい。また、ソース・ドレイン領域上に金属を含む層を堆積ないしは成長させる等の方法を用いてもよい。この様にするとソース・ドレイン領域の抵抗が低減されるので好ましい。また、ゲート電極を多結晶シリコン等で形成する場合にはゲート電極に対してのシリサイド化を施してもよい。その場合にシリサイド化を施すとゲート抵抗が低減されるので好ましい。また、エレベート構造を用いてもよい。エレベート構造によってもソース・ドレイン領域の抵抗が低減されるので好ましい。

また、本実施例では、制御ゲート電極の上部は電極が露出する構造であるが、上部に例えば酸化シリコンや窒化シリコンや酸化窒化シリコン等の絶縁物を設けてもよい。殊に制御ゲート電極が金属を含む材料で形成されており、且つソース・ドレイン領域上にシリサイド層を形成する場合等、製造工程の途中で制御ゲート電極を保護する必要が在る場合等は制御ゲート電極の上部に酸化シリコンや窒化シリコンや酸化窒化シリコン等の保護材料を設けることは必須である。

また、本実施例では、トンネルゲート絶縁膜として熱酸化法に依り形成したSiO2膜を用いたが、Hf(ハフニウム)、Zr(ジルコニウム)、Ti(チタン)、Sc(スカンジウム)、Y(イットリウム)、Ta(タンタル)、Al、La(ランタン)、Ce(セリウム)、Pr(プラセオジム)、ないしはランタノイド系列の元素等の金属等の酸化物等ないしはこれらの元素をはじめとする様々な元素を含むシリケート材料等、ないしはそれらに窒素をも含有させた絶縁膜等、高誘電体膜ないしはそれらの積層等の他の絶縁膜をトンネルゲート絶縁膜として用いてもよい。絶縁膜中に窒素が存在すると、特定の元素のみが結晶化して析出することが抑制されるので好ましい。

また、絶縁膜中に窒素が存在すると、ゲート電極として不純物を含有する多結晶シリコンを用いる場合に不純物が基板中に拡散することを抑制すると言う別の利点もあるので好ましい。また、絶縁膜の形成方法は熱酸化法に限るものではなく、CVD法等の堆積法、蒸着法ないしスパッタ法ないしエピタキシャル成長法等の他の方法を用いてもよい。また、絶縁膜として或る物質の酸化物を用いる等の場合には、まずその物質の膜を形成しておいてそれを酸化する等の方法を用いてもよい。インターポリ膜に関しても同様である。

また、トンネルゲート絶縁膜ないしインターポリ膜を形成する絶縁膜等の厚さは本実施例の値に限るものではない。

また、トンネルゲート絶縁膜ないしインターポリ膜を形成する絶縁膜等の厚さは本実施例の値に限るものではない。

また、本実施例では素子毎に厚さの異なるトンネルゲート絶縁膜を形成する為に、先ず全面に絶縁膜を形成し、薄い絶縁膜を形成したい素子の領域においてのみ絶縁膜を剥離し、続いて全面に再び絶縁膜を形成するという方法を用いたが、この方法は本質的ではなく、絶縁膜形成に先立って窒素原子ないし窒素分子を注入しておくとその後の熱酸化膜の成膜が遅くなることが知られているので、薄い絶縁膜を形成したい素子の領域のみは絶縁膜形成に先立って窒素原子ないし例えば窒素分子を注入しておいてから絶縁膜の成膜を行う等の方法によっても可能である。

また、本実施例ではゲート側壁には言及していないが、ゲート電極に側壁を設けてもよい。殊に高誘電体材料でゲート絶縁膜を形成する場合に高誘電率材料でゲート側壁を設けると本発明者による公開2003−209247号公報に記載されているようにゲート電極下端角近傍のトンネルゲート絶縁膜中の電場が緩和され、トンネルゲート絶縁膜の信頼性が向上すると言う利点が得られるので好ましい。

また、本実施例では、トンネルゲート絶縁膜は単層の構造としたが、このことに必然性はなく、積層構造としても良い。殊に高誘電体材料でトンネルゲート絶縁膜を形成する場合に、基板との界面の近傍に酸化シリコンないし窒化シリコンないし酸化窒化シリコン等の膜を設けるとキャリアのモビリティーが向上するので電流駆動能力が更に向上すると言う利点がある。なお、絶縁膜中や半導体基板との界面に存在する電荷や準位等が少ないことが望ましいので、このことに鑑みると半導体基板と接する層には酸化シリコンを用いることが好ましい。

一方、ゲート電極に半導体を用いた場合において不純物がチャネル領域に拡散することを防ぐと言う観点から考えると、窒素の存在に依り不純物の拡散が抑制されることが知られているので窒化シリコンないし酸化窒化シリコンを用いることが好ましい。

またこれらの膜の形成方法は例えば昇温状態の酸素気体に曝すないしは堆積等の方法を用いることに依り可能であるし、必ずしも昇温を伴わない励起状態の酸素気体に曝してもよい。昇温を伴わない励起状態の酸素気体に曝すと言う方法で形成すれば、チャネル領域中の不純物が拡散に依り濃度分布を変えることが抑制されるので好ましい。更に酸化窒化シリコンを用いる場合には、先ず酸化シリコン膜を形成し、その後に昇温状態ないし励起状態の窒素を含む気体に曝すことに依り絶縁膜中に窒素を導入してもよい。この場合において昇温を伴わない励起状態の窒素気体に曝すと言う方法で形成すれば、チャネル領域中の不純物が拡散に依り濃度分布を変えることが抑制されるので好ましい。

また、本実施例では、素子はバルク基板上に形成したが、SOI基板上に形成してもよい。バルク基板上に形成すると基板を通じてウエル領域の電位を制御する端子を設けることが可能になる為に例えば寄生バイポーラ効果が有効に抑制されるという利点がある。またSOI基板上に形成するとチャネル領域の不純物濃度を極めて低く設定することが可能になる為、キャリアの高い移動度を実現することが可能になるという利点がある。

また、本実施例では、ゲート電極形成後の後酸化には言及していないが、ゲート電極やゲート絶縁膜材料等に鑑みて可能であれば、後酸化工程を行ってもよい。また、必ずしも後酸化に限らず、例えば薬液処理ないしは反応性の気体に曝す等の方法でゲート電極下端の角を丸める処理を行ってもよい。これらの工程が可能な場合にはそれによりゲート電極下端角部の電場が緩和されるのでゲート絶縁膜の信頼性が向上し、好ましい。

また、本実施例では明記していないが、層間絶縁膜としては酸化シリコン膜を用いてもよいし、例えば低誘電率材料等の酸化シリコン以外の物質を層間絶縁膜に用いてもよい。

層間絶縁膜の誘電率を低くすると素子の寄生容量が低減されるので素子の高速動作が得られるという利点がある。

また、本実施例では明記していないが、コンタクト孔に関しては自己整合コンタクトを形成することも可能である。自己整合コンタクトを用いると素子の面積を低減することができるので、集積度の向上が図られ、好ましい。

また、本実施例においてはゲート電極下以外のソース・ドレイン領域上のトンネルゲート絶縁膜は除去したが、除去せずに残してもよい。例えばソース・ドレイン領域を、ゲート電極形成後にイオン注入により形成する場合等はドーズロスが防止されるので、ソース・ドレイン領域上のゲート絶縁膜は除去する方が好ましい。また、ソース・ドレイン領域に対してシリサイド化を行う場合には、除去することが必須である。また、除去の方法はRIE法に限るものではなく、例えばCDE法(化学的気相エッチング法)ないし湿式処理法等の方法を用いてもよい。

また、本実施例においては図5に示す様にゲート絶縁膜の側面はゲート電極に合わせて加工されているが、例えば模式的な断面を図14に示す様にゲート絶縁膜がゲート電極よりも張り出すように加工してもよい。このようにするとソース・ドレイン領域とゲート電極との間の容量結合が強まるのでソース・ドレイン領域の抵抗が低減され、寄生抵抗が抑制されて更なる高速動作が可能になるという利点が得られる。

また図15に示すようにゲート絶縁膜をゲート電極よりも内側に入り込むように加工してもよい。これによれば、ゲート電極とソース・ドレイン領域との間に形成される静電容量が減るので素子の寄生容量が低減され、更なる高速動作が可能になるという利点が得られる。更に、トンネルゲート絶縁膜に高誘電体材料を用いる場合には、ゲート絶縁膜をゲート電極よりも内側に入り込むように加工すると、先の公開2003−209247号公報に記載されているようにゲート電極下端角近傍のトンネルゲート絶縁膜中における電場が緩和されるため、絶縁膜の信頼性が向上するという別の利点も得られる。更に、ソース側とドレイン側とでゲート絶縁膜のゲート電極からの張り出し長さや、ゲート電極の内側への入り込み長さ等が、ソース側とドレイン側とで非対称であってもよい。また、素子毎に異なっていてもよい。なお、本実施例ないし変形例においては素子が二つの場合の構造のみを示したが、ここに示した実施例ないし変形例は素子が二つの場合に限定されるものではなく、かつ同様の効果が得られることは無論である。

(実施例2)

次に本発明の別の実施例による不揮発性半導体記憶装置について、以下、説明する。

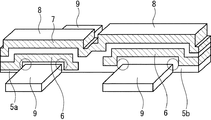

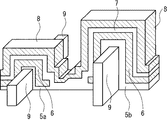

図16の斜視図に模式的に構造を示すように、この実施例の不揮発性半導体記憶装置はSOI基板上に形成され、素子分離はメサ分離法により行われている。

次に本発明の別の実施例による不揮発性半導体記憶装置について、以下、説明する。

図16の斜視図に模式的に構造を示すように、この実施例の不揮発性半導体記憶装置はSOI基板上に形成され、素子分離はメサ分離法により行われている。

なお、この図においては配線金属、制御ゲート電極8ないしソース・ドレイン領域9に対して配線金属を結合させるためのコンタクト領域、層間絶縁膜、等は省略してある。このような構造の素子においてはチャネルの形成される半導体領域とトンネルゲート絶縁膜との界面はメサ分離で得られたSOI基板の半導体層の上面と側面との二つの面に渡り、その境界に稜が存在する。稜を図中に破線の丸で示す。このようにチャネルの形成される領域に稜が在ると、上に記したようにトンネルゲート絶縁膜5の厚さを変えることにより、トンネルゲート絶縁膜中の電場を効果的に変えることができ、その結果、素子毎に書き込み電圧条件や消去電圧条件を容易に異ならせることが可能となるという利点が得られる。

なおこのことは本実施例に示したメサ分離のSOI構造のみならず、トライゲート素子、パイゲート素子、オメガゲート素子、ゲート‐オール‐アラウンド素子、縦型構造素子等のようにチャネルの形成される半導体領域とトンネルゲート絶縁膜との界面が少なくとも二つの面よりなる場合には同様である。

また、図16においては幅の広い方の素子のトンネルゲート絶縁膜が厚い例を示してあるが、このことは本質的ではなく素子の幅とトンネルゲート絶縁膜厚との大小関係が逆であっても同様の効果が得られる。

また、例えば図17に示すように、隣り合う素子の浮遊ゲート電極の間に制御ゲート電極が存在してもよい。なお、この図においては配線金属、制御ゲート電極8ないしソース・ドレイン領域9に対して配線金属を結合させる為のコンタクト領域、層間絶縁膜、等は省略してある。このようにすると異なる素子の浮遊ゲート電極の間に形成される容量結合が制御ゲート電極により弱められるので、各素子の書き込みないし消去電圧条件が他の素子の浮遊ゲート電極に蓄積されている電荷の有無等の状態によって被る影響を低減する事が可能になるという利点がある。

更に図17に示すように、制御ゲート電極が浮遊ゲート電極を覆う様に形成されていると、制御ゲート電極と浮遊ゲート電極との間に形成される容量結合が強まるので、浮遊ゲート電極の電位に対する制御ゲート電極の制御性が高まるという他の利点もまた得られる。

一方、図16に示す様にすると、素子の間隔を狭く設計する事が可能となるので、集積度が増すという他の利点が得られる。

本実施例においても実施例1に記したような種々の変形が可能であり、同様の効果が得られる。

(実施例3)

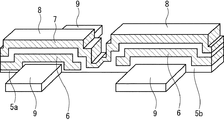

次に本発明のさらに別の実施例による不揮発性半導体記憶装置の例について説明する。

次に本発明のさらに別の実施例による不揮発性半導体記憶装置の例について説明する。

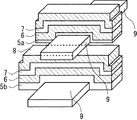

図18の斜視図に模式的に構造を示す様に、この不揮発性半導体記憶装置は、トライゲート素子を用いて形成されている。そして素子に依りソース・ドレイン領域9ないしチャネルの形成される半導体領域の高さが異なっている。そのことにより、素子毎の電流値を異なる値に設定してある。なお、この図においては配線金属、制御ゲート電極8ないしソース・ドレイン領域9に対して配線金属を結合させる為のコンタクト領域、層間絶縁膜、等は省略してある。このようにすると平面構造の素子ないしはメサ分離のSOI構造の素子等を用いた場合と比較して不揮発性半導体記憶装置の面積を縮小する事が可能となり、集積度の向上が図られると言う利点がある。図18においてはトライゲート素子を用いた場合の例を示したが、トライゲート素子に限らず、パイゲート素子、オメガゲート素子、ゲート‐オール‐アラウンド素子、フィン型構造素子(FINFET)等の素子を用いた場合にも同様の利点が得られる。

本実施例においても上記実施例に記した様な種々の変形が可能であり、同様の効果が得られる。

(実施例4)

次に本発明のさらに別の実施例による不揮発性半導体記憶装置の例について説明する。

次に本発明のさらに別の実施例による不揮発性半導体記憶装置の例について説明する。

図19の斜視図に模式的に構造を示すように、この不揮発性半導体記憶装置はメサ分離のSOI素子を用いて形成されている。

そしてそれらの素子は異なる面に形成されている。なお、この図においては配線金属、制御ゲート電極8ないしソース・ドレイン領域9に対して配線金属を結合させる為のコンタクト領域、層間絶縁膜、等は省略してある。この様にすると全ての素子を単一の面内に形成した場合と比較して不揮発性半導体記憶装置の面積を縮小する事が可能となり、集積度の向上が図られると言う利点がある。図19においてはメサ分離SOI型素子を用いた場合の例を示したが、メサ分離SOI型素子に限らず、通常の平面構造素子、トライゲート素子、パイゲート素子、オメガゲート素子、ゲート‐オール‐アラウンド素子、縦型構造素子、フィン型構造素子(FINFET)等の素子を用いた場合にも同様の利点が得られる。なお、図19においては幅ないしトンネルゲート絶縁膜厚の値の小さい素子がより上の面に形成されている場合を示しているが、この事は本質的ではなく、素子の形成される面の上下関係はどの様であっても同様の効果が得られる。

本実施例においても上記実施例に記した様な種々の変形が可能であり、同様の効果が得られる。

以上述べたように、本発明の実施例の不揮発性半導体記憶装置によれば、書き込み電圧条件ないし消去電圧条件の異なる素子が並列に接続された構造であり、各々の素子においては高いしきい値電圧と低いしきい値電圧との2種類のしきい値電圧を設定するのみで1ビットを超える多値の記憶を行う事が可能である。そのため、高い方のしきい値電圧は電源電圧よりも十分に高い値に設定し、低い方のしきい値電圧はゼロよりも十分に低い値に設定すれば、従来の不揮発性半導体記憶装置と異なり、しきい値電圧のバラツキに起因する電源電圧の下限は存在しない。それ故、電源電圧を十分に低く設定することが可能となり、その結果として低消費電力且つ1ビットを超える多値の記憶可能な高性能の不揮発性半導体記憶装置および半導体記憶装置を含む半導体装置が実現される。

1…半導体基板

2…素子分離領域

3…ウエル領域

4…チャネル形成領域

5、5a、5b…トンネルゲート絶縁膜

6…浮遊ゲート電極

7…インターポリ絶縁膜(中間絶縁膜)

8…制御ゲート電極

9…ソース・ドレイン領域

10…半導体基板ないしソース・ドレインを想定した導体領域

11…トンネルゲート絶縁膜を想定した絶縁膜

12…浮遊ゲート電極を想定した導体領域

13…インターポリ絶縁膜を想定した絶縁膜

14…制御ゲート電極を想定した導体領域

15…SiO2膜

16…多結晶シリコン膜

17…SiO2/Si3N4/SiO2積層絶縁膜

2…素子分離領域

3…ウエル領域

4…チャネル形成領域

5、5a、5b…トンネルゲート絶縁膜

6…浮遊ゲート電極

7…インターポリ絶縁膜(中間絶縁膜)

8…制御ゲート電極

9…ソース・ドレイン領域

10…半導体基板ないしソース・ドレインを想定した導体領域

11…トンネルゲート絶縁膜を想定した絶縁膜

12…浮遊ゲート電極を想定した導体領域

13…インターポリ絶縁膜を想定した絶縁膜

14…制御ゲート電極を想定した導体領域

15…SiO2膜

16…多結晶シリコン膜

17…SiO2/Si3N4/SiO2積層絶縁膜

Claims (9)

- 半導体基板中に形成されたソース・ドレイン領域と、前記ソース・ドレイン領域間の前記半導体基板上に第一の絶縁膜を介して形成された第一のゲート電極と、前記第一のゲート電極上に第二の絶縁膜を介して形成された第二のゲート電極と、を備える素子が少なくとも二つ形成され、且つ前記二つの素子の書き込み電圧条件ないし消去電圧条件の少なくとも一方が前記素子毎に異なる値であり、且つ前記素子のソース領域同士、ドレイン領域同士がそれぞれ電気的に結合され、且つ前記素子の第二のゲート電極同士も電気的に結合されていることを特徴とする不揮発性半導体記憶装置。

- 前記素子の書き込み電圧条件及び消去電圧条件のいずれもが前記素子毎に異なる値であることを特徴とする請求項1に記載の不揮発性半導体記憶装置。

- 前記素子のソース・ドレイン領域間を流れる電流の主方向に垂直に測った幅が前記素子毎に異なる値であることを特徴とする請求項2に記載の不揮発性半導体記憶装置。

- 前記素子のソース・ドレイン領域間を流れる電流の主方向に垂直に測った幅に0ないし1を掛けた値の前記素子の全体に渡る総和が、前記素子の各々に対する0ないし1の可能な割り振り方の全てに対して尽く異なる値となることを特徴とする請求項3に記載の不揮発性半導体記憶装置。

- 前記第一の絶縁膜の厚さが前記素子毎に異なる値であることを特徴とする請求項1から請求項4のいずれかに記載の不揮発性半導体記憶装置。

- 前記素子のソース・ドレイン領域間を流れる電流の流路の形成される半導体領域と前記第一の絶縁膜との界面が各々の素子の内で少なくとも二つの面よりなることを特徴とする請求項5に記載の不揮発性半導体記憶装置。

- 前記第一のゲート電極は、浮遊ゲート電極もしくは、酸化膜/窒化膜の積層膜からなることを特徴とする請求1ないし6のいずれかに記載の不揮発性半導体記憶装置。

- 前記第一の絶縁膜は、トンネルゲート絶縁膜であることを特徴とする請求1ないし6のいずれかに記載の不揮発性半導体記憶装置。

- 前記請求項1記載の不揮発性半導体記憶装置を一部に含むことを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108053A JP2005294565A (ja) | 2004-03-31 | 2004-03-31 | 不揮発性半導体記憶装置およびこの不揮発性半導体記憶装置を含む半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108053A JP2005294565A (ja) | 2004-03-31 | 2004-03-31 | 不揮発性半導体記憶装置およびこの不揮発性半導体記憶装置を含む半導体装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294565A true JP2005294565A (ja) | 2005-10-20 |

Family

ID=35327152

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004108053A Pending JP2005294565A (ja) | 2004-03-31 | 2004-03-31 | 不揮発性半導体記憶装置およびこの不揮発性半導体記憶装置を含む半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005294565A (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007250724A (ja) * | 2006-03-15 | 2007-09-27 | Citizen Holdings Co Ltd | 不揮発性半導体記憶装置およびその製造方法と書き込み方法 |

| KR100810519B1 (ko) * | 2007-05-23 | 2008-03-07 | 한국과학기술원 | 기계적인 스위치를 이용한 비휘발성 메모리 셀 및 그어레이 |

| JP2008172195A (ja) * | 2006-10-11 | 2008-07-24 | Macronix Internatl Co Ltd | 縦型チャネルメモリーとその製造方法および稼働方法 |

| JP2013055206A (ja) * | 2011-09-03 | 2013-03-21 | Takehide Shirato | 半導体装置及びその製造方法 |

| US9246015B2 (en) | 2006-10-11 | 2016-01-26 | Macronix International Co., Ltd. | Vertical channel transistor structure and manufacturing method thereof |

| JP2022128589A (ja) * | 2021-02-23 | 2022-09-02 | コリア アドバンスド インスティチュート オブ サイエンス アンド テクノロジィ | 優れた線形性特性を有するニューロモルフィックシナプス素子およびその動作方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6459960A (en) * | 1987-08-31 | 1989-03-07 | Agency Ind Science Techn | Nonvolatile semiconductor memory element |

| JPH0677498A (ja) * | 1992-08-28 | 1994-03-18 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JPH07111292A (ja) * | 1993-08-19 | 1995-04-25 | Matsushita Electric Ind Co Ltd | 不揮発性メモリセル |

| JPH09293795A (ja) * | 1996-04-25 | 1997-11-11 | Nec Corp | 不揮発性半導体記憶装置及びその動作方法 |

| JPH1174382A (ja) * | 1997-08-29 | 1999-03-16 | Nec Corp | 不揮発性半導体記憶装置 |

| JP2002313967A (ja) * | 2001-02-06 | 2002-10-25 | Toshiba Corp | 半導体装置及びその製造方法 |

-

2004

- 2004-03-31 JP JP2004108053A patent/JP2005294565A/ja active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6459960A (en) * | 1987-08-31 | 1989-03-07 | Agency Ind Science Techn | Nonvolatile semiconductor memory element |

| JPH0677498A (ja) * | 1992-08-28 | 1994-03-18 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JPH07111292A (ja) * | 1993-08-19 | 1995-04-25 | Matsushita Electric Ind Co Ltd | 不揮発性メモリセル |

| JPH09293795A (ja) * | 1996-04-25 | 1997-11-11 | Nec Corp | 不揮発性半導体記憶装置及びその動作方法 |

| JPH1174382A (ja) * | 1997-08-29 | 1999-03-16 | Nec Corp | 不揮発性半導体記憶装置 |

| JP2002313967A (ja) * | 2001-02-06 | 2002-10-25 | Toshiba Corp | 半導体装置及びその製造方法 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007250724A (ja) * | 2006-03-15 | 2007-09-27 | Citizen Holdings Co Ltd | 不揮発性半導体記憶装置およびその製造方法と書き込み方法 |

| JP2008172195A (ja) * | 2006-10-11 | 2008-07-24 | Macronix Internatl Co Ltd | 縦型チャネルメモリーとその製造方法および稼働方法 |

| US9246015B2 (en) | 2006-10-11 | 2016-01-26 | Macronix International Co., Ltd. | Vertical channel transistor structure and manufacturing method thereof |

| KR100810519B1 (ko) * | 2007-05-23 | 2008-03-07 | 한국과학기술원 | 기계적인 스위치를 이용한 비휘발성 메모리 셀 및 그어레이 |

| JP2013055206A (ja) * | 2011-09-03 | 2013-03-21 | Takehide Shirato | 半導体装置及びその製造方法 |

| JP2022128589A (ja) * | 2021-02-23 | 2022-09-02 | コリア アドバンスド インスティチュート オブ サイエンス アンド テクノロジィ | 優れた線形性特性を有するニューロモルフィックシナプス素子およびその動作方法 |

| JP7499523B2 (ja) | 2021-02-23 | 2024-06-14 | コリア アドバンスド インスティチュート オブ サイエンス アンド テクノロジィ | 優れた線形性特性を有するニューロモルフィックシナプス素子およびその動作方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9812211B2 (en) | Semiconductor device | |

| TW512495B (en) | Nonvolatile semiconductor memory device, process of manufacturing the same and method of operating the same | |

| US20040245564A1 (en) | Semiconductor storage device, semiconductor device and their manufacturing methods, and portable electronic equipment, and IC card | |

| WO2005119783A2 (en) | Ballistic injection nrom flash memory | |

| US9455352B2 (en) | HTO offset for long leffective, better device performance | |

| US20070018228A1 (en) | Non-volatile memory with carbon nanotubes | |

| KR100904568B1 (ko) | 불휘발성 반도체 기억 소자 및 불휘발성 반도체 기억 장치 | |

| JP4761946B2 (ja) | 不揮発性半導体記憶素子及びその製造方法並びに不揮発性半導体記憶素子を含む半導体集積回路装置 | |

| JP2005294565A (ja) | 不揮発性半導体記憶装置およびこの不揮発性半導体記憶装置を含む半導体装置 | |

| US20110169069A1 (en) | Hto offset and bl trench process for memory device to improve device performance | |

| US9209197B2 (en) | Memory gate landing pad made from dummy features | |

| US20160218227A1 (en) | Gate Formation Memory by Planarization | |

| JP7781476B2 (ja) | フラッシュメモリセルならびにその製造方法、書き込み方法、及び消去方法 | |

| EP1899977B1 (en) | Method for programming a memory device | |

| US20210104533A1 (en) | Split gate charge trapping memory cells having different select gate and memory gate heights | |

| JP4854375B2 (ja) | 半導体記憶装置及びその製造方法、並びに携帯電子機器 | |

| US20140167136A1 (en) | Charge Trapping Device with Improved Select Gate to Memory Gate Isoloation | |

| JP3658542B2 (ja) | 不揮発性半導体記憶装置及び製造方法 | |

| JP5363004B2 (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070801 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080829 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081028 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20091023 |