JP2005292978A - プログラム制御によって動作する機器の簡易デバッグ方式 - Google Patents

プログラム制御によって動作する機器の簡易デバッグ方式 Download PDFInfo

- Publication number

- JP2005292978A JP2005292978A JP2004104064A JP2004104064A JP2005292978A JP 2005292978 A JP2005292978 A JP 2005292978A JP 2004104064 A JP2004104064 A JP 2004104064A JP 2004104064 A JP2004104064 A JP 2004104064A JP 2005292978 A JP2005292978 A JP 2005292978A

- Authority

- JP

- Japan

- Prior art keywords

- output

- program

- function

- debugging

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Debugging And Monitoring (AREA)

Abstract

【課題】インサーキットエミュレータを利用するデバッグ方式の欠点を回避し、予め設定した条件でのプログラムトレースに機能を限定することにより、インサーキットエミュレータを使用せずに簡便にプログラムの実時間トレースが可能になる簡易デバッグ方式を提供する。

【解決手段】ターゲット機器(54)からデバッグ用データを出力する出力端子(55)を備え、数行程度の簡単なプログラムの如きデバッグ用データ出力プログラムをターゲット機器(54)に対する所望のプログラムに含ませて動作させることにより、出力端子(54)からデバッグ用のデータが出力されるように構成されている。

【選択図】 図1

【解決手段】ターゲット機器(54)からデバッグ用データを出力する出力端子(55)を備え、数行程度の簡単なプログラムの如きデバッグ用データ出力プログラムをターゲット機器(54)に対する所望のプログラムに含ませて動作させることにより、出力端子(54)からデバッグ用のデータが出力されるように構成されている。

【選択図】 図1

Description

本発明は、MPUのプログラムによって制御される装置の開発時におけるデバッグや運用中の不具合症状の解析のために、プログラムを運用環境で動作させた状態でプログラム動作状態を外部より知ることができるデバッグ方式に関するものである。

一般的にMPUによって制御される装置の開発段階におけるデバッグは、インサーキットエミュレータやロジックアナライザなどの測定器類を接続して行うか、あるいは、キーボードやディスプレイを備えた装置でOSが稼動できる状態であればオンラインデバッガプログラムなどを用いるのが一般的である。

ハードウェアの多くも小型化や柔軟性のために集積化され、何らかのプロセッサによって制御されるようになっているものも極めて多い。

このように、MPUによって制御される装置は、ソフトウェアのみならずハードウェアの開発においてもソフトウェアデバッグのフェーズを避けることは出来ない。

ハードウェアの多くも小型化や柔軟性のために集積化され、何らかのプロセッサによって制御されるようになっているものも極めて多い。

このように、MPUによって制御される装置は、ソフトウェアのみならずハードウェアの開発においてもソフトウェアデバッグのフェーズを避けることは出来ない。

インサーキットエミュレータ50によるデバッグは、図8に示すように、プログラムの実行・停止が各種条件で可能であり、デバッグの自由度が高いため、非常に有効なデバッキングツールであるが、以下のような欠点がある。

(1)MPUの種類により個別の装置(エミュレーションポッド51とエミュレーションプローブ52)が必要である。また、1台で1台にしか接続できないので、多くの種類の装置開発を手がけると設備投資がかさむ。

(2)プログラム開発環境と整合のとれたデバッグ用の環境(エミュレータ50からの情報とコンパイル/リンク時の情報とソースコードを複合情報として表示/操作する)をPC53上に整える必要があり、そのための費用がエミュレータ台数に応じてかかる。

(3)CPUのパッケージ形態(直接はんだ付けする場合など)によってはエミュレータを接続するために専用の基板を用意する必要があり、開発投資もかさむ。

(4)運用状態で不具合の解析などCPU基板54を装置に実装した状態では、構造上エミュレータ接続が不可能であったり、あるいは非常に困難が伴う場合が多い。

(5)エミュレーションプローブ52をターゲットCPU基板54の如きデバッグのターゲット装置に接続することによって電源負荷やノイズの発生状態,負荷駆動条件などが変わるために、周辺回路が影響を受けて実行条件が変わってしまう場合がある。

(6)エミュレータ50の仕様上、利用できるメモリ空間に制限があるためエミュレーションそのものに制約が発生することもある。

(7)一般的にデバッグ時には条件付きコンパイル等を行い、生成コードの最適化オプションも設定しない。これは最適化処理によりバイナリコードの最適化が行われると、コンパイラの途中出力であるソースコード表示のための情報と、コンパイラの最終出力であるバイナリコードとの整合が取れなくなることがあるためであるが、最終的な実行コードは処理速度向上のために最適化される場合も多く、最適化されたコードではインサーキットエミュレーションが困難になる場合がある。

(1)MPUの種類により個別の装置(エミュレーションポッド51とエミュレーションプローブ52)が必要である。また、1台で1台にしか接続できないので、多くの種類の装置開発を手がけると設備投資がかさむ。

(2)プログラム開発環境と整合のとれたデバッグ用の環境(エミュレータ50からの情報とコンパイル/リンク時の情報とソースコードを複合情報として表示/操作する)をPC53上に整える必要があり、そのための費用がエミュレータ台数に応じてかかる。

(3)CPUのパッケージ形態(直接はんだ付けする場合など)によってはエミュレータを接続するために専用の基板を用意する必要があり、開発投資もかさむ。

(4)運用状態で不具合の解析などCPU基板54を装置に実装した状態では、構造上エミュレータ接続が不可能であったり、あるいは非常に困難が伴う場合が多い。

(5)エミュレーションプローブ52をターゲットCPU基板54の如きデバッグのターゲット装置に接続することによって電源負荷やノイズの発生状態,負荷駆動条件などが変わるために、周辺回路が影響を受けて実行条件が変わってしまう場合がある。

(6)エミュレータ50の仕様上、利用できるメモリ空間に制限があるためエミュレーションそのものに制約が発生することもある。

(7)一般的にデバッグ時には条件付きコンパイル等を行い、生成コードの最適化オプションも設定しない。これは最適化処理によりバイナリコードの最適化が行われると、コンパイラの途中出力であるソースコード表示のための情報と、コンパイラの最終出力であるバイナリコードとの整合が取れなくなることがあるためであるが、最終的な実行コードは処理速度向上のために最適化される場合も多く、最適化されたコードではインサーキットエミュレーションが困難になる場合がある。

このような従来技術の欠点を克服するために、システムLSI,マイクロコンピュータMUP,ディジタル信号処理装置DSP等のデバッグを効率的に行うために、LSI等に接続されたテスト端子より内部情報を出力する技術(特許文献1参照)、CPUに端子数を削減したテスト用入出力端子を接続する技術(特許文献2参照)が提案されている。

特開2001−142733号公報

特開2000−207380号公報

しかしながら、これらの従来技術では、内部情報をとり出すために、特別にテスト信号を入力するテスト端子を設けることが必要である。

本発明の目的は、インサーキットエミュレータを利用するデバッグ方式の上記のような欠点を回避し、予め設定した条件でのプログラムトレースに機能を限定することにより、インサーキットエミュレータを使用せずに簡便にプログラムの実時間トレースが可能になる簡易デバッグ方式を提供することにある。

この目的を達成するために、本発明による簡易デバッグ方式は、ターゲット機器からデバッグ用データを出力する出力端子を備え、

数行程度の簡単なプログラムの如きデバッグ用データ出力プログラムを前記ターゲット機器に対する所望のプログラムに含ませて動作させることにより、

前記出力端子からデバッグ用のデータが出力されるように構成されている。

数行程度の簡単なプログラムの如きデバッグ用データ出力プログラムを前記ターゲット機器に対する所望のプログラムに含ませて動作させることにより、

前記出力端子からデバッグ用のデータが出力されるように構成されている。

本発明により、以下の効果が得られる。

ロジックアナライザないしは相当する機材のみを用いて簡易なプログラムトレースが可能となり、

(1)インサーキットエミュレータがない環境でも簡易的なソフトウェアデバッグや不具合の特定が可能になる。

(2)インサーキットエミュレータに依存する動作の制約や回路への影響を排除することができる。

(3)トレースのための情報を出力するソフト処理は極くわずかであり、ソースコード作成時点でこの処理を埋め込んでおけばソフトウェア上の負担もほとんどなく、最終的に削除しなくてもシステムに与える影響は全くないかあってもごくわずかである。したがってデバッグのためのリソースを殆ど消費しない。

(4)CPUの種類に依存する投資が不要。

(5)開発時のデバッグ環境規模に依存した投資を削減することができる。

ロジックアナライザないしは相当する機材のみを用いて簡易なプログラムトレースが可能となり、

(1)インサーキットエミュレータがない環境でも簡易的なソフトウェアデバッグや不具合の特定が可能になる。

(2)インサーキットエミュレータに依存する動作の制約や回路への影響を排除することができる。

(3)トレースのための情報を出力するソフト処理は極くわずかであり、ソースコード作成時点でこの処理を埋め込んでおけばソフトウェア上の負担もほとんどなく、最終的に削除しなくてもシステムに与える影響は全くないかあってもごくわずかである。したがってデバッグのためのリソースを殆ど消費しない。

(4)CPUの種類に依存する投資が不要。

(5)開発時のデバッグ環境規模に依存した投資を削減することができる。

本発明の実施例を図1,図2,図3,図4,図5,図6,図7に示す。

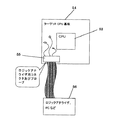

図1は全体構成、図2,図4は本発明の実施例のハードウェア(並列と直列)、図3は本発明の実施例のハードウェア・並列・タイミングチャート、図5は本発明の実施例のハードウェア・直列・タイミングチャート、図6は本発明の実施例のソフトウェア(C言語の場合)、図7は本発明によるトレース状態出力のそれぞれ例である。

図1に示すように、本発明によるデバッグ環境の構成は非常に簡単であり、ターゲットCPU基板54側ではプログラムの処理部分毎に予め割り振ったデータを外部に出力し、この出力をコネクタ及びプローブ55を介して外部のロジックアナライザ56ないしデジタル入力ポートを備えたPC等にて記録するだけである。

並列データを入力して記録し、別途読み出しする手段があればロジックアナライザ56やPCには限定されない。

図1は全体構成、図2,図4は本発明の実施例のハードウェア(並列と直列)、図3は本発明の実施例のハードウェア・並列・タイミングチャート、図5は本発明の実施例のハードウェア・直列・タイミングチャート、図6は本発明の実施例のソフトウェア(C言語の場合)、図7は本発明によるトレース状態出力のそれぞれ例である。

図1に示すように、本発明によるデバッグ環境の構成は非常に簡単であり、ターゲットCPU基板54側ではプログラムの処理部分毎に予め割り振ったデータを外部に出力し、この出力をコネクタ及びプローブ55を介して外部のロジックアナライザ56ないしデジタル入力ポートを備えたPC等にて記録するだけである。

並列データを入力して記録し、別途読み出しする手段があればロジックアナライザ56やPCには限定されない。

図2,図3は本発明のハードウェア部分の実施例である。この実施例ではデータをnビット(nは整数)の並列出力としているが、端子の都合で図4,図6のように直列出力としても構わない。

ただし直列出力の場合には、並列の場合よりも出力に時間がかかるため、出力データの変化する時間間隔が直列出力に要する時間よりも短い場合には利用できない。

ただし直列出力の場合には、並列の場合よりも出力に時間がかかるため、出力データの変化する時間間隔が直列出力に要する時間よりも短い場合には利用できない。

<並列出力の場合>

図2において、出力状態が読み出し可能なnビットレジスタの出力のポートPPOUTは、CPUが生成する書き込み信号/WRと読み出し信号/RD、及びアドレスバス信号などから生成されるデバイス選択信号/CSによって制御される。PPOUTとCPUとのデータ交換はデータバスを介して行われるものとする。これらの制御信号はCPUアーキテクチャに依存するので、必ずしもこの構成でなくても良い。

ラッチクロックLCKはCPUクロックに同期した一定周波数のクロック信号を仮定する。一般にはCPUクロックを分周してこのようなクロックを容易に得ることが可能である。

PPOUTは、CSがロウレベルになることにより、書き込みまたは読み出し可能になるものとする。

PPOUTにデータを書き込む際には、CSをロウとしておき、WRの立ち上がりでデータバスからの入力を確定する。

PPOUTからデータを読み出す際には、CSをロウとしておき、RDをロウとすることでデータバスにデータを出力する。

図2において、出力状態が読み出し可能なnビットレジスタの出力のポートPPOUTは、CPUが生成する書き込み信号/WRと読み出し信号/RD、及びアドレスバス信号などから生成されるデバイス選択信号/CSによって制御される。PPOUTとCPUとのデータ交換はデータバスを介して行われるものとする。これらの制御信号はCPUアーキテクチャに依存するので、必ずしもこの構成でなくても良い。

ラッチクロックLCKはCPUクロックに同期した一定周波数のクロック信号を仮定する。一般にはCPUクロックを分周してこのようなクロックを容易に得ることが可能である。

PPOUTは、CSがロウレベルになることにより、書き込みまたは読み出し可能になるものとする。

PPOUTにデータを書き込む際には、CSをロウとしておき、WRの立ち上がりでデータバスからの入力を確定する。

PPOUTからデータを読み出す際には、CSをロウとしておき、RDをロウとすることでデータバスにデータを出力する。

図3はこれらのタイミングチャートの概念図を示す。制御信号の極性やタイミングなどの物理的な関係はCPUのアーキテクチャに依存するため、図2,図3は概念を示している。

PPOUTの出力は外部機器で容易に読み取ることができる。ロジックアナライザを用いると、LCKを用いなくても予め設定したサンプリング間隔でPPOUTの出力を記録することができる。

ロジックアナライザ以外の手段で出力データを保存するための便宜のために、LCKが用意される。例えば、LCKの立ち上がりで出力データをラッチすることができる。LCKは、また、時間の経過を外部に伝える役割も果たすことができる。例えば、外部機器でLCKをカウンタのクロック入力に接続しておき、出力データの変化点でカウンタの値を記録することにより,プログラムの所定の範囲にどれだけ時間を要したかを容易に推定することができる。

PPOUTの出力は外部機器で容易に読み取ることができる。ロジックアナライザを用いると、LCKを用いなくても予め設定したサンプリング間隔でPPOUTの出力を記録することができる。

ロジックアナライザ以外の手段で出力データを保存するための便宜のために、LCKが用意される。例えば、LCKの立ち上がりで出力データをラッチすることができる。LCKは、また、時間の経過を外部に伝える役割も果たすことができる。例えば、外部機器でLCKをカウンタのクロック入力に接続しておき、出力データの変化点でカウンタの値を記録することにより,プログラムの所定の範囲にどれだけ時間を要したかを容易に推定することができる。

<直列出力の場合>

図4に示すように、直列出力の場合にはPPOUT出力を入力とする並列−直列変換器SPCNVとnビット直列出力制御部SCNTによって並列データを直列に変換して外部に出力する。

図5はそのタイミングチャートである。CPUとPPOUTの関係は、図2,図3と同じである。

PPOUTに書き込まれた並列データは、SCNT内において、WRをSCKを用いて遅延させて生成するラッチ信号/LDによって、SPCNVにロードされる。

SPCNVにラッチされているデータは、直列出力用のクロックScによってSPCNV内で順次シフトされつつSoとして出力される。

直列変換された信号Soを外部で受け取る便宜のために直列出力イネーブル信号/Seを用意し、/Seがロウレベルのときに直列出力データSoを外部で受け取れるようにする。

図2,図4に示すハードウェアは、汎用デバイスを用いて容易に構成することが可能であるため、ここでは詳細な説明はしない。

図4に示すように、直列出力の場合にはPPOUT出力を入力とする並列−直列変換器SPCNVとnビット直列出力制御部SCNTによって並列データを直列に変換して外部に出力する。

図5はそのタイミングチャートである。CPUとPPOUTの関係は、図2,図3と同じである。

PPOUTに書き込まれた並列データは、SCNT内において、WRをSCKを用いて遅延させて生成するラッチ信号/LDによって、SPCNVにロードされる。

SPCNVにラッチされているデータは、直列出力用のクロックScによってSPCNV内で順次シフトされつつSoとして出力される。

直列変換された信号Soを外部で受け取る便宜のために直列出力イネーブル信号/Seを用意し、/Seがロウレベルのときに直列出力データSoを外部で受け取れるようにする。

図2,図4に示すハードウェアは、汎用デバイスを用いて容易に構成することが可能であるため、ここでは詳細な説明はしない。

<ソフトウェア>

本発明においては、図2,図4などに示す簡単なハードウェアとともに、極く僅かなソフトウェア上の構成が必要である。

図6は7個の関数プログラムで本発明を説明する為のC言語のソースプログラムの一例であるが、本発明は言語仕様に依存しないので、他の言語で記述されていても同じ考え方を適用することができる。

図6において、“#define”で開始される行は、本発明において用いる、プログラムの実行部分を示す定数と、図2,図4においてPPOUTとして示すポートのI/Oアドレスの定義である。

本発明においては、図2,図4などに示す簡単なハードウェアとともに、極く僅かなソフトウェア上の構成が必要である。

図6は7個の関数プログラムで本発明を説明する為のC言語のソースプログラムの一例であるが、本発明は言語仕様に依存しないので、他の言語で記述されていても同じ考え方を適用することができる。

図6において、“#define”で開始される行は、本発明において用いる、プログラムの実行部分を示す定数と、図2,図4においてPPOUTとして示すポートのI/Oアドレスの定義である。

図4の例では、各関数プログラムに固有の数値としてMAIN LOOP,FUNC 1,FUNC 2, SUBFUNC 1, SUBFUNC 2, DEVDR 1, DEVDR 2を定義している。また、PPOUTのアドレスとして TRACE IOを定義している。なお、0×0001とは、16進数0001を意味する。

また“extern”で開始される行は、外部参照関数宣言である。ここではI/Oアドレス空間に配置されたI/Oポート入出力の関数 import() とoutport() を宣言している。

また“extern”で開始される行は、外部参照関数宣言である。ここではI/Oアドレス空間に配置されたI/Oポート入出力の関数 import() とoutport() を宣言している。

図6のプログラム構成は以下の通りである。

(1)関数main loop():無限ループを構成していて、関数func 1()と関数func 2()を呼び出す。

(2)関数func 1():関数 subfunc 1()を呼び出す。

(3)関数func 2():関数 subfunc 2()を呼び出す。

(4)関数 subfunc 1():関数 devdr 1()を呼び出す。

(5)関数 subfunc 2():関数 devdr 2()を呼び出す。

(6)関数 devdr 1():特に何もしない。

(7)関数 devdr 2():特に何もしない。

プログラム中の“/*”と“*/”で囲まれた部分はコメントである。

(1)関数main loop():無限ループを構成していて、関数func 1()と関数func 2()を呼び出す。

(2)関数func 1():関数 subfunc 1()を呼び出す。

(3)関数func 2():関数 subfunc 2()を呼び出す。

(4)関数 subfunc 1():関数 devdr 1()を呼び出す。

(5)関数 subfunc 2():関数 devdr 2()を呼び出す。

(6)関数 devdr 1():特に何もしない。

(7)関数 devdr 2():特に何もしない。

プログラム中の“/*”と“*/”で囲まれた部分はコメントである。

<関数main loop()>

処理Sm1,処理Sm2はこの関数の中で使うローカル変数の宣言である。

処理Sm1では符号なし整数として変数 trace out を、Sm2では符号付整数として変数f1及びf2を宣言している。

処理Sm3は無限ループ構造を示し、ループ中で処理Sm4,Sm5,Sm6,Sm7,Sm8を繰り返し実行する。

処理Sm4はPPOUTポートから現状の出力値を読み出し、 trace out に保存する。

処理Sm5はPPOUTポートに関数main loop()の実行を示す定数MAIN LOOPを出力する。

処理Sm6は関数func 1()、Sm7は関数func 2()を呼び出す。

処理Sm8は trace out に保存してあった以前のPPOUT出力状態を出力する。

処理Sm1,処理Sm2はこの関数の中で使うローカル変数の宣言である。

処理Sm1では符号なし整数として変数 trace out を、Sm2では符号付整数として変数f1及びf2を宣言している。

処理Sm3は無限ループ構造を示し、ループ中で処理Sm4,Sm5,Sm6,Sm7,Sm8を繰り返し実行する。

処理Sm4はPPOUTポートから現状の出力値を読み出し、 trace out に保存する。

処理Sm5はPPOUTポートに関数main loop()の実行を示す定数MAIN LOOPを出力する。

処理Sm6は関数func 1()、Sm7は関数func 2()を呼び出す。

処理Sm8は trace out に保存してあった以前のPPOUT出力状態を出力する。

<関数func 1()とfunc 2()>

処理Sf11、処理Sf12、Sf21、Sf22、はこの関数の中で使うローカル変数の宣言である。

処理Sf11,Sf21では符号なし整数として変数 trace out を、Sf12,Sf22では符号整数として変数sbf を宣言している。

処理Sf13,Sf23はPPOUTポートから現状の出力値を読み出し、 trace out に保存する。

処理Sf14,Sf24はPPOUTポートに関数func 1()ないしfunc 2()の実行を示す定数FUNC 1またはFUNC 2を出力する。

処理Sf15は関数 subfunc 1()、Sf25は関数 subfunc 2()を呼び出す。

処理Sf16,Sf26は trace out に保存してあったもの以前のPPOUT出力状態を出力する。

処理Sf17,Sf27は戻り値としてsbf の値を持ってこの関数を抜けることを表す。

処理Sf11、処理Sf12、Sf21、Sf22、はこの関数の中で使うローカル変数の宣言である。

処理Sf11,Sf21では符号なし整数として変数 trace out を、Sf12,Sf22では符号整数として変数sbf を宣言している。

処理Sf13,Sf23はPPOUTポートから現状の出力値を読み出し、 trace out に保存する。

処理Sf14,Sf24はPPOUTポートに関数func 1()ないしfunc 2()の実行を示す定数FUNC 1またはFUNC 2を出力する。

処理Sf15は関数 subfunc 1()、Sf25は関数 subfunc 2()を呼び出す。

処理Sf16,Sf26は trace out に保存してあったもの以前のPPOUT出力状態を出力する。

処理Sf17,Sf27は戻り値としてsbf の値を持ってこの関数を抜けることを表す。

<関数 subfunc 1()と subfunc 2()>

処理Ssf11,処理Ssf12,Ssf21,Ssf22はこの関数の中で使うローカル変数の宣言である。

処理Ssf11,Ssf21では符号なし整数として変数 trace out を、処理Ssf12,Ssf22では符号付整数として変数 devdr stを宣言している。

処理Ssf13,Ssf23はPPOUTポートから現状の出力値を読み出し、 trace out に保存する。

処理Ssf14,Ssf24はPPOUTポートに関数 subfunc 1()ないし subfunc 2()の実行を示す定数 SUBFUNC 1または SUBFUNC 2を出力する。

処理Ssf15は関数 devdr 1()、Ssf25は関数 devdr 2()を呼び出す。

処理Ssf16,Ssf26は trace out に保存してあったもの以前のPPOUT出力状態を出力する。

処理Ssf17,Ssf27は戻り値として devdr stの値を持ってこの関数を抜けることを表す。

処理Ssf11,処理Ssf12,Ssf21,Ssf22はこの関数の中で使うローカル変数の宣言である。

処理Ssf11,Ssf21では符号なし整数として変数 trace out を、処理Ssf12,Ssf22では符号付整数として変数 devdr stを宣言している。

処理Ssf13,Ssf23はPPOUTポートから現状の出力値を読み出し、 trace out に保存する。

処理Ssf14,Ssf24はPPOUTポートに関数 subfunc 1()ないし subfunc 2()の実行を示す定数 SUBFUNC 1または SUBFUNC 2を出力する。

処理Ssf15は関数 devdr 1()、Ssf25は関数 devdr 2()を呼び出す。

処理Ssf16,Ssf26は trace out に保存してあったもの以前のPPOUT出力状態を出力する。

処理Ssf17,Ssf27は戻り値として devdr stの値を持ってこの関数を抜けることを表す。

<関数 devdr 1()と devdr 2()>

処理Sd11,処理Sd21はこの関数の中で使うローカル変数の宣言である。

処理Sd11,処理Sd21では符号なし整数として変数 trace out を宣言している。

処理Sd12,処理Sd22はPPOUTポートから現状の出力値を読み出し、 trace out に保存する。

処理Sd13,処理Sd23はPPOUTポートに関数 devdr 1()ないし devdr 2()の実行を示す定数 DEVDR 1または DEVDR 2を出力する。

処理Sd14,処理Sd24は trace out に保存してあったもの以前のPPOUT出力状態を出力する。

処理Sd15,処理Sd25は戻り値として“1”ないし“2”の値を持ってこの関数を抜けることを表す。

処理Sd11,処理Sd21はこの関数の中で使うローカル変数の宣言である。

処理Sd11,処理Sd21では符号なし整数として変数 trace out を宣言している。

処理Sd12,処理Sd22はPPOUTポートから現状の出力値を読み出し、 trace out に保存する。

処理Sd13,処理Sd23はPPOUTポートに関数 devdr 1()ないし devdr 2()の実行を示す定数 DEVDR 1または DEVDR 2を出力する。

処理Sd14,処理Sd24は trace out に保存してあったもの以前のPPOUT出力状態を出力する。

処理Sd15,処理Sd25は戻り値として“1”ないし“2”の値を持ってこの関数を抜けることを表す。

図6のプログラムを実行すると、時間経過に伴い、図7に示すようなPPOUT出力が得られる。

図6のプログラムは動作を説明するために記述したもので、特に実効的な処理を何も含んでいない。実際には例えば処理Sm5とSm8の間には何らかの処理が通常は記述される。

図6のプログラムは動作を説明するために記述したもので、特に実効的な処理を何も含んでいない。実際には例えば処理Sm5とSm8の間には何らかの処理が通常は記述される。

本発明においてソフトウェア上で必要なことは、トレースしたい処理の先頭でPPOUTに個別データを出力することである。ソフトウェア処理は通常は図6のように入れ子構造になるので、トレースしたい処理を終えたところで以前の出力状態に戻してやる方がデバッグはしやすい。

一般的に、PPOUTのようなI/Oデバイス入出力の処理(図6では外部参照関数とした)は非常に短い処理であり、アセンブリ言語でも1行か2行で記述可能である。図6では関数呼出しで宣言しているが、コンパイラ処理でインラインアセンブリ言語のマイクロとして処理される事も多い。

アセンブリ言語で1行から2行の処理は、特殊な命令でなければ、全体の処理には全く影響を与えない場合が大半であり、割り込み処理中に記述しても多くの場合は問題がない。

一般的にデバッグ時には条件付コンパイル等を行い、デバッグの便宜のために生成コードの最適化オプションも設定しないが、本発明はそもそも簡易的なバッグ手段であることと、本来の処理に直接影響しない部分にコード生成されることが明らかであるため、最適化を行っても影響はない。

本発明ではプログラムの実行・停止を制御することはできず、トレースのみの機能しかないが、最小限のリソースで運用状態でも実時間トレースが可能である。

一般的に、PPOUTのようなI/Oデバイス入出力の処理(図6では外部参照関数とした)は非常に短い処理であり、アセンブリ言語でも1行か2行で記述可能である。図6では関数呼出しで宣言しているが、コンパイラ処理でインラインアセンブリ言語のマイクロとして処理される事も多い。

アセンブリ言語で1行から2行の処理は、特殊な命令でなければ、全体の処理には全く影響を与えない場合が大半であり、割り込み処理中に記述しても多くの場合は問題がない。

一般的にデバッグ時には条件付コンパイル等を行い、デバッグの便宜のために生成コードの最適化オプションも設定しないが、本発明はそもそも簡易的なバッグ手段であることと、本来の処理に直接影響しない部分にコード生成されることが明らかであるため、最適化を行っても影響はない。

本発明ではプログラムの実行・停止を制御することはできず、トレースのみの機能しかないが、最小限のリソースで運用状態でも実時間トレースが可能である。

システムLSI,マイクロコンピュータMPU,DPS等のプログラム制御によって動作するターゲット機器のデバッグを効率よく実施することができる。

50 エミュレータ本体

51 エミュレーションポッド

52 エミュレーションプローブ

53 パソコン(PC)

54 ターゲット(CPU基板)

55 コネクタ及びプローブ

56 ロジックアナライザ(PCなど)

51 エミュレーションポッド

52 エミュレーションプローブ

53 パソコン(PC)

54 ターゲット(CPU基板)

55 コネクタ及びプローブ

56 ロジックアナライザ(PCなど)

Claims (1)

- ターゲット機器からデバッグ用データを出力する出力端子を備え、

数行程度の簡単なプログラムの如きデバッグ用データ出力プログラムを前記ターゲット機器に対する所望のプログラムに含ませて動作させることにより、

前記出力端子からデバッグ用のデータが出力されるようにした

プログラム制御によって動作する機器の簡易デバッグ方式。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004104064A JP2005292978A (ja) | 2004-03-31 | 2004-03-31 | プログラム制御によって動作する機器の簡易デバッグ方式 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004104064A JP2005292978A (ja) | 2004-03-31 | 2004-03-31 | プログラム制御によって動作する機器の簡易デバッグ方式 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005292978A true JP2005292978A (ja) | 2005-10-20 |

Family

ID=35325873

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004104064A Pending JP2005292978A (ja) | 2004-03-31 | 2004-03-31 | プログラム制御によって動作する機器の簡易デバッグ方式 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005292978A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101540706B (zh) * | 2009-04-23 | 2011-12-28 | 中兴通讯股份有限公司 | 一种实现远程调试的方法及系统 |

-

2004

- 2004-03-31 JP JP2004104064A patent/JP2005292978A/ja active Pending

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101540706B (zh) * | 2009-04-23 | 2011-12-28 | 中兴通讯股份有限公司 | 一种实现远程调试的方法及系统 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6536031B2 (en) | Method for generating behavior model description of circuit and apparatus for logic verification | |

| JP2002123562A (ja) | テスタ構築データの生成方法およびテスタの構築方法並びにテスト回路 | |

| JP2002323995A (ja) | トレース回路 | |

| US6484273B1 (en) | Integrated EJTAG external bus interface | |

| US7428661B2 (en) | Test and debug processor and method | |

| JP3003782B2 (ja) | 開発支援装置 | |

| CN111954854B (zh) | 支持装置以及计算机可读取存储介质 | |

| US4636945A (en) | Microprocessor | |

| CN100487668C (zh) | 一种嵌入式处理器的调试方法 | |

| KR100423891B1 (ko) | 트레이스 모듈을 구비한 마이크로프로세서 | |

| JP2005292978A (ja) | プログラム制御によって動作する機器の簡易デバッグ方式 | |

| US5349660A (en) | Method of improving performance in an automated test system | |

| JPH11282709A (ja) | インサーキットエミュレータ | |

| US8612942B2 (en) | System for debugging computer program | |

| US5828859A (en) | Method and apparatus for setting the status mode of a central processing unit | |

| JP2006318412A (ja) | 半導体装置 | |

| JP3745968B2 (ja) | 試験システム及び試験方法及び試験プログラム及び試験プログラムを記録した計算機で読み取り可能な記録媒体 | |

| JP2563708B2 (ja) | マイクロプロセッサ装置およびそれを用いたエミュレータ装置 | |

| JPH08272770A (ja) | マイクロコントローラディベロップメントシステム | |

| JPH0550016B2 (ja) | ||

| KR100788913B1 (ko) | 반도체 장치의 테스트 시스템을 위한 전치 분기 패턴 발생장치 | |

| KR100189977B1 (ko) | 트레이스기능을 구비한 에뮬레이터시스템과 그 트레이스방법 | |

| JPS63291135A (ja) | マイクロコンピュ−タ開発装置 | |

| CN119201750A (zh) | 一种嵌入式测试的方法、装置及系统 | |

| JPH0444292B2 (ja) |