JP2005190207A - 割り込み制御装置、制御方法 - Google Patents

割り込み制御装置、制御方法 Download PDFInfo

- Publication number

- JP2005190207A JP2005190207A JP2003431252A JP2003431252A JP2005190207A JP 2005190207 A JP2005190207 A JP 2005190207A JP 2003431252 A JP2003431252 A JP 2003431252A JP 2003431252 A JP2003431252 A JP 2003431252A JP 2005190207 A JP2005190207 A JP 2005190207A

- Authority

- JP

- Japan

- Prior art keywords

- interrupt

- type

- resource

- interruption

- address information

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 238000000034 method Methods 0.000 title claims description 107

- 230000008569 process Effects 0.000 claims description 88

- 230000004913 activation Effects 0.000 claims description 13

- 238000006243 chemical reaction Methods 0.000 claims description 6

- 230000004044 response Effects 0.000 claims description 3

- 230000003213 activating effect Effects 0.000 claims description 2

- 230000007704 transition Effects 0.000 description 12

- 238000010586 diagram Methods 0.000 description 8

- 230000007246 mechanism Effects 0.000 description 8

- 230000002093 peripheral effect Effects 0.000 description 5

- 230000004043 responsiveness Effects 0.000 description 4

- 230000008859 change Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/48—Program initiating; Program switching, e.g. by interrupt

- G06F9/4806—Task transfer initiation or dispatching

- G06F9/4812—Task transfer initiation or dispatching by interrupt, e.g. masked

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/24—Handling requests for interconnection or transfer for access to input/output bus using interrupt

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Bus Control (AREA)

- Executing Machine-Instructions (AREA)

- Memory System Of A Hierarchy Structure (AREA)

Abstract

【解決手段】本発明の割り込み制御装置は、割り込み資源のうちOSが管理する第1タイプの割り込み資源およびOSが管理しない第2タイプの割り込み資源のそれぞれに対応するアドレス情報を保持する割り込みベクタレジスタ103aを備え、OSが管理する第1タイプの割り込み資源が発生した割り込みに対しては、割り込みベクタレジスタ103aのアドレス情報に基づいて第1タイプの割り込み資源に共通するスケジュール処理の対象となる共通割り込みエントリ関数105を起動し、ユーザが管理する第2タイプの割り込み資源が発生した割り込みに対しては、割り込みベクタレジスタ103aのアドレス情報に基づいて前記スケジュール処理の対象とならない拡張割り込みエントリ関数を起動する。

【選択図】図2

Description

図10は、従来におけるコンピュータシステムにおける割り込み発生時に、OSのカーネル空間からユーザープロセス空間への遷移関係を示す図である。同図のように、割り込みは、カーネル空間602内において、割り込みを受け付ける割り込み処理部からスケジューラによる割り込みのスケジュール処理の後、プロセス空間601内のユーザープロセスへ遷移する。

ところで、一般的なOSは特定の割り込み資源だけをOSの管理外とする場合を想定しておらず、そうするには特別な機構が必要である。そのための特別な機構として特許文献1では、複数のOSと、OSから独立した割り込み管理プログラムによる実現方法が開示されている。

具体的には、オペレーティングシステム(OS)上の特定の割り込み資源を、他のプログラムにより分離、独立して管理する場合には、以下のような問題がある。

上記の課題に鑑み本発明は、汎用OSにおいて特定の割り込み資源からの割り込みに対してリアルタイム性を保証する割り込み制御装置、その制御方法およびプログラムを提供することを目的とする。特に、本発明は、組み込み機器に広く必要とされるリアルタイム性を汎用OS上で保証、実現する割り込み制御装置、その制御方法およびプログラムを提供することを目的とする。

ここで、前記割り込み制御装置は、さらに、アプリケーションから特定の割り込み資源とアドレス情報とを示す通知を受け付ける受付手段を有し、前記テーブル手段は、受付手段によって受け付けられた通知に従って第2タイプの割り込み資源に対応するアドレス情報を保持する構成としてもよい。

ここで、前記起動手段は、前記第2の制御処理において、コンテキストの退避と、割り込みを発生した第2タイプの割り込み資源に対応する割り込み処理と、退避していたコンテキストの復帰とを順に実行する構成としてもよい。

この構成によれば、第2タイプの割り込み資源に対応する割り込み処理においてリアルタイム性を要する処理が完了するまでは他の割り込み入力を禁止するので、リアルタイム性をより確実に確保することができる。

この構成によれば、仮想記憶用のいわゆるTLB(Translation Look aside Buffer)と呼ばれる変換バッファを更新するので、割り込み処理をプロセス空間に容易に配置することができる。

ここで、前記起動手段は、発生した割り込みの割り込みレベルと所定レベルの優先順位を比較して、前記第1タイプと第2タイプのいずれであるかを判別する構成としてもよい。

さらに、アプリケーションが管理する割り込み処理関数をカーネル空間とは別空間となるアプリケーションのユーザープロセス空間に実装することを可能としている。第2タイプの割り込み資源に対応する割り込み処理、つまり割り込み処理関数(ユーザープロセス空間)への遷移は、リアルタイム性を保証することができる。

以下、本発明の割り込み制御方式の実施形態について、図面を参照しながら説明する。

<割り込み制御装置の構成>

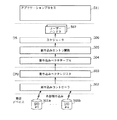

図1は、本発明の実施の形態1における割り込み制御装置のシステム構成を示すブロック図である。同図では、アプリケーションと、OSと、CPUと、割り込みコントローラと、外部デバイスと階層的に示している。図11に示した従来のシステム構成と異なる点は、アプリケーションが自プロセスからOSに対してユーザーで管理したい割り込みレベル、すなわちOSの管理外とする割り込みレベルを通知する機構としてユーザ管理割り込み番号通知部112を備える点と、アプリケーションが準備する拡張割り込みエントリ関数108と呼ぶ関数アドレスを通知する機構として拡張割り込みエントリ関数通知部113を備える点と、OS内に前記アプリケーションが準備する拡張割り込み関数のアドレスの通知を受け取る割り込みベクタ更新部110を備える点とである。拡張割り込みエントリ関数108およびユーザハンドラ109はOSの一部としてではなくアプリケーションとして準備される。

割り込みコントローラ102が、各種周辺デバイス(I/O装置)101a、101b等からの割り込み発生を検出し、該当割り込み要因に対応する要因番号レジスタ102aのフラグをセットする。当該割り込み要因がソフトウェア設定によりマスクされていなければ、割り込みコントローラ102はCPU103に割り込み発生を通知する。

図2の例では、割り込みベクタレジスタ103aにおいてレベル0からレベルmまでの割り込みレベルレジスタは第1タイプの割り込み用であり、それぞれ共通割り込みエントリ関数105の先頭アドレスを保持しているものとする。また、レベルm+1からレベルnまでの割り込みベクタレジスタは第2タイプの割り込み用であり、それぞれ拡張割り込みエントリ関数108の先頭アドレスを保持しているものする。ここで、第1タイプの割り込みとは、従来技術と同様にOSによって共通の管理処理(主としてスケジューラ106のスケジュール処理)を経由して割り込み処理(ユーザの割り込みハンドラ107a、107bなど)が起動される汎用性に優れた割り込みをいう。第2タイプの割り込みとは、アプリケーションが管理する割り込みであって上記の管理処理を経由しないで割り込み処理(ユーザの割り込みハンドラ109a、109bなど)が起動されるリアルタイム性を保証される割り込みをいう。

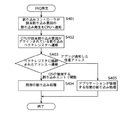

図3は、ユーザーアプリケーションで準備する割り込み処理ルーチン(つまり拡張割り込みエントリ関数108)のアドレスをCPU内の割り込みベクタレジスタへ登録する処理を示すフローチャートである。同図の手順は、リアルタイム性を必要とする任意の割り込み要因を第2タイプの割り込みに設定する場合に、例えばアプリケーションの起動時の最初に実行される。

<割り込み制御処理>

図4は、図3での登録処理後、実際に割り込みが発生した場合の割り込み制御処理を示すフローチャートである。

この結果、図2に示したように、割り込みベクタレジスタ内に格納される割り込みエントリ関数のアドレスは、既存のOSで管理する共通割り込みエントリ関数105のアドレスだけでなく、アプリケーションで準備される拡張割り込みエントリ関数108のアドレスも存在しているので、アプリケーション独自にリアルタイム性のよい割り込み処理が能となる。図2の例では、割り込みレベルがレベルmよりも大きい場合には、第2タイプの割り込みとして拡張割り込みエントリ関数108が起動される。

なお、図4に示した割り込み制御の代わりに図5に示す割り込み制御処理を実行してもよい。図5は、図4と比べて、ステップS405の代わりにステップS504〜S508を実行する点が異なっている。図4と同じステップ番号は同じなので説明を省略し、異なる点を中心に説明する。

まず、拡張割り込みエントリ関数の起動により、まず他の割り込み処理の入力を禁止する(S504)。この禁止は、割り込みコントローラ102のマスクレジスタの設定を変更することにより、マスカブルな割り込みの全部または一部でよい。次に、現在実行中のプロセスのコンテキスト(CPUの各種制御レジスタのデータなど)を退避し(S505)、割り込みを発生した資源に対応するユーザの割り込みハンドラ109a等を選択して実行し(S506)、ユーザの割り込みハンドラの終了後に退避したコンテキストを復帰し(S507)、割り込み入力の禁止を解除する(S508)。

また、図6および図2において、図3に示した登録手順なしに、予めそれぞれの割り込みエントリ関数を登録するようにしてもよい。

図7は、本発明の実施の形態2における割り込み制御装置のシステム構成を示すブロック図である。同図は、図1のシステム構成と比較して、アプリケーションが自プロセスのIDをOSに対して通知するプロセスID通知部114と、OS内に前記アプリケーションから通知されたプロセスIDに基づいてCPUのTLBを更新するTLB更新部117を備える点が主として異なっている。また、同図では、CPU内に仮想記憶用の仮想アドレスと実アドレスとの対応表であるページテーブル115と、ページテーブル115から実行中のプロセスに対応するページデータを一時的にキャッシュするTLB116を備える点を明記している。

次に図9は、図8での登録処理後に実際に割り込みが発生した場合の割り込み制御処理を示すフローチャートである。図9は、図5に示した割り込み制御処理と比較して、ステップS505とS506の間にステップS901が追加されている点が異なっている。図5と同じ番号のステップは同じ処理内容なので説明を省略し、異なる点を中心に説明する。

また、割り込み発生後、拡張割り込みエントリ処理(カーネル空間)からアプリケーションが管理する割り込み処理関数(ユーザープロセス空間)へ遷移するが、カーネル内のスケジューラ106を通らないため、割り込み応答性を阻害することがない。

102a 割り込み要因番号レジスタ

103 CPU

103a 割り込みベクタレジスタ

105 共通割り込みエントリ関数

106 スケジューラ

107 割り込みハンドラ

108 拡張割り込みエントリ関数

109 ユーザ割り込みハンドラ

110 割り込みベクタ更新部

112 ユーザ管理割り込み番号通知部

113 拡張割り込みエントリ関数通知部

114 プロセスID通知部

115 ページテーブル

116 TLB

117 TLB更新部

Claims (10)

- コンピュータシステムを制御するOSの一部として、割り込みを発生する割り込み資源からの割り込みを制御する割り込み制御装置であって、

割り込み資源のうちOSが管理する第1タイプの割り込み資源およびOSが管理しない第2タイプの割り込み資源のそれぞれに対応するアドレス情報を保持するテーブル手段と、

第1タイプの割り込み資源が発生した割り込みに対しては、テーブル手段のアドレス情報に基づいて第1タイプの割り込み資源に共通する管理処理を含む第1の制御処理を起動し、第2タイプの割り込み資源が発生した割り込みに対しては、テーブル手段のアドレス情報に基づいて前記管理処理を含まない第2の制御処理を起動する起動手段と

を備えることを特徴とする割り込み制御装置。 - 前記割り込み制御装置は、さらに、アプリケーションから特定の割り込み資源とアドレス情報とを示す通知を受け付ける受付手段を有し、

前記テーブル手段は、受付手段によって受け付けられた通知に従って第2タイプの割り込み資源に対応するアドレス情報を保持する

ことを特徴とする請求項1記載の割り込み制御装置。 - 前記起動手段は、前記第2の制御処理において、コンテキストの退避と、割り込みを発生した第2タイプの割り込み資源に対応する割り込み処理と、退避していたコンテキストの復帰とを順に実行する

ことを特徴とする請求項1又は2記載の割り込み制御装置。 - 前記起動手段は、前記第2の制御処理において前記コンテキスト退避の開始前に他の割り込み入力を禁止し、前記第2の制御処理が完了するまでに前記割り込み入力の禁止を解除する

ことを特徴とする請求項3記載の割り込み制御装置。 - 前記割り込み制御手段は、さらに、仮想記憶用のページテーブルのうち実行中プロセスに対応するページデータをキャッシュする変換バッファと、

前記起動手段は、前記第2の制御処理において前記割り込み処理実行前に当該割り込み処理に対応するページデータを保持するよう前記変換バッファを更新する更新手段と

を備えることを特徴とする請求項3記載の割り込み制御装置。 - 前記受付手段は、さらにアプリケーションから、第2タイプの割り込み資源に対応する割り込み処理のプロセスIDを示す通知を受け付け、

前記更新手段は、受付手段によって受け付けられた通知に示されるプロセスIDに従って前記ページテーブルから前記ページデータを読み出して前記変換バッファに格納する

ことを特徴とする請求項5記載の割り込み制御装置。 - 前記テーブル手段は、さらに割り込み資源毎に割り込みレベルと前記第1タイプか第2タイプかを示す区分とを保持し、

前記起動手段は、発生した割り込みの割り込みレベルとテーブル手段に保持された区分とに基づいて第1タイプと第2タイプのいずれであるかを判別する

ことを特徴とする請求項1から6の何れかに記載の割り込み制御装置。 - 前記起動手段は、発生した割り込みの割り込みレベルと所定レベルの優先順位を比較して、前記第1タイプと第2タイプのいずれであるかを判別する

ことを特徴とする請求項1から6の何れかに記載の割り込み制御装置。 - コンピュータシステムを制御するOSの一部として、割り込みを発生する割り込み資源からの割り込みを制御する割り込み制御方法であって、

アプリケーションから特定の割り込み資源とアドレス情報とを示す通知を受け付ける受付ステップと、

割り込み資源のうちOSが管理する第1タイプの割り込み資源に対応するアドレス情報を保持する管理テーブルに、受付手段によって受け付けられた通知に従ってOSが管理しない第2タイプの割り込み資源に対応するアドレス情報を追加する追加ステップと、

第1タイプの割り込み資源が発生した割り込みに対しては、管理テーブルのアドレス情報に従って第1タイプの割り込み資源に共通する管理処理を含む第1の制御処理を起動し、第2タイプの割り込み資源が発生した割り込みに対しては、管理テーブルのアドレス情報に基づいて前記管理処理を含まない第2の制御処理を起動する起動ステップと

を有することを特徴とする割り込み制御方法。 - 請求項9記載の割り込み制御方法をコンピュータに実行させる

ことを特徴とするプログラム。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003431252A JP2005190207A (ja) | 2003-12-25 | 2003-12-25 | 割り込み制御装置、制御方法 |

| EP04027460A EP1577768A3 (en) | 2003-12-25 | 2004-11-18 | Apparatus and method for interrupt control |

| US10/995,175 US7209993B2 (en) | 2003-12-25 | 2004-11-24 | Apparatus and method for interrupt control |

| KR1020040104272A KR20050065308A (ko) | 2003-12-25 | 2004-12-10 | 인터럽트 제어 장치, 제어 방법 |

| CNB2004101046992A CN100419688C (zh) | 2003-12-25 | 2004-12-27 | 中断控制装置及控制方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003431252A JP2005190207A (ja) | 2003-12-25 | 2003-12-25 | 割り込み制御装置、制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005190207A true JP2005190207A (ja) | 2005-07-14 |

| JP2005190207A5 JP2005190207A5 (ja) | 2006-12-28 |

Family

ID=34697652

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003431252A Withdrawn JP2005190207A (ja) | 2003-12-25 | 2003-12-25 | 割り込み制御装置、制御方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7209993B2 (ja) |

| EP (1) | EP1577768A3 (ja) |

| JP (1) | JP2005190207A (ja) |

| KR (1) | KR20050065308A (ja) |

| CN (1) | CN100419688C (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013502004A (ja) * | 2009-08-14 | 2013-01-17 | アドバンスト・マイクロ・ディバイシズ・インコーポレイテッド | マルチコア・アーキテクチャのためのユーザレベル割り込み機構 |

| JP2017091544A (ja) * | 2015-11-16 | 2017-05-25 | インターナショナル・ビジネス・マシーンズ・コーポレーションInternational Business Machines Corporation | 仮想プロセッサ・スレッド・グループを使用する処理ユニット内の割込みを処理するための方法、処理ユニット、および設計構造 |

| JP2020512604A (ja) * | 2018-02-13 | 2020-04-23 | 北京小米移動軟件有限公司Beijing Xiaomi Mobile Software Co.,Ltd. | 指紋ロック解除方法、装置、プログラム及び記録媒体 |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7480755B2 (en) * | 2004-12-08 | 2009-01-20 | Hewlett-Packard Development Company, L.P. | Trap mode register |

| CN100458708C (zh) * | 2005-07-05 | 2009-02-04 | 英业达股份有限公司 | 中断控制系统及方法 |

| JP2007079789A (ja) * | 2005-09-13 | 2007-03-29 | Nec Corp | 計算機システム及びイベント処理方法 |

| KR100731983B1 (ko) * | 2005-12-29 | 2007-06-25 | 전자부품연구원 | 저전력 무선 디바이스 프로세서용 하드와이어드 스케줄러및 스케줄링 방법 |

| US7415557B2 (en) * | 2006-06-06 | 2008-08-19 | Honeywell International Inc. | Methods and system for providing low latency and scalable interrupt collection |

| KR100843134B1 (ko) * | 2006-09-15 | 2008-07-02 | 삼성전자주식회사 | 인터럽트 금지구간 처리 장치 및 방법과 페이지 고정 장치및 방법 |

| JP5119994B2 (ja) * | 2008-03-14 | 2013-01-16 | 富士通株式会社 | 性能モニタリングプログラム、性能モニタリング方法、性能モニタリング装置 |

| US7921195B2 (en) * | 2008-06-09 | 2011-04-05 | International Business Machines Corporation | Optimizing service processing based on business information, operational intelligence, and self-learning |

| CN102591719A (zh) * | 2011-01-17 | 2012-07-18 | 上海华虹集成电路有限责任公司 | 一种基于8051cpu系统的中断扩展方法 |

| US9921891B1 (en) * | 2015-03-31 | 2018-03-20 | Integrated Device Technology, Inc. | Low latency interconnect integrated event handling |

| JP6316522B1 (ja) * | 2017-01-25 | 2018-04-25 | 三菱電機株式会社 | 計算機装置、タスク起動方法およびタスク起動プログラム |

| CN111078387B (zh) * | 2017-12-25 | 2024-01-23 | 贵阳忆芯科技有限公司 | 中断聚合装置及其方法 |

| CN117056062B (zh) * | 2023-10-13 | 2024-04-02 | 武汉天喻信息产业股份有限公司 | 一种强制退出中断服务程序的方法和装置 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6356989B1 (en) * | 1992-12-21 | 2002-03-12 | Intel Corporation | Translation lookaside buffer (TLB) arrangement wherein the TLB contents retained for a task as swapped out and reloaded when a task is rescheduled |

| JP3672634B2 (ja) * | 1994-09-09 | 2005-07-20 | 株式会社ルネサステクノロジ | データ処理装置 |

| US6421754B1 (en) * | 1994-12-22 | 2002-07-16 | Texas Instruments Incorporated | System management mode circuits, systems and methods |

| US5768599A (en) * | 1995-02-28 | 1998-06-16 | Nec Corporation | Interrupt managing system for real-time operating system |

| DE19535546B4 (de) * | 1995-09-25 | 2004-04-08 | Siemens Ag | Verfahren zum Betreiben eines durch ein Realzeit-Betriebssystem gesteuerten Realzeit-Computersystems |

| JP2001216172A (ja) * | 1997-09-12 | 2001-08-10 | Hitachi Ltd | マルチos構成方法 |

| US6192442B1 (en) * | 1998-04-29 | 2001-02-20 | Intel Corporation | Interrupt controller |

| JP3404322B2 (ja) * | 1999-05-25 | 2003-05-06 | 株式会社エルミックシステム | 割込処理方法、os支援システム、情報処理装置、記録媒体 |

| US6425038B1 (en) * | 1999-09-28 | 2002-07-23 | Rockwell Automation Technologies, Inc. | Conversion of desk-top operating system for real-time control using installable interrupt service routines |

| US6968412B1 (en) * | 1999-12-30 | 2005-11-22 | Intel Corporation | Method and apparatus for interrupt controller data re-direction |

| DE10063936A1 (de) * | 2000-12-20 | 2002-06-27 | Thomson Brandt Gmbh | Interrupt Controller für einen Mikroprozessor |

-

2003

- 2003-12-25 JP JP2003431252A patent/JP2005190207A/ja not_active Withdrawn

-

2004

- 2004-11-18 EP EP04027460A patent/EP1577768A3/en not_active Ceased

- 2004-11-24 US US10/995,175 patent/US7209993B2/en active Active

- 2004-12-10 KR KR1020040104272A patent/KR20050065308A/ko not_active Application Discontinuation

- 2004-12-27 CN CNB2004101046992A patent/CN100419688C/zh not_active Expired - Fee Related

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013502004A (ja) * | 2009-08-14 | 2013-01-17 | アドバンスト・マイクロ・ディバイシズ・インコーポレイテッド | マルチコア・アーキテクチャのためのユーザレベル割り込み機構 |

| JP2017091544A (ja) * | 2015-11-16 | 2017-05-25 | インターナショナル・ビジネス・マシーンズ・コーポレーションInternational Business Machines Corporation | 仮想プロセッサ・スレッド・グループを使用する処理ユニット内の割込みを処理するための方法、処理ユニット、および設計構造 |

| JP2020512604A (ja) * | 2018-02-13 | 2020-04-23 | 北京小米移動軟件有限公司Beijing Xiaomi Mobile Software Co.,Ltd. | 指紋ロック解除方法、装置、プログラム及び記録媒体 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100419688C (zh) | 2008-09-17 |

| US7209993B2 (en) | 2007-04-24 |

| EP1577768A2 (en) | 2005-09-21 |

| CN1637712A (zh) | 2005-07-13 |

| EP1577768A3 (en) | 2007-08-22 |

| US20050144347A1 (en) | 2005-06-30 |

| KR20050065308A (ko) | 2005-06-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7487503B2 (en) | Scheduling threads in a multiprocessor computer | |

| US7979861B2 (en) | Multi-processor system and program for causing computer to execute controlling method of multi-processor system | |

| JP2005190207A (ja) | 割り込み制御装置、制御方法 | |

| JP4345630B2 (ja) | 情報処理装置、割り込み処理制御方法、並びにコンピュータ・プログラム | |

| US20090241119A1 (en) | Interrupt and Exception Handling for Multi-Streaming Digital Processors | |

| US7590990B2 (en) | Computer system | |

| US6748453B2 (en) | Distributed applications in a portable thread environment | |

| US20020065953A1 (en) | Priority in a portable thread environment | |

| JP2006243865A (ja) | プロセッサおよび情報処理方法 | |

| WO2008062647A1 (en) | Multiprocessor system, system configuration method in multiprocessor system, and program thereof | |

| US10248456B2 (en) | Method and system for providing stack memory management in real-time operating systems | |

| US10489188B2 (en) | Method for reducing interrupt latency in embedded systems | |

| JP2008123157A (ja) | プロセッサ及び割込み制御方法 | |

| JP2010140290A (ja) | マルチプロセッサシステム及びその排他制御の調停方法 | |

| US6961934B2 (en) | Portable thread environment | |

| WO2001086448A2 (en) | A diagnostic tool for a portable thread environment | |

| KR20070117605A (ko) | 멀티프로세서 시스템 및 멀티프로세서 시스템의 제어 방법을 컴퓨터에 실행시키기 위한 프로그램을 기록한 컴퓨터로 판독 가능한 기록 매체 | |

| JP2005149312A (ja) | タスク管理システム | |

| US7702836B2 (en) | Parallel processing device and exclusive control method | |

| JP2005327007A (ja) | 組込みコンピュータ制御プログラム、そのプログラムを記録した記録媒体、及び組込みシステム | |

| JP2005173643A (ja) | コンピュータシステム及びそのオペレーティング方法 | |

| US11403138B2 (en) | Method and electronic device for handling relative priority based scheduling procedure | |

| JP2001229038A (ja) | マルチオペレーテング計算機システム | |

| JP2006228074A (ja) | マルチタスクシステムおよびマルチタスク制御方法 | |

| JP2023091314A (ja) | 半導体装置、半導体装置の制御方法及びプログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061109 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061109 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080617 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080806 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080909 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20081009 |