JP2004030598A - 平衡デバイスポートを有する多ポートデバイスの電気的挙動を予測するシステム - Google Patents

平衡デバイスポートを有する多ポートデバイスの電気的挙動を予測するシステム Download PDFInfo

- Publication number

- JP2004030598A JP2004030598A JP2003116105A JP2003116105A JP2004030598A JP 2004030598 A JP2004030598 A JP 2004030598A JP 2003116105 A JP2003116105 A JP 2003116105A JP 2003116105 A JP2003116105 A JP 2003116105A JP 2004030598 A JP2004030598 A JP 2004030598A

- Authority

- JP

- Japan

- Prior art keywords

- impedance

- balanced

- matching network

- network

- port

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/36—Circuit design at the analogue level

- G06F30/367—Design verification, e.g. using simulation, simulation program with integrated circuit emphasis [SPICE], direct methods or relaxation methods

Abstract

【課題】平衡デバイスポートを有する多ポートデバイスの電気的挙動を予測する

【解決手段】デバイス(500,1900)の電気的挙動を予測するシステムであって、演算処理手段と、平衡入力ポート(102)および平衡出力ポート(108)を有する少なくとも1つの平衡整合回路網(100)を表現する手段と、前記平衡出力ポート(108)と前記デバイス(500)の平衡ポートとの間の前記少なくとも1つの整合回路網の接続を表現する手段と、整合回路網Sパラメータ行列SMを計算する手段と、デバイスSパラメータ行列SDを求める手段と、前記デバイス(500)と組み合わせた前記整合回路網(100)についての直列接続Sパラメータ行列SCを計算する手段と、前記直列接続Sパラメータ行列から混在モード直列接続SパラメータSCmmを抽出する手段と、を備えることを特徴とする。

【選択図】図24

【解決手段】デバイス(500,1900)の電気的挙動を予測するシステムであって、演算処理手段と、平衡入力ポート(102)および平衡出力ポート(108)を有する少なくとも1つの平衡整合回路網(100)を表現する手段と、前記平衡出力ポート(108)と前記デバイス(500)の平衡ポートとの間の前記少なくとも1つの整合回路網の接続を表現する手段と、整合回路網Sパラメータ行列SMを計算する手段と、デバイスSパラメータ行列SDを求める手段と、前記デバイス(500)と組み合わせた前記整合回路網(100)についての直列接続Sパラメータ行列SCを計算する手段と、前記直列接続Sパラメータ行列から混在モード直列接続SパラメータSCmmを抽出する手段と、を備えることを特徴とする。

【選択図】図24

Description

【0001】

【発明の属する技術分野】

本発明は、平衡デバイスポートを有する多ポートデバイスの電気的挙動を予測するシステムに関する。

【0002】

【従来の技術】

ディジタル電子機器のためのデータ転送速度は、無線通信や有線通信の全ての分野で増加している。従って、ビデオや高品位テレビ(HDTV)やグラフィックスやシリアルインターフェースや他の多くのアプリケーション向けのディジタルデータストリームは、より高い帯域を必要としている。ディジタルデータの転送速度の増加はインターネットの成長する人気に一部起因するものであり、チップや機能ボードやシステムの間の高速相互接続を必要としている。当事者には言うまでもないが、データはディジタルであっても、ディジタルデータがそこに沿って移動する伝送媒体はアナログである。

【0003】

帯域の増加は、雑音源に対しディジタル通信回路がより影響を受け易くする。より高いデータ伝送速度を達成するため、電子回路は電磁障害に対する不感応性を改善し、偶数次高調波を抑制でき、非理想的接地に対しより高い許容範囲を持つようにせねばならない。平衡伝送型の回路構成の使用は、前記事項の達成に役立つ。従って、平衡伝送型の回路構成は過去に比べより一般的になっている。用語「平衡回路構成」に精通した当事者には、それが電気信号をデバイスの単一平衡ポート(シングル・バランスド・ポート)へ給送する、適当に結合された2つの導体線路の存在を意味することは言うまでもないことである。2つの端子がデバイスの単一平衡ポート(シングル・バランスド・ポート)を形成するのは、各端子を被結合導体の一方へ接続した場合である。ここで使用する用語「デバイス」は、電気的挙動を呈する任意のデバイスあるいは回路を指す。平衡デバイスの解析は、デバイスの標準Sパラメータを混在モードSパラメータに変換することで達成することができる。混在モードSパラメータは、平衡構造内を伝搬する差動モード信号と同相モード信号を記述するものである。2つの被結合導体を互いに180度位相をずらし同振幅でもって駆動したときに、差動モードが発生する。2つの被結合導体が同相同振幅を有するときに、同相モードが発生する。平衡構造内の理想的な信号は、純差動モードである。差動モードが有利であるのは、被結合導体上の電圧が「1」を表わしかつ反対極性を有する場合に、高速ディジタル差動受信器が不平衡の場合よりも大電圧を発生し、ディジタル値「1」を表わすからである。同様に、被結合導体上の電圧が「0」を表わしかつ反対極性を有する場合は、差動受信器は不平衡の場合よりも小電圧を発生し、ディジタル値「0」を表わす。平衡回路構成において導体を結合する目的は、接地面の戻り線路内で発生する雑音などのあらゆる同相モード信号が両導体上で同振幅同位相に見えるようになし、ディジタル差動受信器でキャンセルすることにある。

【0004】

不平衡の回路構成を有するデバイスのディジタル設計者が用いる幾つかのツールキットの一部として試験、測定、解析の各手法が開発され、1つのモデルに基づくデバイスや素子の多数相互接続からなるデバイスの電気的挙動の予測に役立っている。デバイス設計を準備した後、設計者は新規に設計したデバイスの電気的挙動を数学的に予測し、そのデバイスにとっての所望性能仕様に対しそれを比較することが可能となる。場合によっては、予測された電気挙動は所望の性能仕様を満たさず、それ故にデバイスを設計しようとしているニーズに応えないことがある。こうした場合、電子設計者は新規設計デバイスを試作しないことを選択し、所望の予測挙動が得られるようデバイスの再設計へと進む。期待性能を満たさないデバイスの試作ステップの排除は、無駄な努力と経費を排し、より性能の良好な製品の市場への投入時間を改善するのに役立つ。

【0005】

ここで「ディエンベディング/エンベディング・アプリケーションノート」と呼ぶ非特許文献1には、「ディエンベディング(除去)」と名付けた方法が開示されている。ディエンベディング手法は、2つのアダプタを直列接続(カスケード接続)したデバイスの測定値と2つのアダプタ自体の測定値からのデバイスのSパラメータを割り出すのに用いられる。ディエンベディング/エンベディング・アプリケーションノートには、モデル化デバイスの電気的挙動を予測する「エンベディング」と名付けた方法もまた開示されている。エンベディング処理では、デバイスのSパラメータと2つのアダプタのSパラメータとの組み合わせがアダプタとの電気的な組み合わせにおけるデバイスの挙動を予測するのに役立つ。エンベディング処理に使用するSパラメータはディエンベディング処理から入手するか、あるいは回路のモデル化と関連Sパラメータの計算を通じて入手することができる。エンベディング及びディエンベディング手法の使用が、コンピュータ支援設計(CAD)ツールと電子デバイス設計者ツールキットの測定ツールとの間の重要なリンクをもたらす。

【0006】

【非特許文献1】

「ベクトル・ネットワーク・アナライザを使用したSパラメータ・ネットワークのディエンベディング及びエンベディング」,アプリケーションノート1364−1,アジレントテクノロジーズ・インク,2000年11月

【0007】

【発明が解決しようとする課題】

ディエンベディング/エンベディング・アプリケーションノートにて教示されるエンベディング手法の1つの限界は、教示用途が不平衡デバイスに向けられたものであることである。従来技術は平衡デバイスに適用できる手法を提供しておらず、しかも電子設計分野の平衡デバイスの使用は増えつつある。それ故、平衡デバイスや平衡回路に適用可能なエンベディング手法に対する要求が存在する。

【0008】

平衡と不平衡のデバイスポートを両方有するデバイスや回路の使用もまた、より一般的になっている。両ポート様式を有するデバイスや回路を、本願明細書では「混在ポートデバイス」と呼ぶことにする。用語「デバイス」がデバイスと回路を指すことは理解されたい。混在ポートデバイスでは、不平衡デバイスポートと平衡ポートが平衡回路構成と不平衡回路構成のインタフェースとなり、不平衡回路構成と平衡回路構成を単一作動システムとして併せ一体化してあるのが普通である。それ故、混在ポートデバイスだけでなく純平衡デバイスも併せ電気的な挙動を予測する方法に対する要求が存在する。

【0009】

多くの平衡回路構成では、デバイスを整合回路網内にエンベディングしたときに、ユーザはその電気的挙動を予測することを欲する。一般に、モデル測定値すなわちSパラメータ測定値は、整合回路網を表す。ベクトル回路網解析器は、線形デバイスのSパラメータを測定する。ベクトル回路網解析器を、ベクトル・ネットワーク・アナライザとも称され、以降、VNAと略称する。大半の市販のVNAは50オーム標準に校正してあるため、測定したSパラメータSDは50オーム特性インピーダンスへ正規化される。Sパラメータ行列SDは、それ故に特性インピーダンスの関数となる。平衡フィルタのような一部の平衡デバイスは、不平衡デバイスポート向けの従来の50オームや平衡ポート向けの従来の100オーム以外の特性インピーダンスへの正規化を必要とする。その上、デバイスインピーダンスの正規化は、ポートごとに異なることもある。多くの商用電子設計自動化ソフトウェアパッケージは、モデルにより表わされる不平衡整合回路網のモデル化へ利用可能で、ユーザが指定したインピーダンスへモデルを正規化できるようにしてある。平衡混在ポート型の回路構成に関し、この種の市販のソフトウェアパッケージは一切存在しない。それ故、任意のインピーダンス値への正規化を可能にする純差動混在ポートデバイスのエンベディング手法に対する要求が存在する。

【0010】

【課題を解決するための手段】

本発明は、上記課題を解決したものであり、デバイスの電気的挙動を予測するシステムであって、演算処理手段と、平衡入力ポートおよび平衡出力ポートを有する少なくとも1つの平衡整合回路網を表現する手段と、前記平衡出力ポートと前記デバイスの平衡ポートとの間の前記少なくとも1つの整合回路網の接続を表現する手段と、整合回路網Sパラメータ行列SMを計算する手段と、デバイスSパラメータ行列SDを求める手段と、前記デバイスと組み合わせた前記整合回路網についての直列接続Sパラメータ行列SCを計算する手段と、前記直列接続Sパラメータ行列から混在モード直列接続SパラメータSCmmを抽出する手段と、を備えることを特徴とする。

【0011】

【発明の実施の形態】

整合回路や整合回路網は、デバイスに現われるインピーダンスを記述する電気的モデルを表す。本発明の教示は、デバイスと組み合わせて表わされる特定の整合回路の仕様をもたらすものである。図1を具体的に参照するに、第1の入力端子104と第2の入力端子106とを含む平衡入力ポート102、および、第1の出力ポート110と第2の出力ポート112とを含む平衡出力ポート108を有する整合回路網100が図示してある。整合回路網100は、平衡入力ポート102と平衡出力ポート108との間のインピーダンスを表す一般的な回路モデルの一実施形態である。図1に示す整合回路網100の実施形態は、三つの異なる副回路の電気的組み合わせを備える。各副回路は、個別の不平衡入力ポートと不平衡出力ポートをもって表わしてある。

【0012】

従来のVNAは、固定インピーダンス環境下でデバイスのパラメータを測定する。一般に、固定インピーダンス環境は全ての被測定デバイスポートについて50オームであり、「基準特性インピーダンス」と呼ばれる。被測定デバイスの各ポートに対し、任意のインピーダンスの選択を可能にすることが望ましい。第1の副回路部はインピーダンス変換素子202であり、図2に図示してある。インピーダンス変換素子202は、平衡インピーダンス変換入力ポート204におけるインピーダンスを平衡インピーダンス変換出力ポート206における異なるインピーダンスへ変換する平衡2ポート回路素子の理想的モデルである。

【0013】

第2の副回路部は、図3に示す一般的な平衡2ポート分流回路網302である。分流回路網302は、第1の分流接続点306と第2の分流接続点308との間に配設した並列インピーダンス素子304を含む。第1の分流接続点306は、第1の入力端子310と第1の出力端子314とに共通である。第2の分流接続点308は、第2の入力端子312と第2の出力端子316とに共通である。第1の入力端子310と第2の入力端子312は、分流回路網302用の第1の平衡入力ポート318を構成している。第1の出力端子314と第2の出力端子316は、分流回路網302用の第2の平衡出力ポート320を構成している。一般的な分流回路網320は、また、第1の分流接続点306と共通電位端101との間に電気的に配設した第1の分流インピーダンス素子322、および、第2の分流接続点308と共通電位端101との間に電気的に配設した第2の分流インピーダンス素子324を含む。当事者には言うまでもないが、この種のモデルを用いたときに、どんなインピーダンス素子も短絡回路あるいは開放回路のどちらかとして一般化することができる。

【0014】

第3の副回路部は、図4に示す一般的な平衡2ポート格子回路網402である。格子回路網402は、第1の格子回路網接続点406と第3の格子回路網接続点410との間に第1の直列インピーダンス素子404を備える。格子回路網402はまた、第2の格子回路網接続点408と第4の格子回路網接続点412との間に第2の直列インピーダンス素子414を備える。第1の格子回路網接続点406と第2の格子回路網接続点408は、格子回路網402の平衡入力ポート416を構成する。第3の格子回路網接続点410と第4の格子回路網接続点412は、格子回路網402の平衡出力ポート418を構成する。一般的な格子回路網402は、第1の交差インピーダンス素子422と第2の交差インピーダンス素子420を備える。第1の交差インピーダンス素子422は、第1の格子回路網接続点406と第4の格子回路網接続点412との間に電気的に配設される。第2の交差インピーダンス素子420は、第2の格子回路網接続点408と第3の格子回路網接続点410との間に電気的に配設される。当事者には言うまでもないが、この種のモデルを用いたときにどんなインピーダンス素子も短絡回路あるいは開放回路のどちらかとして一般化することができる。

【0015】

図1に示す整合回路網実施形態は、1つのインピーダンス変換素子202、および、1つの分流回路網302と1つの格子回路網402との組み合わせからなる2つの回路を備える。図1は、平衡入力ポート102と平衡出力ポート108の間のインピーダンスを表す一般的な回路の一実施形態を表わす。より複雑な整合回路は、必要数の追加の分流回路網と格子回路網を含む組み合わせ回路として表わすことができよう。

【0016】

図5を具体的に参照するに、平衡回路構成を有する多ポートデバイス500が図示してある。デバイス500は、図1に例示す平衡整合回路網100と同様の構造を有する複数の平衡整合回路網内にエンベディングしてある。本発明の開示は、「複数の装置ポートを有する装置の特性を解明する方法及び機器」と題し、2002年3月14日に出願した米国特許出願第10/098,040号の利点と併せ、複数の平衡整合回路網100中にエンベディングした多ポートデバイス500のSパラメータの予測を可能にする。以降、米国特許出願第10/098,040号を「エンベディング/ディエンベディング特許出願」と呼ぶ。エンベディング/ディエンベディング特許出願は、その教示を本願明細書中に参照用に取り込むものであるが、2Nポートアダプタが接続されるNポートデバイスの挙動を予測する方法が教示されている。この教示は、デバイスとデバイスに接続されるアダプタの分散パラメータ(Sパラメータ)が既知であるときに、2つのデバイスあるいは回路を直列接続したものの電気的挙動の予測方法を示している。得られるのは、直列接続Sパラメータ行列SCである。

【0017】

エンベディング/ディエンベディング特許出願の教示を用いるため、SMで表わされる整合平衡回路網のそれぞれのSパラメータを入手する。図3を具体的に参照するに、Z1は第1の分流インピーダンス素子322の複素インピーダンスを表わし、Z2は並列インピーダンス素子304の複素インピーダンスを表わし、Z3は第2の分流インピーダンス素子324の複素インピーダンスを表わす。従って、分流器回路網302の開放インピーダンス行列Zは、下記となる。

【0018】

【数1】

【0019】

図4を具体的に参照するに、Z4は第1の直列インピーダンス素子404の複素インピーダンスを表わす。Z7は第2の直列インピーダンス素子414の複素インピーダンスを表わす。Z5は、第1の交差インピーダンス素子422の複素インピーダンスを表す。Z6は、第2の交差インピーダンス素子420の複素インピーダンスを表す。従って、格子回路網402の短絡アドミタンス行列Yは、下記となる。

【0020】

【数2】

【0021】

図1に示す整合回路網の各分流インピーダンス素子や各直列インピーダンス素子や各交差インピーダンス素子は、多数の回路のうちの任意の1つとすることができる。実施例としてかつ例示のみを目的に、より一般的な回路構成の一部が図6から図14に図示してある。平衡回路構成の設計者は、インピーダンス素子114からインピーダンス素子128のそれぞれを整合回路網100のモデルをもって表現することを選択する。図6から図14に示す各回路は、それらの複素インピーダンスによって表わすことができる。従って、整合回路網100の構成部分であるインピーダンス素子114からインピーダンス素子128のそれぞれは、インピーダンスの実数部成分とインピーダンスの虚数部成分とにより数学的に表わすことができる。図6から図14に示す各複素インピーダンスの実数部成分と虚数部成分は、それぞれ式3から式11をもって記述される。

【0022】

【数3】

【0023】

【数4】

【0024】

【数5】

【0025】

【数6】

【0026】

【数7】

【0027】

【数8】

【0028】

【数9】

【0029】

【数10】

【0030】

【数11】

【0031】

ここで、Rはオーム単位の抵抗値を表わし、Lはヘンリー単位のインダクタンス値を表わし、Cはファラッド単位の容量値を表わし、w=2πfである。ここで、πは定数であり、fはヘルツ単位の動作周波数を表わす。より多くの複素インピーダンス素子が、図6から図14により与えられる一般的な回路構成の直列接続あるいは並列接続から構成することができる。一例として、図15に示す回路は図8に示す回路と図9に示す回路とを並列合成して構成したものである。図16に示す回路は、図7に示す回路と図10に示す回路とを並列合成して構成したものである。図17に示す回路は、図6に示す回路と図11に示す回路とを並列合成して構成したものである。図18に示す回路は、図6に示す回路と図7に示す回路と図8に示す回路とを直列合成して構成したものである。図6から図18に表す全ての回路の複素インピーダンス特性は、ソフトウェアライブラリに保存することができる。回路設計者が適当な整合回路網100を確立するときに、従来の「クリックとドロップ」の手法を用いてライブラリから特定の回路構成を入手し、整合回路網向け一般モデルへ挿入することができる。整合回路網についての全構成インピーダンスを選択すると、対応する全インピーダンスを計算することができる。

【0032】

複素インピーダンス成分を有する各回路にとって、誘導リアクタンスや容量リアクタンスのQ値と周波数とが特定された場合、そこで等価抵抗を計算し、インピーダンス素子へ代入することができる。インダクタの等価直列抵抗RQLは、下式で与えられる。

【0033】

【数12】

【0034】

コンデンサの等価直列抵抗RQCは、下式で与えられる。

【0035】

【数13】

【0036】

コンデンサの等価並列抵抗RQCは、下式で与えられる。

【0037】

【数14】

【0038】

図1を具体的に参照するに、開放インピーダンスZ行列と短絡アドミッタンスY行列を計算する前に、インピーダンス素子114からインピーダンス素子128の全ては、指定される基準特性インピーダンスZrefへ正規化される。一般に、基準特性インピーダンスは50オームとして指定される。開放インピーダンス行列と短絡アドミタンス行列によるSパラメータ行列Sは、下式で与えられる。

【0039】

【数15】

【0040】

【数16】

【0041】

ここで、Iは下式により規定される4行4列の単位行列である。

【0042】

【数17】

【0043】

整合回路網100を構成する各副回路部のSパラメータは、式15,式16から計算することができる。式1又は式2を用いることで、各構成回路のインピーダンス行列全体を解くことが可能である。式15あるいは式16で得られるインピーダンス行列を用いることで、構成回路の対応するSパラメータ行列を解くことが可能となる。エンベディング/ディエンベディング特許出願の教示を用いることで、2つのSパラメータ行列を組み合わせて、2つのデバイスの電気的な組み合わせに関するSパラメータ行列へ至ることが可能である。整合回路網100の単一の全体的Sパラメータ行列SMが割り出されるまで、この手順は全ての副回路部について繰り返される。整合回路網100に関して得られたSパラメータ行列SMは、インピーダンス行列やアドミッタンス行列と同じ基準特性インピーダンスへ正規化される。

【0044】

図5を具体的に参照するに、複数の平衡整合回路網100間にエンベディングした多ポート平衡デバイス500が図示してある。各平衡整合回路網100は、インピーダンス素子114からインピーダンス素子128に対し、異なる構成回路の選択を通じて異なるインピーダンス回路網とすることができる。平衡デバイス500をエンベディングした各整合回路網100は、固有の整合回路網Sパラメータ行列SMを有することとなろう。2001年9月18日出願の「複数端子不平衡又は平衡デバイスの線形特性解明方法及び装置」と題する米国特許出願第09/954,962号の教示は、米国仮特許出願第60/233,596号(596仮特許出願と呼ぶ)に基づく優先権を主張するものであり、ここに参照用に取り込むことにするが、そこには多ポート混在モードSパラメータの抽出方法が開示されている。本方法には、SDとして指定された多ポート標準デバイスSパラメータ行列を行列SDmmでもって指定された混在モードSパラメータとして知られる線形平衡パラメータへ変換することが含まれる。混在モードSパラメータSDmmは、デバイスの平衡ポートと不平衡ポートとの間の相互作用を規定する項をもたらす。596仮特許出願には、任意の多ポート純平衡回路構成あるいは任意の多ポート混在回路構成の不平衡パラメータと平衡パラメータを抽出するための一般的統一解が記述されている。596仮特許出願に開示された本方法は、差動モード挙動と同相モード挙動との間、差動挙動と不平衡挙動との間、および、差動モードの電気的挙動と同相モードの電気的挙動との間の相互作用だけでなく、純差動モードや純同相モードや純不平衡電気的挙動も含む多ポートデバイスの平衡ポートと不平衡ポートとの間の任意の結合を予測することができる。エンベディング/ディエンベディング特許出願の教示を用いることで、平衡デバイス500のSパラメータSDが既知である場合に、多ポート平衡デバイス500と複数の平衡整合回路網100の直列組み合わせのSパラメータを割り出すことが可能である。直列組み合わせから得られるSパラメータ行列の表示は、SCである。多ポート平衡デバイス500と複数の整合回路網100の直列組み合わせのSパラメータを割り出した後、得られたSパラメータSCは596仮特許出願の教示の利点とともに用い、直列組み合わせの混在モードSパラメータSCmmの抽出に用いることができる。混在モードSパラメータは、直列組み合わせの差動、同相、不平衡、混在モードの挙動の予測と解析に役立つ情報をもたらす。かくして、デバイスの線形Sパラメータと平衡整合回路網100のインピーダンスモデルから複数の平衡回路網100にエンベディングした平衡デバイスの電気的な組み合わせの混在モードSパラメータ行列を抽出することが可能となる。

【0045】

混在ポートデバイス、すなわち不平衡ポートと平衡ポートとの双方を有するデバイスの電気的挙動を予測する必要性もまた存在する。このケースは、本願明細書に示す一般的な解法の延長にある。図19を具体的に参照するに、混在ポートデバイス1900が図示してある。図示の如く、混在ポートデバイス1900は、デバイス1900の異なるポートに接続した平衡整合回路だけでなく不平衡回路もまた含むものである。最近の用途では、多数の混在ポートデバイスが存在する。実施例には、不平衡−平衡ラインバラン、フィルタ、3dB電力スプリッタ/カップラ、低温焼成セラミックデバイス、高性能マイクロプロセッサ部品、および、それらを支持する集積回路が含まれる。

【0046】

図20は、整合回路網2000の不平衡実施形態を例示するものである。不平衡整合回路網2000は、一般的な平衡整合回路網100の簡略版を含む。具体的には、図1から図4を参照するに、仮に平衡整合回路網100の第2の入力端子106と第2の出力端子112を接地電位端101に接続し、第2の分流接続点308と第2の直列接続点408と第4の直列接続点412もまた接地電位端101に接続したとすると、得られるのが図20に示す不平衡整合回路網2000である。図21から図23もまた、得られた構成不平衡インピーダンス変換素子2100と不平衡分流回路網2200と格子回路網2300を示す。当事者には言うまでもないことではあるが、基準電位端101に対し特定のノードを終端させることで、平衡構成に比べさらに簡単化されたインピーダンス線路が得られる。図21から図23に示す汎用素子は、図20に示す不平衡整合回路網回路構成の生成に用いられる。汎用平衡整合回路網100と同様、その用途に適当なものとして回路内に追加の並列インピーダンス素子及び直列インピーダンス素子を用いることで、不平衡整合回路網モデルの追加の実施形態が達成可能である。ここに教示する一般解の利点は、平衡整合回路網100と不平衡整合回路網2000のモデル化に生成される任意の回路構成にそれを適用できることにある。

【0047】

図20に示す不平衡整合回路網2000の実施形態は、第1の並列インピーダンス素子2002と第2の並列インピーダンス素子2004と第1の直列インピーダンス素子2006と第2の直列インピーダンス素子2008からなる。不平衡整合回路網2000のSパラメータを計算するため、構成副回路素子2001から構成副回路素子2008について開放インピーダンスと短絡アドミッタンスが計算される。

【0048】

図22の開放分流インピーダンス行列[Z]は、下式で与えられる。

【0049】

【数18】

【0050】

図23の短絡直列アドミタンス行列[Y]は、下式で与えられる。

【0051】

【数19】

【0052】

式18,式19を用いて副回路のインピーダンス行列あるいはアドミッタンス行列を割り出した後、式15,式16を用いて不平衡整合回路網2000を構成する各副回路のSパラメータを計算することができる。当事者には言うまでもないことであるが、この場合の式15,式16の行列の次元は2行2列である。エンベディング/ディエンベディング特許出願の教示を用いることで、2つの副回路の直列接続組み合わせのSパラメータを割り出すことができる。先に直列接続した回路と組み合わせた全ての副回路についてこの手順を複数回繰り返すことで、不平衡整合回路網2000全体に対する単一のSパラメータ行列を割り出すことができる。得られたSパラメータ行列は、構成部分の開放インピーダンス行列や短絡アドミッタンス行列と同じ基準特性インピーダンスへ正規化される。

【0053】

前述の如く、VNAは固定されたインピーダンス環境において、デバイスの特性試験を可能にする。しかしながら、50オーム環境はしばしばデバイスの実際の電気的インピーダンス環境を表わしはしない。一般に、各デバイスポートは他の全てのデバイスポートに接続されたインピーダンスとは異なる値を有するインピーダンスに接続される。デバイスが動作するインピーダンス環境により近いインピーダンス環境においてデバイスの特性を解明する能力が、より正確で信頼できる特性解明をもたらす。それ故に、特性を解明したデバイスの各ポートにおいてユーザが選択したインピーダンス値を有するデバイスの特性を解明する必要が存在する。本発明の教示により、1以上の不平衡整合回路網2000あるいは平衡整合回路網100と組み合わせた不平衡デバイス1900あるいは平衡デバイス500の直列接続組み合わせの電気的挙動が予測できるようになる。図2,図21を具体的に参照するに、それぞれ平衡インピーダンス変換素子202と不平衡インピーダンス変換素子2100が図示してある。インピーダンス変換素子の機能は、基準特性インピーダンスへ正規化されるSパラメータ行列を異なるインピーダンス値へ変更することにある。理想的には、回路設計者は基準インピーダンス値とは異なる整合インピーダンス値の正規化を随意確立することができる。デバイス500あるいはデバイス1900の各ポートをデバイス500あるいはデバイス1900の他のポート用に設定されたインピーダンスの正規化とは無関係なインピーダンスへ正規化することが、さらに望ましい。このインピーダンス変換を達成するには、不平衡整合回路網用に2行2列の行列演算が用いられ、平衡整合回路網用に4行4列の行列演算が用いられる。ここに記載した正規化公式は平衡回路構成用であり、それ故4行4列の行列演算が展開される。同じ定式化は、2行2列の行列演算を展開するケースを除き、不平衡のケースに用いることができる。

【0054】

平衡整合回路網100については、基準特性インピーダンスとは異なる特性インピーダンスへ正規化される4行4列のSパラメータ行列の解を、開放インピーダンス行列Zあるいは短絡アドミッタンス行列Yにより表わすことができる。異なる特性インピーダンスへ正規化した回路網インピーダンスの関数としてSパラメータを解く数式は、以下の通りである

【0055】

【数20】

【0056】

【数21】

【0057】

ここで、行列cは正規化行列である。

【0058】

正規化行列は、行添え字と列添え字の等しくない要素が零値を有するよう構成してある。正規化マトリックスの行添え字と列添え字が一致する場合は、行列要素は非零値を有する。従って、行列対角沿いにのみ値は非零とされる。非零値は、正規化対象各ポートについての特性インピーダンスの平方根に等しい。1つのポートについての正規化がそのままである場合、行列要素は基準特性インピーダンスZrefの平方根値を有する。かくして、ポートiを基準特性インピーダンスへではなく異なる特性インピーダンスへ正規化すべき場合は、ここで行i列iの行列要素の値は新たな特性インピーダンスの平方根√Z0iに一致する。ただし、iは正規化対象ポート数に等しい。それ故、2ポート平衡デバイスあるいは4端子不平衡デバイス用の任意のインピーダンス正規化行列cは、下式により与えられる。

【0059】

【数22】

【0060】

全ポートを基準インピーダンスへ正規化すべき場合、そこでは正規化行列の対角沿いの全ての値は値√Zrefを有する。この場合、基準特性正規化行列は行列crefであり、以下の如く2ポート平衡デバイス用に規定される。

【0061】

【数23】

【0062】

基準特性正規化マトリックスcrefへ正規化するSパラメータ行列は、Srefである。行列Sは、任意のインピーダンス正規化行列cへ正規化するSパラメータ行列として規定される。正規化Sパラメータ行列Sref,Sは共に、同じ開放インピーダンスあるいは短絡アドミッタンスを有する。Sパラメータは、特性インピーダンスの正規化に依存する。しかしながら、異なる特性インピーダンスへ正規化したSパラメータが、各Sパラメータ行列に対応して開放インピーダンスあるいは短絡アドミッタンスを変更することはない。従って、基準特性インピーダンスへ正規化したSパラメータ行列と任意の特性インピーダンスへ正規化したSパラメータ行列との双方から計算したインピーダンス行列は、互いに等価である。

【0063】

式20,式21から、インピーダンス行列とアドミッタンス行列はSパラメータ行列と正規化行列の関数として表わすことができる。すなわち、

【0064】

【数24】

【0065】

【数25】

【0066】

である。Sパラメータ行列の正規化処理が開放インピーダンスZや短絡アドミッタンスYのいずれも変更しないので、そこで2つの異なる正規化ケースに対し同じ式を適用することが可能である。正規化に関係なくインピーダンス行列とアドミッタンス行列の等価原理を用いることで、基準特性インピーダンスや基準正規化行列crefや任意の正規化行列cへ正規化したSパラメータ行列の関数として任意の正規化を用いてSパラメータ行列について解くことが可能となる。一例として式24を用い、基準特性インピーダンスSrefへ正規化したSパラメータ行列の関数としても、任意のインピーダンス行列Sへ正規化したSパラメータ行列の関数としても、その両方でインピーダンス行列Zは確立される。従って、

【0067】

【数26】

【0068】

【数27】

【0069】

となる。等価原理を用いることで、Zについての等式は互いに等値に設定することができる。すなわち、

【0070】

【数28】

【0071】

である。Sパラメータ行列Sについて解くことで、

【0072】

【数29】

【0073】

が得られる。ただし、

【0074】

【数30】

【0075】

アドミタンス行列を用い、式26から式29で表わされる同じ原理に従って下式を適用する。

【0076】

【数31】

【0077】

【数32】

【0078】

等価原理を用いることで、Yについての等式は互いに等値設定することができる。すなわち、

【0079】

【数33】

【0080】

である。Sパラメータ行列について解くことで、

【0081】

【数34】

【0082】

が得られる。ただし、

【0083】

【数35】

【0084】

かくして、本発明の教示を用いることで、平衡デバイスと不平衡デバイスの直列合成あるいは1以上の整合回路網をもった両種ポートを備えるデバイスについてのSパラメータを、基準特性インピーダンスあるいは任意のインピーダンスのどちらかで予測することができる。

【0085】

コンピュータの処理、記憶、グラフィカルユーザインタフェース能力を含む一実施形態において、本発明の教示を実装することは有益である。図24を具体的に参照することで、図1に例示するような平衡回路網100の整合は、図5の平衡デバイス500の設計者に図式的に提示することができる。デバイス500の各平衡ポートは、たとえ一般的な回路構成表現が同様であるにしても、異なる平衡整合回路網100に接続することができる。具体的には、図6から図18の回路構成は、他同様、グラフィカルユーザインタフェースをもって設計者に視覚的に提示することができる。以降、グラフィカルユーザインタフェースを「GUI」と称する。加えて、開放や短絡をインピーダンス素子として表現することもできる。コンピュータ上のソフトウェアにより、設計者は回路構成のうちの1つを「クリック」し、それを平衡整合回路網のうちの一回路網の中の1以上のインピーダンス素子へ「ドロップ」することができる。1以上の整合回路網が、平衡デバイス及び混在ポートデバイスの設計者に対しGUIで表わすことができる。コンピュータ上のソフトウェアにより、設計者は図6から図18に示す回路構成のうちの一つを「クリック」し、それを選択し、選択した回路構成をそこで不平衡あるいは平衡整合回路網のうちの1つの1以上のインピーダンス素子へ「ドロップ」できるようになる。図24のステップ2402を具体的に参照するに、この「クリック及びドロップ」の処理は、平衡整合回路網100あるいは不平衡整合回路網2000を構成する全てのインピーダンス素子がインピーダンス値を有する回路により規定されるまで繰り返される。また、処理の一端として、抵抗やインダクタンスや容量やQ値や動作周波数などの各電気回路用の値を適当に割り当てることもできる。このステップは、参照符号114から参照符号128あるいは参照符号2002から参照符号2008で示すそれらのインピーダンス素子Z1からインピーダンス素子Z14及びインピーダンス変換素子202,インピーダンス変換素子2001による全ての整合回路網100,整合回路網2000の表現にて完了する。ステップ2404を具体的に参照することで、全ての平衡整合回路網100あるいは不平衡整合回路網2000がそれらの構成回路をもって規定された時点で、コンピュータのプロセッサは以下の式1又は式2,式3から式11から開放複素インピーダンス行列Zあるいは短絡複素アドミッタンス行列Yの計算が可能となる。インピーダンス行列Zあるいはアドミッタンス行列Yから、プロセッサは基準特性インピーダンスにて整合回路網の関連SパラメータSMを算出することが可能である。ステップ2406を具体的に参照するに、基準特性インピーダンスにおける平衡デバイス500のSパラメータSDの入手もまた可能である。デバイスのSパラメータSDは、デバイス500のモデル及び期待されるSパラメータの計算を通じ、あるいは実際のデバイスのSパラメータの測定値を通じ、あるいは本処理による検索向けに保存した適当なデバイスSパラメータを有するコンピュータがアクセス可能なデータファイルから入手することができる。ステップ2408を具体的に参照し、エンベディング/ディエンベディング特許出願の教示を用いるに、プロセッサは平衡デバイス500及び平衡整合回路網100の直列組み合わせのSパラメータSCの計算が可能である。所望とあらば、式20又は式21を用い、プロセッサはデバイス500と整合回路網100,2000を組み合わせたデバイスの各ポートについて任意の特性インピーダンスにて正規化した直列接続Sパラメータを計算することもできる。ステップ2410を具体的に参照するに、596仮特許出願の教示の利点を用い、ここでプロセッサは得られたSパラメータ行列SCの混在モードSパラメータSCmmを抽出し、複数の整合回路網100,2000内にエンベディングした平衡デバイス500の電気的挙動の予測を支援することが可能となる。図24に例示し、上記に開示す平衡型の場合のソフトウェアによる実装は、不平衡型で混在ポートの場合にも適用し用いることができる。本発明の教示による方法の実施形態は、Microsoft Visual Studio 6.0,Roguewave Stringray Studio, Roguewave Math H++及びVictor Imaging Processing Libraryの両ソフトウェアパッケージを搭載したマイクロソフト社ウインドウズ動作環境を備えるパーソナルコンピュータを用い実装することができる。

【0086】

以上説明した本発明の実施の形態は、特許請求の範囲に記載した本発明の説明のための一実施形態にすぎず、特許請求の範囲で示した権利範囲内において種々の変形を行うことができることは、当業者にとって明らかである。最後に、本発明の広汎な応用の可能性に鑑み、本発明の実施態様の幾つかを以下に示す。

【0087】

(実施態様1)

デバイス(500,1900)の電気的挙動を予測するシステムであって、

演算処理手段と、

平衡入力ポート(102)および平衡出力ポート(108)を有する少なくとも1つの平衡整合回路網(100)を表現する手段と、

前記平衡出力ポート(108)と前記デバイス(500)の平衡ポートとの間の前記少なくとも1つの整合回路網の接続を表現する手段と、

整合回路網Sパラメータ行列SMを計算する手段と、

デバイスSパラメータ行列SDを求める手段と、

前記デバイス(500)と組み合わせた前記整合回路網(100)についての直列接続Sパラメータ行列SCを計算する手段と、

前記直列接続Sパラメータ行列から混在モード直列接続SパラメータSCmmを抽出する手段と、

を備えることを特徴とするシステム。

【0088】

(実施態様2)

少なくとも1つの整合回路網(100)の前記表現手段は、さらに、分流回路網(302)と格子回路網(402)の組み合わせをもって、前記少なくとも1つの整合回路網を表現する手段を備える、

ことを特徴とする実施態様1に記載のシステム。

【0089】

(実施態様3)

前記表現手段は、さらに、インピーダンス変換素子(202)を有する前記少なくとも1つの整合回路網(100)を表現する手段を備える、

ことを特徴とする実施態様2に記載のシステム。

【0090】

(実施態様4)

前記少なくとも1つの整合回路網(100)は、平衡インピーダンス変換素子(202)と、第1の分流回路網(114,116,117)と、第1の格子回路網(118〜121)と、第2の分流回路網(122〜124)と、第2の格子回路網(125〜128)との直列接続組み合わせを備え、

前記各分流回路網は、第1と第2の分流接続点(306,308)間の並列インピーダンス素子(304)と、それぞれ前記第1と第2の分流接続点(306,308)間の第1及び第2の分流インピーダンス素子(322,324)と、基準電位端(101)を具備し、

前記格子回路網は、第1と第3の格子接続点(406,410)間の第1の直列インピーダンス素子(404)と、前記第2と第4の格子接続点(408,412)間の第2の直列インピーダンス素子(414)と、前記第1と第4の格子接続点(406,412)間の第1の交差インピーダンス素子(422)と、前記第2と第3の格子接続点(408,410)間の第2の交差インピーダンス素子(420)とを具備し、

前記システムは、対応する整合回路網Sパラメータ行列SMを計算する手段と、前記整合回路網100と電気的に組み合わせた前記デバイス(500)の少なくとも1つのポートの特性を解明する手段とを備える、

ことを特徴とする実施態様1乃至実施態様3のいずれかに記載のシステム。

【0091】

(実施態様5)

前記整合回路網Sパラメータ行列の計算手段はさらに、前記第1の分流回路網及び第2の分流回路網について開放インピーダンス行列Zを計算する手段と、前記第1及び第2の格子インピーダンス回路網について短絡アドミッタンス行列Yを計算する手段と、前記整合回路網についてインピーダンス行列を計算する手段と、前記インピーダンス行列を前記整合回路網Sパラメータ行列へ変換する手段を備える、

ことを特徴とする実施態様2乃至実施態様4のいずれかに記載のシステム。

【0092】

(実施態様6)

さらに、前記直列接続Sパラメータ行列SCを任意の特性インピーダンスへ正規化する手段を備える、

ことを特徴とする実施態様5に記載の前記システム。

【0093】

(実施態様7)

さらに、前記直列接続Sパラメータ行列から多ポート混在モードSパラメータを抽出する手段を備える、

ことを特徴とする実施態様1乃至実施態様6のいずれかに記載の前記システム。

【0094】

(実施態様8)

さらに、前記デバイス(1900)の少なくとも1つの不平衡ポートと電気的に組み合わせた少なくとも1つの不平衡整合回路網(2000)を表現する手段を備える、

ことを特徴とする実施態様1乃至実施態様7のいずれかに記載の前記システム。

【0095】

(実施態様9)

前記デバイスは複数の平衡ポート有し、

前記システムは、前記平衡整合回路網(100)の表現と整合回路網Sパラメータ行列SMの計算を繰り返す手段をさらに備える、

ことを特徴とする実施態様1乃至実施態様9のいずれかに記載の前記システム。

【0096】

(実施態様10)

前記正規化手段は、前記整合回路網を異なる特性インピーダンス値へ正規化する、

ことを特徴とする実施態様9に記載の前記システム。

【図面の簡単な説明】

【図1】本発明の教示になる平衡整合回路網の一実施形態を表わす図である。

【図2】平衡インピーダンス変換素子を表わす図である。

【図3】分流回路網素子を表わす図である。

【図4】格子回路網素子を表わす図である。

【図5】2N個の平衡デバイスポートを有し、複数の平衡整合回路網中にエンベディングした平衡デバイスを表わす図である。

【図6】図1の整合回路網と併用可能な回路素子の一例を示す図である。

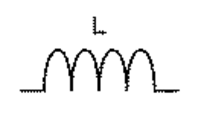

【図7】図1の整合回路網と併用可能な回路素子の一例を示す図である。

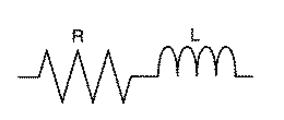

【図8】図1の整合回路網と併用可能な回路素子の一例を示す図である。

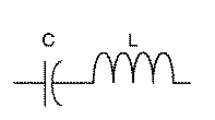

【図9】図1の整合回路網と併用可能な回路素子の一例を示す図である。

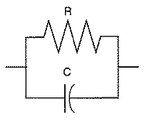

【図10】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図11】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図12】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図13】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図14】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図15】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図16】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図17】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図18】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図19】不平衡整合回路網と平衡整合回路網をそれぞれ組み合わせた不平衡デバイスポート及び平衡デバイスポートを有するデバイスのモデルを例示する図である。

【図20】本発明の教示になる不平衡整合回路網の一実施形態を表わす図である。

【図21】不平衡インピーダンス変換素子を表わす図である。

【図22】不平衡分流回路網素子を表わす図である。

【図23】直列インピーダンス素子へ簡約した不平衡格子回路網素子を表わす図である。

【図24】本発明の教示を利用する方法の一実施形態を表わすフローチャートである。

【符号の説明】

100 平衡整合回路網

101 共通電位端

102 平衡入力ポート

104 第1の入力端子

106 第2の入力端子

108 平衡出力ポート

110 第1の出力ポート

112 第2の出力ポート

114〜128 インピーダンス素子

202 平衡インピーダンス変換素子

204 平衡インピーダンス変換入力ポート

206 平衡インピーダンス変換出力ポート

302 平衡2ポート分流回路網

304 並列インピーダンス素子

306 第1の分流接続点

308 第2の分流接続点

310 第1の入力端子

312 第2の入力端子

314 第1の出力端子

316 第2の出力端子

318 第1の平衡入力ポート

320 第2の平衡出力ポート

322 第1の分流インピーダンス素子

324 第2の分流インピーダンス素子

402 平衡2ポート格子回路網

404 第1の直列インピーダンス素子

406 第1の格子回路網接続点

408 第2の格子回路網接続点

410 第3の格子回路網接続点

412 第4の格子回路網接続点

414 第2の直列インピーダンス素子

416 平衡入力端

418 平衡出力ポート

420 第2の交差インピーダンス素子

422 第1の交差インピーダンス素子

500,1900 デバイス

2000 不平衡整合回路網

2002 第1の並列インピーダンス素子

2004 第2の並列インピーダンス素子

2006 第1の直列インピーダンス素子

2008 第2の直列インピーダンス素子

2100 不平衡インピーダンス変換素子

2300 格子回路網

【発明の属する技術分野】

本発明は、平衡デバイスポートを有する多ポートデバイスの電気的挙動を予測するシステムに関する。

【0002】

【従来の技術】

ディジタル電子機器のためのデータ転送速度は、無線通信や有線通信の全ての分野で増加している。従って、ビデオや高品位テレビ(HDTV)やグラフィックスやシリアルインターフェースや他の多くのアプリケーション向けのディジタルデータストリームは、より高い帯域を必要としている。ディジタルデータの転送速度の増加はインターネットの成長する人気に一部起因するものであり、チップや機能ボードやシステムの間の高速相互接続を必要としている。当事者には言うまでもないが、データはディジタルであっても、ディジタルデータがそこに沿って移動する伝送媒体はアナログである。

【0003】

帯域の増加は、雑音源に対しディジタル通信回路がより影響を受け易くする。より高いデータ伝送速度を達成するため、電子回路は電磁障害に対する不感応性を改善し、偶数次高調波を抑制でき、非理想的接地に対しより高い許容範囲を持つようにせねばならない。平衡伝送型の回路構成の使用は、前記事項の達成に役立つ。従って、平衡伝送型の回路構成は過去に比べより一般的になっている。用語「平衡回路構成」に精通した当事者には、それが電気信号をデバイスの単一平衡ポート(シングル・バランスド・ポート)へ給送する、適当に結合された2つの導体線路の存在を意味することは言うまでもないことである。2つの端子がデバイスの単一平衡ポート(シングル・バランスド・ポート)を形成するのは、各端子を被結合導体の一方へ接続した場合である。ここで使用する用語「デバイス」は、電気的挙動を呈する任意のデバイスあるいは回路を指す。平衡デバイスの解析は、デバイスの標準Sパラメータを混在モードSパラメータに変換することで達成することができる。混在モードSパラメータは、平衡構造内を伝搬する差動モード信号と同相モード信号を記述するものである。2つの被結合導体を互いに180度位相をずらし同振幅でもって駆動したときに、差動モードが発生する。2つの被結合導体が同相同振幅を有するときに、同相モードが発生する。平衡構造内の理想的な信号は、純差動モードである。差動モードが有利であるのは、被結合導体上の電圧が「1」を表わしかつ反対極性を有する場合に、高速ディジタル差動受信器が不平衡の場合よりも大電圧を発生し、ディジタル値「1」を表わすからである。同様に、被結合導体上の電圧が「0」を表わしかつ反対極性を有する場合は、差動受信器は不平衡の場合よりも小電圧を発生し、ディジタル値「0」を表わす。平衡回路構成において導体を結合する目的は、接地面の戻り線路内で発生する雑音などのあらゆる同相モード信号が両導体上で同振幅同位相に見えるようになし、ディジタル差動受信器でキャンセルすることにある。

【0004】

不平衡の回路構成を有するデバイスのディジタル設計者が用いる幾つかのツールキットの一部として試験、測定、解析の各手法が開発され、1つのモデルに基づくデバイスや素子の多数相互接続からなるデバイスの電気的挙動の予測に役立っている。デバイス設計を準備した後、設計者は新規に設計したデバイスの電気的挙動を数学的に予測し、そのデバイスにとっての所望性能仕様に対しそれを比較することが可能となる。場合によっては、予測された電気挙動は所望の性能仕様を満たさず、それ故にデバイスを設計しようとしているニーズに応えないことがある。こうした場合、電子設計者は新規設計デバイスを試作しないことを選択し、所望の予測挙動が得られるようデバイスの再設計へと進む。期待性能を満たさないデバイスの試作ステップの排除は、無駄な努力と経費を排し、より性能の良好な製品の市場への投入時間を改善するのに役立つ。

【0005】

ここで「ディエンベディング/エンベディング・アプリケーションノート」と呼ぶ非特許文献1には、「ディエンベディング(除去)」と名付けた方法が開示されている。ディエンベディング手法は、2つのアダプタを直列接続(カスケード接続)したデバイスの測定値と2つのアダプタ自体の測定値からのデバイスのSパラメータを割り出すのに用いられる。ディエンベディング/エンベディング・アプリケーションノートには、モデル化デバイスの電気的挙動を予測する「エンベディング」と名付けた方法もまた開示されている。エンベディング処理では、デバイスのSパラメータと2つのアダプタのSパラメータとの組み合わせがアダプタとの電気的な組み合わせにおけるデバイスの挙動を予測するのに役立つ。エンベディング処理に使用するSパラメータはディエンベディング処理から入手するか、あるいは回路のモデル化と関連Sパラメータの計算を通じて入手することができる。エンベディング及びディエンベディング手法の使用が、コンピュータ支援設計(CAD)ツールと電子デバイス設計者ツールキットの測定ツールとの間の重要なリンクをもたらす。

【0006】

【非特許文献1】

「ベクトル・ネットワーク・アナライザを使用したSパラメータ・ネットワークのディエンベディング及びエンベディング」,アプリケーションノート1364−1,アジレントテクノロジーズ・インク,2000年11月

【0007】

【発明が解決しようとする課題】

ディエンベディング/エンベディング・アプリケーションノートにて教示されるエンベディング手法の1つの限界は、教示用途が不平衡デバイスに向けられたものであることである。従来技術は平衡デバイスに適用できる手法を提供しておらず、しかも電子設計分野の平衡デバイスの使用は増えつつある。それ故、平衡デバイスや平衡回路に適用可能なエンベディング手法に対する要求が存在する。

【0008】

平衡と不平衡のデバイスポートを両方有するデバイスや回路の使用もまた、より一般的になっている。両ポート様式を有するデバイスや回路を、本願明細書では「混在ポートデバイス」と呼ぶことにする。用語「デバイス」がデバイスと回路を指すことは理解されたい。混在ポートデバイスでは、不平衡デバイスポートと平衡ポートが平衡回路構成と不平衡回路構成のインタフェースとなり、不平衡回路構成と平衡回路構成を単一作動システムとして併せ一体化してあるのが普通である。それ故、混在ポートデバイスだけでなく純平衡デバイスも併せ電気的な挙動を予測する方法に対する要求が存在する。

【0009】

多くの平衡回路構成では、デバイスを整合回路網内にエンベディングしたときに、ユーザはその電気的挙動を予測することを欲する。一般に、モデル測定値すなわちSパラメータ測定値は、整合回路網を表す。ベクトル回路網解析器は、線形デバイスのSパラメータを測定する。ベクトル回路網解析器を、ベクトル・ネットワーク・アナライザとも称され、以降、VNAと略称する。大半の市販のVNAは50オーム標準に校正してあるため、測定したSパラメータSDは50オーム特性インピーダンスへ正規化される。Sパラメータ行列SDは、それ故に特性インピーダンスの関数となる。平衡フィルタのような一部の平衡デバイスは、不平衡デバイスポート向けの従来の50オームや平衡ポート向けの従来の100オーム以外の特性インピーダンスへの正規化を必要とする。その上、デバイスインピーダンスの正規化は、ポートごとに異なることもある。多くの商用電子設計自動化ソフトウェアパッケージは、モデルにより表わされる不平衡整合回路網のモデル化へ利用可能で、ユーザが指定したインピーダンスへモデルを正規化できるようにしてある。平衡混在ポート型の回路構成に関し、この種の市販のソフトウェアパッケージは一切存在しない。それ故、任意のインピーダンス値への正規化を可能にする純差動混在ポートデバイスのエンベディング手法に対する要求が存在する。

【0010】

【課題を解決するための手段】

本発明は、上記課題を解決したものであり、デバイスの電気的挙動を予測するシステムであって、演算処理手段と、平衡入力ポートおよび平衡出力ポートを有する少なくとも1つの平衡整合回路網を表現する手段と、前記平衡出力ポートと前記デバイスの平衡ポートとの間の前記少なくとも1つの整合回路網の接続を表現する手段と、整合回路網Sパラメータ行列SMを計算する手段と、デバイスSパラメータ行列SDを求める手段と、前記デバイスと組み合わせた前記整合回路網についての直列接続Sパラメータ行列SCを計算する手段と、前記直列接続Sパラメータ行列から混在モード直列接続SパラメータSCmmを抽出する手段と、を備えることを特徴とする。

【0011】

【発明の実施の形態】

整合回路や整合回路網は、デバイスに現われるインピーダンスを記述する電気的モデルを表す。本発明の教示は、デバイスと組み合わせて表わされる特定の整合回路の仕様をもたらすものである。図1を具体的に参照するに、第1の入力端子104と第2の入力端子106とを含む平衡入力ポート102、および、第1の出力ポート110と第2の出力ポート112とを含む平衡出力ポート108を有する整合回路網100が図示してある。整合回路網100は、平衡入力ポート102と平衡出力ポート108との間のインピーダンスを表す一般的な回路モデルの一実施形態である。図1に示す整合回路網100の実施形態は、三つの異なる副回路の電気的組み合わせを備える。各副回路は、個別の不平衡入力ポートと不平衡出力ポートをもって表わしてある。

【0012】

従来のVNAは、固定インピーダンス環境下でデバイスのパラメータを測定する。一般に、固定インピーダンス環境は全ての被測定デバイスポートについて50オームであり、「基準特性インピーダンス」と呼ばれる。被測定デバイスの各ポートに対し、任意のインピーダンスの選択を可能にすることが望ましい。第1の副回路部はインピーダンス変換素子202であり、図2に図示してある。インピーダンス変換素子202は、平衡インピーダンス変換入力ポート204におけるインピーダンスを平衡インピーダンス変換出力ポート206における異なるインピーダンスへ変換する平衡2ポート回路素子の理想的モデルである。

【0013】

第2の副回路部は、図3に示す一般的な平衡2ポート分流回路網302である。分流回路網302は、第1の分流接続点306と第2の分流接続点308との間に配設した並列インピーダンス素子304を含む。第1の分流接続点306は、第1の入力端子310と第1の出力端子314とに共通である。第2の分流接続点308は、第2の入力端子312と第2の出力端子316とに共通である。第1の入力端子310と第2の入力端子312は、分流回路網302用の第1の平衡入力ポート318を構成している。第1の出力端子314と第2の出力端子316は、分流回路網302用の第2の平衡出力ポート320を構成している。一般的な分流回路網320は、また、第1の分流接続点306と共通電位端101との間に電気的に配設した第1の分流インピーダンス素子322、および、第2の分流接続点308と共通電位端101との間に電気的に配設した第2の分流インピーダンス素子324を含む。当事者には言うまでもないが、この種のモデルを用いたときに、どんなインピーダンス素子も短絡回路あるいは開放回路のどちらかとして一般化することができる。

【0014】

第3の副回路部は、図4に示す一般的な平衡2ポート格子回路網402である。格子回路網402は、第1の格子回路網接続点406と第3の格子回路網接続点410との間に第1の直列インピーダンス素子404を備える。格子回路網402はまた、第2の格子回路網接続点408と第4の格子回路網接続点412との間に第2の直列インピーダンス素子414を備える。第1の格子回路網接続点406と第2の格子回路網接続点408は、格子回路網402の平衡入力ポート416を構成する。第3の格子回路網接続点410と第4の格子回路網接続点412は、格子回路網402の平衡出力ポート418を構成する。一般的な格子回路網402は、第1の交差インピーダンス素子422と第2の交差インピーダンス素子420を備える。第1の交差インピーダンス素子422は、第1の格子回路網接続点406と第4の格子回路網接続点412との間に電気的に配設される。第2の交差インピーダンス素子420は、第2の格子回路網接続点408と第3の格子回路網接続点410との間に電気的に配設される。当事者には言うまでもないが、この種のモデルを用いたときにどんなインピーダンス素子も短絡回路あるいは開放回路のどちらかとして一般化することができる。

【0015】

図1に示す整合回路網実施形態は、1つのインピーダンス変換素子202、および、1つの分流回路網302と1つの格子回路網402との組み合わせからなる2つの回路を備える。図1は、平衡入力ポート102と平衡出力ポート108の間のインピーダンスを表す一般的な回路の一実施形態を表わす。より複雑な整合回路は、必要数の追加の分流回路網と格子回路網を含む組み合わせ回路として表わすことができよう。

【0016】

図5を具体的に参照するに、平衡回路構成を有する多ポートデバイス500が図示してある。デバイス500は、図1に例示す平衡整合回路網100と同様の構造を有する複数の平衡整合回路網内にエンベディングしてある。本発明の開示は、「複数の装置ポートを有する装置の特性を解明する方法及び機器」と題し、2002年3月14日に出願した米国特許出願第10/098,040号の利点と併せ、複数の平衡整合回路網100中にエンベディングした多ポートデバイス500のSパラメータの予測を可能にする。以降、米国特許出願第10/098,040号を「エンベディング/ディエンベディング特許出願」と呼ぶ。エンベディング/ディエンベディング特許出願は、その教示を本願明細書中に参照用に取り込むものであるが、2Nポートアダプタが接続されるNポートデバイスの挙動を予測する方法が教示されている。この教示は、デバイスとデバイスに接続されるアダプタの分散パラメータ(Sパラメータ)が既知であるときに、2つのデバイスあるいは回路を直列接続したものの電気的挙動の予測方法を示している。得られるのは、直列接続Sパラメータ行列SCである。

【0017】

エンベディング/ディエンベディング特許出願の教示を用いるため、SMで表わされる整合平衡回路網のそれぞれのSパラメータを入手する。図3を具体的に参照するに、Z1は第1の分流インピーダンス素子322の複素インピーダンスを表わし、Z2は並列インピーダンス素子304の複素インピーダンスを表わし、Z3は第2の分流インピーダンス素子324の複素インピーダンスを表わす。従って、分流器回路網302の開放インピーダンス行列Zは、下記となる。

【0018】

【数1】

【0019】

図4を具体的に参照するに、Z4は第1の直列インピーダンス素子404の複素インピーダンスを表わす。Z7は第2の直列インピーダンス素子414の複素インピーダンスを表わす。Z5は、第1の交差インピーダンス素子422の複素インピーダンスを表す。Z6は、第2の交差インピーダンス素子420の複素インピーダンスを表す。従って、格子回路網402の短絡アドミタンス行列Yは、下記となる。

【0020】

【数2】

【0021】

図1に示す整合回路網の各分流インピーダンス素子や各直列インピーダンス素子や各交差インピーダンス素子は、多数の回路のうちの任意の1つとすることができる。実施例としてかつ例示のみを目的に、より一般的な回路構成の一部が図6から図14に図示してある。平衡回路構成の設計者は、インピーダンス素子114からインピーダンス素子128のそれぞれを整合回路網100のモデルをもって表現することを選択する。図6から図14に示す各回路は、それらの複素インピーダンスによって表わすことができる。従って、整合回路網100の構成部分であるインピーダンス素子114からインピーダンス素子128のそれぞれは、インピーダンスの実数部成分とインピーダンスの虚数部成分とにより数学的に表わすことができる。図6から図14に示す各複素インピーダンスの実数部成分と虚数部成分は、それぞれ式3から式11をもって記述される。

【0022】

【数3】

【0023】

【数4】

【0024】

【数5】

【0025】

【数6】

【0026】

【数7】

【0027】

【数8】

【0028】

【数9】

【0029】

【数10】

【0030】

【数11】

【0031】

ここで、Rはオーム単位の抵抗値を表わし、Lはヘンリー単位のインダクタンス値を表わし、Cはファラッド単位の容量値を表わし、w=2πfである。ここで、πは定数であり、fはヘルツ単位の動作周波数を表わす。より多くの複素インピーダンス素子が、図6から図14により与えられる一般的な回路構成の直列接続あるいは並列接続から構成することができる。一例として、図15に示す回路は図8に示す回路と図9に示す回路とを並列合成して構成したものである。図16に示す回路は、図7に示す回路と図10に示す回路とを並列合成して構成したものである。図17に示す回路は、図6に示す回路と図11に示す回路とを並列合成して構成したものである。図18に示す回路は、図6に示す回路と図7に示す回路と図8に示す回路とを直列合成して構成したものである。図6から図18に表す全ての回路の複素インピーダンス特性は、ソフトウェアライブラリに保存することができる。回路設計者が適当な整合回路網100を確立するときに、従来の「クリックとドロップ」の手法を用いてライブラリから特定の回路構成を入手し、整合回路網向け一般モデルへ挿入することができる。整合回路網についての全構成インピーダンスを選択すると、対応する全インピーダンスを計算することができる。

【0032】

複素インピーダンス成分を有する各回路にとって、誘導リアクタンスや容量リアクタンスのQ値と周波数とが特定された場合、そこで等価抵抗を計算し、インピーダンス素子へ代入することができる。インダクタの等価直列抵抗RQLは、下式で与えられる。

【0033】

【数12】

【0034】

コンデンサの等価直列抵抗RQCは、下式で与えられる。

【0035】

【数13】

【0036】

コンデンサの等価並列抵抗RQCは、下式で与えられる。

【0037】

【数14】

【0038】

図1を具体的に参照するに、開放インピーダンスZ行列と短絡アドミッタンスY行列を計算する前に、インピーダンス素子114からインピーダンス素子128の全ては、指定される基準特性インピーダンスZrefへ正規化される。一般に、基準特性インピーダンスは50オームとして指定される。開放インピーダンス行列と短絡アドミタンス行列によるSパラメータ行列Sは、下式で与えられる。

【0039】

【数15】

【0040】

【数16】

【0041】

ここで、Iは下式により規定される4行4列の単位行列である。

【0042】

【数17】

【0043】

整合回路網100を構成する各副回路部のSパラメータは、式15,式16から計算することができる。式1又は式2を用いることで、各構成回路のインピーダンス行列全体を解くことが可能である。式15あるいは式16で得られるインピーダンス行列を用いることで、構成回路の対応するSパラメータ行列を解くことが可能となる。エンベディング/ディエンベディング特許出願の教示を用いることで、2つのSパラメータ行列を組み合わせて、2つのデバイスの電気的な組み合わせに関するSパラメータ行列へ至ることが可能である。整合回路網100の単一の全体的Sパラメータ行列SMが割り出されるまで、この手順は全ての副回路部について繰り返される。整合回路網100に関して得られたSパラメータ行列SMは、インピーダンス行列やアドミッタンス行列と同じ基準特性インピーダンスへ正規化される。

【0044】

図5を具体的に参照するに、複数の平衡整合回路網100間にエンベディングした多ポート平衡デバイス500が図示してある。各平衡整合回路網100は、インピーダンス素子114からインピーダンス素子128に対し、異なる構成回路の選択を通じて異なるインピーダンス回路網とすることができる。平衡デバイス500をエンベディングした各整合回路網100は、固有の整合回路網Sパラメータ行列SMを有することとなろう。2001年9月18日出願の「複数端子不平衡又は平衡デバイスの線形特性解明方法及び装置」と題する米国特許出願第09/954,962号の教示は、米国仮特許出願第60/233,596号(596仮特許出願と呼ぶ)に基づく優先権を主張するものであり、ここに参照用に取り込むことにするが、そこには多ポート混在モードSパラメータの抽出方法が開示されている。本方法には、SDとして指定された多ポート標準デバイスSパラメータ行列を行列SDmmでもって指定された混在モードSパラメータとして知られる線形平衡パラメータへ変換することが含まれる。混在モードSパラメータSDmmは、デバイスの平衡ポートと不平衡ポートとの間の相互作用を規定する項をもたらす。596仮特許出願には、任意の多ポート純平衡回路構成あるいは任意の多ポート混在回路構成の不平衡パラメータと平衡パラメータを抽出するための一般的統一解が記述されている。596仮特許出願に開示された本方法は、差動モード挙動と同相モード挙動との間、差動挙動と不平衡挙動との間、および、差動モードの電気的挙動と同相モードの電気的挙動との間の相互作用だけでなく、純差動モードや純同相モードや純不平衡電気的挙動も含む多ポートデバイスの平衡ポートと不平衡ポートとの間の任意の結合を予測することができる。エンベディング/ディエンベディング特許出願の教示を用いることで、平衡デバイス500のSパラメータSDが既知である場合に、多ポート平衡デバイス500と複数の平衡整合回路網100の直列組み合わせのSパラメータを割り出すことが可能である。直列組み合わせから得られるSパラメータ行列の表示は、SCである。多ポート平衡デバイス500と複数の整合回路網100の直列組み合わせのSパラメータを割り出した後、得られたSパラメータSCは596仮特許出願の教示の利点とともに用い、直列組み合わせの混在モードSパラメータSCmmの抽出に用いることができる。混在モードSパラメータは、直列組み合わせの差動、同相、不平衡、混在モードの挙動の予測と解析に役立つ情報をもたらす。かくして、デバイスの線形Sパラメータと平衡整合回路網100のインピーダンスモデルから複数の平衡回路網100にエンベディングした平衡デバイスの電気的な組み合わせの混在モードSパラメータ行列を抽出することが可能となる。

【0045】

混在ポートデバイス、すなわち不平衡ポートと平衡ポートとの双方を有するデバイスの電気的挙動を予測する必要性もまた存在する。このケースは、本願明細書に示す一般的な解法の延長にある。図19を具体的に参照するに、混在ポートデバイス1900が図示してある。図示の如く、混在ポートデバイス1900は、デバイス1900の異なるポートに接続した平衡整合回路だけでなく不平衡回路もまた含むものである。最近の用途では、多数の混在ポートデバイスが存在する。実施例には、不平衡−平衡ラインバラン、フィルタ、3dB電力スプリッタ/カップラ、低温焼成セラミックデバイス、高性能マイクロプロセッサ部品、および、それらを支持する集積回路が含まれる。

【0046】

図20は、整合回路網2000の不平衡実施形態を例示するものである。不平衡整合回路網2000は、一般的な平衡整合回路網100の簡略版を含む。具体的には、図1から図4を参照するに、仮に平衡整合回路網100の第2の入力端子106と第2の出力端子112を接地電位端101に接続し、第2の分流接続点308と第2の直列接続点408と第4の直列接続点412もまた接地電位端101に接続したとすると、得られるのが図20に示す不平衡整合回路網2000である。図21から図23もまた、得られた構成不平衡インピーダンス変換素子2100と不平衡分流回路網2200と格子回路網2300を示す。当事者には言うまでもないことではあるが、基準電位端101に対し特定のノードを終端させることで、平衡構成に比べさらに簡単化されたインピーダンス線路が得られる。図21から図23に示す汎用素子は、図20に示す不平衡整合回路網回路構成の生成に用いられる。汎用平衡整合回路網100と同様、その用途に適当なものとして回路内に追加の並列インピーダンス素子及び直列インピーダンス素子を用いることで、不平衡整合回路網モデルの追加の実施形態が達成可能である。ここに教示する一般解の利点は、平衡整合回路網100と不平衡整合回路網2000のモデル化に生成される任意の回路構成にそれを適用できることにある。

【0047】

図20に示す不平衡整合回路網2000の実施形態は、第1の並列インピーダンス素子2002と第2の並列インピーダンス素子2004と第1の直列インピーダンス素子2006と第2の直列インピーダンス素子2008からなる。不平衡整合回路網2000のSパラメータを計算するため、構成副回路素子2001から構成副回路素子2008について開放インピーダンスと短絡アドミッタンスが計算される。

【0048】

図22の開放分流インピーダンス行列[Z]は、下式で与えられる。

【0049】

【数18】

【0050】

図23の短絡直列アドミタンス行列[Y]は、下式で与えられる。

【0051】

【数19】

【0052】

式18,式19を用いて副回路のインピーダンス行列あるいはアドミッタンス行列を割り出した後、式15,式16を用いて不平衡整合回路網2000を構成する各副回路のSパラメータを計算することができる。当事者には言うまでもないことであるが、この場合の式15,式16の行列の次元は2行2列である。エンベディング/ディエンベディング特許出願の教示を用いることで、2つの副回路の直列接続組み合わせのSパラメータを割り出すことができる。先に直列接続した回路と組み合わせた全ての副回路についてこの手順を複数回繰り返すことで、不平衡整合回路網2000全体に対する単一のSパラメータ行列を割り出すことができる。得られたSパラメータ行列は、構成部分の開放インピーダンス行列や短絡アドミッタンス行列と同じ基準特性インピーダンスへ正規化される。

【0053】

前述の如く、VNAは固定されたインピーダンス環境において、デバイスの特性試験を可能にする。しかしながら、50オーム環境はしばしばデバイスの実際の電気的インピーダンス環境を表わしはしない。一般に、各デバイスポートは他の全てのデバイスポートに接続されたインピーダンスとは異なる値を有するインピーダンスに接続される。デバイスが動作するインピーダンス環境により近いインピーダンス環境においてデバイスの特性を解明する能力が、より正確で信頼できる特性解明をもたらす。それ故に、特性を解明したデバイスの各ポートにおいてユーザが選択したインピーダンス値を有するデバイスの特性を解明する必要が存在する。本発明の教示により、1以上の不平衡整合回路網2000あるいは平衡整合回路網100と組み合わせた不平衡デバイス1900あるいは平衡デバイス500の直列接続組み合わせの電気的挙動が予測できるようになる。図2,図21を具体的に参照するに、それぞれ平衡インピーダンス変換素子202と不平衡インピーダンス変換素子2100が図示してある。インピーダンス変換素子の機能は、基準特性インピーダンスへ正規化されるSパラメータ行列を異なるインピーダンス値へ変更することにある。理想的には、回路設計者は基準インピーダンス値とは異なる整合インピーダンス値の正規化を随意確立することができる。デバイス500あるいはデバイス1900の各ポートをデバイス500あるいはデバイス1900の他のポート用に設定されたインピーダンスの正規化とは無関係なインピーダンスへ正規化することが、さらに望ましい。このインピーダンス変換を達成するには、不平衡整合回路網用に2行2列の行列演算が用いられ、平衡整合回路網用に4行4列の行列演算が用いられる。ここに記載した正規化公式は平衡回路構成用であり、それ故4行4列の行列演算が展開される。同じ定式化は、2行2列の行列演算を展開するケースを除き、不平衡のケースに用いることができる。

【0054】

平衡整合回路網100については、基準特性インピーダンスとは異なる特性インピーダンスへ正規化される4行4列のSパラメータ行列の解を、開放インピーダンス行列Zあるいは短絡アドミッタンス行列Yにより表わすことができる。異なる特性インピーダンスへ正規化した回路網インピーダンスの関数としてSパラメータを解く数式は、以下の通りである

【0055】

【数20】

【0056】

【数21】

【0057】

ここで、行列cは正規化行列である。

【0058】

正規化行列は、行添え字と列添え字の等しくない要素が零値を有するよう構成してある。正規化マトリックスの行添え字と列添え字が一致する場合は、行列要素は非零値を有する。従って、行列対角沿いにのみ値は非零とされる。非零値は、正規化対象各ポートについての特性インピーダンスの平方根に等しい。1つのポートについての正規化がそのままである場合、行列要素は基準特性インピーダンスZrefの平方根値を有する。かくして、ポートiを基準特性インピーダンスへではなく異なる特性インピーダンスへ正規化すべき場合は、ここで行i列iの行列要素の値は新たな特性インピーダンスの平方根√Z0iに一致する。ただし、iは正規化対象ポート数に等しい。それ故、2ポート平衡デバイスあるいは4端子不平衡デバイス用の任意のインピーダンス正規化行列cは、下式により与えられる。

【0059】

【数22】

【0060】

全ポートを基準インピーダンスへ正規化すべき場合、そこでは正規化行列の対角沿いの全ての値は値√Zrefを有する。この場合、基準特性正規化行列は行列crefであり、以下の如く2ポート平衡デバイス用に規定される。

【0061】

【数23】

【0062】

基準特性正規化マトリックスcrefへ正規化するSパラメータ行列は、Srefである。行列Sは、任意のインピーダンス正規化行列cへ正規化するSパラメータ行列として規定される。正規化Sパラメータ行列Sref,Sは共に、同じ開放インピーダンスあるいは短絡アドミッタンスを有する。Sパラメータは、特性インピーダンスの正規化に依存する。しかしながら、異なる特性インピーダンスへ正規化したSパラメータが、各Sパラメータ行列に対応して開放インピーダンスあるいは短絡アドミッタンスを変更することはない。従って、基準特性インピーダンスへ正規化したSパラメータ行列と任意の特性インピーダンスへ正規化したSパラメータ行列との双方から計算したインピーダンス行列は、互いに等価である。

【0063】

式20,式21から、インピーダンス行列とアドミッタンス行列はSパラメータ行列と正規化行列の関数として表わすことができる。すなわち、

【0064】

【数24】

【0065】

【数25】

【0066】

である。Sパラメータ行列の正規化処理が開放インピーダンスZや短絡アドミッタンスYのいずれも変更しないので、そこで2つの異なる正規化ケースに対し同じ式を適用することが可能である。正規化に関係なくインピーダンス行列とアドミッタンス行列の等価原理を用いることで、基準特性インピーダンスや基準正規化行列crefや任意の正規化行列cへ正規化したSパラメータ行列の関数として任意の正規化を用いてSパラメータ行列について解くことが可能となる。一例として式24を用い、基準特性インピーダンスSrefへ正規化したSパラメータ行列の関数としても、任意のインピーダンス行列Sへ正規化したSパラメータ行列の関数としても、その両方でインピーダンス行列Zは確立される。従って、

【0067】

【数26】

【0068】

【数27】

【0069】

となる。等価原理を用いることで、Zについての等式は互いに等値に設定することができる。すなわち、

【0070】

【数28】

【0071】

である。Sパラメータ行列Sについて解くことで、

【0072】

【数29】

【0073】

が得られる。ただし、

【0074】

【数30】

【0075】

アドミタンス行列を用い、式26から式29で表わされる同じ原理に従って下式を適用する。

【0076】

【数31】

【0077】

【数32】

【0078】

等価原理を用いることで、Yについての等式は互いに等値設定することができる。すなわち、

【0079】

【数33】

【0080】

である。Sパラメータ行列について解くことで、

【0081】

【数34】

【0082】

が得られる。ただし、

【0083】

【数35】

【0084】

かくして、本発明の教示を用いることで、平衡デバイスと不平衡デバイスの直列合成あるいは1以上の整合回路網をもった両種ポートを備えるデバイスについてのSパラメータを、基準特性インピーダンスあるいは任意のインピーダンスのどちらかで予測することができる。

【0085】

コンピュータの処理、記憶、グラフィカルユーザインタフェース能力を含む一実施形態において、本発明の教示を実装することは有益である。図24を具体的に参照することで、図1に例示するような平衡回路網100の整合は、図5の平衡デバイス500の設計者に図式的に提示することができる。デバイス500の各平衡ポートは、たとえ一般的な回路構成表現が同様であるにしても、異なる平衡整合回路網100に接続することができる。具体的には、図6から図18の回路構成は、他同様、グラフィカルユーザインタフェースをもって設計者に視覚的に提示することができる。以降、グラフィカルユーザインタフェースを「GUI」と称する。加えて、開放や短絡をインピーダンス素子として表現することもできる。コンピュータ上のソフトウェアにより、設計者は回路構成のうちの1つを「クリック」し、それを平衡整合回路網のうちの一回路網の中の1以上のインピーダンス素子へ「ドロップ」することができる。1以上の整合回路網が、平衡デバイス及び混在ポートデバイスの設計者に対しGUIで表わすことができる。コンピュータ上のソフトウェアにより、設計者は図6から図18に示す回路構成のうちの一つを「クリック」し、それを選択し、選択した回路構成をそこで不平衡あるいは平衡整合回路網のうちの1つの1以上のインピーダンス素子へ「ドロップ」できるようになる。図24のステップ2402を具体的に参照するに、この「クリック及びドロップ」の処理は、平衡整合回路網100あるいは不平衡整合回路網2000を構成する全てのインピーダンス素子がインピーダンス値を有する回路により規定されるまで繰り返される。また、処理の一端として、抵抗やインダクタンスや容量やQ値や動作周波数などの各電気回路用の値を適当に割り当てることもできる。このステップは、参照符号114から参照符号128あるいは参照符号2002から参照符号2008で示すそれらのインピーダンス素子Z1からインピーダンス素子Z14及びインピーダンス変換素子202,インピーダンス変換素子2001による全ての整合回路網100,整合回路網2000の表現にて完了する。ステップ2404を具体的に参照することで、全ての平衡整合回路網100あるいは不平衡整合回路網2000がそれらの構成回路をもって規定された時点で、コンピュータのプロセッサは以下の式1又は式2,式3から式11から開放複素インピーダンス行列Zあるいは短絡複素アドミッタンス行列Yの計算が可能となる。インピーダンス行列Zあるいはアドミッタンス行列Yから、プロセッサは基準特性インピーダンスにて整合回路網の関連SパラメータSMを算出することが可能である。ステップ2406を具体的に参照するに、基準特性インピーダンスにおける平衡デバイス500のSパラメータSDの入手もまた可能である。デバイスのSパラメータSDは、デバイス500のモデル及び期待されるSパラメータの計算を通じ、あるいは実際のデバイスのSパラメータの測定値を通じ、あるいは本処理による検索向けに保存した適当なデバイスSパラメータを有するコンピュータがアクセス可能なデータファイルから入手することができる。ステップ2408を具体的に参照し、エンベディング/ディエンベディング特許出願の教示を用いるに、プロセッサは平衡デバイス500及び平衡整合回路網100の直列組み合わせのSパラメータSCの計算が可能である。所望とあらば、式20又は式21を用い、プロセッサはデバイス500と整合回路網100,2000を組み合わせたデバイスの各ポートについて任意の特性インピーダンスにて正規化した直列接続Sパラメータを計算することもできる。ステップ2410を具体的に参照するに、596仮特許出願の教示の利点を用い、ここでプロセッサは得られたSパラメータ行列SCの混在モードSパラメータSCmmを抽出し、複数の整合回路網100,2000内にエンベディングした平衡デバイス500の電気的挙動の予測を支援することが可能となる。図24に例示し、上記に開示す平衡型の場合のソフトウェアによる実装は、不平衡型で混在ポートの場合にも適用し用いることができる。本発明の教示による方法の実施形態は、Microsoft Visual Studio 6.0,Roguewave Stringray Studio, Roguewave Math H++及びVictor Imaging Processing Libraryの両ソフトウェアパッケージを搭載したマイクロソフト社ウインドウズ動作環境を備えるパーソナルコンピュータを用い実装することができる。

【0086】

以上説明した本発明の実施の形態は、特許請求の範囲に記載した本発明の説明のための一実施形態にすぎず、特許請求の範囲で示した権利範囲内において種々の変形を行うことができることは、当業者にとって明らかである。最後に、本発明の広汎な応用の可能性に鑑み、本発明の実施態様の幾つかを以下に示す。

【0087】

(実施態様1)

デバイス(500,1900)の電気的挙動を予測するシステムであって、

演算処理手段と、

平衡入力ポート(102)および平衡出力ポート(108)を有する少なくとも1つの平衡整合回路網(100)を表現する手段と、

前記平衡出力ポート(108)と前記デバイス(500)の平衡ポートとの間の前記少なくとも1つの整合回路網の接続を表現する手段と、

整合回路網Sパラメータ行列SMを計算する手段と、

デバイスSパラメータ行列SDを求める手段と、

前記デバイス(500)と組み合わせた前記整合回路網(100)についての直列接続Sパラメータ行列SCを計算する手段と、

前記直列接続Sパラメータ行列から混在モード直列接続SパラメータSCmmを抽出する手段と、

を備えることを特徴とするシステム。

【0088】

(実施態様2)

少なくとも1つの整合回路網(100)の前記表現手段は、さらに、分流回路網(302)と格子回路網(402)の組み合わせをもって、前記少なくとも1つの整合回路網を表現する手段を備える、

ことを特徴とする実施態様1に記載のシステム。

【0089】

(実施態様3)

前記表現手段は、さらに、インピーダンス変換素子(202)を有する前記少なくとも1つの整合回路網(100)を表現する手段を備える、

ことを特徴とする実施態様2に記載のシステム。

【0090】

(実施態様4)

前記少なくとも1つの整合回路網(100)は、平衡インピーダンス変換素子(202)と、第1の分流回路網(114,116,117)と、第1の格子回路網(118〜121)と、第2の分流回路網(122〜124)と、第2の格子回路網(125〜128)との直列接続組み合わせを備え、

前記各分流回路網は、第1と第2の分流接続点(306,308)間の並列インピーダンス素子(304)と、それぞれ前記第1と第2の分流接続点(306,308)間の第1及び第2の分流インピーダンス素子(322,324)と、基準電位端(101)を具備し、

前記格子回路網は、第1と第3の格子接続点(406,410)間の第1の直列インピーダンス素子(404)と、前記第2と第4の格子接続点(408,412)間の第2の直列インピーダンス素子(414)と、前記第1と第4の格子接続点(406,412)間の第1の交差インピーダンス素子(422)と、前記第2と第3の格子接続点(408,410)間の第2の交差インピーダンス素子(420)とを具備し、

前記システムは、対応する整合回路網Sパラメータ行列SMを計算する手段と、前記整合回路網100と電気的に組み合わせた前記デバイス(500)の少なくとも1つのポートの特性を解明する手段とを備える、

ことを特徴とする実施態様1乃至実施態様3のいずれかに記載のシステム。

【0091】

(実施態様5)

前記整合回路網Sパラメータ行列の計算手段はさらに、前記第1の分流回路網及び第2の分流回路網について開放インピーダンス行列Zを計算する手段と、前記第1及び第2の格子インピーダンス回路網について短絡アドミッタンス行列Yを計算する手段と、前記整合回路網についてインピーダンス行列を計算する手段と、前記インピーダンス行列を前記整合回路網Sパラメータ行列へ変換する手段を備える、

ことを特徴とする実施態様2乃至実施態様4のいずれかに記載のシステム。

【0092】

(実施態様6)

さらに、前記直列接続Sパラメータ行列SCを任意の特性インピーダンスへ正規化する手段を備える、

ことを特徴とする実施態様5に記載の前記システム。

【0093】

(実施態様7)

さらに、前記直列接続Sパラメータ行列から多ポート混在モードSパラメータを抽出する手段を備える、

ことを特徴とする実施態様1乃至実施態様6のいずれかに記載の前記システム。

【0094】

(実施態様8)

さらに、前記デバイス(1900)の少なくとも1つの不平衡ポートと電気的に組み合わせた少なくとも1つの不平衡整合回路網(2000)を表現する手段を備える、

ことを特徴とする実施態様1乃至実施態様7のいずれかに記載の前記システム。

【0095】

(実施態様9)

前記デバイスは複数の平衡ポート有し、

前記システムは、前記平衡整合回路網(100)の表現と整合回路網Sパラメータ行列SMの計算を繰り返す手段をさらに備える、

ことを特徴とする実施態様1乃至実施態様9のいずれかに記載の前記システム。

【0096】

(実施態様10)

前記正規化手段は、前記整合回路網を異なる特性インピーダンス値へ正規化する、

ことを特徴とする実施態様9に記載の前記システム。

【図面の簡単な説明】

【図1】本発明の教示になる平衡整合回路網の一実施形態を表わす図である。

【図2】平衡インピーダンス変換素子を表わす図である。

【図3】分流回路網素子を表わす図である。

【図4】格子回路網素子を表わす図である。

【図5】2N個の平衡デバイスポートを有し、複数の平衡整合回路網中にエンベディングした平衡デバイスを表わす図である。

【図6】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図7】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図8】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図9】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図10】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図11】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図12】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図13】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図14】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図15】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図16】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図17】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図18】図1の整合回路網と併用可能な回路素子の一例を示す図である。

【図19】不平衡整合回路網と平衡整合回路網をそれぞれ組み合わせた不平衡デバイスポート及び平衡デバイスポートを有するデバイスのモデルを例示する図である。

【図20】本発明の教示になる不平衡整合回路網の一実施形態を表わす図である。

【図21】不平衡インピーダンス変換素子を表わす図である。

【図22】不平衡分流回路網素子を表わす図である。

【図23】直列インピーダンス素子へ簡約した不平衡格子回路網素子を表わす図である。

【図24】本発明の教示を利用する方法の一実施形態を表わすフローチャートである。

【符号の説明】

100 平衡整合回路網

101 共通電位端

102 平衡入力ポート

104 第1の入力端子

106 第2の入力端子

108 平衡出力ポート

110 第1の出力ポート

112 第2の出力ポート

114〜128 インピーダンス素子

202 平衡インピーダンス変換素子

204 平衡インピーダンス変換入力ポート

206 平衡インピーダンス変換出力ポート

302 平衡2ポート分流回路網

304 並列インピーダンス素子

306 第1の分流接続点

308 第2の分流接続点

310 第1の入力端子

312 第2の入力端子

314 第1の出力端子

316 第2の出力端子

318 第1の平衡入力ポート

320 第2の平衡出力ポート

322 第1の分流インピーダンス素子

324 第2の分流インピーダンス素子

402 平衡2ポート格子回路網

404 第1の直列インピーダンス素子

406 第1の格子回路網接続点

408 第2の格子回路網接続点

410 第3の格子回路網接続点

412 第4の格子回路網接続点

414 第2の直列インピーダンス素子

416 平衡入力端

418 平衡出力ポート

420 第2の交差インピーダンス素子

422 第1の交差インピーダンス素子

500,1900 デバイス

2000 不平衡整合回路網

2002 第1の並列インピーダンス素子

2004 第2の並列インピーダンス素子

2006 第1の直列インピーダンス素子

2008 第2の直列インピーダンス素子

2100 不平衡インピーダンス変換素子

2300 格子回路網

Claims (10)

- デバイスの電気的挙動を予測するシステムであって、

演算処理手段と、

平衡入力ポートおよび平衡出力ポートを有する少なくとも1つの平衡整合回路網を表現する手段と、

前記平衡出力ポートと前記デバイスの平衡ポートとの間の前記少なくとも1つの整合回路網の接続を表現する手段と、

整合回路網Sパラメータ行列SMを計算する手段と、

デバイスSパラメータ行列SDを求める手段と、

前記デバイスと組み合わせた前記整合回路網についての直列接続Sパラメータ行列SCを計算する手段と、

前記直列接続Sパラメータ行列から混在モード直列接続SパラメータSCmmを抽出する手段と、

を備えることを特徴とするシステム。 - 少なくとも1つの整合回路網の前記表現手段は、さらに、分流回路網と格子回路網の組み合わせをもって、前記少なくとも1つの整合回路網を表現する手段を備える、

ことを特徴とする請求項1に記載のシステム。 - 前記表現手段は、さらに、インピーダンス変換素子を有する前記少なくとも1つの整合回路網を表現する手段を備える、

ことを特徴とする請求項2に記載のシステム。 - 前記少なくとも1つの整合回路網は、平衡インピーダンス変換素子と、第1の分流回路網と、第1の格子回路網と、第2の分流回路網と、第2の格子回路網との直列接続組み合わせを備え、

前記各分流回路網は、第1と第2の分流接続点間の並列インピーダンス素子と、それぞれ前記第1と第2の分流接続点間の第1及び第2の分流インピーダンス素子と、基準電位端を具備し、

前記格子回路網は、第1と第3の格子接続点間の第1の直列インピーダンス素子と、前記第2と第4の格子接続点間の第2の直列インピーダンス素子と、前記第1と第4の格子接続点間の第1の交差インピーダンス素子と、前記第2と第3の格子接続点間の第2の交差インピーダンス素子とを具備し、

前記システムは、対応する整合回路網Sパラメータ行列SMを計算する手段と、前記整合回路網100と電気的に組み合わせた前記デバイスの少なくとも1つのポートの特性を解明する手段とを備える、

ことを特徴とする請求項1乃至請求項3のいずれかに記載のシステム。 - 前記整合回路網Sパラメータ行列の計算手段はさらに、前記第1の分流回路網及び第2の分流回路網について開放インピーダンス行列Zを計算する手段と、前記第1及び第2の格子インピーダンス回路網について短絡アドミッタンス行列Yを計算する手段と、前記整合回路網についてインピーダンス行列を計算する手段と、前記インピーダンス行列を前記整合回路網Sパラメータ行列へ変換する手段を備える、

ことを特徴とする請求項2乃至請求項4のいずれかに記載のシステム。 - さらに、前記直列接続Sパラメータ行列SCを任意の特性インピーダンスへ正規化する手段を備える、

ことを特徴とする請求項5に記載の前記システム。 - さらに、前記直列接続Sパラメータ行列から多ポート混在モードSパラメータを抽出する手段を備える、

ことを特徴とする請求項1乃至請求項6のいずれかに記載の前記システム。 - さらに、前記デバイスの少なくとも1つの不平衡ポートと電気的に組み合わせた少なくとも1つの不平衡整合回路網を表現する手段を備える、

ことを特徴とする請求項1乃至請求項7のいずれかに記載の前記システム。 - 前記デバイスは複数の平衡ポート有し、

前記システムは、前記平衡整合回路網の表現と整合回路網Sパラメータ行列SMの計算を繰り返す手段をさらに備える、

ことを特徴とする請求項1乃至請求項9のいずれかに記載の前記システム。 - 前記正規化手段は、前記整合回路網を異なる特性インピーダンス値へ正規化する、

ことを特徴とする請求項9に記載の前記システム。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/127,744 US6757625B2 (en) | 2002-04-22 | 2002-04-22 | Method, apparatus, and article of manufacture for predicting electrical behavior of a multiport device having balanced device ports |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004030598A true JP2004030598A (ja) | 2004-01-29 |

| JP2004030598A5 JP2004030598A5 (ja) | 2006-06-15 |

Family

ID=29215322

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003116105A Pending JP2004030598A (ja) | 2002-04-22 | 2003-04-21 | 平衡デバイスポートを有する多ポートデバイスの電気的挙動を予測するシステム |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6757625B2 (ja) |

| JP (1) | JP2004030598A (ja) |

| DE (1) | DE10318202A1 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007207168A (ja) * | 2006-02-06 | 2007-08-16 | Nec Electronics Corp | Emiシミュレーションモデル、emiシミュレーションシステムと方法 |

| WO2010016200A1 (ja) * | 2008-08-08 | 2010-02-11 | 日本電気株式会社 | 差動型トランスインピーダンスアンプの評価方法、光受信回路評価方法、そのプログラムが格納された記憶媒体および装置 |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6920407B2 (en) * | 2000-09-18 | 2005-07-19 | Agilent Technologies, Inc. | Method and apparatus for calibrating a multiport test system for measurement of a DUT |

| US6826506B2 (en) * | 2000-09-18 | 2004-11-30 | Agilent Technologies, Inc. | Method and apparatus for calibrating a multiport test system for measurement of a DUT |

| US6744262B2 (en) | 2002-03-14 | 2004-06-01 | Agilent Technologies, Inc. | Method, apparatus, and article of manufacture for characterizing a device and predicting electrical behavior of the device in a circuit |

| US6853198B2 (en) * | 2002-11-14 | 2005-02-08 | Agilent Technologies, Inc. | Method and apparatus for performing multiport through-reflect-line calibration and measurement |

| US7034548B2 (en) * | 2003-04-11 | 2006-04-25 | Agilent Technologies, Inc. | Balanced device characterization including test system calibration |

| US7013229B2 (en) * | 2003-11-13 | 2006-03-14 | Agilent Technologies, Inc. | Obtaining calibration parameters for a three-port device under test |

| US7126346B2 (en) * | 2003-12-18 | 2006-10-24 | Agilent Technologies, Inc. | Method, apparatus, and article of manufacture for manufacturing high frequency balanced circuits |

| JP2005274373A (ja) * | 2004-03-25 | 2005-10-06 | Fujitsu Ltd | Sパラメータ算出装置,sパラメータ算出方法,sパラメータ算出プログラムおよびそのプログラムを記録したコンピュータ読み取り可能な記録媒体 |

| US8476326B2 (en) * | 2006-09-22 | 2013-07-02 | Dow Global Technologies Llc | Fibrillated polyolefin foam |

| US20080195344A1 (en) * | 2007-02-14 | 2008-08-14 | Suss Microtec Test Systems Gmbh | Method for determining measurement errors in scattering parameter measurements |

| US7679434B2 (en) | 2008-01-21 | 2010-03-16 | Infineon Technologies Ag | Amplifier modulation method and apparatus |

| EP2363719A1 (en) * | 2010-02-12 | 2011-09-07 | ATE Systems, Inc | Method and apparatus for calibrating a test system for measuring a device under test |

| CN103323688B (zh) * | 2012-03-20 | 2015-11-25 | 华北电力科学研究院有限责任公司 | 一种电力系统的谐波状态估计方法及设备 |

| CN107943641A (zh) * | 2017-11-16 | 2018-04-20 | 郑州云海信息技术有限公司 | 一种生成多端口s参数文档的方法及装置 |

| US10938490B1 (en) * | 2018-10-31 | 2021-03-02 | Christos Tsironis | Calibration method for coupler-tuner assembly |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5025402A (en) | 1989-04-07 | 1991-06-18 | Northern Telecom Limited | Method of transient simulation of transmission line networks using a circuit simulator |

| US4962359A (en) * | 1989-06-29 | 1990-10-09 | Hewlett-Packard Company | Dual directional bridge and balun used as reflectometer test set |

| US5467021A (en) | 1993-05-24 | 1995-11-14 | Atn Microwave, Inc. | Calibration method and apparatus |

| US5434511A (en) | 1993-05-24 | 1995-07-18 | Atn Microwave, Inc. | Electronic microwave calibration device |

| US5793213A (en) | 1996-08-01 | 1998-08-11 | Motorola, Inc. | Method and apparatus for calibrating a network analyzer |

| US6106563A (en) | 1997-09-26 | 2000-08-22 | Motorola, Inc. | Method and apparatus for extracting parameters for an electrical structure |

| US6347382B1 (en) * | 1998-11-30 | 2002-02-12 | Advantest Corp. | Multi-port device analysis apparatus and method |

| US6292070B1 (en) * | 1999-03-11 | 2001-09-18 | Anaren Microwave, Inc. | Balun formed from symmetrical couplers and method for making same |

| US20020003455A1 (en) * | 2000-03-30 | 2002-01-10 | Gerd Vandersteen | Broadband high frequency differential coupler |

| US6826506B2 (en) | 2000-09-18 | 2004-11-30 | Agilent Technologies, Inc. | Method and apparatus for calibrating a multiport test system for measurement of a DUT |

| US6483415B1 (en) * | 2001-05-21 | 2002-11-19 | Industrial Technology Research Institute | Multi-layer LC resonance balun |

| TW535322B (en) * | 2001-06-27 | 2003-06-01 | Ind Tech Res Inst | Multi-layer radio frequency chip balun |

| US6665628B2 (en) * | 2002-01-15 | 2003-12-16 | Anritsu Company | Methods for embedding and de-embedding balanced networks |

| US6744262B2 (en) | 2002-03-14 | 2004-06-01 | Agilent Technologies, Inc. | Method, apparatus, and article of manufacture for characterizing a device and predicting electrical behavior of the device in a circuit |

-

2002

- 2002-04-22 US US10/127,744 patent/US6757625B2/en not_active Expired - Lifetime

-

2003

- 2003-04-21 JP JP2003116105A patent/JP2004030598A/ja active Pending

- 2003-04-22 DE DE10318202A patent/DE10318202A1/de not_active Ceased

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007207168A (ja) * | 2006-02-06 | 2007-08-16 | Nec Electronics Corp | Emiシミュレーションモデル、emiシミュレーションシステムと方法 |

| WO2010016200A1 (ja) * | 2008-08-08 | 2010-02-11 | 日本電気株式会社 | 差動型トランスインピーダンスアンプの評価方法、光受信回路評価方法、そのプログラムが格納された記憶媒体および装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| DE10318202A1 (de) | 2003-11-06 |

| US20030200039A1 (en) | 2003-10-23 |

| US6757625B2 (en) | 2004-06-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2004030598A (ja) | 平衡デバイスポートを有する多ポートデバイスの電気的挙動を予測するシステム | |

| Palmer et al. | Simple broadband measurements of balanced loads using a network analyzer | |

| CN110188381B (zh) | 一种用于电磁干扰预测的仿真模型的构建方法及系统 | |

| JP2003294794A (ja) | 複数の装置ポートを有する装置の特性を解明する方法及び機器 | |

| US6961669B2 (en) | De-embedding devices under test | |

| Arsenovic et al. | scikit-rf: An open source python package for microwave network creation, analysis, and calibration [speaker’s corner] | |

| Morsey et al. | PRIME: Passive realization of interconnect models from measured data | |

| US6106563A (en) | Method and apparatus for extracting parameters for an electrical structure | |

| US7127363B2 (en) | Calculating differential scattering parameters | |

| Halligan et al. | Maximum crosstalk estimation in weakly coupled transmission lines | |

| Fasig et al. | Introduction to non-invasive current estimation (NICE) | |

| US11300616B2 (en) | Systems and methods for non-invasive current estimation | |

| Kolstad et al. | A new circuit augmentation method for modeling of interconnects and passive components | |

| Wei et al. | S-parameters characterization and sequence model of three-phase EMI filter | |

| CN115422499A (zh) | 基于有理式拟合与矩阵变换的耦合矩阵提取方法及设备 | |

| Coetzer et al. | String-to-String Coupling Within a Large Photovoltaic Module: Measurement and Circuit-Computational Electromagnetic Hybrid Modelling | |

| Stevanović et al. | Multiconductor cable modeling for EMI simulations in power electronics | |

| Mohan et al. | Causal reduced-order modeling of distributed structures in a transient circuit simulator | |

| Gurrala et al. | An intuitive approach to fit a frequency dependent equivalent circuit for transmission line models | |

| Kolstad et al. | A new modeling methodology for passive components based on black-box augmentation combined with equivalent circuit perturbation | |

| Mora et al. | Critical equipment input impedance measurement for IEMI calculations | |

| Belforte | Digital wave simulation of lossy lines for multi-gigabit applications | |

| Stošić | Wave digital models of ideal and real transformers | |

| Rotgerink et al. | Mixed-Mode S-Parameter Measurements for Determination of Cable Coupling | |

| Kofler et al. | Implementing S-parameter models in MATLAB Simulink to analyze transients in ungrounded shipboard power systems |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060413 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060413 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080814 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090205 |