EP4102559A1 - Power semiconductor module - Google Patents

Power semiconductor module Download PDFInfo

- Publication number

- EP4102559A1 EP4102559A1 EP21178802.1A EP21178802A EP4102559A1 EP 4102559 A1 EP4102559 A1 EP 4102559A1 EP 21178802 A EP21178802 A EP 21178802A EP 4102559 A1 EP4102559 A1 EP 4102559A1

- Authority

- EP

- European Patent Office

- Prior art keywords

- power semiconductor

- semiconductor module

- group

- module according

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5381—Crossover interconnections, e.g. bridge stepovers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5383—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5385—Assembly of a plurality of insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5386—Geometry or layout of the interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5387—Flexible insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/58—Structural electrical arrangements for semiconductor devices not otherwise provided for, e.g. in combination with batteries

- H01L23/64—Impedance arrangements

- H01L23/645—Inductive arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/03—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/07—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group subclass H10D

- H01L25/072—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group subclass H10D the devices being arranged next to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/18—Assemblies consisting of a plurality of semiconductor or other solid state devices the devices being of the types provided for in two or more different main groups of the same subclass of H10B, H10D, H10F, H10H, H10K or H10N

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/181—Printed circuits structurally associated with non-printed electric components associated with surface mounted components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/189—Printed circuits structurally associated with non-printed electric components characterised by the use of a flexible or folded printed circuit

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4911—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain

- H01L2224/49113—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain the connectors connecting different bonding areas on the semiconductor or solid-state body to a common bonding area outside the body, e.g. converging wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13055—Insulated gate bipolar transistor [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19107—Disposition of discrete passive components off-chip wires

Definitions

- the present disclosure relates to a power semiconductor module with a plurality of semiconductor switches arranged in at least two groups, the semiconductor switches having a first terminal and a second terminal of a controlled path and a control terminal.

- a power semiconductor module is known in which several power semiconductor switches are connected together using separate substrate metallizations which are arranged in a stacked manner.

- the object is achieved by a power semiconductor module with a plurality of semiconductor switches arranged in at least two groups, the semiconductor switches having a first terminal and a second terminal of a controlled path and a control terminal, each group having a first group contact which is connected to the first terminals, a second group contact which is connected to the second terminals and a control group contact which is connected to the control terminals, an interconnection bridge for connecting the control group contacts and the first group contacts of the at least two groups, the interconnection bridge comprising a layer structure with a first conductive layer and a second conductive layer being separated by an insulating layer.

- Voltage applied between the control group contacts and between the first group contacts is used to control the state of the semiconductor devices, i.e. the voltage effects a switching of states between open and closed. Therefore, fast change of this voltage without critical oscillations is important for low-loss operation.

- the described embodiments have an improved gate connection. Because of the very close arrangement within the interconnection bridge where both conductive layers are separated only by a very thin insulating layer, a substantial reduction of the gate control loop inductance can be achieved compared to the conventional wire-bond connection between substrates.

- the physical reason for the reduced inductance is that for a very close arrangement of two conductors the inductive coupling significantly increases.

- a current flowing through a the gate connection layer of the interconnection bridge to the gate terminals of the switches of that group mainly charges capacities of the gate electrodes.

- Related currents flow in the other direction through the source connection layer of the interconnection bridge. Due to the anti-parallel direction of the currents and the mutual inductive coupling, a substantial reduction of the gate inductance can be effected.

- the proposed embodiment enables that also in power semiconductor modules in which a large number of semiconductor switches are connected in parallel and accordingly the lengths of the connection paths to the different groups of semiconductor switches are very different, the effect of the different lengths on the gate inductances of the different groups of semiconductor switches is attenuated and a better synchronization of the switching behavior and less oscillations can be achieved. This results in an improved switching behavior and less power loss during the switching period.

- resistors e.g. gate resistors located directly in the module, which are normally used to attenuate the oscillations between switches can be omitted or at least reduced. This additionally improves the switching behavior.

- resistors are omitted, a direct connection between a module gate contact and control terminals of the plurality of semiconductor switches can be implemented, which mean that there are no electronic elements in between.

- the layer structure is formed as a "normal" or flexible printed circuit board.

- both sides of a flexible insulating material are at least partly covered by a conductive material such as a metal.

- a conductive material such as a metal. Copper or aluminum or an alloy of copper and aluminum is advantageous as conductive material.

- the layer structure is formed by a ceramic substrate with a two side metallization. It is advantageous if the interconnection bridge has at least two feet on each side, the feet being connected to group contacts of both groups by soldering or welding or by an adhesive connection.

- Exemplarily MOSFETs or MISFETs or IGBTs are used as semiconductor switches in the embodiments described.

- the semiconductor switches may be based on Silicon or a wide bandgap material, exemplarily SiC or GaN.

- the present disclosure comprises an additional aspect of improvements of the gate connection, which is selectively increasing the inductance of certain connections within the module.

- a compensation structure is provided for shorter gate connection paths. While the total gate inductance is increased by this measure, the differences between the inductances of gate connection paths of different groups within the module can be reduced. This further reduces oscillations and accordingly improves the switching behavior.

- Compensation structures according to this aspect can be used in combination with the reduction of inductance as described above. This might become necessary or beneficial, because the physical possibilities to reduce the inductance are limited and a complete equalization cannot be achieved in all practical configurations. However, a combination of both aspects, i.e. reduction of the inductance of long connection paths and increase of inductance of short connection paths can lead to complete equalization or at least a substantial reduction of the differences of gate inductances.

- Figure 1 is a schematic view of a power module 1 comprising two groups 2 and 3 of semiconductor switches 4. Gate terminals 10 of semiconductor switches 4 are connected to a module gate contact 5. The length of the conduction paths between the module gate contact 5 and the gate terminals 10 of the semiconductor switches 4 depends on the geometric arrangement of the components within the module 1. For example, if more than two groups of semiconductor switches are provided, it can be difficult to achieve an equal length of the connection paths for each of the groups of semiconductor switches.

- the present disclosure it is not the aim to suppress oscillations but to avoid them from the beginning.

- the approach is not to minimize the total gate inductance of the power semiconductor module 1, but to equalize the gate inductances of different groups of semiconductor switches. While the switching capability of the power semiconductor module 1 also depends on the total inductance of the gate path, oscillations strongly depend on the difference of inductances and the path lengths of two different groups 2 and 3 of semiconductor switches 4.

- module stray inductance must be sufficiently low to avoid critical voltage overshoots, and inductance imbalance must be low to avoid oscillations between semiconductor switches.

- the inductance of the gate path of the first group 2 can be described as a shared inductance L_shared + interconnection inductance L_interconnection + inductance L1, while the inductance of the second gate path can be described as shared inductance L_shared + L2.

- the connection path to the first group 2 is longer than to the second group 3.

- a part of the gate path to the first group 2 is implemented with an interconnection bridge 6.

- the inductance of this part of the gate path can be reduced. In practice, a reduction of about 50% of the gate inductance of the gate path to the first group 2 can be achieved.

- the proposed features can be beneficial especially in design of complex high-power modules based on many silicon carbide or gallium nitride switches located on several substrates and connected in parallel.

- the concept of this disclosure can be implemented also in smaller power modules as shown in figure 1 .

- Figure 2 shows the effect of an interconnection bridge in such an embodiment.

- such two substrates would represent upper or lower side of the module.

- Another such two substrates, connected in parallel, would form the other switch of this half-bridge module.

- a resistor in the gate path can be at least reduced to a value of less than 2 ⁇ .

- Such resistors can be implemented as semiconductor resistors and do not require additional production steps.

- the disclosure has the advantage that resistors may be omitted to suppress oscillations or at least the implementation as substrate resistor.

- Figure 3 shows a more detailed view of two groups 2 and 3 of semiconductor switches 4.

- Semiconductor switches 4 are arranged on a metallization layer.

- a section 15 of the metallization layer is used as a drain connection.

- Another section of the metallization layer is separated to form a gate group contact 13, also referenced to as control group contact 13.

- Further parts of the metallization are separated as source group contact 14 which is also referenced to as first group contact 14. This applies to both substrates of groups 2 and 3.

- the gate terminals 10 of switches 4 are connected to a first side metallization 11 which appears in Figure 3 as top side metallization and from there to the gate group contact 13 as shown for the left group 2.

- the first side metallization can also be split in for example two parts connected via a resistor 24 and a bond wire as shown for the right group 3. This way the resistor 24 with a value of less than 2 Qis integrated in the gate path to attenuate oscillations.

- the source terminals of switches 4 are connected to a further metallization 16 which forms a source interconnection and from there to the first group contact 14.

- the interconnection bridge 6 is used for the connection between the substrates, that means also between the different groups of switches.

- Figure 4 shows a more detailed view of the interconnection bridge 6. It comprises two conductive layers 17 and 18. While the layer 18 is used as gate connection, layer 17 is used as source connection. Both layers are separated by an insulating layer which is not shown in this figure. On both sides of the interconnection bridge 6, feet 19 for the gate connection and feet 20 for the source connection are provided. These feet are connected to the control group contacts 13 and the first group contacts 14, for example, by welding or sintering or soldering or an adhesive.

- Figure 5 shows an even more detailed view of the interconnection bridge 6.

- the conductive layers 17 and 18 are separated by an insulating layer 21.

- the interconnection bridge comprises a stacked sequence of layers with an insulating and protecting layer 25, followed by a first metallization 26 for a first potential, a thin insulating layer 27, a second metallization 28 for a second potential and a second insulating and protecting layer 29.

- layers 25 and 26 and also layers 29 and 28 are provided as PCB.

- terminals 30 and 36 are arranged which are used for electrical connection of both metallizations, i.e. the first metallization 26 and the second metallization 28.

- vias can be used to access the metallizations 26 and 28 from the terminal side of the second insulating and protecting layer 29.

- Figure 7 shows a cross-section of the embodiment of Figure 7 .

- the terminals 30 and 36 for both potentials which can relate to the gate and source connection, are connected by vias to the first metallization 26 and the second metallization 28, respectively.

- the mechanical stability is increased. This can be beneficial for very long interconnection bridges and additionally opens the possibility to reduce the thickness of the insulating layer to a minimum because it does not have to provide a mechanical function for mechanically stabilizing the interconnection bridge.

- Another possibility for mechanically stabilizing the interconnection bridge is to use a glue somewhere between the terminals to support the bridge. This can be implemented for example in connection with all embodiments of this disclosure.

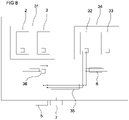

- FIG. 8 shows a further embodiment of this disclosure.

- groups 2 and 3 of semiconductor switches are integrated within a submodule 31.

- Two additional groups of semiconductor switches 32 and 33 are integrated within a second submodule 34.

- Each of the submodules 31 and 34 comprises a connection between the groups via an interconnection bridge 6 as described in the previous figures.

- an interconnection bridge 35 is used which is formed similar to the interconnection bridge 6 for the intergroup connection within each submodule 31 and 34.

- interconnection bridge 35 cannot fully equalize the differences of gate inductances of the gate paths to submodules 31 and 34. Therefore, an additional compensation structure 36 is provided according to the second aspect of this disclosure as described above.

- the compensation structure effects an increase of the inductance of the gate connection path to the switches of the first submodule 31. Both, the decrease of inductance by interconnection bridge 35 and increase of inductance by compensation structure 36 contributes to more equal inductances in the gate connection paths of both submodules 31 and 34.

- Figures 9 to 12 show possibilities which can be easily implemented.

- Figure 9 shows a meander like structure in which the connection between contact point 38 and contact point 39 is increased by the meander structure.

- islands 40 are formed in a metallization 22 of a substrate 23 and are connected by bond wires 41. Also this way the current path between connection points 38 and 39 is extended.

- the compensation structure can also be implemented in the metallization 11.

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Geometry (AREA)

- Power Conversion In General (AREA)

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP21178802.1A EP4102559A1 (en) | 2021-06-10 | 2021-06-10 | Power semiconductor module |

| CN202210647719.9A CN115472594A (zh) | 2021-06-10 | 2022-06-08 | 功率半导体模块 |

| JP2022093745A JP2022189793A (ja) | 2021-06-10 | 2022-06-09 | パワー半導体モジュール |

| US17/806,337 US12293973B2 (en) | 2021-06-10 | 2022-06-10 | Power semiconductor module |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP21178802.1A EP4102559A1 (en) | 2021-06-10 | 2021-06-10 | Power semiconductor module |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| EP4102559A1 true EP4102559A1 (en) | 2022-12-14 |

Family

ID=76421920

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| EP21178802.1A Pending EP4102559A1 (en) | 2021-06-10 | 2021-06-10 | Power semiconductor module |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US12293973B2 (enExample) |

| EP (1) | EP4102559A1 (enExample) |

| JP (1) | JP2022189793A (enExample) |

| CN (1) | CN115472594A (enExample) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2025191974A1 (ja) * | 2024-03-11 | 2025-09-18 | 富士電機株式会社 | 半導体装置 |

| CN119314974B (zh) * | 2024-12-13 | 2025-04-11 | 北京怀柔实验室 | 功率半导体封装结构 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20110233608A1 (en) * | 2008-10-29 | 2011-09-29 | Abb Research Ltd | Connection arrangement for semiconductor power modules |

| EP3113223A1 (en) | 2015-07-02 | 2017-01-04 | ABB Technology AG | Power semiconductor module |

| US20180123478A1 (en) * | 2016-11-02 | 2018-05-03 | Ford Global Technologies, Llc | Inverter switching devices with common source inductance layout to avoid shoot-through |

| US20200185359A1 (en) * | 2017-09-04 | 2020-06-11 | Mitsubishi Electric Corporation | Semiconductor module and power conversion device |

| US20200373852A1 (en) * | 2019-05-20 | 2020-11-26 | Ford Global Technologies, Llc | Dc inverter/converter current balancing for paralleled phase leg switches |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1298802A1 (de) * | 2001-09-28 | 2003-04-02 | ABB Schweiz AG | Verfahren zum Ansteuern eines Leistungshalbleiters |

| CN100380661C (zh) | 2002-01-29 | 2008-04-09 | 美高森美公司 | 分栅式功率模块以及用于抑制其中振荡的方法 |

| CN103199017B (zh) | 2003-12-30 | 2016-08-03 | 飞兆半导体公司 | 形成掩埋导电层方法、材料厚度控制法、形成晶体管方法 |

| US8154874B2 (en) | 2006-06-21 | 2012-04-10 | International Rectifier Corporation | Use of flexible circuits in a power module for forming connections to power devices |

| WO2014090685A1 (de) * | 2012-12-10 | 2014-06-19 | Abb Technology Ag | Leistungshalbleitermodul und kontaktierungsanordnung |

| US9355950B1 (en) * | 2015-01-08 | 2016-05-31 | Infineon Technologies Ag | Power semiconductor module having low gate drive inductance flexible board connection |

| EP3168873A1 (en) | 2015-11-11 | 2017-05-17 | ABB Technology AG | Power semiconductor module |

| WO2017157486A1 (en) | 2016-03-16 | 2017-09-21 | Abb Schweiz Ag | Semiconductor device |

| CN110867438A (zh) | 2019-09-30 | 2020-03-06 | 臻驱科技(上海)有限公司 | 功率半导体模块衬底 |

-

2021

- 2021-06-10 EP EP21178802.1A patent/EP4102559A1/en active Pending

-

2022

- 2022-06-08 CN CN202210647719.9A patent/CN115472594A/zh active Pending

- 2022-06-09 JP JP2022093745A patent/JP2022189793A/ja active Pending

- 2022-06-10 US US17/806,337 patent/US12293973B2/en active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20110233608A1 (en) * | 2008-10-29 | 2011-09-29 | Abb Research Ltd | Connection arrangement for semiconductor power modules |

| EP3113223A1 (en) | 2015-07-02 | 2017-01-04 | ABB Technology AG | Power semiconductor module |

| US20180123478A1 (en) * | 2016-11-02 | 2018-05-03 | Ford Global Technologies, Llc | Inverter switching devices with common source inductance layout to avoid shoot-through |

| US20200185359A1 (en) * | 2017-09-04 | 2020-06-11 | Mitsubishi Electric Corporation | Semiconductor module and power conversion device |

| US20200373852A1 (en) * | 2019-05-20 | 2020-11-26 | Ford Global Technologies, Llc | Dc inverter/converter current balancing for paralleled phase leg switches |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2022189793A (ja) | 2022-12-22 |

| CN115472594A (zh) | 2022-12-13 |

| US20220399279A1 (en) | 2022-12-15 |

| US12293973B2 (en) | 2025-05-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US12046584B2 (en) | Semiconductor module | |

| KR101755085B1 (ko) | 전력용 반도체 모듈 및 전력 변환 장치 | |

| US8441128B2 (en) | Semiconductor arrangement | |

| KR100430772B1 (ko) | 반도체장치 | |

| US9972569B2 (en) | Robust low inductance power module package | |

| US12087699B2 (en) | Semiconductor module | |

| US12293973B2 (en) | Power semiconductor module | |

| WO2021130110A1 (en) | Power module with improved electrical and thermal characteristics | |

| WO2020229114A1 (en) | Semiconductor module | |

| CN117337490A (zh) | 半导体装置 | |

| JPS5915183B2 (ja) | マトリツクス配線基板 | |

| US11538725B2 (en) | Semiconductor module arrangement | |

| CN112332635B (zh) | 半导体模块装置以及用于操作半导体模块装置的方法 | |

| US11133303B2 (en) | Semiconductor device and semiconductor arrangement comprising semiconductor devices | |

| US12136603B2 (en) | Semiconductor arrangement comprising a semiconductor element, a substrate and bond connecting means | |

| US9633927B2 (en) | Chip arrangement and method for producing a chip arrangement | |

| WO2023243418A1 (ja) | 半導体装置 | |

| EP4102558A1 (en) | Power semiconductor module | |

| US20240213196A1 (en) | Power Semiconductor Devices Including Multiple Layer Metallization | |

| US20240363497A1 (en) | Semiconductor module arrangements | |

| US20220102291A1 (en) | Power module | |

| US20240332271A1 (en) | Semiconductor device | |

| CN120153481A (zh) | 功率电子模块、用于制造功率电子模块的方法 | |

| EP3321959A1 (en) | Power semiconductor module |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PUAI | Public reference made under article 153(3) epc to a published international application that has entered the european phase |

Free format text: ORIGINAL CODE: 0009012 |

|

| STAA | Information on the status of an ep patent application or granted ep patent |

Free format text: STATUS: REQUEST FOR EXAMINATION WAS MADE |

|

| 17P | Request for examination filed |

Effective date: 20220511 |

|

| AK | Designated contracting states |

Kind code of ref document: A1 Designated state(s): AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR |

|

| P01 | Opt-out of the competence of the unified patent court (upc) registered |

Effective date: 20230527 |

|

| RAP1 | Party data changed (applicant data changed or rights of an application transferred) |

Owner name: HITACHI ENERGY LTD |

|

| STAA | Information on the status of an ep patent application or granted ep patent |

Free format text: STATUS: EXAMINATION IS IN PROGRESS |

|

| 17Q | First examination report despatched |

Effective date: 20250613 |

|

| RIN1 | Information on inventor provided before grant (corrected) |

Inventor name: KICIN, SLAVO Inventor name: SCHROEDER, ARNE Inventor name: YAGHOUBI, FARHAD |

|

| GRAP | Despatch of communication of intention to grant a patent |

Free format text: ORIGINAL CODE: EPIDOSNIGR1 |

|

| STAA | Information on the status of an ep patent application or granted ep patent |

Free format text: STATUS: GRANT OF PATENT IS INTENDED |