EP0889612A2 - Viterbi decoder and decision feedback equalizer for coded modulation - Google Patents

Viterbi decoder and decision feedback equalizer for coded modulation Download PDFInfo

- Publication number

- EP0889612A2 EP0889612A2 EP98304933A EP98304933A EP0889612A2 EP 0889612 A2 EP0889612 A2 EP 0889612A2 EP 98304933 A EP98304933 A EP 98304933A EP 98304933 A EP98304933 A EP 98304933A EP 0889612 A2 EP0889612 A2 EP 0889612A2

- Authority

- EP

- European Patent Office

- Prior art keywords

- signal

- signal points

- state

- path

- generated

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/23—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using convolutional codes, e.g. unit memory codes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/03—Shaping networks in transmitter or receiver, e.g. adaptive shaping networks

- H04L25/03006—Arrangements for removing intersymbol interference

- H04L25/03178—Arrangements involving sequence estimation techniques

- H04L25/03203—Trellis search techniques

- H04L25/03235—Trellis search techniques with state-reduction using feedback filtering

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0045—Arrangements at the receiver end

- H04L1/0054—Maximum-likelihood or sequential decoding, e.g. Viterbi, Fano, ZJ algorithms

Definitions

- the present invention relates to the use of decision feedback equalization in communication systems which employ coded modulation.

- Decision feedback equalization is a preferred technique for compensating for intersymbol interference, or ISI, engendered in certain kinds of transmission channels.

- ISI intersymbol interference

- an estimate of the ISI component of a received signal representing a transmitted signal point is subtracted from the received signal prior to a decision being made as to which signal point was transmitted.

- the estimate is generated as a function of a plurality of previous decisions-typically, as a linear combination of same.

- the process of decoding the transmitted signal points involves a delay of many signaling intervals due to the use of maximum likelihood decoding in, for example, the Viterbi decoder that is typically used.

- the decision feedback equalizer, or DFE requires immediate past decisions in order to estimate the ISI component.

- U.S. Patent No. 5,056,117 issued to Gitlin et al. on Oct. 8, 1991 discloses a joint Viterbi decoder/DFE arrangement which addresses this problem by providing a separate DFE for each state of the Viterbi decoder. The tentative signal point decisions along the surviving path of each state are used in the associated DFE to generate an equalized signal for use in calculating the so-called branch metrics for trellis branches emanating from the state in question.

- the present invention is directed to a further enhancement of this approach in the context of systems which use both coded modulation and decision feedback equalization.

- the received stream of transmitted signal points includes first signal points that were generated using a particular coded modulation scheme interspersed with second signal points that were generated in some other way.

- One particular such application is the probabilistic trellis coded modulation scheme of the type disclosed in my co-pending United States patent applications serial no. 08/753,351 filed Nov. 25, 1996 and serial no. 08/855,829 filed May 12, 1997, both hereby incorporated by reference.

- the invention is directed to an advantageous decoder/DFE, i.e. joint Viterbi decoder and DFE, for use in such an environment and, in particular, in accordance with the invention, estimated ISI components for the second signal points are generated in response to tentative decisions as to the first signal points formed by the Viterbi decoder.

- the signal points along the so-called very best surviving path within the Viterbi decoder could be used as the past decisions that are input to a DFE used to form the estimated ISI component for one of the second-illustratively uncoded-signal points and an immediate final decision as to the transmitted signal point could then be made. That decision would also be applied to whatever DFEs are employed in the system (such as the per-state DFEs mentioned above) and used over a number of subsequent signaling intervals to represent the value of the uncoded signal point in question.

- Preferred more powerful, implementations of the invention form not an immediate final decision as to the second-again, illustratively uncoded-signal points but, rather form a tentative decision associated with each Viterbi decoder state using an estimated ISI component provided from a DFE associated with that state.

- Each second-signal-point tentative decision is used to extend the surviving path for the associated state and, in preferred embodiments, to also update its path metric.

- An alternative implementation of the invention is to retain in the above joint decoder/DFE only the surviving paths that are associated with a reduced number, M, of states which have the smaller path metrics, and to use a separate DFE for each of those M states.

- Yet another alternative implementation of the invention is to retain in the joint decoder/DFE some number, M, of the surviving paths which have the smallest path metrics, even if two or more of those paths may come into a given state. For each surviving path, an equalized signal is formed using a DFE the inputs of which are the tentative past decisions from that path, the equalized signal then being used to extend that path and to update its path metric.

- the decoder/DFE of FIG. 1 is illustratively part of a receiving modem in which a signal x n , representing a transmitted signal point, is generated for the n th of a succession of signaling intervals.

- Signal x n was illustratively generated within the modem using conventional front-end steps such as sampling of an incoming line signal received from a telephone channel, demodulation and possibly feedforward equalization.

- Four replicas of x n are formed and a respective estimated intersymbol interference, or ISI, component is subtracted from each replica by a respective one of adders 10, to produce equalized signals x (0) / n through x (3) / n.

- the ISI components are provided by respective ones of decision feedback equalizers 20, as described below.

- the transmitted signal points represented by the x n 's were generated in a transmit modem which used illustratively a probabilistic trellis coded modulation scheme of the type disclosed in my above-cited co-pending '351 and '829 patent applications.

- a transmit modem which used illustratively a probabilistic trellis coded modulation scheme of the type disclosed in my above-cited co-pending '351 and '829 patent applications.

- other codes may be preferred, such as the 64-state code shown in those patent applications.

- Viterbi decoder 30 of the decoder/DFE receives the equalized signals x (0) / n through x (3) / n and provides a so-called final decision P and n - 8 associated with the earlier signal x n-8 .

- the notation here indicates that the final decision that is output by Viterbi decoder 30 as to the value of a particular x n is delayed by, in this example, 8 signaling intervals, this corresponding to the so-called decoding depth of the Viterbi decoder.

- the decoding depth of 8 is used herein for purposes of illustration. In actual practice, the decoding depth depends on the code that is being used and will typically be greater than 8.

- the representation of Viterbi decoder 30 in FIG. 1 includes a representation of the so-called trellis-made up of concatentations of the trellis code's state transition diagram, as described below-and further shows the so-called surviving paths extending through the trellis, each surviving path being associated with, and terminating on, one of the four states of the code, those states being denominated 0, 1, 2 and 3.

- the coder in the transmit modem proceeds through a sequence of states which, in turn, defines a unique sequence of signal point subsets of a signal constellation.

- the coder output is a sequence of signal points each selected from a respective subset of the subset sequence thus defined.

- the task of the Viterbi decoder is to determine what the most likely sequence of signal points actually was, and central to that task is to determine the most likely sequence of transmitted signal points leading into each state of the code at any point in time. These are the aforementioned surviving paths, and the signal points along each path constitute a sequence of tentative signal point decisions.

- a metric is maintained for each surviving path, and, as described below, the current equalized signals x (0) / n through x (3) / n are used to determine new surviving paths having updated path metrics.

- a final decision is thereupon made as to the value of one of the transmitted signal points-specifically one that was transmitted (in this case) 8 signaling intervals earlier.

- Each of DFEs 20 is associated with a particular one of the code states o, 1, 2 and 3.

- each DFE generates its respective ISI estimate as a function of the tentative signal point decisions which lie along the surviving path leading to the code state associated with that DFE.

- the ensemble of tentative signal point decisions along each newly determined surviving path are applied to the associated DFE in prepartion for the generation of next set of ISI estimates to be applied to adders 10.

- a DFE forms its ISI estimate by forming a combination (illustratively a linear combination) of the decisions that have been input to it using an ensemble of coefficients whose values may be adaptively updated.

- each of the equalized signals x (0) / n through x (3) / n is associated with a particular state of the code in that the ISI estimate that was used to form that equalized signal was generated as a function of the then surviving path leading to the state in question.

- the process by which, as mentioned above, the current equalized signals x (0) / n through x (3) / n are used to determine new surviving paths having updated path metrics is carried out by updating unit 31 within Viterbi decoder 30.

- updating unit 31 Associated with the code in question is a so-called state transition diagram which defines, for each current code state, which next state or states the coder is allowed to transition to.

- the code can transition from current state 0 to either next state 0 or next state 1; from current state 1 to either next state 2 or next state 3; from current state 2 to either next state 0 or next state 1 ; and from current state 3 to either next state 2 or next state 3.

- Each such transition is associated with one of the aforementioned constellation subsets, meaning that when the encoder transitions from a particular current state to one of the allowed next states, a signal point will be output by the transmitter which is taken from the subset associated with that state transition.

- a so-called branch metric is calculated for each of the (in this case) eight current-to-next-state transitions defined by the state transition diagram.

- the branch metric for each transition is given by the squared Euclidean distance between one of the equalized signals x (0) / n through x (3) / n and the closest signal point in the subset associated with that transition. That distance is typically referred to as being the distance between hte equalized signal and the associated subset. As shown in FIG.

- 2 illustrative values of the eight branch metrics are 0.4, 0.6, 0.3, 0.5, 0.5, 0.2, 0.2 and 0.1.

- the particular one of the equalized signals x (0) / n through x (3) / n that is used to calculate any given one of the branch metrics is the equalized signal associated with the state from which that branch emanates.

- equalized signal x (0) / n is used in calculating the branch metrics for the branches between current state 0 and next states 0 and 1; x (1) / n is used in calculating the branch metrics for the branches between current state 1 and next states 2 and 3; x (2) / n is used in calculating the branch metrics for the branches between current state 2 and next states 0 and 1; and x (3) / n is used in calculating the branch metrics for the branches between current state 3 and next states 2 and 3.

- Each candidate path has an associated metric given by the sum of the current path metric of the corresponding current state and the branch metric of the corresponding branch, the four current path metrics illustratively being 0.0, 0.2, 0.3 and 0.5.

- the one of those two candidate paths having the smaller path metric is declared the new surviving path for that state and the corresponding path metric becomes the new path metric for that state.

- the candidate paths leading into next state 0 from current states 0 and 2 have metrics of 0.4 (0.0+0.4) and 0.8 (0.3+0.5), respectively, so that the former becomes the surviving path into next state 0.

- the branches shown in solid line within updating unit 31 are the branches of the new surviving paths. (As is well known, normalization or other techniques may be used at this point to prevent the values of the path metrics from becoming so large as to possibly cause register overflow. However, the new path metrics shown in FIG. 2 are the pre-normalized values.)

- the present invention is directed to a joint decoder/DFE which is designed to provide accurate ISI estimates in such an environment, and in accordance with the invention, ISI estimates for the uncoded signal points are generated in response to tentative decisions as to the coded signal points as formed by the Viterbi decoder.

- the signal points along the very best surviving path within the Viterbi decoder can be used as the past decisions input to a DFE used to form the ISI estimate for one of the uncoded signal points and an immediate final decision as to the uncoded signal point can be made. That decision would also be applied to whatever DFEs are employed in the system (such as the per-state DFEs mentioned above) and used over a number of subsequent signaling intervals to represent the value of the uncoded signal point in question.

- FIG. 3 A more powerful, and preferred, implementation of the invention, however, is as shown in FIG. 3.

- Each uncoded signal point tentative decision is used to extend the surviving path for the associated state and, in preferred embodiments, to also update its path metric.

- FIG. 3 is similar to FIG. 1, except that since the received signal x n+1 represents an uncoded signal point, the state transition diagram used in updating unit 31 is that shown in FIG. 4.

- the state transition diagram used by updating unit 31 for uncoded signal points simply comprises four parallel branches, each extending from the current state to the same next state, i.e., current state 0 to next state 0, current state 1 to next state 1, and so forth.

- a decision is made as soon as each signal is received as to whether it represents a coded or uncoded signal point.

- C 1 for the illustrative (n+1) st signaling interval represented by FIG. 3.

- Each one of equalized signals x (0) / n+1 through x (3) / n+1 is used to calculate a respective one of the four branch metrics-given by the squared Euclidian distance between that equalized signal and the closest encoded signal point of the transmit constellation.

- the four branch metrics are illustratively 0.5, 0.2, 0.3 and 0.3.

- each new surviving path is simply an extended version of the surviving path previously extending into that state. Also as before, the very best surviving path is identified-now it is the path leading into state 1-and a final decision P and n-7 is output, it being the signal point along that very best surviving path from 7 signaling intervals earlier.

- FIG. 5 provides a combined block diagram/functional description view of the decoder/DFE of FIGS. I and 3 tailored for probablistic trellis-coded modulation of the type described in the above-cited patent applications.

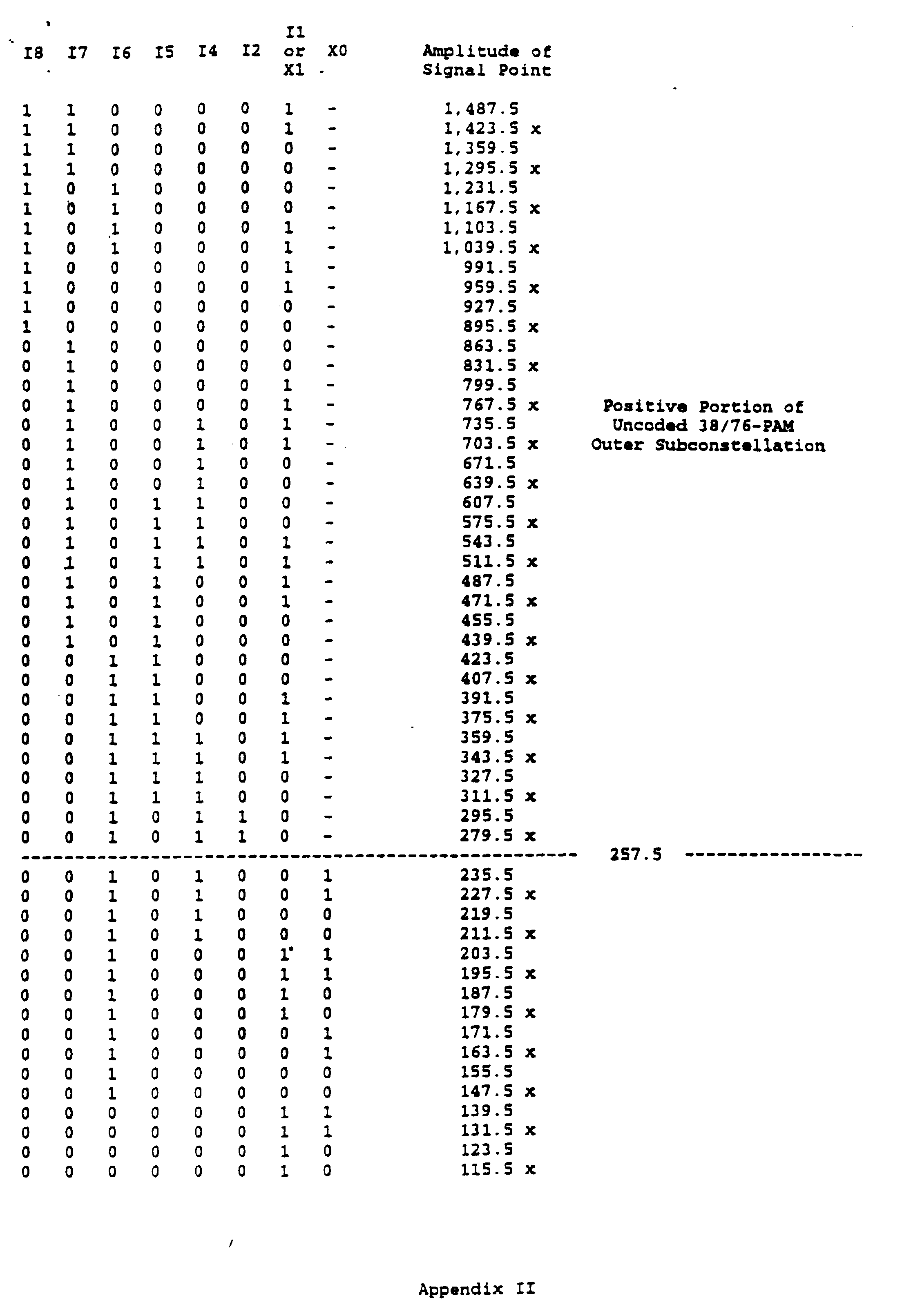

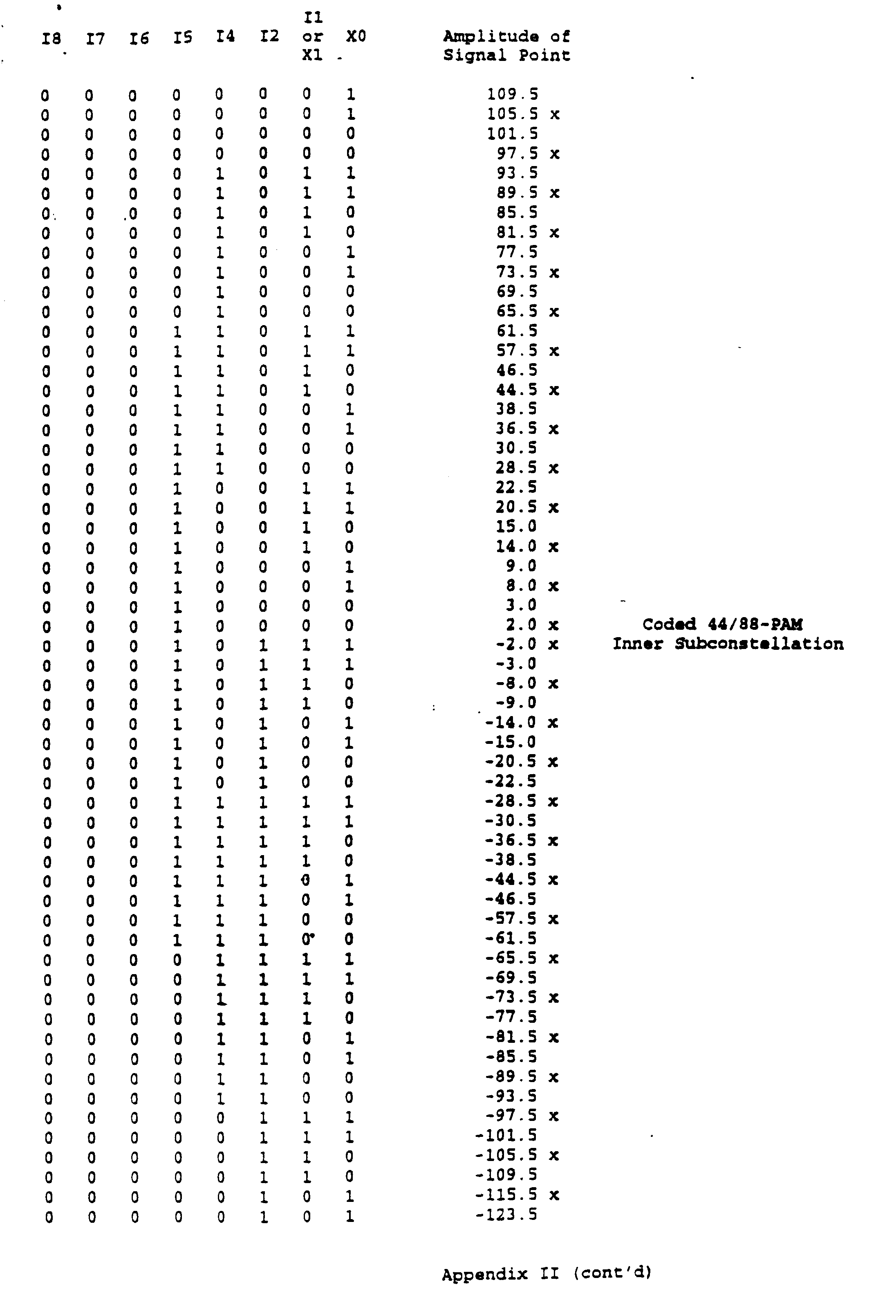

- the coded signal points are the signal points of the so-called inner sub-constellation of the overall signal constellation and the uncoded signal points are the signal points of the so-called outer sub-constellation of the overall signal constellation.

- the code used is that implemented by the coder shown in FIG. 5 of my above-cited '829 patent application. The state transition diagram for that code is shown in the present FIG.

- the received signal x n is processed at block 51 to produce an equalized signal associated with each state of the code.

- the functionality of this block is that for each state, i, of the code, an equalized signal x (i) / n is formed using a DFE whose inputs are the tentative past decisions along the surviving path associated with the i th state.

- a signal indicative of whether the received signal represents a coded, inner sub-constellation, signal point or an uncoded, outer sub-constellation signal point is provided by sub-constellation decision block 52 in a manner to be described. That signal corresponds to one-bit control signal C in FIGS. 1 and 3.

- switch 53 is in the "down" position and the equalized signals are processed at block 56.

- the functionality of this block is that for each state, i, of the code, we use x (i) / n to find a) the closest signal point in the subset associated with each branch and b) the branch metric for each branch emanating from that state based on the state transition diagram of FIG. 6.

- the path metrics and the surviving paths are updated based on the same state transitiondiagram.

- Switch 58 will be in the "down" position at this time so that the flow proceeds to block 59 at which the very best surviving path is found and a final output decision is made.

- switch 53 is in the "up" position and the equalized signals are processed at block 54.

- the functionality of this block is essentially similar to that of block 56 except that the state transition diagram is that shown in FIG. 7.

- the state transition diagram of FIG. 7 comprises a single branch emanating from each current state and extending to the same next state. Each branch is associated with the entire outer sub-constellation.

- the functionality of this block is that for each state, i, of the code, we use x (i) / n to find a) the closest outer sub-constellation signal point and b) the branch metric for the branch emanating from that state. Then, at block 55, the path metric is updated and the surviving path is extended, as noted earler. Switch 58 will be in the "up" position at this time so that the flow proceeds to block 59 at which, as before, the very best surviving path is found and a final output decision is made.

- a decision as to whether signal x n represents an inner or outer sub-constellation signal point would be most accurately made if one were to wait for the Viterbi decoder to provide a final decision as to that signal. However, that decision must be made at sub-constellation decision block 52 soon as the signal is received.

- a combining step 62 and a decision feedback equalization block 61 are used to form an equalized signal x (b) / n at the time signal x n is received, the inputs of block 61 being the tentative past decisions from the very best surviving path of the Viterbi decoder. Based on whether signal x (b) / n falls into the region of the inner or outer subconstellation, subconstellation decision block 52 makes the inner or outer subconstellation decision.

- the constellation may be designed in such a way that the distance between its inner and outer sub-constellations is greater than would be otherwise dictated by other design criteria, e.g., greater than the effective minimum distance of the overall modulation scheme.

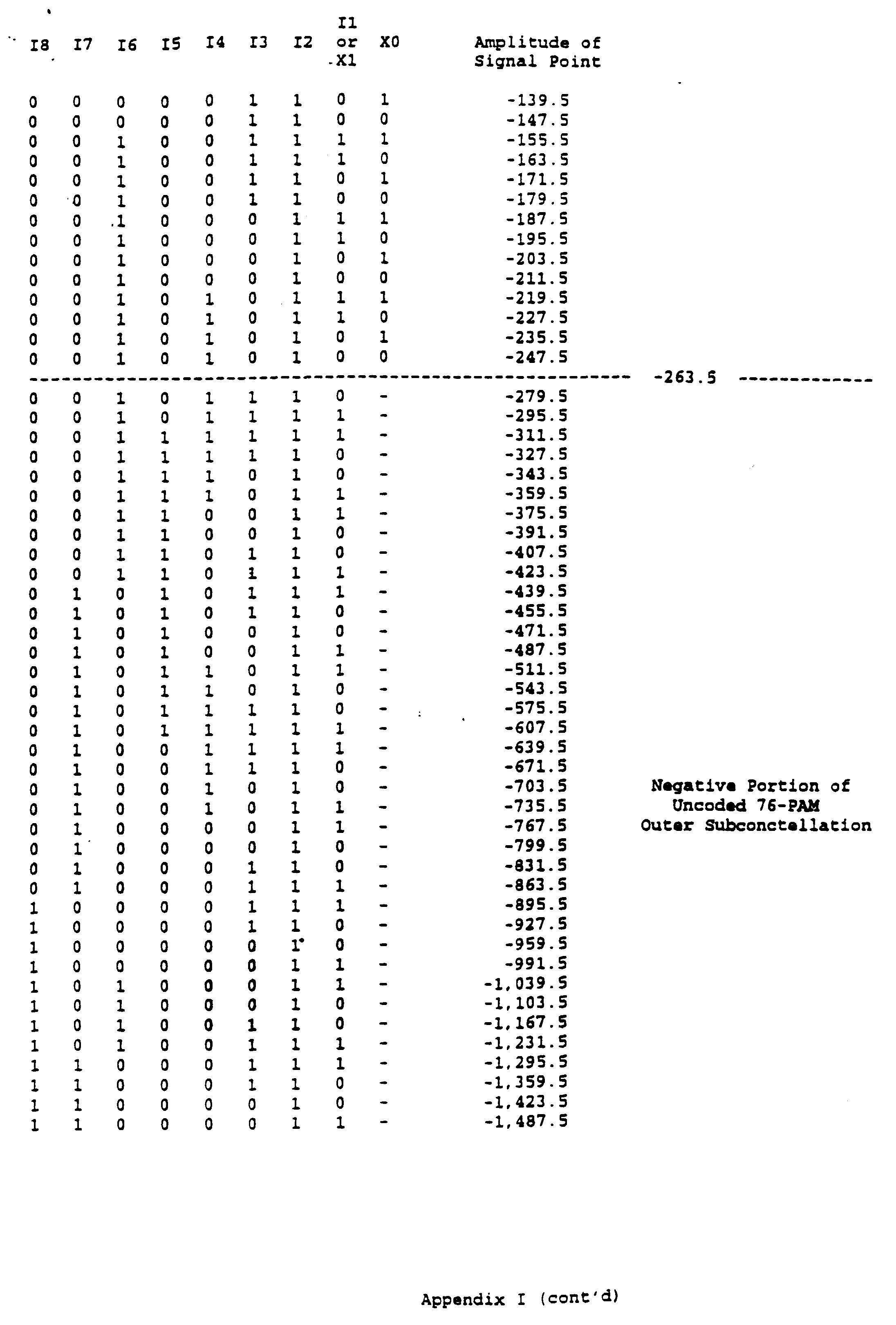

- Such a constellation is shown in Appendix I hereof, this constellation being very similar to that shown in Appendix II of the '829 application except that the distance between the inner and outer sub-constellations has been increased from 16 to 32.

- bit robbing (as described in the '829 application) may occur

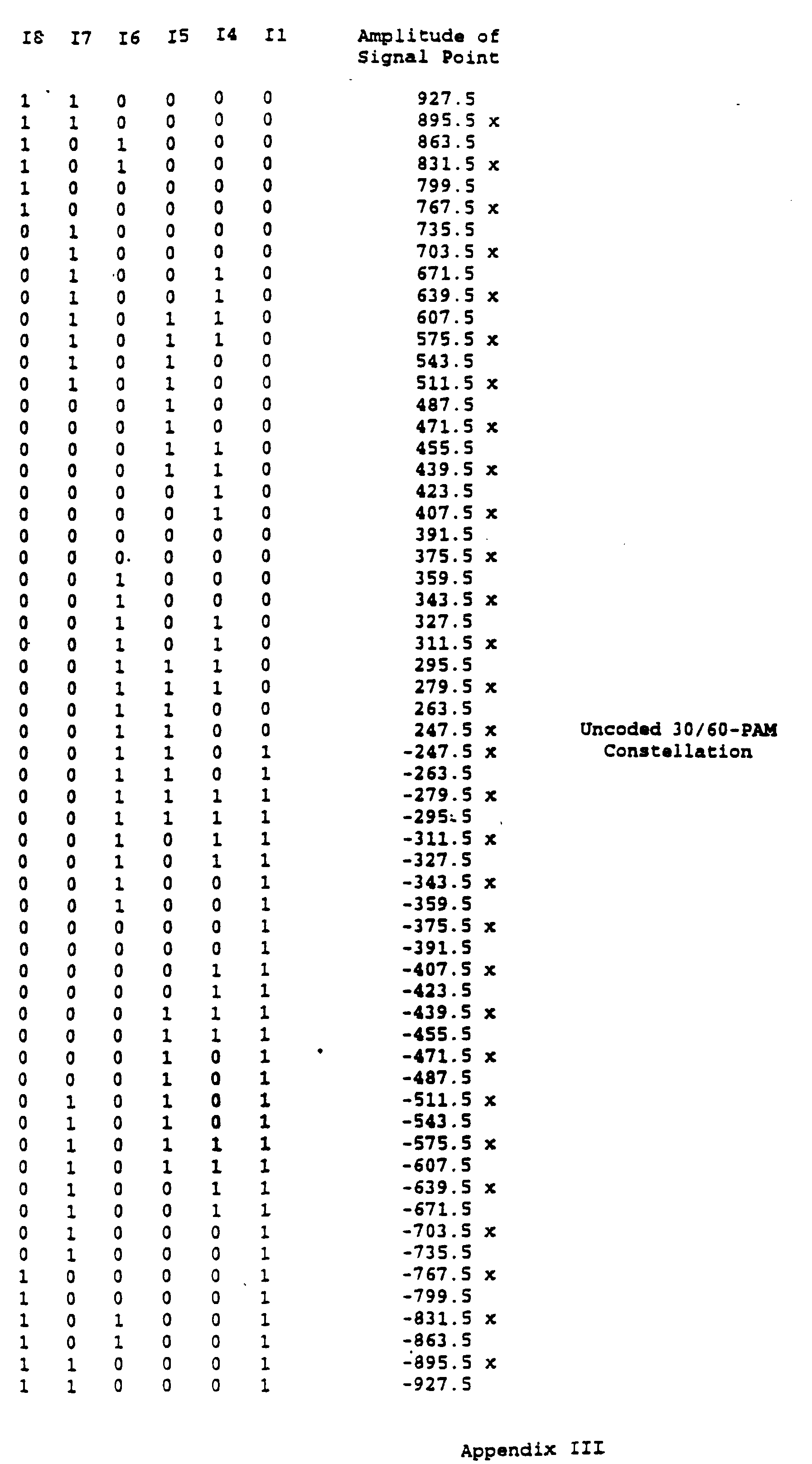

- the constellation shown in Appendix m of the '829 application may be used for the bit-robbed signaling intervals.

- a bit robbing indicator indicating the occurrence of a bit-robbed signaling interval would be applied at blocks 52, 54 and 56, causing the use of that constellation at those blocks.

- the constellation shown in Appendix II hereof may be used instead, it having a distance between the inner and outer sub-constellations of 44, as compared to 16 for the constellation shown in Appendix III of the '829 application.

- a further consideration relative to bit robbing is as follows: On the one hand, although a transmitted signal point can be received as another signal point due to bit robbing, both of those signal points map back into the same transmitted bit pattern so from that standpoint there is no problem, as discussed in my '829 application. A potential problem arises, however, in that the decision as to the amplitude of the signal point is fed back to the DFE and it is possible that, due to noise and impairments between the receiving central office and the receiving modem, the signal point that was transmitted from the central office to the receiving modem may become so displaced that an incorrect decision is made in the receiving modem as to which of the two signal points was sent. The presence of this incorrect decision in the DFE will have a negative effect on the accuracy of the decoding process.

- the constellation of Appendix III is comprised solely of an outer sub-constellation whose smallest magnitude signal points are +/- 247.5. No signal points of smaller amplitude can be used because below the magnitude of 247.5, the distance between each pair of signal points is less than 15, thereby violating the desired design constraint. Moreover, since the minimum distance of 16 between different pairs of signal points of the constellation of Appendix m is already greater than the effective minimum distance of the overall modulation scheme, there would be no benefit to using coding to that constellation. It may be noted that the number of signal point pairs in this constellation is 30. As a consequence, this approach will support one less bit during the bit-robbed intervals than for the case of Appendix II. The choice between the use of the constellations of Appendices II and III will be made based on whether one is willing to endure the lower level of error rate performance provided by the constellation of Appendix II in order to have a higher bandwidth efficiency.

- the other approach is to design the constellation in such a way that the distance between each pair of points that become one another due to bit robbing is much smaller than the effective minimum distance of the overall modulation scheme, so that an error made in the receiver as to which one was transmitted will have a negligible effect on the decoder/DFE performance.

- both of these approaches together, for example, having an inner, coded sub-constellation wherein each pair of signal points are very close together and an uncoded outer sub-constellation wherein each pair of signal points are very far apart, as just described.

- M 16-that is, retaining only the 16 best paths-and achieve essentially the same performance as the much more complex state-oriented approach in which 64 paths-one for each state-are retained. Moreover, in at least one case, I have observed that the simpler path-oriented approach can even outperform the state-oriented approach.

- FIG. 8 shows the implementation of my path-oriented approach for joint decoder/DFE in the present context of probablistic TCM. More particularly, various elements shown in FIG. 8 correspond, either exactly, or with modifications, to those shown in FIG. 5. Those that correspond exactly bear the same reference numeral, whereas blocks 51, 54, 55, 56 and 57 are replaced in FIG. 8 with blocks 851, 854, 855, 856 and 857.

- blocks 851, 854 and 856 the calculations that are carried out vis-a-vis the equalized signal x (i) / n are carried out for each M best surviving paths rather than for each state of the code. And in blocks 855 and 857 a new set of M best surviving paths are identified, along with their associated path metrics, rather than, as in FIG. 5, identifying an updated surviving path, and its associated metric, for each state.

- any element expressed as a means for performing a specified function is intended to encompass any way of performing that function including, for example, a) a combination of circuit elements which performs that function or b) software in any form (including, therefore, firmware, microcode or the like) combined with appropriate circuitry for executing that software to perform the function.

- the invention is defined by such claims resides in the fact that the functionalities provided by the various recited means are combined and brought together in the manner which the claims call for. Applicant thus regards any means which can provide those functionalities as equivalent as those shown herein.

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Artificial Intelligence (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Probability & Statistics with Applications (AREA)

- Theoretical Computer Science (AREA)

- Error Detection And Correction (AREA)

- Digital Transmission Methods That Use Modulated Carrier Waves (AREA)

- Detection And Correction Of Errors (AREA)

- Cable Transmission Systems, Equalization Of Radio And Reduction Of Echo (AREA)

Abstract

Description

Claims (9)

- A maximum-likelihood decoding method for decoding a stream of signal points, a first plurality of said signal points having been generated using a predetermined code defined by a state transition diagram and a second plurality of said signal points having been generated not using said predetermined code, said method comprising the steps ofa) maintaining path metrics respectively associated with at least ones of the states of said code,b) responsive to each received first plurality signal point, generating for each of said ones of said states, a branch metric associated with each next state to which said each state is connected by a particular branch in the state transition diagram, and computing an updated path metric for at least ones of said states based on their associated path metrics and the generated branch metrics, andc) responsive to each received second plurality signal point, generating for each of said ones of said states a branch metric associated only with that particular state, and computing an updated path metric for at least ones of said states based on the existing path metrics and the generated branch metrics,

- The invention of claim 1 wherein said first plurality signal points are representative of signal points of a first signal constellation, wherein each of the branches of said state transition diagram is associated with a respective subset of said first signal constellation and wherein in step b) each said branch metric is a function of the distance within said constellation between said each received first plurality signal point and the subset associated with each said particular branch.

- The invention of claims 1 or 2 wherein said second plurality signal points are signal points of a second signal constellation, and wherein in step c) said branch metric is a function of the distance in said second signal constellation between said each received second plurality signal point and the nearest signal point of said second signal constellation.

- The invention of claim 3 wherein said first and second signal constellations are respective sub-constellations of an overall signal constellation.

- The invention of claim 3 comprising the further step of forming decisions as to values of said stream of signal points in response to the updated path metrics.

- A method for use in a Viterbi decoder for decoding a stream of signal points corrupted by intersymbol interference, the method comprising the steps ofa first plurality of said signal points having been generated using a particular trellis code and a second plurality of said signal points having been generated elsewise.a) generating in response to each received signal point a plurality of equalized signal points, each equalized signal point being generated as a function of a respective estimate of the intersymbol interference component of said each received signal point, each estimate being a function of a respective present surviving path of said Viterbi decoder,b) generating updated surviving paths for said Viterbi decoder as a function of the set of equalized signal points, andc) forming a decision as to a particular one of the signal points of said stream as a function at least of a particular one of the updated surviving paths,

- The invention of claim 6 wherein in step a) said each estimate is formed by a decision feedback equalizer which utilizes as its input decisions tentatative decisions as to the values of said stream of signal points which lie along the respective present surviving path.

- The invention of claim 6 wherein each of said present surviving paths has an associated metric and wherein step b) comprises the steps ofgenerating a path metric for each of a plurality of candidate paths, each candidate path comprising a respective one of the present surviving paths extended from its respective terminating state of the trellis code i) along a branch of the trellis code state transition diagram, if said received signal point is one of said first plurality signal points, or ii) to that same state, if said received signal point is one of said second plurality signal points, andselecting ones of the candidate paths to be said updated surviving paths, said selecting being in response to the path metrics generated for the candidate paths.

- A method for decoding a stream of signal points, a first plurality of said signal points having been generated using a predetermined trellis code defined by a state transition diagram, a second plurality of said signal points having been generated not using said predetrmined code, said method comprising the steps ofmaintaining a path metric associated with each of a plurality of surviving paths through the code trellis, each of said surviving paths terminating on a respective state of the code,responsive to a received one of said signal points, generating an updated path metric for each of a plurality of candidate paths, each candidate path comprising a respective one of the surviving paths extended from the respective terminating state a) along a branch of said state transition diagram, if said received signal point is one of said first plurality signal point, or b) to that same state, if said received signal point is one of said second plurality signal points,identifying new surviving paths from the candidate paths as a function of the updated path metrics, andforming a decision as to the value of a previously received one of said signal points as a function of at least one of said new surviving paths.

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US5156197P | 1997-07-02 | 1997-07-02 | |

| US51561P | 1997-07-02 | ||

| US936649 | 1997-09-24 | ||

| US08/936,649 US5872817A (en) | 1997-07-02 | 1997-09-24 | Joint viterbi decoder and decision feedback equalizer |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| EP0889612A2 true EP0889612A2 (en) | 1999-01-07 |

| EP0889612A3 EP0889612A3 (en) | 2000-08-09 |

| EP0889612B1 EP0889612B1 (en) | 2011-05-18 |

Family

ID=26729558

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| EP98304933A Expired - Lifetime EP0889612B1 (en) | 1997-07-02 | 1998-06-23 | Maximum-likelihood decoding method for coded modulation |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US5872817A (en) |

| EP (1) | EP0889612B1 (en) |

| JP (1) | JP3280622B2 (en) |

| KR (1) | KR100583897B1 (en) |

Cited By (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1999049631A1 (en) * | 1998-03-25 | 1999-09-30 | Ascom Powerline Communications Ag | Iterative equalization and decoding |

| WO2000028691A2 (en) * | 1998-11-09 | 2000-05-18 | Broadcom Corporation, Et Al. | Multi-pair gigabit ethernet transceiver |

| WO2000048369A1 (en) * | 1999-02-09 | 2000-08-17 | Lucent Technologies Inc. | Termination of coded or uncoded modulation with path-oriented decoder |

| WO2001019011A1 (en) * | 1999-09-10 | 2001-03-15 | Ericsson Inc. | Combined equalization and decoding technique |

| FR2798540A1 (en) * | 1999-09-13 | 2001-03-16 | France Telecom | PROCESS FOR DECODING AND JOINT EQUALIZATION OF A DIGITAL SIGNAL PROTECTED BY A CODE DEFINED BY A LATTICE |

| US6226332B1 (en) | 1998-11-13 | 2001-05-01 | Broadcom Corporation | Multi-pair transceiver decoder system with low computation slicer |

| US6249544B1 (en) | 1998-11-13 | 2001-06-19 | Broadcom Corporation | System and method for high-speed decoding and ISI compensation in a multi-pair transceiver system |

| US6253345B1 (en) | 1998-11-13 | 2001-06-26 | Broadcom Corporation | System and method for trellis decoding in a multi-pair transceiver system |

| US6252904B1 (en) | 1998-11-13 | 2001-06-26 | Broadcom Corporation | High-speed decoder for a multi-pair gigabit transceiver |

| WO2001069872A2 (en) * | 2000-03-10 | 2001-09-20 | Broadcom Corporation | Architecture for high-speed decision feedback sequence estimation |

| US6459746B2 (en) | 1998-11-09 | 2002-10-01 | Broadcom Corporation | Multi-pair gigabit ethernet transceiver |

| WO2002084965A1 (en) * | 2001-04-10 | 2002-10-24 | Koninklijke Philips Electronics N.V. | A two stage equalizer for trellis coded systems |

| WO2002087180A1 (en) * | 2001-04-23 | 2002-10-31 | Koninklijke Philips Electronics N.V. | Apparatus and method for decision feedback sequence estimation for reduction of error propagation in a decision feedback equalizer |

| WO2002087181A1 (en) * | 2001-04-23 | 2002-10-31 | Koninklijke Philips Electronics N.V. | Generation of decision feedback equalizer data using trellis decoder traceback output in an atsc hdtv receiver |

| WO2004014032A2 (en) * | 2002-08-01 | 2004-02-12 | Aware, Inc. | Multi-tap frequency domain equalization with decision feedback and trellis decoding |

| US6754294B1 (en) | 1999-11-12 | 2004-06-22 | Cornell Research Foundation, Inc. | Dual equalizer for use in an receiver and method of operation |

| FR2866167A1 (en) * | 2004-02-05 | 2005-08-12 | Samsung Electronics Co Ltd | Decision feed-back equalizer for use in digital video broadcasting, has filter including set of filter updaters to receive set of decisions from decoder, and adder updating filter coefficients |

| KR100606326B1 (en) * | 2001-06-07 | 2006-07-28 | 마이크로나스 세미컨덕터, 인코포레이티드 | Error generation for adaptive equalizer |

| US7092438B2 (en) | 2002-01-22 | 2006-08-15 | Siemens Communications, Inc. | Multilevel decision feedback equalizer |

| US7656976B2 (en) | 2001-08-02 | 2010-02-02 | Aware, Inc. | Systems and methods for multicarrier modulation using multi-tap frequency-domain equalizer and decision feedback |

| CN102882817A (en) * | 2012-09-26 | 2013-01-16 | 华为技术有限公司 | Equalizer circuit, data transmission system and equalization method |

Families Citing this family (47)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6195386B1 (en) * | 1994-09-26 | 2001-02-27 | Texas Instruments Incorporated | Parallel decision feedback equalizer |

| US6151370A (en) * | 1998-02-12 | 2000-11-21 | Lucent Technologies Inc. | Path-oriented decoder for signal-dependent noise |

| US6553518B1 (en) | 1999-03-08 | 2003-04-22 | International Business Machines Corporation | Severe error detectors, methods and computer program products that use constellation specific error event thresholds to detect severe error events during demodulation of a signal comprising symbols from a plurality of symbol constellations |

| US6661847B1 (en) | 1999-05-20 | 2003-12-09 | International Business Machines Corporation | Systems methods and computer program products for generating and optimizing signal constellations |

| US6570919B1 (en) * | 1999-07-30 | 2003-05-27 | Agere Systems Inc. | Iterative decoding of data packets employing decision feedback equalization |

| US6356586B1 (en) * | 1999-09-03 | 2002-03-12 | Lucent Technologies, Inc. | Methods and apparatus for parallel decision-feedback decoding in a communication system |

| US6816545B1 (en) | 1999-10-29 | 2004-11-09 | International Business Machines Corporation | Systems, methods and computer program products for identifying digital impairments in modems based on clusters and/or skips in pulse code modulation signal levels |

| US6754258B1 (en) | 1999-10-29 | 2004-06-22 | International Business Machines Corporation | Systems, methods and computer program products for averaging learned levels in the presence of digital impairments based on patterns |

| US6650657B1 (en) | 1999-10-29 | 2003-11-18 | International Business Machines Corporation | Systems, methods and computer program products for identifying digital impairments in modem signals |

| US6505222B1 (en) | 1999-10-29 | 2003-01-07 | International Business Machines Corporation | Systems methods and computer program products for controlling undesirable bias in an equalizer |

| US6611563B1 (en) | 1999-10-29 | 2003-08-26 | International Business Machines Corporation | Systems, methods and computer program products for data mode refinement of modem constellation points |

| US6823017B1 (en) | 1999-10-29 | 2004-11-23 | International Business Machines Corporation | Systems, methods and computer program products for filtering glitches from measured values in a sequence of code points |

| US6765955B1 (en) | 1999-10-29 | 2004-07-20 | International Business Machines Corporation | Methods, systems and computer program products establishing a communication configuration for a modem connection to compensate for echo noise |

| US6662322B1 (en) | 1999-10-29 | 2003-12-09 | International Business Machines Corporation | Systems, methods, and computer program products for controlling the error rate in a communication device by adjusting the distance between signal constellation points |

| US6823004B1 (en) | 1999-10-29 | 2004-11-23 | International Business Machines Corporation | Methods, systems and computer program products for monitoring performance of a modem during a connection |

| US6826157B1 (en) | 1999-10-29 | 2004-11-30 | International Business Machines Corporation | Systems, methods, and computer program products for controlling data rate reductions in a communication device by using a plurality of filters to detect short-term bursts of errors and long-term sustainable errors |

| US6792004B1 (en) | 1999-10-29 | 2004-09-14 | International Business Machines Corporation | Systems, methods and computer program products for averaging learned levels in the presence of robbed-bit signaling based on proximity |

| US6792040B1 (en) | 1999-10-29 | 2004-09-14 | International Business Machines Corporation | Modems having a dual power mode capability and methods of operating same |

| JP3515720B2 (en) | 1999-11-22 | 2004-04-05 | 松下電器産業株式会社 | Viterbi decoder |

| US6690739B1 (en) | 2000-01-14 | 2004-02-10 | Shou Yee Mui | Method for intersymbol interference compensation |

| EP1119145A1 (en) * | 2000-01-20 | 2001-07-25 | TELEFONAKTIEBOLAGET LM ERICSSON (publ) | Parallel decision feedback equalizer with adaptive thresholding based on noise estimates |

| US6600617B1 (en) | 2000-03-07 | 2003-07-29 | International Business Machines Corporation | Method and apparatus for adjusting digital filter taps based upon minimization of viterbi margin counts |

| US7106813B1 (en) * | 2000-03-16 | 2006-09-12 | Qualcomm, Incorporated | Method and apparatus for combined soft-decision based interference cancellation and decoding |

| EP1224783A2 (en) * | 2000-04-06 | 2002-07-24 | Lucent Technologies Inc. | Upstream data transmission |

| US6760385B1 (en) * | 2000-05-30 | 2004-07-06 | Adtran, Inc. | Universal parallel processing decoder |

| US7072392B2 (en) * | 2000-11-13 | 2006-07-04 | Micronas Semiconductors, Inc. | Equalizer for time domain signal processing |

| US6940557B2 (en) * | 2001-02-08 | 2005-09-06 | Micronas Semiconductors, Inc. | Adaptive interlace-to-progressive scan conversion algorithm |

| US6829297B2 (en) * | 2001-06-06 | 2004-12-07 | Micronas Semiconductors, Inc. | Adaptive equalizer having a variable step size influenced by output from a trellis decoder |

| US7418034B2 (en) * | 2001-06-19 | 2008-08-26 | Micronas Semiconductors. Inc. | Combined trellis decoder and decision feedback equalizer |

| US20030206053A1 (en) * | 2002-04-04 | 2003-11-06 | Jingsong Xia | Carrier recovery for DTV receivers |

| US20030235259A1 (en) * | 2002-04-04 | 2003-12-25 | Jingsong Xia | System and method for symbol clock recovery |

| US6995617B2 (en) * | 2002-04-05 | 2006-02-07 | Micronas Semiconductors, Inc. | Data-directed frequency-and-phase lock loop |

| US7321642B2 (en) * | 2002-04-05 | 2008-01-22 | Micronas Semiconductors, Inc. | Synchronization symbol re-insertion for a decision feedback equalizer combined with a trellis decoder |

| US7272203B2 (en) * | 2002-04-05 | 2007-09-18 | Micronas Semiconductors, Inc. | Data-directed frequency-and-phase lock loop for decoding an offset-QAM modulated signal having a pilot |

| US7376181B2 (en) * | 2002-04-05 | 2008-05-20 | Micronas Semiconductors, Inc. | Transposed structure for a decision feedback equalizer combined with a trellis decoder |

| US6980059B2 (en) * | 2002-04-05 | 2005-12-27 | Micronas Semiconductors, Inc. | Data directed frequency acquisition loop that synchronizes to a received signal by using the redundancy of the data in the frequency domain |

| ATE381195T1 (en) * | 2002-08-01 | 2007-12-15 | Research In Motion Ltd | MOBILE STATION FOR MAINTAINING ALWAYS-ON WIRELESS INTERNET PROTOCOL COMMUNICATIONS AND METHOD THEREOF |

| KR20040025516A (en) * | 2002-09-19 | 2004-03-24 | 삼성전자주식회사 | Channel Equalizer of Single carrier Receiver and a method equalizing thereof |

| CN100413295C (en) * | 2002-11-01 | 2008-08-20 | 上海奇普科技有限公司 | Self Adaptive equalizer for improving error signal production |

| US7003716B2 (en) * | 2002-12-26 | 2006-02-21 | Zydas Technology Corp. | Method and apparatus for using multi-dimensional trellis codes over multi-path channels |

| US20090252202A1 (en) * | 2004-12-10 | 2009-10-08 | Koninklijke Philips Electronics, N.V. | Method and apparatus for enhanced decoding in multi-band ultra-wideband communications |

| CN100364257C (en) * | 2005-05-26 | 2008-01-23 | 上海奇普科技有限公司 | Time-domain adaptive aqualizer combined with NR code |

| US20070183489A1 (en) * | 2006-02-07 | 2007-08-09 | Samsung Electronics Co., Ltd. | Apparatus for decoding a signal and method thereof and a trellis coded modulation decoder and method thereof |

| US7912119B2 (en) * | 2007-08-23 | 2011-03-22 | Freescale Semiconductor, Inc. | Per-survivor based adaptive equalizer |

| EP2382748B1 (en) * | 2008-12-31 | 2014-12-24 | ST-Ericsson SA | Process and receiver for interference cancellation of interfering base stations in a synchronized ofdm system |

| US20130028299A1 (en) * | 2011-07-26 | 2013-01-31 | Himax Media Solutions, Inc. | Adaptive ethernet transceiver with joint decision feedback equalizer and trellis decoder |

| US8938035B1 (en) | 2012-02-29 | 2015-01-20 | Marvell International Ltd. | System and method for transferring data over a two-pair communication system |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US617678A (en) | 1899-01-10 | emery | ||

| US5953376A (en) | 1996-09-26 | 1999-09-14 | Lucent Technologies Inc. | Probabilistic trellis coded modulation with PCM-derived constellations |

| US6157678A (en) | 1996-12-18 | 2000-12-05 | Lucent Technologies Inc. | Probabilistic trellis/coded modulation with PCM-derived constellations |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5056117A (en) * | 1989-08-07 | 1991-10-08 | At&T Bell Laboratories | Decision feedback equalization with trellis coding |

| US5775855A (en) * | 1995-06-08 | 1998-07-07 | Valenite Inc. | Cutting insert and cutter for milling |

| JP3171772B2 (en) * | 1995-08-23 | 2001-06-04 | 沖電気工業株式会社 | Viterbi decoding method and Viterbi decoding device |

-

1997

- 1997-09-24 US US08/936,649 patent/US5872817A/en not_active Expired - Lifetime

-

1998

- 1998-06-23 EP EP98304933A patent/EP0889612B1/en not_active Expired - Lifetime

- 1998-07-02 KR KR1019980027735A patent/KR100583897B1/en not_active IP Right Cessation

- 1998-07-02 JP JP18706998A patent/JP3280622B2/en not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US617678A (en) | 1899-01-10 | emery | ||

| US5953376A (en) | 1996-09-26 | 1999-09-14 | Lucent Technologies Inc. | Probabilistic trellis coded modulation with PCM-derived constellations |

| US6157678A (en) | 1996-12-18 | 2000-12-05 | Lucent Technologies Inc. | Probabilistic trellis/coded modulation with PCM-derived constellations |

Cited By (54)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1999049631A1 (en) * | 1998-03-25 | 1999-09-30 | Ascom Powerline Communications Ag | Iterative equalization and decoding |

| US7733952B2 (en) | 1998-11-09 | 2010-06-08 | Broadcom Corporation | Multi-pair gigabit Ethernet transceiver having adaptive disabling of circuit elements |

| US6477200B1 (en) | 1998-11-09 | 2002-11-05 | Broadcom Corporation | Multi-pair gigabit ethernet transceiver |

| WO2000028691A3 (en) * | 1998-11-09 | 2000-11-23 | Broadcom Corp | Multi-pair gigabit ethernet transceiver |

| US6459746B2 (en) | 1998-11-09 | 2002-10-01 | Broadcom Corporation | Multi-pair gigabit ethernet transceiver |

| US7570701B2 (en) | 1998-11-09 | 2009-08-04 | Broadcom Corporation | Multi-pair gigabit ethernet transceiver |

| US8306104B2 (en) | 1998-11-09 | 2012-11-06 | Broadcom Corporation | Method and device for multi-dimensional processing using a single-state decision feedback equalizer |

| WO2000028691A2 (en) * | 1998-11-09 | 2000-05-18 | Broadcom Corporation, Et Al. | Multi-pair gigabit ethernet transceiver |

| US6731691B2 (en) | 1998-11-09 | 2004-05-04 | Broadcom Corp. | Multi-pair gigabit ethernet transceiver having adaptive disabling of circuit elements |

| US7801240B2 (en) | 1998-11-09 | 2010-09-21 | Broadcom Corporation | Multi-pair gigabit ethernet transceiver |

| US7801241B2 (en) | 1998-11-09 | 2010-09-21 | Broadcom Corporation | Multi-pair gigabit Ethernet transceiver |

| US8451885B2 (en) | 1998-11-09 | 2013-05-28 | Broadcom Corporation | Multi-pair gigabit ethernet transceiver having adaptive disabling of circuit elements |

| US6253345B1 (en) | 1998-11-13 | 2001-06-26 | Broadcom Corporation | System and method for trellis decoding in a multi-pair transceiver system |

| US6249544B1 (en) | 1998-11-13 | 2001-06-19 | Broadcom Corporation | System and method for high-speed decoding and ISI compensation in a multi-pair transceiver system |

| US8320443B2 (en) | 1998-11-13 | 2012-11-27 | Broadcom Corporation | System and method for high-speed decoding and ISI compensation in a multi-pair transceiver system |

| US7466751B2 (en) | 1998-11-13 | 2008-12-16 | Broadcom Corporation | System and method for high-speed decoding and ISI compensation in a multi-pair transceiver system |

| US7630434B2 (en) | 1998-11-13 | 2009-12-08 | Broadcom Corporation | High-speed decoder for a multi-pair gigabit transceiver |

| US6226332B1 (en) | 1998-11-13 | 2001-05-01 | Broadcom Corporation | Multi-pair transceiver decoder system with low computation slicer |

| US8201045B2 (en) | 1998-11-13 | 2012-06-12 | Broadcom Corporation | System and method for trellis decoding in a multi-pair transceiver system |

| US6959038B2 (en) | 1998-11-13 | 2005-10-25 | Broadcom Corporation | High-speed decoder for a multi-pair gigabit transceiver |

| US6252904B1 (en) | 1998-11-13 | 2001-06-26 | Broadcom Corporation | High-speed decoder for a multi-pair gigabit transceiver |

| US6947482B2 (en) | 1998-11-13 | 2005-09-20 | Broadcom Corporation | System and method for high-speed decoding and ISI compensation in a multi-pair transceiver system |

| US6721916B2 (en) | 1998-11-13 | 2004-04-13 | Broadcom Corporation | System and method for trellis decoding in a multi-pair transceiver system |

| US6373900B2 (en) | 1998-11-13 | 2002-04-16 | Broadcom Corporation | Multi-pair transceiver decoder system with low computation slicer |

| US7434134B2 (en) | 1998-11-13 | 2008-10-07 | Broadcom Corporation | System and method for trellis decoding in a multi-pair transceiver system |

| US8259787B2 (en) | 1998-11-13 | 2012-09-04 | Broadcom Corporation | High-speed decoder for a multi-pair gigabit transceiver |

| US7711077B2 (en) | 1998-11-13 | 2010-05-04 | Broadcom Corporation | System and method for high-speed decoding and ISI compensation in a multi-pair transceiver system |

| WO2000048369A1 (en) * | 1999-02-09 | 2000-08-17 | Lucent Technologies Inc. | Termination of coded or uncoded modulation with path-oriented decoder |

| US6327317B1 (en) | 1999-09-10 | 2001-12-04 | Telefonaktiebolaget Lm Ericsson (Publ) | Combined equalization and decoding techniques |

| WO2001019011A1 (en) * | 1999-09-10 | 2001-03-15 | Ericsson Inc. | Combined equalization and decoding technique |

| US7012976B1 (en) | 1999-09-13 | 2006-03-14 | France Telecom | Method for decoding and of joint equalization of a digital signal protected by a code defined by a trellis |

| WO2001020861A1 (en) * | 1999-09-13 | 2001-03-22 | France Telecom | Method for joint decoding and equalising of a digital signal protected by a trellis-defined code |

| FR2798540A1 (en) * | 1999-09-13 | 2001-03-16 | France Telecom | PROCESS FOR DECODING AND JOINT EQUALIZATION OF A DIGITAL SIGNAL PROTECTED BY A CODE DEFINED BY A LATTICE |

| US6754294B1 (en) | 1999-11-12 | 2004-06-22 | Cornell Research Foundation, Inc. | Dual equalizer for use in an receiver and method of operation |

| US7177353B2 (en) | 2000-03-10 | 2007-02-13 | Broadcom Corporation | Architecture for very high-speed decision feedback sequence estimation |

| US8934527B2 (en) | 2000-03-10 | 2015-01-13 | Broadcom Corporation | Architecture for very high-speed decision feedback sequence estimation |

| WO2001069872A2 (en) * | 2000-03-10 | 2001-09-20 | Broadcom Corporation | Architecture for high-speed decision feedback sequence estimation |

| WO2001069872A3 (en) * | 2000-03-10 | 2002-06-27 | Broadcom Corp | Architecture for high-speed decision feedback sequence estimation |

| US7738549B2 (en) | 2000-03-10 | 2010-06-15 | Broadcom Corporation | Architecture for very high-speed decision feedback sequence estimation |

| KR100871072B1 (en) * | 2001-04-10 | 2008-11-28 | 코닌클리케 필립스 일렉트로닉스 엔.브이. | A two stage equalizer for trellis coded systems |

| WO2002084965A1 (en) * | 2001-04-10 | 2002-10-24 | Koninklijke Philips Electronics N.V. | A two stage equalizer for trellis coded systems |

| WO2002087181A1 (en) * | 2001-04-23 | 2002-10-31 | Koninklijke Philips Electronics N.V. | Generation of decision feedback equalizer data using trellis decoder traceback output in an atsc hdtv receiver |

| KR100915846B1 (en) * | 2001-04-23 | 2009-09-07 | 코닌클리케 필립스 일렉트로닉스 엔.브이. | Apparatus and method for decision feedback sequence estimation for reduction of error propagation in a decision feedback equalizer |

| US6734920B2 (en) | 2001-04-23 | 2004-05-11 | Koninklijke Philips Electronics N.V. | System and method for reducing error propagation in a decision feedback equalizer of ATSC VSB receiver |

| WO2002087180A1 (en) * | 2001-04-23 | 2002-10-31 | Koninklijke Philips Electronics N.V. | Apparatus and method for decision feedback sequence estimation for reduction of error propagation in a decision feedback equalizer |

| KR100606326B1 (en) * | 2001-06-07 | 2006-07-28 | 마이크로나스 세미컨덕터, 인코포레이티드 | Error generation for adaptive equalizer |

| US7656976B2 (en) | 2001-08-02 | 2010-02-02 | Aware, Inc. | Systems and methods for multicarrier modulation using multi-tap frequency-domain equalizer and decision feedback |

| US7092438B2 (en) | 2002-01-22 | 2006-08-15 | Siemens Communications, Inc. | Multilevel decision feedback equalizer |

| WO2004014032A2 (en) * | 2002-08-01 | 2004-02-12 | Aware, Inc. | Multi-tap frequency domain equalization with decision feedback and trellis decoding |

| WO2004014032A3 (en) * | 2002-08-01 | 2004-04-08 | Aware Inc | Multi-tap frequency domain equalization with decision feedback and trellis decoding |

| FR2866167A1 (en) * | 2004-02-05 | 2005-08-12 | Samsung Electronics Co Ltd | Decision feed-back equalizer for use in digital video broadcasting, has filter including set of filter updaters to receive set of decisions from decoder, and adder updating filter coefficients |

| US7706436B2 (en) | 2004-02-05 | 2010-04-27 | Samsung Electronics Co., Ltd. | Decision-feedback equalizer and method of updating filter coefficients |

| CN102882817A (en) * | 2012-09-26 | 2013-01-16 | 华为技术有限公司 | Equalizer circuit, data transmission system and equalization method |

| CN102882817B (en) * | 2012-09-26 | 2017-07-14 | 华为技术有限公司 | Equalizing circuit, data transmission system and equalization methods |

Also Published As

| Publication number | Publication date |

|---|---|

| KR19990013737A (en) | 1999-02-25 |

| JP3280622B2 (en) | 2002-05-13 |

| US5872817A (en) | 1999-02-16 |

| EP0889612A3 (en) | 2000-08-09 |

| JPH11150481A (en) | 1999-06-02 |

| KR100583897B1 (en) | 2006-11-30 |

| EP0889612B1 (en) | 2011-05-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5872817A (en) | Joint viterbi decoder and decision feedback equalizer | |

| CA2032867C (en) | Maximum likelihood sequence estimation apparatus | |

| Kubo et al. | An adaptive maximum-likelihood sequence estimator for fast time-varying intersymbol interference channels | |

| Raheli et al. | Per-survivor processing: A general approach to MLSE in uncertain environments | |

| US6178209B1 (en) | Method of estimating trellis encoded symbols utilizing simplified trellis decoding | |

| Eyuboglu et al. | Reduced-state sequence estimation for coded modulation of intersymbol interference channels | |

| EP1151589B1 (en) | Modem with a reduced state maximum likelihood sequence estimator | |

| US7042938B2 (en) | Soft bit computation for a reduced state equalizer | |

| US6151370A (en) | Path-oriented decoder for signal-dependent noise | |

| US6269116B1 (en) | Method and arrangement for demodulating data symbols | |

| US6233286B1 (en) | Path-oriented decoder using refined receiver trellis diagram | |

| US20130064332A1 (en) | Method and apparatus for generating soft bit values in reduced-state equalizers | |

| JPH08307283A (en) | Device and method for estimating maximum likelihood series | |

| JPH11508114A (en) | Equalizer with reduced state sequence estimation method for digital transmission equipment receiver. | |

| KR100644952B1 (en) | Decision feedback equalizer for a digital signal receiving system | |

| US5905743A (en) | Apparatus, methods and computer program products for sequential maximum likelihood estimating communications signals using whitening path metrics | |

| Giridhar et al. | Joint demodulation of cochannel signals using MLSE and MAPSD algorithms | |

| CA2361374C (en) | Termination of coded or uncoded modulation with path-oriented decoder | |

| US6782046B1 (en) | Decision-directed adaptation for coded modulation | |

| WO2002071710A1 (en) | Method for enhancing soft-value information | |

| JP4024364B2 (en) | Digital transmission system, digital signal receiver and digital signal receiving method | |

| JP2003506912A (en) | Method of generating reliability information for channel decoding in wireless receiver and corresponding wireless receiver | |

| JP2560893B2 (en) | Data signal receiver | |

| Mak et al. | Detection of trellis-coded modulation on time-dispersive channels | |

| JPH10262090A (en) | Maximum likelihood sequence estimation device nd maximum likelihood sequence estimation method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PUAI | Public reference made under article 153(3) epc to a published international application that has entered the european phase |

Free format text: ORIGINAL CODE: 0009012 |

|

| AK | Designated contracting states |

Kind code of ref document: A2 Designated state(s): DE FR GB |

|

| AX | Request for extension of the european patent |

Free format text: AL;LT;LV;MK;RO;SI |

|

| PUAL | Search report despatched |

Free format text: ORIGINAL CODE: 0009013 |

|

| AK | Designated contracting states |

Kind code of ref document: A3 Designated state(s): AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE |

|

| AX | Request for extension of the european patent |

Free format text: AL;LT;LV;MK;RO;SI |

|

| RIC1 | Information provided on ipc code assigned before grant |

Free format text: 7H 04L 25/03 A, 7H 04L 27/34 B, 7H 04L 1/00 B |

|

| 17P | Request for examination filed |

Effective date: 20010125 |

|

| AKX | Designation fees paid |

Free format text: DE FR GB |

|

| 17Q | First examination report despatched |

Effective date: 20070425 |

|

| RAP3 | Party data changed (applicant data changed or rights of an application transferred) |

Owner name: LUCENT TECHNOLOGIES INC. |

|

| APBK | Appeal reference recorded |

Free format text: ORIGINAL CODE: EPIDOSNREFNE |

|

| APBN | Date of receipt of notice of appeal recorded |

Free format text: ORIGINAL CODE: EPIDOSNNOA2E |

|

| APBR | Date of receipt of statement of grounds of appeal recorded |

Free format text: ORIGINAL CODE: EPIDOSNNOA3E |

|

| APBV | Interlocutory revision of appeal recorded |

Free format text: ORIGINAL CODE: EPIDOSNIRAPE |

|

| GRAP | Despatch of communication of intention to grant a patent |

Free format text: ORIGINAL CODE: EPIDOSNIGR1 |

|

| RTI1 | Title (correction) |

Free format text: MAXIMUM-LIKELIHOOD DECODING METHOD FOR CODED MODULATION |

|

| GRAS | Grant fee paid |

Free format text: ORIGINAL CODE: EPIDOSNIGR3 |

|

| GRAA | (expected) grant |

Free format text: ORIGINAL CODE: 0009210 |

|

| REG | Reference to a national code |

Ref country code: GB Ref legal event code: FG4D |

|

| REG | Reference to a national code |

Ref country code: DE Ref legal event code: R096 Ref document number: 69842273 Country of ref document: DE Effective date: 20110630 |

|

| PLBE | No opposition filed within time limit |

Free format text: ORIGINAL CODE: 0009261 |

|

| STAA | Information on the status of an ep patent application or granted ep patent |

Free format text: STATUS: NO OPPOSITION FILED WITHIN TIME LIMIT |

|

| 26N | No opposition filed |

Effective date: 20120221 |

|

| REG | Reference to a national code |

Ref country code: DE Ref legal event code: R097 Ref document number: 69842273 Country of ref document: DE Effective date: 20120221 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: FR Payment date: 20140609 Year of fee payment: 17 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: GB Payment date: 20150527 Year of fee payment: 18 |

|

| REG | Reference to a national code |

Ref country code: FR Ref legal event code: ST Effective date: 20160229 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: FR Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20150630 |

|

| GBPC | Gb: european patent ceased through non-payment of renewal fee |

Effective date: 20160623 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: GB Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20160623 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: DE Payment date: 20170522 Year of fee payment: 20 |

|

| REG | Reference to a national code |

Ref country code: DE Ref legal event code: R071 Ref document number: 69842273 Country of ref document: DE |