CN101847997A - 一种9b/10b编解码器及其实现方法 - Google Patents

一种9b/10b编解码器及其实现方法 Download PDFInfo

- Publication number

- CN101847997A CN101847997A CN201010160763A CN201010160763A CN101847997A CN 101847997 A CN101847997 A CN 101847997A CN 201010160763 A CN201010160763 A CN 201010160763A CN 201010160763 A CN201010160763 A CN 201010160763A CN 101847997 A CN101847997 A CN 101847997A

- Authority

- CN

- China

- Prior art keywords

- data

- polarity

- special character

- processing module

- encoder

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000000034 method Methods 0.000 title claims abstract description 34

- 230000000295 complement effect Effects 0.000 claims description 8

- 230000003111 delayed effect Effects 0.000 claims description 4

- 230000001934 delay Effects 0.000 claims description 2

- 230000008569 process Effects 0.000 abstract description 6

- 230000014509 gene expression Effects 0.000 abstract description 4

- 238000004891 communication Methods 0.000 description 11

- 230000005540 biological transmission Effects 0.000 description 7

- 238000006243 chemical reaction Methods 0.000 description 7

- 238000010586 diagram Methods 0.000 description 7

- 238000005516 engineering process Methods 0.000 description 7

- 230000008901 benefit Effects 0.000 description 4

- 238000011084 recovery Methods 0.000 description 4

- 230000007547 defect Effects 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

Images

Landscapes

- Compression, Expansion, Code Conversion, And Decoders (AREA)

Abstract

本发明公开了一种9B/10B编码器,所述编码器中,待编码数据包括特殊字符和普通数据,而普通数据又可以分为可以简单变换以及不可简单变换两类,对于可以简单变换的普通数据,通过主编码器在9B数据的最左侧附加1位0来实现;采用查找表的方式实现不可简单变换的普通数据以及特殊字符的编码。本发明还公开了基于相同构思的9B/10B解码器。相比较于现有技术中通过逻辑表达式实现9B/10B编解码,本发明的实现过程更为简洁,并易于被开发人员理解;本发明的编解码极性计算器和线路极性计算器相比较于现有技术中大量使用加法器和减法器的实现方案来说,更适合在低成本的FPGA中实现。

Description

技术领域

本发明涉及通信技术领域,特别涉及线路编解码技术领域,尤其涉及一种9B/10B编解码器及其实现方法。

背景技术

随着线路传输带宽的不断增加,并行通信技术成为进一步提高数据传输速率的瓶颈,基于串行器和解串器(SERDES)的串行通信技术逐渐成为高速数据通信的主流。基于SERDES的串行通信技术能够充分利用传输通道的信道容量,减少传输通道和器件的个数,从而显著地降低系统成本。

SERDES是串行器和解串器的简称。基于SERDES的串行通信系统如图1和图2所示。其中图1示出的是串行器的结构,图2示出的是解串器的结构。

如图1所示,串行器105的主要功能是把并行数据转换成串行数据,其中包括并串转换器102、锁相环103和发送器104。锁相环103接收发送时钟,并向并串转换器102发送锁频的时钟信号;并串转换器102接收来自编码器101编码后的并行输入数据,根据所述时钟信号将并行数据转换为串行数据,并经由发送器104发出该串行数据。

如图2所示,解串器205的主要功能是先从串行数据流中恢复时钟和数据,然后把恢复后的串行数据转换成并行数据。其中,接收器201接收串行输入数据,将其分别发送至串并转换器202以及时钟和数据恢复电路204。时钟和数据恢复电路204从所述串行输入数据中恢复出时钟信号,将所述时钟信号发送至串并转换器202,并同时对外输出该时钟信号;而串并转换器202根据所述时钟信号将接收的串行输入信号转换为并行信号,并发送至解码器203,解码器203将其解码后输出。

常用SERDES的串并比有1∶4,1∶8,1∶10等。基于SERDES的串行通信技术的关键技术之一是解串器的时钟和数据恢复。影响解串器时钟和数据恢复性能的主要因素有:串行数据流的电平变换和串行数据流的直流平衡。电平变换是指串行数据从“0”到“1”的变换或从“1”到“0”的变换,直流平衡是指串行数据流中0和1的个数基本相同。

为了保证串行数据流有充足的电平变换和直流平衡特性,需要对输入到串行器的并行数据进行处理,现有技术中有如下两种解决方案:

第一种是编码技术,常用的线路编码有4B/5B以及8B/10B。4B/5B编码把4位数据编码成5位数据,8B/10B编码把8位数据编码成10位数据。编码技术的优点是具有充足的电平变换和直流平衡特征,但其缺点是有开销,4B/5B、8B/10B编码的开销高达20%。

第二种是扰码技术,扰码是使用伪随机序列对数据进行加扰,进而打乱原始数据的分布。扰码技术的优点是无开销,但其也有缺点,对于某些特定的输入数据序列,扰码器可能会输出全0或全1,导致扰码器无法工作;扰码的另一个缺点是解扰时会导致误码增殖,即当传输线路发生单比特错误时,接收端解扰器会输出多个误码。

为了解决8B/10B编码的高开销和扰码等固有缺陷,专利(US PatNo.7405697B1、US Pat No.7471217B2、US Pat No.6747580B1)等提出一种新的编码方式,即9B/10B编码。9B/10B编码把9位数据编码成10位数据,同时保证串行数据流中有充足的电平变换和直流平衡。采用9B/10B编码线路的开销减少到10%。

其中,US Pat No.7405697B1给出9B/10B编解码器的码表以及实现编解码器的逻辑表达式,但是其实现过程非常复杂。US Pat No.7471217B2给出9B/10B编解码器的实现过程,但其没有给出码表,也没有给出极性控制的方法。US PatNo.6747580B1给出9B/10B编解码的码表以及实现编解码器的逻辑框图,但其极性计算器的实现非常复杂,需要使用加法器和减法器,不易在低成本的现场可编程逻辑器件(FPGA)中实现。

发明内容

有鉴于此,本发明提出了一种9B/10B编码器、解码器及其实现方法,本发明方案可以在低成本的FPGA中实现。

本发明实施例提出的一种9B/10B编码器,包括第1级处理模块(301),第2级处理模块(302)和第3级处理模块(303);

所述第1级处理模块(301)用于在输入的9B数据的最左边附加1位“0”后构成的10B数据,并计算所述10B数据的数据极性;将所述数据极性以及输入的9B数据原样输出至第2级处理模块(302);

所述第2级处理模块(302)预先设置了针对不同数据类别的编码方式,采用每一种预置的编码方式将所述9B数据分别转换为10B数据,并将每一种预置编码方式得到的10B数据均输出至第3级处理模块(303);第2级处理模块(302)还根据来自第1级处理模块(301)的数据极性,生成与预置的编码方式对应的有效标志,并将所述有效标志输出至第3级处理模块(303);

所述第3级处理模块(303)用于根据接收的有效标志,选择接收与所述有效标志对应的预置的编码方式得到的10B数据。

较佳地,所述第2级处理模块(302)包括主编码器(305)、第二编码器(306)和特殊字符编码器(307);

主编码器(305)用于将来自第1级处理模块(301)的9B数据的最左边附加1位0构成10B数据,然后再根据该10B数据的数据极性和线路的极性,将所述10B数据或其补码输出至第3级处理模块(303);

第二编码器(306)中预先设置普通数据查找表,所述普通数据查找表定义104个9B普通数据与其对应的10B普通数据;第二编码器(306)用于根据来自第1级处理模块(301)的9B数据查找所述普通数据查找表,若找到对应的10B普通数据,则生成第二编码器有效标志,并将所得10B普通数据以及所述第二编码器有效标志输出至第3级处理模块(303);

特殊字符编码器(307)中预先设置特殊字符查找表,所述特殊字符查找表定义11组9B特殊字符与10B特殊字符的对应关系;特殊字符编码器(307)用于根据来自第1级处理模块(301)的9B数据查找所述特殊字符查找表,若找到对应的10B特殊字符,则生成特殊字符编码器有效标志,并将所得10B特殊字符以及所述特殊字符编码器有效标志输出至第3级处理模块(303);

所述第3级处理模块(303)在收到特殊字符编码器有效标志时,选择来自特殊字符编码器(307)的10B特殊字符作为最终输出信号输出;否则,若收到第二编码器有效标志时,选择来自第二编码器(306)的10B普通数据作为最终输出信号输出;以上两种情况均不成立,则选择来自主编码器(305)的10B普通数据作为最终输出信号输出。

较佳地,所述第1级处理模块(301)包括编码极性计算器(304);所述计算所述10B数据的数据极性通过极性查找表实现。

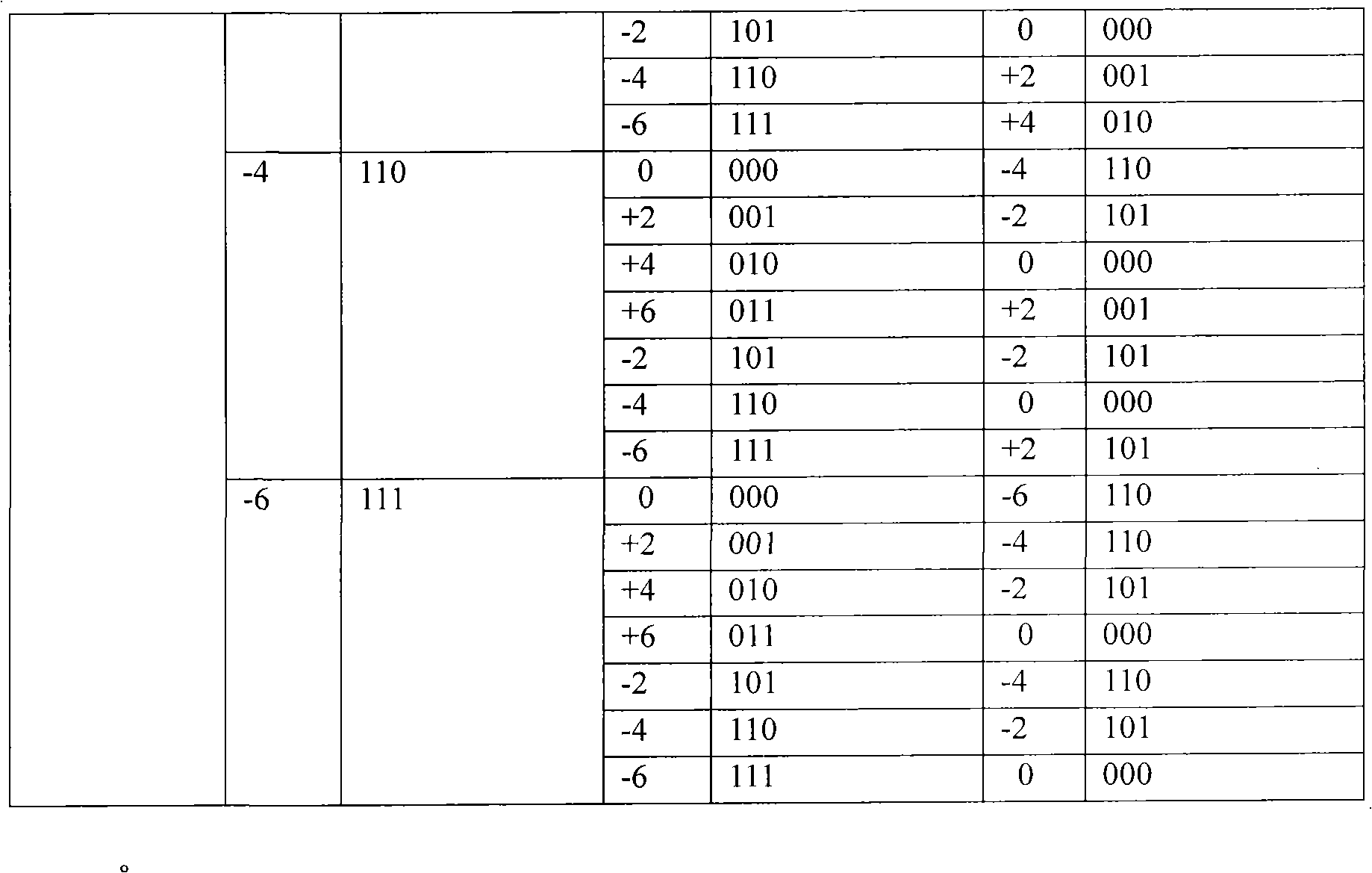

较佳地,所述数据极性查找表中,000表示极性是0,001表示极性是+2,010表示极性是+4,011表示极性是+6,101表示极性是-2,110表示极性是-4,111表示极性是-6。

较佳地,所述第1级处理模块(301)将输入的9B数据原样输出至第2级处理模块(302)为:第1级处理模块(301)将输入的9B数据延迟一个时钟周期后输出至第2级处理模块(302)。

较佳地,所述特殊字符查找表中的11组特殊字符分别为:K.001和K.101、K.002和K.102、K.003和K.103、K.004和K.104、K.005和K.105、K.006和K.106、K.007和K.107、K.008和K.108、K.009和K.109以及K.00A和K.10A。

较佳地,所述第2级处理模块(302)进一步包括线路极性计算器(308);

线路极性计算器(308)用于接收来自编码极性计算器(304)的9B普通数据kin以及数据极性sdisp,还接收自身输出的线路极性rdisp,根据如下表格输出线路极性rdisp:

较佳地,所述主编码器(305)接收所述编码极性计算器(304)输出的9B普通数据和数据极性,以及所述线路极性计算器(308)输出的线路极性;

若所述线路极性是0时,主编码器(305)将所述9B普通数据附加1位0得到的10B数据输出;

若所述线路极性是正时,如果数据极性是正的,主编码器(305)将所述9B普通数据附加1位0得到的10B数据取反后输出;如果数据极性是0或负的,主编码器(305)将所述9B普通数据附加1位0得到的10B数据直接输出;

若所述线路极性是负时,如果数据极性是负的,主编码器(305)将所述9B普通数据附加1位0得到的10B数据取反后输出;如果数据极性是0或正的,主编码器(305)将所述9B普通数据附加1位0得到的10B数据直接输出。

本发明实施例还提出一种9B/10B解码器,包括第1级处理模块(401)和第2级处理模块(402),第1级处理模块401用于接收10B数据,第2级处理模块(402)用于输出解码得到的9B数据;

所述第1级处理模块401包括主解码器(403),第二解码器(404)和特殊字符解码器(405);所述主解码器403通过判断接收的10B编码的最高位是否是1,如果是1,把10B编码的低9位取反后输出;否则,直接把10B编码的低9位输出至第2级处理模块(402);

所述第二解码器(404)中预先设置普通数据查找表,所述普通数据查找表定义104个9B普通数据与其对应的10B普通数据;所述第二解码器(404)用于根据接收的10B数据查找所述普通数据查找表,若找到对应的9B普通数据,则生成第二解码器有效标志,并将所得9B普通数据以及所述第二解码器有效标志输出至第2级处理模块(402);

所述特殊字符解码器(405)中预先设置特殊字符查找表,所述特殊字符查找表定义11组9B特殊字符与10B特殊字符的对应关系;特殊字符解码器(405)用于根据接收的10B数据查找所述特殊字符查找表,若找到对应的9B特殊字符,则生成特殊字符解码器有效标志,并将所得9B特殊字符以及所述特殊字符解码器有效标志输出至第2级处理模块(402);

所述第2级处理模块(402)在收到特殊字符解码器有效标志时,选择来自特殊字符解码器(405)的9B特殊字符作为最终输出信号输出;否则,若收到第二解码器有效标志时,选择来自第二解码器(404)的9B普通数据作为最终输出信号输出;以上两种情况均不成立,则选择来自主解码器(403)的9B普通数据作为最终输出信号输出。

本发明实施例提出一种9B/10B编码器的实现方法,预先设置了针对不同数据类别的编码方式;该实现方法包括如下步骤:

A1:在输入的9B数据的最左边附加1位“0”后构成10B数据,并计算所述10B数据的极性;

B1、采用每一种预置的编码方式将所述9B数据分别转换为10B数据;根据所述数据极性,生成与预置的编码方式对应的有效标志;

C1、根据所述有效标志,选择接收与所述有效标志对应的预置的编码方式得到的10B数据。

所述预先设置了针对不同数据类别的编码方式包括:预先设置特殊字符查找表和普通数据查找表,所述特殊字符查找表定义11组9B特殊字符与10B特殊字符的对应关系,所述普通数据查找表定义104个9B普通数据与其对应的10B普通数据;

所述步骤B1包括:

B11、判断步骤A输出的9B数据是否属于预先定义的特殊字符,若是,执行步骤B12,否则执行步骤B13;

B12、生成特殊字符编码器输出有效标志,并按照预先设置的特殊字符查找表找到对应的10B特殊字符;然后转至步骤C1;B13、判断所述9B数据是否与预先设置的普通数据查找表中的任一个9B普通数据中的相匹配,若是,则生成第二编码器输出有效标志,并根据所述普通数据查找表找到对应的10B普通数据;否则,执行步骤B14;

B14、在所述9B数据的最左边附加1位0构成10B数据,然后再根据该10B数据的极性和线路的极性,把10B数据转换为其补码或不进行转换;

所述步骤C1包括:

在收到特殊字符编码器有效标志时,将步骤B12得到的10B特殊字符作为最终输出信号输出;否则,若收到第二编码器有效标志时,将步骤B13得到的10B普通数据作为最终输出信号输出;以上两种情况均不成立,则将步骤B14得到的10B数据作为最终输出信号输出。

较佳地,步骤A1所述计算所述10B数据的数据极性通过极性查找表实现。

较佳地,所述数据极性查找表中,000表示极性是0,001表示极性是+2,010表示极性是+4,011表示极性是+6,101表示极性是-2,110表示极性是-4,111表示极性是-6。

较佳地,所述特殊字符查找表中的11组特殊字符分别为:K.001和K.101、K.002和K.102、K.003和K.103、K.004和K.104、K.005和K.105、K.006和K.106、K.007和K.107、K.008和K.108、K.009和K.109以及K.00A和K.10A。

较佳地,所述步骤B14包括:

若所述线路极性是0时,将所述9B普通数据附加1位0得到的10B数据输出;

若所述线路极性是正时,如果数据极性是正的,将所述9B普通数据附加1位0得到的10B数据取反后输出;如果数据极性是0或负的,将所述9B普通数据附加1位0得到的10B数据直接输出;

若所述线路极性是负时,如果数据极性是负的,将所述9B普通数据附加1位0得到的10B数据取反后输出;如果数据极性是0或正的,将所述9B普通数据附加1位0得到的10B数据直接输出。

本发明实施例还提出一种9B/10解码器的实现方法,预先设置特殊字符查找表和普通数据查找表,所述特殊字符查找表定义11组9B特殊字符与10B特殊字符的对应关系,所述普通数据查找表定义104个9B普通数据与其对应的10B普通数据;该方法包括如下步骤:

A2、判断接收的10B编码的最高位是否是1,如果是1,把10B编码的低9位取反后输出至第2级处理模块(402);否则,直接把10B编码的低9位输出至第2级处理模块(402);或者,

根据接收的10B数据查找所述普通数据查找表,若找到对应的9B普通数据,则生成第二解码器有效标志,并将所得9B普通数据以及所述第二解码器有效标志输出至第2级处理模块(402);或者,

根据接收的10B数据查找所述特殊字符查找表,若找到对应的9B特殊字符,则生成特殊字符解码器有效标志,并将所得9B特殊字符以及所述特殊字符解码器有效标志输出至第2级处理模块(402);

B2、所述第2级处理模块(402)在收到特殊字符解码器有效标志时,选择来自特殊字符解码器(405)的9B特殊字符作为最终输出信号输出;否则,若收到第二解码器有效标志时,选择来自第二解码器(404)的9B普通数据作为最终输出信号输出;以上两种情况均不成立,则选择来自主解码器(403)的9B普通数据作为最终输出信号输出。

从以上技术方案可以看出,本发明实施例的9B/10B编码器中,待编码数据包括特殊字符和普通数据,而普通数据又可以分为可以简单变换以及不可简单变换两类,对于可以简单变换的普通数据,通过主编码器在9B数据的最左侧附加1位0来实现;第二编码器、特殊字符编码器则分别采用查找表的方式实现不可简单变换的普通数据以及特殊字符的编码。对于解码器采用类似的思路实现。

相比较于现有技术中通过逻辑表达式实现9B/10编解码,本发明的实现过程更为简洁,并易于被开发人员理解;本发明的编解码极性计算器和线路极性计算器相比较于现有技术中大量使用加法器和减法器的实现方案来说,更适合在低成本的FPGA中实现。

附图说明

图1为现有技术的SERDES通信系统的串行器的结构示意图;

图2为现有技术的SERDES通信系统的解串器的结构示意图;

图3为本发明实施例提出的9B/10B编码器结构示意图;

图4为本发明实施例提出的9B/10B解码器结构示意图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚,以下通过实施例对本发明方案进行详细阐述。

为了便于表述,首先对本发明实施例提出的9B/10B编码器的编码前的数据和编码后的数据的比特顺序对应的阿拉伯数字进行规定,具体如表1所示,其中A和I分别对应于编码前的数据的最低比特位和最高比特位,a和j分别对应于编码后的数据的最低比特位和最高比特位。

| 编码前的数据 | 编码后的数据 |

| 9=>j | |

| 8=>I | 8=>i |

| 7=>H | 7=>h |

| 6=>G | 6=>g |

| 5=>F | 5=>f |

| 4=>E | 4=>e |

| 3=>D | 3=>d |

| 2=>C | 2=>c |

| 1=>B | 1=>b |

| 0=>A | 0=>a |

表1比特顺序对应表

编码前的数据用字母V表示。编码前的数据分成两类:普通数据和特殊字符,分别用D.X和K.X表示。其中,字母“D”标识的编码前的数据是普通数据,字母“K”标识的编码前的数据是特殊字符。编码前的数据长度为9位,数据位从高到低依次为“IHGFEDCBA”。编码后的数据长度为10位,数据位从高到低依次为“jihgfedcba”。

极性(Disparity)也称不平衡性,用来表示二进制编码数据块中1和0的个数之差。正极性(Positive Disparity)表示数据块中的1的个数比0的个数多,正N极性中的“N”,表示数据块中1的个数与0的个数之差。负极性(NegativeDisparity)表示数据块中的1的个数比0的个数少。负N极性中的“N”,表示数据块中0的个数与1的个数之差。N为自然数。本文所述极性包括数据极性和线路极性。

运行不一致性(Running Disparity)表示连续的串行码流中1和0的个数之差。

运行长度(Run Length)表示连续的串行码流中,连续的1或0的个数。本发明实施例提出的9B/10B编码器中,除了特殊字符的编码允许运行长度大于或等于8外,普通数据编码或两个连续的普通数据编码之间不允许出现运行长度大于或等于8的情况。

9位数据共有512个组合,10位数据共有1024个组合。在10位数据的1024个组合中,具有0极性的编码有252个,正2、负2极性的码型各有210个,正4、负4极性的编码各有120个,正6、负6极性的编码各有45个,正8、负8极性的编码各有10个,正10、负10极性的编码各有1个。此处所述极性均为数据极性。

为了保证编码后的数据有充足的电平变换,同时保证数据编码或两个连续的数据编码之间连续0或连续1的长度不大于7,需要对1024个10位数据进行过滤,过滤规则包括:

A、去掉那些连续0或连续1个数大于等于8的编码;

B、去掉那些编码前后0到1或1到0变换数目小于3的编码;

C、去掉那些首端连续0或连续1的数目大于3的编码;以及

D、去掉那些末端连续0或连续1的数目大于4的编码。

本发明实施例提出的9B/10B编码器的编码特征包括:

10B编码的极性在[-6、+6]之间;

除特殊字符的编码外,10B编码的连续0或1的最大值是7;以及

每个10B码组至少有3次0到1或1到0的变换。

本发明实施例提出的9B/10B编码器中,9位数据的512个组合中,有408个数据的编码可以通过在9位数据的最左端附加1个0来完成,只有104个数据的编码需要使用查找表来实现。

本发明实施例提出一种9B/10B编码器的实现方法,预先设置特殊字符查找表和普通数据查找表,所述特殊字符查找表定义11组9B特殊字符与10B特殊字符的对应关系,所述普通数据查找表定义104个9B普通数据与其对应的10B普通数据;该实现方法包括如下步骤:

A1:在输入的9B数据的最左边附加1位“0”后构成10B数据,并计算所述10B数据的极性,将极性输出至第2级处理模块(302),并将输入的9B数据延迟一个时钟周期后输出;

B1、判断步骤A输出的9B数据是否属于预先定义的特殊字符,若是,执行步骤C1,否则执行步骤D1;

C1、生成特殊字符编码器输出有效标志,并按照预先设置的特殊字符查找表找到对应的10B特殊字符,将所述特殊字符编码器输出有效标志和10B特殊字符输出,并结束本流程;

D1、判断所述9B数据是否与预先设置的普通数据查找表中的任一个9B普通数据中的相匹配,若是,则生成第二编码器输出有效标志,并根据所述普通数据查找表将对应的10B普通数据输出;否则,在所述9B数据的最左边附加1位0构成10B数据,然后再根据该10B数据的极性和线路的极性,输出该10B数据或其补码。

本发明实施例提出的一种9B/10B解码器的实现方法,预先设置特殊字符查找表和普通数据查找表,所述特殊字符查找表定义11组9B特殊字符与10B特殊字符的对应关系,所述普通数据查找表定义104个9B普通数据与其对应的10B普通数据;该方法包括如下步骤:

A2、判断接收的10B编码的最高位是否是1,如果是1,把10B编码的低9位取反后输出至第2级处理模块(402);否则,直接把10B编码的低9位输出至第2级处理模块(402);或者,

根据接收的10B数据查找所述普通数据查找表,若找到对应的9B普通数据,则生成第二解码器有效标志,并将所得9B普通数据以及所述第二解码器有效标志输出至第2级处理模块(402);或者,

根据接收的10B数据查找所述特殊字符查找表,若找到对应的9B特殊字符,则生成特殊字符解码器有效标志,并将所得9B特殊字符以及所述特殊字符解码器有效标志输出至第2级处理模块(402);

B2、所述第2级处理模块(402)在收到特殊字符解码器有效标志时,选择来自特殊字符解码器(405)的9B特殊字符作为最终输出信号输出;否则,若收到第二解码器有效标志时,选择来自第二解码器(404)的9B普通数据作为最终输出信号输出;以上两种情况均不成立,则选择来自主解码器(403)的9B普通数据作为最终输出信号输出。

图3为本发明实施例提出的9B/10B编码器的电路原理图。如图3所示,所述9B/10B编码器采用3级处理模块结构:第1级处理模块301(电路-01),第2级处理模块302(电路-02,电路-03,电路-04,电路-05)和第3级处理模块303(电路-06)。每级处理模块的处理时长占用1个时钟周期,因此9B/10B编码器完成一次编码需要3个时钟周期。

第1级处理模块301由编码极性计算器304(电路-01)构成。

编码极性计算器304用于在输入的9B数据的最左边附加1位“0”后构成的10B数据,并计算所述10B数据的极性;将所述极性输出,并将输入的9B数据原样输出至第2级处理模块302。9B数据在最左边附加1位0后构成的10B数据的极性为+2、+4、+6、0、-2、-4或-6。极性计算器通过数据极性查找表实现。

编码极性计算器304有2个输入信号:

din:输入9B普通数据;

kin:输入9B特殊字符;以及

3个输出信号:

dout:输入的9B普通数据延时1个时钟周期后输出;

kout:输入的9B特殊字符延时1个时钟周期后输出;

sdisp:9B数据在最左边附加1位0后构成的10B数据的极性,用3位编码表示:000表示极性是0,001表示极性是+2,010表示极性是+4,011表示极性是+6,101表示极性是-2,110表示极性是-4,111表示极性是-6。所述编码形式仅为举例,实际的编码与极性的对应关系可以不限于此。

第2级处理模块302由主编码器305(电路-02)、第二编码器306(电路-03)、特殊字符编码器307(电路-04)和线路极性编码器308构成。

1.主编码器(第一编码器)305

9B数据的512个组合中,408个通过主编码器得到10B编码,主编码器305得到的10B编码如果极性不等于零,则其有一个互补的编码,如果极性等于零,则其只有一个编码(即不存在补码)。

主编码器305有3个输入信号:

din:连接到编码极性计算器304的输出dout;

rdisp:连接到线路极性计算器308的输出rdisp;

sdisp:连接到编码极性计算器304的输出sdisp;以及

1个输出信号:pri_code。

主编码器305首先在输入的9B数据的最左边附加1位0构成10B数据,然后再根据该10B数据的极性(sdisp)和线路的极性(rdisp),决定把10B数据还是其补码赋给pri_code并输出该信号pri_code。

其中,rdisp用3位编码表示,000表示极性是0,001表示极性是+2,010表示极性是+4,011表示极性是+6,101表示极性是-2,110表示极性是-4,111表示极性是-6。所述编码形式仅为举例,实际的编码与极性的对应关系可以不限于此。

当rdisp是0时,编码器可以输出零极性、正极性编码或负极性编码,因此,把附加1位0的10B数据(可能是正极性,负极性或零极性)直接赋给pri_code。

当rdisp是正时,编码器必须输出一个负极性或零极性的编码而不能输出一个正极性的编码,因此,如果sdisp是正的,把附加1位0的10B数据取反后(得到一个负极性编码)赋给pri_code,如果sdisp是0或负的,把附加1位0的10B数据直接赋给pri_code。

当rdisp是负时,编码器必须输出一个正极性或零极性的编码而不能输出一个负极性的编码,因此,如果sdisp是负的,把附加1位0的10B数据取反后(得到一个正极性编码)赋给pri_code,如果sdisp是0或正的,把附加1位0的10B数据直接赋给pri_code。

2.第二编码器306

512个9B数据中,104个数据通过第二编码器306得到10B编码,第二编码器306得到的10B编码极性都是零,且编码是唯一的。

第二编码器306通过普通数据查找表实现。所述普通数据查找表中包含104个9B普通数据及其对应的编码后的10B普通数据。第二编码器306有1个输入:

din:来自第1级处理模块301的编码极性计算器304的输出dout;以及

两个输出:

sec_sel:第二编码器输出有效标志,该信号输出到第3级处理模块303的编码选择器309;

sec_code:第二编码器输出的10B编码,该信号也输出到第3级处理模块303的编码选择器309。

如果输入的9B数据在第二编码器306的查找表中包括的104个9B普通数据的范围之内,则sec_sel有效(高电平),同时输出有效的10B编码,否则sec_sel无效(低电平),同时输出10B为全0。

3.特殊字符编码器307

9B/10B编解码定义11组共22个特殊字符,分别是K.001和K.101、K.002和K.102、K.003和K.103、K.004和K.104、K.005和K.105、K.006和K.106、K.007和K.107、K.008和K.108、K.009和K.109、K.00A和K.10A。特殊字符可以完成字节对齐,帧定界,字符填充等功能。

特殊字符编码307器通过特殊字符查找表实现。特殊字符编码器307有2个输入:

din:来自第1级处理模块301的编码极性计算器304的输出dout;

kin:来自第1级处理模块301的编码极性计算器304的输出kout;以及

2个输出:

k_sel:特殊字符编码器输出有效标志,输出到第3级处理模块303的编码选择器309;

k_code:特殊字符编码器输出的10B编码,也输出到第3级处理模块303的编码选择器309。

当输入的9B数据在特殊字符范围之内,同时特殊数据标识符kin有效,则k_sel有效(高电平),同时输出有效的10B编码,否则k_sel无效(低电平),同时输出10B为全0。

4.线路极性计算器308

线路极性计算器308用于计算线路编码的极性。线路极性计算器308有3个输入:

kin:来自第1级处理模块301的编码极性计算器304的输出kout。

sdisp:来自第1级处理模块301的编码极性计算器304的输出sdisp。

rdisp:线路极性计算器308自己输出的线路极性(rdisp)又作为其输入信号;

以及1个输出:

rdisp:线路极性计算器308输出的线路极性。

线路极性计算器308通过线路极性查找表实现。

当输入的9B数据是特殊字符时,由于特殊字符(特殊代码组)极性都是零,故线路极性(rdisp)在特殊数据字符传输前后不改变。当输入的9B数据不是特殊数据时,按照表2所示的线路极性查找表输出相应的线路极性rdisp。

表2线路极性查找表

第3级处理模块303从第2级处理模块302中的主编码器305(第一编码器)、第二编码器306以及特殊字符编码器307输出的10B数据中,选择1个10B编码输出。第3级处理模块303由编码选择器309(电路-06)构成。

较佳地,编码选择器309可以通过现有技术中的多路选择器电路实现。

编码选择器309接收的各种有效标志信号中,k_sel优先级最高,其次是sec_sel。当k_sel有效时,选择特殊字符编码器307的输出k_code作为编码选择器309的输出;当k_sel无效而sec_sel有效时;选择第二编码器306的输出sec_code作为编码选择器309的输出;以上两种情况均不成立,则选择主编码器305的输出pri_code作为编码选择器309的输出。

图4为本发明实施例提出的9B/10B解码器的电路原理图。解码是编码的逆过程,本发明实施例提出的9B/10B解码器采用2级处理模块结构,包括第1级处理模块401(电路-11,电路-12,电路-13)和第2级处理模块402(电路-14)。每级处理模块占用1个时钟周期,因此9B/10B解码器完成一次解码需要2个时钟周期。

第1级处理模块401由主解码器403(电路-11),第二解码器404(电路-12)和特殊字符解码器405(电路-13)构成。

1.主解码器403(第一解码器)

主解码器403通过反相器实现。

通过判断10B编码的最高位是否是1,如果是1,把10B编码的低9位取反赋给pri_symbol;否则,直接把10B编码的低9位赋给pri_symbol。

2.第二解码器404

第二解码器404通过普通数据查找表实现。

如果输入的10B编码code在104个编码范围之内,sec_sel输出有效(高电平),同时sec_symbol输出有效;否则sec_sel输出无效。

3.特殊字符解码器405

特殊字符解码器405通过查找表实现。

如果10B编码在特殊编码范围之内,k_sel输出有效(高电平),同时k_symbol输出有效,否则k_sel输出无效。

第2级处理模块402

第2级处理模块402从第1级处理模块401的输出(pri_symbol、sec_symbol、k_symbol)中,选择1个9B数据输出。第2级处理模块402由解码选择器406(电路-14)构成。

解码选择器406通过现有技术中的多路选择器电路实现。

解码选择器406的k_sel优先级最高,其次是sec_sel。当k_sel有效时,选择特殊字符解码器405的输出k_symbol作为解码选择器406的输出;当k_sel无效sec_sel有效时选择第二解码器404的输出sec_symbol作为解码选择器406的输出;若以上两种情况均不成立,则选择主解码器403的输出pri_symbol作为解码选择器406的输出。

综上,本发明实施例的9B/10B编码器中,主编码器305采用在9B数据的最左侧附加1位0来实现;第二编码器306、特殊字符编码器307根据9B/10B码表采用查找表实现。这实际相当于将待编码数据分为特殊字符和普通数据,而普通数据又可以分为可以简单变换以及不可简单变换两类,对于可以简单变换的普通数据,通过主编码器在9B数据的最左侧附加1位0来实现;第二编码器、特殊字符编码器则分别采用查找表的方式实现不可简单变换的普通数据以及特殊字符的编码。对于解码器采用类似的思路实现。相比较于现有技术(US Pat No.7405697B1)的通过逻辑表达式实现,本发明的实现过程更易于理解。本发明的编码极性计算器和线路极性计算器相比较于现有技术(US PatNo.6747580B1)使用的加法器和减法器,以及更适合在低成本的FPGA中实现。

使用本发明在低端FPGA中实现9B/10B编解码器,可以达到133MHz以上的时钟频率,可以满足1.25Gbps的串行通信要求。

使用本发明在高端FPGA中实现9B/10B编解码器,可以达到160MHz以上的时钟频率,可以满足3.125Gbps的串行通信要求。

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

Claims (16)

1.一种9B/10B编码器,其特征在于,包括第1级处理模块(301),第2级处理模块(302)和第3级处理模块(303);

所述第1级处理模块(301)用于在输入的9B数据的最左边附加1位“0”后构成的10B数据,并计算所述10B数据的数据极性;将所述数据极性以及输入的9B数据原样输出至第2级处理模块(302);

所述第2级处理模块(302)预先设置了针对不同数据类别的编码方式,采用每一种预置的编码方式将所述9B数据分别转换为10B数据,并将每一种预置编码方式得到的10B数据均输出至第3级处理模块(303);第2级处理模块(302)还根据来自第1级处理模块(301)的数据极性,生成与预置的编码方式对应的有效标志,并将所述有效标志输出至第3级处理模块(303);

所述第3级处理模块(303)用于根据接收的有效标志,选择接收与所述有效标志对应的预置的编码方式得到的10B数据。

2.根据权利要求1所述的方法,其特征在于,所述第2级处理模块(302)包括主编码器(305)、第二编码器(306)和特殊字符编码器(307);

主编码器(305)用于将来自第1级处理模块(301)的9B数据的最左边附加1位0构成10B数据,然后再根据该10B数据的数据极性和线路的极性,将所述10B数据或其补码输出至第3级处理模块(303);

第二编码器(306)中预先设置普通数据查找表,所述普通数据查找表定义104个9B普通数据与其对应的10B普通数据;第二编码器(306)用于根据来自第1级处理模块(301)的9B数据查找所述普通数据查找表,若找到对应的10B普通数据,则生成第二编码器有效标志,并将所得10B普通数据以及所述第二编码器有效标志输出至第3级处理模块(303);

特殊字符编码器(307)中预先设置特殊字符查找表,所述特殊字符查找表定义11组9B特殊字符与10B特殊字符的对应关系;特殊字符编码器(307)用于根据来自第1级处理模块(301)的9B数据查找所述特殊字符查找表,若找到对应的10B特殊字符,则生成特殊字符编码器有效标志,并将所得10B特殊字符以及所述特殊字符编码器有效标志输出至第3级处理模块(303);

所述第3级处理模块(303)在收到特殊字符编码器有效标志时,选择来自特殊字符编码器(307)的10B特殊字符作为最终输出信号输出;否则,若收到第二编码器有效标志时,选择来自第二编码器(306)的10B普通数据作为最终输出信号输出;以上两种情况均不成立,则选择来自主编码器(305)的10B普通数据作为最终输出信号输出。

3.根据权利要求2所述的9B/10B编码器,其特征在于,所述第1级处理模块(301)包括编码极性计算器(304);所述计算所述10B数据的数据极性通过极性查找表实现。

4.根据权利要求3所述的9B/10B编码器,其特征在于,所述数据极性查找表中,000表示极性是0,001表示极性是+2,010表示极性是+4,011表示极性是+6,101表示极性是-2,110表示极性是-4,111表示极性是-6。

5.根据权利要求4所述的9B/10B编码器,其特征在于,所述第1级处理模块(301)将输入的9B数据原样输出至第2级处理模块(302)为:第1级处理模块(301)将输入的9B数据延迟一个时钟周期后输出至第2级处理模块(302)。

6.根据权利要求5所述的9B/10B编码器,其特征在于,所述特殊字符查找表中的11组特殊字符分别为:K.001和K.101、K.002和K.102、K.003和K.103、K.004和K.104、K.005和K.105、K.006和K.106、K.007和K.107、K.008和K.108、K.009和K.109以及K.00A和K.10A。

8.根据权利要求7所述的9B/10编码器,其特征在于,所述主编码器(305)接收所述编码极性计算器(304)输出的9B普通数据和数据极性,以及所述线路极性计算器(308)输出的线路极性;

若所述线路极性是0时,主编码器(305)将所述9B普通数据附加1位0得到的10B数据输出;

若所述线路极性是正时,如果数据极性是正的,主编码器(305)将所述9B普通数据附加1位0得到的10B数据取反后输出;如果数据极性是0或负的,主编码器(305)将所述9B普通数据附加1位0得到的10B数据直接输出;

若所述线路极性是负时,如果数据极性是负的,主编码器(305)将所述9B普通数据附加1位0得到的10B数据取反后输出;如果数据极性是0或正的,主编码器(305)将所述9B普通数据附加1位0得到的10B数据直接输出。

9.一种9B/10B解码器,其特征在于,包括第1级处理模块(401)和第2级处理模块(402),第1级处理模块401用于接收10B数据,第2级处理模块(402)用于输出解码得到的9B数据;

所述第1级处理模块401包括主解码器(403),第二解码器(404)和特殊字符解码器(405);所述主解码器403通过判断接收的10B编码的最高位是否是1,如果是1,把10B编码的低9位取反后输出;否则,直接把10B编码的低9位输出至第2级处理模块(402);

所述第二解码器(404)中预先设置普通数据查找表,所述普通数据查找表定义104个9B普通数据与其对应的10B普通数据;所述第二解码器(404)用于根据接收的10B数据查找所述普通数据查找表,若找到对应的9B普通数据,则生成第二解码器有效标志,并将所得9B普通数据以及所述第二解码器有效标志输出至第2级处理模块(402);

所述特殊字符解码器(405)中预先设置特殊字符查找表,所述特殊字符查找表定义11组9B特殊字符与10B特殊字符的对应关系;特殊字符解码器(405)用于根据接收的10B数据查找所述特殊字符查找表,若找到对应的9B特殊字符,则生成特殊字符解码器有效标志,并将所得9B特殊字符以及所述特殊字符解码器有效标志输出至第2级处理模块(402);

所述第2级处理模块(402)在收到特殊字符解码器有效标志时,选择来自特殊字符解码器(405)的9B特殊字符作为最终输出信号输出;否则,若收到第二解码器有效标志时,选择来自第二解码器(404)的9B普通数据作为最终输出信号输出;以上两种情况均不成立,则选择来自主解码器(403)的9B普通数据作为最终输出信号输出。

10.一种9B/10B编码器的实现方法,其特征在于,预先设置了针对不同数据类别的编码方式;该实现方法包括如下步骤:

A1:在输入的9B数据的最左边附加1位“0”后构成10B数据,并计算所述10B数据的极性;

B1、采用每一种预置的编码方式将所述9B数据分别转换为10B数据;根据所述数据极性,生成与预置的编码方式对应的有效标志;

C1、根据所述有效标志,选择接收与所述有效标志对应的预置的编码方式得到的10B数据。

11.根据权利要求10所述的方法,其特征在于,所述预先设置了针对不同数据类别的编码方式包括:预先设置特殊字符查找表和普通数据查找表,所述特殊字符查找表定义11组9B特殊字符与10B特殊字符的对应关系,所述普通数据查找表定义104个9B普通数据与其对应的10B普通数据;

所述步骤B1包括:

B11、判断步骤A输出的9B数据是否属于预先定义的特殊字符,若是,执行步骤B12,否则执行步骤B13;

B12、生成特殊字符编码器输出有效标志,并按照预先设置的特殊字符查找表找到对应的10B特殊字符;然后转至步骤C1;B13、判断所述9B数据是否与预先设置的普通数据查找表中的任一个9B普通数据中的相匹配,若是,则生成第二编码器输出有效标志,并根据所述普通数据查找表找到对应的10B普通数据;否则,执行步骤B14;

B14、在所述9B数据的最左边附加1位0构成10B数据,然后再根据该10B数据的极性和线路的极性,把10B数据转换为其补码或不进行转换;

所述步骤C1包括:

在收到特殊字符编码器有效标志时,将步骤B12得到的10B特殊字符作为最终输出信号输出;否则,若收到第二编码器有效标志时,将步骤B13得到的10B普通数据作为最终输出信号输出;以上两种情况均不成立,则将步骤B14得到的10B数据作为最终输出信号输出。

12.根据权利要求11所述的方法,其特征在于,步骤A1所述计算所述10B数据的数据极性通过极性查找表实现。

13.根据权利要求12所述的方法,其特征在于,所述数据极性查找表中,000表示极性是0,001表示极性是+2,010表示极性是+4,011表示极性是+6,101表示极性是-2,110表示极性是-4,111表示极性是-6。

14.根据权利要求11所述的方法,其特征在于,所述特殊字符查找表中的11组特殊字符分别为:K.001和K.101、K.002和K.102、K.003和K.103、K.004和K.104、K.005和K.105、K.006和K.106、K.007和K.107、K.008和K.108、K.009和K.109以及K.00A和K.10A。

15.根据权利要求7所述的9B/10编码器,其特征在于,所述步骤B14包括:

若所述线路极性是0时,将所述9B普通数据附加1位0得到的10B数据输出;

若所述线路极性是正时,如果数据极性是正的,将所述9B普通数据附加1位0得到的10B数据取反后输出;如果数据极性是0或负的,将所述9B普通数据附加1位0得到的10B数据直接输出;

若所述线路极性是负时,如果数据极性是负的,将所述9B普通数据附加1位0得到的10B数据取反后输出;如果数据极性是0或正的,将所述9B普通数据附加1位0得到的10B数据直接输出。

16.一种9B/10解码器的实现方法,其特征在于,预先设置特殊字符查找表和普通数据查找表,所述特殊字符查找表定义11组9B特殊字符与10B特殊字符的对应关系,所述普通数据查找表定义104个9B普通数据与其对应的10B普通数据;该方法包括如下步骤:

A2、判断接收的10B编码的最高位是否是1,如果是1,把10B编码的低9位取反后输出至第2级处理模块(402);否则,直接把10B编码的低9位输出至第2级处理模块(402);或者,

根据接收的10B数据查找所述普通数据查找表,若找到对应的9B普通数据,则生成第二解码器有效标志,并将所得9B普通数据以及所述第二解码器有效标志输出至第2级处理模块(402);或者,

根据接收的10B数据查找所述特殊字符查找表,若找到对应的9B特殊字符,则生成特殊字符解码器有效标志,并将所得9B特殊字符以及所述特殊字符解码器有效标志输出至第2级处理模块(402);

B2、所述第2级处理模块(402)在收到特殊字符解码器有效标志时,选择来自特殊字符解码器(405)的9B特殊字符作为最终输出信号输出;否则,若收到第二解码器有效标志时,选择来自第二解码器(404)的9B普通数据作为最终输出信号输出;以上两种情况均不成立,则选择来自主解码器(403)的9B普通数据作为最终输出信号输出。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201010160763.4A CN101847997B (zh) | 2010-04-26 | 2010-04-26 | 一种9b/10b编解码器及其实现方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201010160763.4A CN101847997B (zh) | 2010-04-26 | 2010-04-26 | 一种9b/10b编解码器及其实现方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101847997A true CN101847997A (zh) | 2010-09-29 |

| CN101847997B CN101847997B (zh) | 2014-02-05 |

Family

ID=42772477

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201010160763.4A Expired - Fee Related CN101847997B (zh) | 2010-04-26 | 2010-04-26 | 一种9b/10b编解码器及其实现方法 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN101847997B (zh) |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102497249A (zh) * | 2011-10-07 | 2012-06-13 | 友达光电股份有限公司 | 编码方法、编码装置、解码方法、解码装置、数据传送装置及数据接收装置 |

| CN106411322A (zh) * | 2016-11-04 | 2017-02-15 | 深圳国人通信股份有限公司 | 基于SerDes技术串行通信系统的编解码方法及装置 |

| CN108694918A (zh) * | 2017-06-09 | 2018-10-23 | 京东方科技集团股份有限公司 | 编码方法及装置、解码方法及装置及显示装置 |

| CN109309548A (zh) * | 2018-05-11 | 2019-02-05 | 深圳市华星光电技术有限公司 | 编码方法、设备及可读存储介质 |

| WO2019214140A1 (zh) * | 2018-05-11 | 2019-11-14 | 深圳市华星光电技术有限公司 | 编码方法、设备及可读存储介质 |

| CN110740011A (zh) * | 2019-10-08 | 2020-01-31 | 苏州浪潮智能科技有限公司 | 一种编解码方法及编解码器 |

| CN111599300A (zh) * | 2020-06-19 | 2020-08-28 | 京东方科技集团股份有限公司 | 信号处理方法、发送及接收信号装置、以及显示装置 |

| WO2020206875A1 (zh) * | 2019-04-08 | 2020-10-15 | 深圳市华星光电技术有限公司 | 数据编码方法、解码方法、相关装置及存储介质 |

| CN114598579A (zh) * | 2022-03-03 | 2022-06-07 | 天津瑞发科半导体技术有限公司 | 一种适用于低通和带通信道的9b/10b编解码方法 |

| WO2022144030A1 (zh) * | 2020-12-30 | 2022-07-07 | 天津瑞发科半导体技术有限公司 | 一种9b/10b编解码方法 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6198413B1 (en) * | 1999-07-01 | 2001-03-06 | International Business Machines Corporation | Partitioned DC balanced (0,6) 16B/18B transmission code with error correction |

| US6747580B1 (en) * | 2003-06-12 | 2004-06-08 | Silicon Image, Inc. | Method and apparatus for encoding or decoding data in accordance with an NB/(N+1)B block code, and method for determining such a block code |

-

2010

- 2010-04-26 CN CN201010160763.4A patent/CN101847997B/zh not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6198413B1 (en) * | 1999-07-01 | 2001-03-06 | International Business Machines Corporation | Partitioned DC balanced (0,6) 16B/18B transmission code with error correction |

| US6747580B1 (en) * | 2003-06-12 | 2004-06-08 | Silicon Image, Inc. | Method and apparatus for encoding or decoding data in accordance with an NB/(N+1)B block code, and method for determining such a block code |

Cited By (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102497249A (zh) * | 2011-10-07 | 2012-06-13 | 友达光电股份有限公司 | 编码方法、编码装置、解码方法、解码装置、数据传送装置及数据接收装置 |

| CN102497249B (zh) * | 2011-10-07 | 2015-01-14 | 友达光电股份有限公司 | 编码方法、编码装置、解码方法、解码装置、数据传送装置及数据接收装置 |

| TWI489814B (zh) * | 2011-10-07 | 2015-06-21 | Au Optronics Corp | 編碼方法、編碼裝置、解碼方法、解碼裝置、資料傳送裝置及資料接收裝置 |

| CN106411322A (zh) * | 2016-11-04 | 2017-02-15 | 深圳国人通信股份有限公司 | 基于SerDes技术串行通信系统的编解码方法及装置 |

| WO2018082286A1 (zh) * | 2016-11-04 | 2018-05-11 | 深圳国人通信股份有限公司 | 基于 SerDes 技术串行通信系统的编解码方法及装置 |

| CN108694918B (zh) * | 2017-06-09 | 2021-09-28 | 京东方科技集团股份有限公司 | 编码方法及装置、解码方法及装置及显示装置 |

| US11056070B2 (en) | 2017-06-09 | 2021-07-06 | Beijing Boe Display Technology Co., Ltd. | Encoding method and device, decoding method and device, and display device |

| CN108694918A (zh) * | 2017-06-09 | 2018-10-23 | 京东方科技集团股份有限公司 | 编码方法及装置、解码方法及装置及显示装置 |

| CN109309548A (zh) * | 2018-05-11 | 2019-02-05 | 深圳市华星光电技术有限公司 | 编码方法、设备及可读存储介质 |

| WO2019214140A1 (zh) * | 2018-05-11 | 2019-11-14 | 深圳市华星光电技术有限公司 | 编码方法、设备及可读存储介质 |

| WO2020206875A1 (zh) * | 2019-04-08 | 2020-10-15 | 深圳市华星光电技术有限公司 | 数据编码方法、解码方法、相关装置及存储介质 |

| US11611354B2 (en) | 2019-04-08 | 2023-03-21 | Tcl China Star Optoelectronics Technology Co., Ltd. | Data encoding method, decoding method, related device, and storage medium |

| CN110740011A (zh) * | 2019-10-08 | 2020-01-31 | 苏州浪潮智能科技有限公司 | 一种编解码方法及编解码器 |

| CN110740011B (zh) * | 2019-10-08 | 2022-12-13 | 苏州浪潮智能科技有限公司 | 一种编解码方法及编解码器 |

| CN111599300A (zh) * | 2020-06-19 | 2020-08-28 | 京东方科技集团股份有限公司 | 信号处理方法、发送及接收信号装置、以及显示装置 |

| WO2022144030A1 (zh) * | 2020-12-30 | 2022-07-07 | 天津瑞发科半导体技术有限公司 | 一种9b/10b编解码方法 |

| CN114598579A (zh) * | 2022-03-03 | 2022-06-07 | 天津瑞发科半导体技术有限公司 | 一种适用于低通和带通信道的9b/10b编解码方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101847997B (zh) | 2014-02-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101847997A (zh) | 一种9b/10b编解码器及其实现方法 | |

| US7180958B2 (en) | Technique for utilizing spare bandwidth resulting from the use of a transition-limiting code in a multi-level signaling system | |

| JP3542809B2 (ja) | 遷移制御された平衡エンコード体系 | |

| US5243627A (en) | Signal point interleaving technique | |

| US20090119571A1 (en) | 64b/66b Coding Apparatus and Method | |

| EP1834459A2 (en) | 16b/10s coding apparatus and method | |

| US7518534B2 (en) | 8-bit to 10-bit encoding method and apparatus | |

| KR20010018672A (ko) | 무직류, 최소대역폭특성을 갖는 선로부호의 설계방법 및 부호화/복호화 장치 | |

| KR20060129398A (ko) | 로컬 패리티를 갖는 직류 평형된 6b/8b 송신 코드 | |

| US20090276683A1 (en) | Data transmission equipment and generating method for transmission code | |

| KR100281738B1 (ko) | 니블 반전 및 블록 반전 부호의 부호화 및 복호화 방법, 그 부호 및 복호장치 | |

| WO2022144030A1 (zh) | 一种9b/10b编解码方法 | |

| US6917312B2 (en) | Technique for improving the quality of digital signals in a multi-level signaling system | |

| US6346895B1 (en) | Apparatus and method for using nibble inversion code | |

| CN113949388B (zh) | 用于串行器/解串器系统的编解码器与编解码方法 | |

| US11888962B2 (en) | System and method for transition encoding with flexible word-size | |

| US20060015790A1 (en) | Low overhead coding techniques | |

| KR100528139B1 (ko) | 코드워드를 생성하는 방법 및 장치 | |

| CN110740011B (zh) | 一种编解码方法及编解码器 | |

| Lin et al. | Balance of 0, 1 bits for Huffman and reversible variable-length coding | |

| US6806817B2 (en) | Means and method of data encoding and communication at rates above the channel bandwidth | |

| JP2011155330A (ja) | 伝送システム | |

| KR20110012525A (ko) | 가시광 통신 시스템에서 데이터 전송을 위한 라인 코딩 장치 및 방법 | |

| US7725036B2 (en) | Efficient transmission of digital return path data in cable television return path | |

| Yuan et al. | A novel multilevel codes with 16QAM |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20140205 |