CN100530081C - 分支预测控制 - Google Patents

分支预测控制 Download PDFInfo

- Publication number

- CN100530081C CN100530081C CNB200610091510XA CN200610091510A CN100530081C CN 100530081 C CN100530081 C CN 100530081C CN B200610091510X A CNB200610091510X A CN B200610091510XA CN 200610091510 A CN200610091510 A CN 200610091510A CN 100530081 C CN100530081 C CN 100530081C

- Authority

- CN

- China

- Prior art keywords

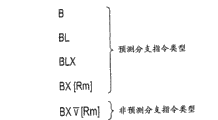

- branch

- instruction

- instructions

- predicted

- predictor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3836—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution

- G06F9/3842—Speculative instruction execution

- G06F9/3844—Speculative instruction execution using dynamic branch prediction, e.g. using branch history tables

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3836—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution

- G06F9/3842—Speculative instruction execution

- G06F9/3846—Speculative instruction execution using static prediction, e.g. branch taken strategy

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3861—Recovery, e.g. branch miss-prediction, exception handling

Landscapes

- Engineering & Computer Science (AREA)

- Software Systems (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Advance Control (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/139984 | 2005-05-31 | ||

| US11/139,984 US7725695B2 (en) | 2005-05-31 | 2005-05-31 | Branch prediction apparatus for repurposing a branch to instruction set as a non-predicted branch |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1873611A CN1873611A (zh) | 2006-12-06 |

| CN100530081C true CN100530081C (zh) | 2009-08-19 |

Family

ID=36425044

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB200610091510XA Active CN100530081C (zh) | 2005-05-31 | 2006-05-30 | 分支预测控制 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7725695B2 (enExample) |

| JP (1) | JP4727491B2 (enExample) |

| CN (1) | CN100530081C (enExample) |

| GB (1) | GB2426842B (enExample) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8245017B2 (en) * | 2009-02-12 | 2012-08-14 | Via Technologies, Inc. | Pipelined microprocessor with normal and fast conditional branch instructions |

| US8521996B2 (en) * | 2009-02-12 | 2013-08-27 | Via Technologies, Inc. | Pipelined microprocessor with fast non-selective correct conditional branch instruction resolution |

| US9891922B2 (en) | 2012-06-15 | 2018-02-13 | International Business Machines Corporation | Selectively blocking branch prediction for a predetermined number of instructions |

| US20140115257A1 (en) * | 2012-10-22 | 2014-04-24 | Advanced Micro Devices, Inc. | Prefetching using branch information from an instruction cache |

| GB2506462B (en) * | 2013-03-13 | 2014-08-13 | Imagination Tech Ltd | Indirect branch prediction |

| US9639370B1 (en) * | 2015-12-15 | 2017-05-02 | International Business Machines Corporation | Software instructed dynamic branch history pattern adjustment |

| US10423510B2 (en) * | 2017-10-04 | 2019-09-24 | Arm Limited | Apparatus and method for predicting a redundancy period |

| US11822923B1 (en) * | 2018-06-26 | 2023-11-21 | Advanced Micro Devices, Inc. | Performing store-to-load forwarding of a return address for a return instruction |

| US11513801B2 (en) * | 2018-09-10 | 2022-11-29 | Advanced Micro Devices, Inc. | Controlling accesses to a branch prediction unit for sequences of fetch groups |

| US20210149676A1 (en) * | 2019-11-14 | 2021-05-20 | Higon Austin R&D Center Corporation | Branch Prediction Method, Branch Prediction Unit and Processor Core |

| CN115577395B (zh) * | 2022-10-27 | 2025-07-15 | 中国人民解放军国防科技大学 | 一种防范分支历史注入攻击的方法和装置 |

| CN120447968B (zh) * | 2025-07-08 | 2025-09-30 | 此芯科技集团有限公司 | 一种取指模块与处理器 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2603626B2 (ja) * | 1987-01-16 | 1997-04-23 | 三菱電機株式会社 | データ処理装置 |

| US5228131A (en) * | 1988-02-24 | 1993-07-13 | Mitsubishi Denki Kabushiki Kaisha | Data processor with selectively enabled and disabled branch prediction operation |

| US5333283A (en) * | 1991-10-29 | 1994-07-26 | International Business Machines Corporation | Case block table for predicting the outcome of blocks of conditional branches having a common operand |

| US5608886A (en) * | 1994-08-31 | 1997-03-04 | Exponential Technology, Inc. | Block-based branch prediction using a target finder array storing target sub-addresses |

| US5638525A (en) * | 1995-02-10 | 1997-06-10 | Intel Corporation | Processor capable of executing programs that contain RISC and CISC instructions |

| JP3486690B2 (ja) * | 1995-05-24 | 2004-01-13 | 株式会社ルネサステクノロジ | パイプライン方式プロセッサ |

| US5721893A (en) * | 1996-05-14 | 1998-02-24 | Hewlett-Packard Company | Exploiting untagged branch prediction cache by relocating branches |

| US6282663B1 (en) * | 1997-01-22 | 2001-08-28 | Intel Corporation | Method and apparatus for performing power management by suppressing the speculative execution of instructions within a pipelined microprocessor |

| US6601161B2 (en) * | 1998-12-30 | 2003-07-29 | Intel Corporation | Method and system for branch target prediction using path information |

| US6859875B1 (en) | 2000-06-12 | 2005-02-22 | Freescale Semiconductor, Inc. | Processor having selective branch prediction |

| US20020073301A1 (en) * | 2000-12-07 | 2002-06-13 | International Business Machines Corporation | Hardware for use with compiler generated branch information |

| US6823447B2 (en) * | 2001-03-01 | 2004-11-23 | International Business Machines Corporation | Software hint to improve the branch target prediction accuracy |

| JP3798998B2 (ja) * | 2002-06-28 | 2006-07-19 | 富士通株式会社 | 分岐予測装置および分岐予測方法 |

| US7000095B2 (en) | 2002-09-06 | 2006-02-14 | Mips Technologies, Inc. | Method and apparatus for clearing hazards using jump instructions |

| US7595752B2 (en) * | 2002-10-02 | 2009-09-29 | Global Locate, Inc. | Method and apparatus for enhanced autonomous GPS |

| JP2005078234A (ja) * | 2003-08-29 | 2005-03-24 | Renesas Technology Corp | 情報処理装置 |

| US20050216713A1 (en) * | 2004-03-25 | 2005-09-29 | International Business Machines Corporation | Instruction text controlled selectively stated branches for prediction via a branch target buffer |

-

2005

- 2005-05-31 US US11/139,984 patent/US7725695B2/en not_active Expired - Lifetime

-

2006

- 2006-03-31 GB GB0606560A patent/GB2426842B/en active Active

- 2006-04-18 JP JP2006114589A patent/JP4727491B2/ja active Active

- 2006-05-30 CN CNB200610091510XA patent/CN100530081C/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| GB2426842B (en) | 2009-07-29 |

| GB0606560D0 (en) | 2006-05-10 |

| CN1873611A (zh) | 2006-12-06 |

| US7725695B2 (en) | 2010-05-25 |

| US20060271770A1 (en) | 2006-11-30 |

| JP4727491B2 (ja) | 2011-07-20 |

| GB2426842A (en) | 2006-12-06 |

| JP2006338656A (ja) | 2006-12-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101074621B1 (ko) | 프로액티브 브랜치 타겟 어드레스 캐시 관리를 위한 방법들 및 장치 | |

| CN111886580B (zh) | 用于控制分支预测的装置和方法 | |

| KR100930199B1 (ko) | 루프―종료 브랜치들에 의한 브랜치 히스토리 레지스터의업데이트 억제 | |

| KR101459536B1 (ko) | 사전 통지 기법들을 사용하여 프로그램의 순차적 흐름을 변경하기 위한 방법들 및 장치 | |

| US8156286B2 (en) | Processor and method for using an instruction hint to prevent hardware prefetch from using certain memory accesses in prefetch calculations | |

| KR100974384B1 (ko) | 분기 명령들을 예측하기 위한 방법 및 장치 | |

| JP2007515715A (ja) | 命令キャッシュからラベル境界上のトレースキャッシュに遷移させる方法 | |

| JP2011100466A5 (enExample) | ||

| JP2008532142A5 (enExample) | ||

| WO2008067277A2 (en) | Methods and apparatus for recognizing a subroutine call | |

| CN100530081C (zh) | 分支预测控制 | |

| US20040117606A1 (en) | Method and apparatus for dynamically conditioning statically produced load speculation and prefetches using runtime information | |

| US20040225866A1 (en) | Branch prediction in a data processing system | |

| US20030204705A1 (en) | Prediction of branch instructions in a data processing apparatus | |

| KR101026978B1 (ko) | 리턴 스택을 운용하는 방법 및 장치 | |

| US7640422B2 (en) | System for reducing number of lookups in a branch target address cache by storing retrieved BTAC addresses into instruction cache | |

| US20040186984A1 (en) | Branch prediction in a data processing system | |

| HK1112980A (en) | Method and apparatus for managing a return stack |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant |