CN100530081C - 分支预测控制 - Google Patents

分支预测控制 Download PDFInfo

- Publication number

- CN100530081C CN100530081C CNB200610091510XA CN200610091510A CN100530081C CN 100530081 C CN100530081 C CN 100530081C CN B200610091510X A CNB200610091510X A CN B200610091510XA CN 200610091510 A CN200610091510 A CN 200610091510A CN 100530081 C CN100530081 C CN 100530081C

- Authority

- CN

- China

- Prior art keywords

- branch

- instruction

- instructions

- predicted

- predictor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000000872 buffer Substances 0.000 claims description 21

- 238000000034 method Methods 0.000 claims description 16

- 230000008859 change Effects 0.000 claims description 2

- 230000007246 mechanism Effects 0.000 abstract description 25

- 230000015556 catabolic process Effects 0.000 abstract 1

- 238000006731 degradation reaction Methods 0.000 abstract 1

- 238000004590 computer program Methods 0.000 description 5

- 230000006399 behavior Effects 0.000 description 4

- 230000008901 benefit Effects 0.000 description 4

- 238000001514 detection method Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 238000011010 flushing procedure Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000009897 systematic effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3836—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution

- G06F9/3842—Speculative instruction execution

- G06F9/3844—Speculative instruction execution using dynamic branch prediction, e.g. using branch history tables

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3836—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution

- G06F9/3842—Speculative instruction execution

- G06F9/3846—Speculative instruction execution using static prediction, e.g. branch taken strategy

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3861—Recovery, e.g. branch miss-prediction, exception handling

Landscapes

- Engineering & Computer Science (AREA)

- Software Systems (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Advance Control (AREA)

Abstract

处理器(2)含有分支预测机构(14、18、20),分支预测机构的作用是为预测型分支指令预测分支结果。处理器还支持非预测型分支指令,所述非预测型分支指令被分支预测机构(14、18、20)忽略而不经受预测。在已知那些转移操作有可能误预测时,用非预测型分支程序指令来代表/控制转移操作,以减小误预测对分支预测机构(14、18、20)整体性能降低的影响。

Description

技术领域

本发明涉及数据处理系统领域。更具体地说,本发明涉及含有分支预测机构和对分支预测机制之控制的数据处理系统。

背景技术

众所周知,提供包括有分支预测机制的处理器,所述分支预测机制以不同方式进行关于程序指令序列内的分支指令是否将导致转移操作(程序流程中的转移)的预测。精确预测分支指令是否将导致转移操作的结果是,在已知分支是否将实际导致转移操作(如分支是否将传递其条件码或者分支是否将导致转移至与前面的间接分支情形相同的位置等等)之前,可以开始依照分支预测结果从存储单元取出程序指令。与这样的分支预测机制相关联的电路和复杂性开销之合理性,由其产生的性能的显著增加所证明。具体地说,精确预测分支结果减少了在分支指令执行之前因为流水线刷新结果而使错误的程序指令经推测而取出以及重新取出所需的正确指令序列的可能性。

能够增加分支预测机制的精度及有效性的技术在处理器性能的改进方面具有强大优势。

发明内容

在一个方面,本发明提供了用于在程序指令序列的控制下处理数据的设备,所述设备包含:

指令解码器,可用来为多个不同编码类型的分支程序指令解码;

分支预测器,可用来检测所述程序指令序列内的分支指令并预测转移操作是否将由所检测的分支指令产生;其中

所述多个不同编码类型的分支程序指令包括至少一个由所述分支预测器为其进行预测的预测型分支指令;并且包括至少一个非预测型分支指令,除了不受制于所述分支预测器的预测以外,它提供与其中一个所述预测型分支指令相同的功能性。

本发明认识到,对于给定的分支程序指令,在某些情况下,与误预测相关联的性能损失比与未作预测相关联的性能损失更糟。本发明还认识到,在程序被编码并提供一种将不会导致由分支预测机构所作的预测的分支程序指令时,这样的情形可能经常被提前认识到。因此,所述系统提供了被分支预测机构检测并预测的一些分支程序指令编码以及不被分支预测机构预测的其他分支程序指令编码。因此,在所作的任何预测可能会是误预测、导致比未作预测更糟的后果的场合,程序员或编译器可选择使用非预测型分支程序指令。特定的转移操作可能难以预测,因为随机行为或系统行为与分支预测机构的假设相反。在这种场合不作分支预测有各种各样的好处,其中可包括不消耗可在别处有效使用的分支预测机构资源。其他的例子是,由于分支预测机构试图预测已知不适合预测的转移操作的缘故,用于其他转移操作的预测可能变得不够精确。

在一些优选的示范实施例中,分支预测器可包括分支历史缓冲器,可用来存储表示基于所存储的过去行为的历史给定分支是否将被采用的分支历史数据。通过试图预测和跟踪已知无规律的转移操作,这样的机构可能变得效率低下(例如,它可能不够精确地识别分支结果的样式),并且因此本发明的方法可用来使分支历史缓冲器不存储与非预测性的转移操作有关的数据。

另一个优选的实施例中,用分支目标缓冲存储器来存储先前遇到的转移操作的分支目标地址。这种分支目标缓冲存储器的容量是有限的,将这样的容量耗费在已知不准确预测的类型的转移操作上会使这样的容量无法提供给可被精确预测的其他转移操作使用。因此,分支目标缓冲存储器被布置成不存储与非预测转移操作有关的数据。

对分支目标缓冲存储器的又一限制是,它们通常具有有限数量的存取端口,且浪费这些端口的其中一个来试图存取以不被预测为好的类型的分支有关的数据,将导致该存取端口无法提供给可在该时被取出并可有效地被预测的其他分支指令使用。

当会理解,属于预测型和非预测型的不同类型的分支指令可具有各种各样的不同形式。然而,非预测型分支指令的优选形式是一种可附加地表明指令集内之变化的形式。当这种被表明有某种变化的附加指令集不存在时,这种分支指令的非预测性质可叠加在这类指令上来获益,否则该分支指令的可区分特征会是多余的,并且可被有效地重新用来发出信号,表示分支预测机构不应当被用于这种类型的分支指令。

在一些优选实施例中,这种非预测型分支指令包括一种使用间接参考存储该目标地址的寄存器来规定其目标地址的分支指令。与采用目标地址直接表示的指令相比,采用对分支目标的间接参考更可能表明精确预测之低概率。在分支目标可能变化时通常使用间接参考,因此这正是一种其中精确预测不太可能的情况。

在另一个方面,本发明提供了用于在程序指令序列的控制下处理数据的设备,所述设备包含:

指令解码器装置,用于为多个不同编码类型的分支程序指令解码;

分支预测器装置,用于检测所述程序指令序列内的分支指令并预测转移操作是否将从所检测的分支指令产生;其中

所述多个不同编码类型的分支程序指令包括至少一个预测型分支指令,所述分支预测器装置对其进行预测;并且包括至少一个非预测型分支指令,它提供了与其中一个所述预测型分支指令(除了不受所述分支预测器预测以外)相同的功能性。

在又一个方面,本发明提供了一种用于在程序指令序列的控制下处理数据的方法,所述方法包含下列步骤:

为多个不同编码类型的分支程序指令解码;

使用分支预测器检测所述程序指令序列内的分支指令并预测转移操作是否将从所检测的分支指令产生;其中

所述多个不同编码类型的分支程序指令包括至少一个预测型分支指令,所述分支预测器对其进行预测;并且包括至少一个非预测型分支指令,其提供了与其中一个所述预测型分支指令(除了不受所述分支预测器预测之外)相同的功能性。

在另一个方面,本发明提供了装有计算机程序的计算机程序载体,可用来控制数据处理设备在程序指令序列的控制下处理数据,所述数据处理设备设有分支预测器,可用来检测所述程序指令序列内的分支指令并预测转移操作是否将从所检测的分支指令产生,所述计算机程序包含:

多个不同编码类型的分支程序指令;

至少一个预测型分支指令,所述分支预测器对其进行预测;以及

至少一个非预测型分支指令,其提供了与其中一个所述预测型分支指令(除了不受所述分支预测器预测以外)相同的功能性。

在一个辅助方面,本发明提供了编译器,用于编译计算机程序以控制数据处理设备在包括有多个不同编码类型的分支程序指令的程序指令序列的控制下处理数据,所述数据处理设备具有分支预测器,可用来检测所述程序指令序列内的分支指令并预测转移操作是否将从所检测的分支指令产生,所述编译器可用来生成:

至少一个预测型分支指令,所述分支预测器对其进行预测;以及

至少一个非预测型分支指令,它提供了与其中一个所述预测型分支指令(除了不受所述分支预测器预测以外)相同的功能性。

当会理解,用于编译计算机程序的编译器通过它们自身有利地使用本发明的方法或使用由程序员提供的信息来识别那些可能不会导致精确预测的转移操作,并因此在它们生成的代码中用非预测型分支指令而不是预测型分支指令来表示那些转移操作。

通过下面参照附图详细描述的说明性实施例,本发明上述的及其他的目的、特征和优点将显而易见。

附图说明

图1示意说明结合了分支预测机构的处理器;

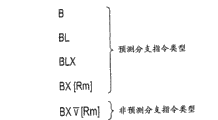

图2示意说明包括预测分支指令类型和非预测分支指令类型的许多不同的编码分支指令;以及

图3是示意说明具有预测数据的预测分支机构的增殖流程图。

具体实施方式

图1示出了处理器2,其中包括标准数据处理部件,例如寄存器文件4、乘法器6、移位器8和加法器10,它们在由解码器12生成的控制信号的控制下发挥作用来实施期望的数据处理操作。由取指令单元14从存储器(未作图示)取出的指令被送进指令流水线16,所述指令沿指令流水线16行进以按标准流水线处理原理被解码并执行。

处理器2包括分支预测机构,在此示范实施例中,分支预测机构包含分支历史缓冲器18,存储关于先前遇到的预测型分支指令之被采用和未被采用之结果的样式。分支预测机构还包含分支目标缓冲器20,用于存储与已被采用的、先前遇到的预测型分支指令相关联的分支目标地址。取指令单元14在接收指令时将指令地址发送到分支目标缓冲器20,在此处它被用来导引进所存储的、先前遇到的分支目标地址的阵列。按内容寻址的存储器用于存储先前遇到的分支指令的地址,以在来自当前取出的指令的地址被应用于此时、若当前取出指令的地址与被存储的先前曾找到分支指令的地址相对应,则发生命中。如果这样的命中发生,则分支目标缓冲器将该分支指令的分支目标地址返回到取指令单元14。此时还要访问分支历史缓冲器18,以依照先前观测到的行为来确定依照前述的关于分支被采用和未被采用的结果的检测样式刚被识别的分支指令是否将被采用或不被采用。如果分支历史缓冲器表明遇到的分支指令被预测将被采用,则由分支目标缓冲器20返回的分支目标地址可被取指令单元14使用,以按照分支预测根据由分支目标缓冲器20表明的地址开始取出指令。

当会理解,这些分支预测机构本身是公知的,且依照本发明的方法可使用不同类型的分支预测机构。

当分支指令到达指令流水线末端并且将被从该处收回时,分支预测更新电路20的作用是依照目前已被正确执行的分支指令的实际结果更新分支预测机构14、18和20。指令解码器12对多个不同编码类型的分支程序指令有响应。这些类型的分支指令中的某些是经历了分支预测机构14、18、20预测的经预测指令。另外,还有这样一些分支指令的编码,这些分支指令尽管在被执行时确实实施转移操作,但不受到分支预测机构14、18、20的预测,并且不用来更新分支历史缓冲器18或分支目标缓冲器20。这样的非预测分支指令因为不更新由分支预测机构14、18、20存储的预测数据,它们在指令流内发生时将不会被分支预测机构检测并且将不会受到预测。说明最好不试图预测已知可能是误预测的分支指令的原因的一个实例是:分支目标缓冲器20的单个存取端口如果被不必要地占用以试图存取与可能被误预测的分支有关的信息,则可阻止另一个对可能被成功地精确预测的分支指令的存取。此外,如果分支预测机构有限的存储资源用来存储与不可能被成功预测的分支指令有关的信息,则它们就会被浪费。另一个因素是误预测干扰了历史数据并且可使整个预测的精度降级,因此它们最好被排除在数据之外,例如被排除在分支历史缓冲器18的关于分支被采用/未被采用的历史数据之外。

图2说明了依照由ARM Limited Cambridge England设计的ARM处理器的ARM指令集体系结构的五个不同编码类型的分支指令。这些不同编码类型的分支指令的头四个为经受了分支预测的预测分支指令。最后的类型是非预测分支指令类型,可以在可能被误预测场合在程序内使用(在程序员的显式控制下或者如由编译器自动生成)。该非预测分支指令类型未经受预测,因此不会不必要地使分支预测机构的性能降级。将会看到,在此示范性实施例中,非预测分支指令类型是一种采用经由寄存器Rm对其分支目标作间接参考的类型。这种对分支目标的间接参考应当可能在高级的误检测会发生的场合使用。在此例中,非预测分支指令BXJ提供了与被预测的BX指令相同的功能性而不是非预测的提示信息。当会理解,图2中说明的特定指令只是可能经受本发明的方法的分支指令的一例,而在不同处理器体系结构中或ARM处理器体系结构中采用不同指令将是适当的。

图3是示意说明存储的预测数据更新的流程图。在步骤22中,指令从流水线上撤下。接着在步骤24中,确定撤下的分支指令是否属于预测型。如果分支指令不属于预测型,则处理结束。如果分支指令属于预测型,则在步骤26中更新分支历史缓冲器,并在步骤28中更新分支目标缓冲器。因为非预测型分支指令不会导致对分支预测机构14、18、20的任何更新,在被遇到时会被这些机构忽略并且不会经受那些分支预测机构的分支预测。非预测的提示信息将来可能被具有分支预测机构的处理器忽略,所述的分支预测机构具有有效地预测这些不易分支行为的能力,从而提供有用的正向兼容性路径。

如前所述,非预测型分支指令可由知道特定转移操作可能受到误预测的程序员手工插入程序代码内。或者,这些非预测型分支指令也可由按照本发明的方法的编译器自动或半自动地调用。程序员可用表示特定转移操作可能被误预测的信息来注释高级代码,并且编译器可对该提示信息作出响应以将非预测型分支指令用于该转移操作。另外作为备选或另加的方式,编译器可自动检测那些表现出可能表明分支误预测将经常发生之特性的高级程序指令代码的序列。这种特性的实例会有大量的间接分支参考例如与嵌套的DLL或者未解决的面向对象语言中的过程调用一起存在。当编译器检测出这样的特征时,它可使用将被分支预测机构14、18、20忽略的非预测型分支指令。可在编译器内使用的另一种技术是它可仿效编译器生成的被编译代码的执行并且描绘所述代码的状态以识别某些分支是否正导致较大数量的误预测。如果这样的误预测分支正在发生,则代表那些分支的程序指令可由非预测型程序指令取代。

尽管在这里已经参照附图对本发明的说明性实施例进行了详细描述,但是应当理解,本发明并不拘泥于那些实施例,并且只要不背离所附权利要求书规定的本发明的范围和精神,本领域的技术人员可实施各种变更和修改。

Claims (6)

1.一种在程序指令序列的控制下处理数据的设备,所述设备包含:

指令解码器,可用来为多个不同编码类型的分支程序指令解码;

分支预测器,可用来检测所述程序指令序列内的分支指令并预测转移操作是否将由经检测的分支指令产生;其中

所述多个不同编码类型的分支程序指令包括至少一个预测型分支指令,所述分支预测器对其进行预测,并包括至少一个非预测型分支指令,除了不受所述分支预测器预测以外,该指令提供与其中一个所述预测型分支指令相同的功能性,其中,所述分支预测器包括分支历史缓冲器,可用来存储分支历史数据,为预测型分支指令的给定分支指令示出在先前被遇到时所述给定分支指令是否导致了转移操作,所述分支历史预测器不存储非预测型分支指令的分支历史数据。

2.如权利要求1所述的设备,其中,所述分支预测器包括分支目标缓冲存储器,可用来存储先前遇到的预测型分支指令的分支目标地址,所述分支目标缓冲存储器不存储先前遇到的非预测型分支指令的分支目标地址。

3.如权利要求2所述的设备,其中,所述设备可用来在一个处理循环中取出多于所述分支目标缓冲存储器具有的端口的程序指令,分支目标地址可通过所述端口存取。

4.如权利要求1所述的设备,其中,所述至少一个非预测型分支指令包括一种除转移操作外还表明正被执行的指令集的变化的分支指令类型。

5.如权利要求1所述的设备,其中,所述至少一个非预测型分支指令包括利用间接参考存有分支目标地址的寄存器来指定所述分支目标地址的分支指令类型。

6.一种在程序指令序列的控制下处理数据的方法,所述方法包含下列步骤:

将多个不同编码类型的分支程序指令解码;

使用分支预测器检测所述程序指令序列内的分支指令并预测转移操作是否将由经检测的分支指令产生;其中

所述多个不同编码类型的分支程序指令包括:至少一个预测型分支指令,所述分支预测器对其进行预测;以及至少一个非预测型分支指令,除了不受所述分支预测器预测以外,该指令提供与其中一个所述预测型分支指令相同的功能性,其中,所述分支预测器包括分支历史缓冲器,可用来存储分支历史数据,为预测型分支指令的给定分支指令示出在先前被遇到时所述给定分支指令是否导致了转移操作,所述分支历史预测器不存储非预测型分支指令的分支历史数据。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/139984 | 2005-05-31 | ||

| US11/139,984 US7725695B2 (en) | 2005-05-31 | 2005-05-31 | Branch prediction apparatus for repurposing a branch to instruction set as a non-predicted branch |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1873611A CN1873611A (zh) | 2006-12-06 |

| CN100530081C true CN100530081C (zh) | 2009-08-19 |

Family

ID=36425044

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB200610091510XA Active CN100530081C (zh) | 2005-05-31 | 2006-05-30 | 分支预测控制 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7725695B2 (zh) |

| JP (1) | JP4727491B2 (zh) |

| CN (1) | CN100530081C (zh) |

| GB (1) | GB2426842B (zh) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8635437B2 (en) * | 2009-02-12 | 2014-01-21 | Via Technologies, Inc. | Pipelined microprocessor with fast conditional branch instructions based on static exception state |

| US8521996B2 (en) * | 2009-02-12 | 2013-08-27 | Via Technologies, Inc. | Pipelined microprocessor with fast non-selective correct conditional branch instruction resolution |

| US9891922B2 (en) | 2012-06-15 | 2018-02-13 | International Business Machines Corporation | Selectively blocking branch prediction for a predetermined number of instructions |

| US20140115257A1 (en) * | 2012-10-22 | 2014-04-24 | Advanced Micro Devices, Inc. | Prefetching using branch information from an instruction cache |

| GB2511949B (en) * | 2013-03-13 | 2015-10-14 | Imagination Tech Ltd | Indirect branch prediction |

| US9639370B1 (en) * | 2015-12-15 | 2017-05-02 | International Business Machines Corporation | Software instructed dynamic branch history pattern adjustment |

| US10423510B2 (en) * | 2017-10-04 | 2019-09-24 | Arm Limited | Apparatus and method for predicting a redundancy period |

| US11822923B1 (en) * | 2018-06-26 | 2023-11-21 | Advanced Micro Devices, Inc. | Performing store-to-load forwarding of a return address for a return instruction |

| US11513801B2 (en) * | 2018-09-10 | 2022-11-29 | Advanced Micro Devices, Inc. | Controlling accesses to a branch prediction unit for sequences of fetch groups |

| US20210149676A1 (en) * | 2019-11-14 | 2021-05-20 | Higon Austin R&D Center Corporation | Branch Prediction Method, Branch Prediction Unit and Processor Core |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2603626B2 (ja) * | 1987-01-16 | 1997-04-23 | 三菱電機株式会社 | データ処理装置 |

| US5228131A (en) * | 1988-02-24 | 1993-07-13 | Mitsubishi Denki Kabushiki Kaisha | Data processor with selectively enabled and disabled branch prediction operation |

| US5333283A (en) * | 1991-10-29 | 1994-07-26 | International Business Machines Corporation | Case block table for predicting the outcome of blocks of conditional branches having a common operand |

| US5608886A (en) * | 1994-08-31 | 1997-03-04 | Exponential Technology, Inc. | Block-based branch prediction using a target finder array storing target sub-addresses |

| US5638525A (en) * | 1995-02-10 | 1997-06-10 | Intel Corporation | Processor capable of executing programs that contain RISC and CISC instructions |

| JP3486690B2 (ja) * | 1995-05-24 | 2004-01-13 | 株式会社ルネサステクノロジ | パイプライン方式プロセッサ |

| US5721893A (en) * | 1996-05-14 | 1998-02-24 | Hewlett-Packard Company | Exploiting untagged branch prediction cache by relocating branches |

| US6282663B1 (en) * | 1997-01-22 | 2001-08-28 | Intel Corporation | Method and apparatus for performing power management by suppressing the speculative execution of instructions within a pipelined microprocessor |

| US6601161B2 (en) * | 1998-12-30 | 2003-07-29 | Intel Corporation | Method and system for branch target prediction using path information |

| US6859875B1 (en) * | 2000-06-12 | 2005-02-22 | Freescale Semiconductor, Inc. | Processor having selective branch prediction |

| US20020073301A1 (en) * | 2000-12-07 | 2002-06-13 | International Business Machines Corporation | Hardware for use with compiler generated branch information |

| US6823447B2 (en) * | 2001-03-01 | 2004-11-23 | International Business Machines Corporation | Software hint to improve the branch target prediction accuracy |

| JP3798998B2 (ja) * | 2002-06-28 | 2006-07-19 | 富士通株式会社 | 分岐予測装置および分岐予測方法 |

| US7000095B2 (en) | 2002-09-06 | 2006-02-14 | Mips Technologies, Inc. | Method and apparatus for clearing hazards using jump instructions |

| US7595752B2 (en) * | 2002-10-02 | 2009-09-29 | Global Locate, Inc. | Method and apparatus for enhanced autonomous GPS |

| JP2005078234A (ja) * | 2003-08-29 | 2005-03-24 | Renesas Technology Corp | 情報処理装置 |

| US20050216713A1 (en) * | 2004-03-25 | 2005-09-29 | International Business Machines Corporation | Instruction text controlled selectively stated branches for prediction via a branch target buffer |

-

2005

- 2005-05-31 US US11/139,984 patent/US7725695B2/en active Active

-

2006

- 2006-03-31 GB GB0606560A patent/GB2426842B/en active Active

- 2006-04-18 JP JP2006114589A patent/JP4727491B2/ja active Active

- 2006-05-30 CN CNB200610091510XA patent/CN100530081C/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN1873611A (zh) | 2006-12-06 |

| GB2426842B (en) | 2009-07-29 |

| US7725695B2 (en) | 2010-05-25 |

| US20060271770A1 (en) | 2006-11-30 |

| GB0606560D0 (en) | 2006-05-10 |

| GB2426842A (en) | 2006-12-06 |

| JP2006338656A (ja) | 2006-12-14 |

| JP4727491B2 (ja) | 2011-07-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100530081C (zh) | 分支预测控制 | |

| KR101074621B1 (ko) | 프로액티브 브랜치 타겟 어드레스 캐시 관리를 위한 방법들 및 장치 | |

| CN111886580B (zh) | 用于控制分支预测的装置和方法 | |

| KR100930199B1 (ko) | 루프―종료 브랜치들에 의한 브랜치 히스토리 레지스터의업데이트 억제 | |

| KR100974384B1 (ko) | 분기 명령들을 예측하기 위한 방법 및 장치 | |

| KR101459536B1 (ko) | 사전 통지 기법들을 사용하여 프로그램의 순차적 흐름을 변경하기 위한 방법들 및 장치 | |

| US6088793A (en) | Method and apparatus for branch execution on a multiple-instruction-set-architecture microprocessor | |

| US8156286B2 (en) | Processor and method for using an instruction hint to prevent hardware prefetch from using certain memory accesses in prefetch calculations | |

| JP2007515715A (ja) | 命令キャッシュからラベル境界上のトレースキャッシュに遷移させる方法 | |

| JP2011100466A5 (zh) | ||

| JP2008532142A5 (zh) | ||

| WO2008067277A2 (en) | Methods and apparatus for recognizing a subroutine call | |

| KR101026978B1 (ko) | 리턴 스택을 운용하는 방법 및 장치 | |

| US20040117606A1 (en) | Method and apparatus for dynamically conditioning statically produced load speculation and prefetches using runtime information | |

| US7640422B2 (en) | System for reducing number of lookups in a branch target address cache by storing retrieved BTAC addresses into instruction cache | |

| US20030204705A1 (en) | Prediction of branch instructions in a data processing apparatus | |

| US20040225866A1 (en) | Branch prediction in a data processing system | |

| US7343481B2 (en) | Branch prediction in a data processing system utilizing a cache of previous static predictions |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant |