CN100473066C - 简化的硬件网络适配器和通信方法 - Google Patents

简化的硬件网络适配器和通信方法 Download PDFInfo

- Publication number

- CN100473066C CN100473066C CNB008157006A CN00815700A CN100473066C CN 100473066 C CN100473066 C CN 100473066C CN B008157006 A CNB008157006 A CN B008157006A CN 00815700 A CN00815700 A CN 00815700A CN 100473066 C CN100473066 C CN 100473066C

- Authority

- CN

- China

- Prior art keywords

- data

- register

- network

- mac

- computer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000004891 communication Methods 0.000 title claims abstract description 38

- 238000000034 method Methods 0.000 title claims description 11

- 230000003139 buffering effect Effects 0.000 claims abstract description 8

- 230000006870 function Effects 0.000 claims description 32

- 230000005540 biological transmission Effects 0.000 claims description 22

- 238000012546 transfer Methods 0.000 claims description 4

- 230000014509 gene expression Effects 0.000 claims description 3

- 230000008878 coupling Effects 0.000 claims description 2

- 238000010168 coupling process Methods 0.000 claims description 2

- 238000005859 coupling reaction Methods 0.000 claims description 2

- 230000007423 decrease Effects 0.000 claims 2

- 238000001514 detection method Methods 0.000 description 9

- 101100172132 Mus musculus Eif3a gene Proteins 0.000 description 6

- 230000008859 change Effects 0.000 description 6

- 238000012545 processing Methods 0.000 description 6

- 108010022579 ATP dependent 26S protease Proteins 0.000 description 5

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 3

- 241001269238 Data Species 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 125000004122 cyclic group Chemical group 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 238000009434 installation Methods 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 230000009471 action Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 238000009432 framing Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 230000008520 organization Effects 0.000 description 1

- 230000002085 persistent effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 230000001052 transient effect Effects 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

- H04L12/407—Bus networks with decentralised control

- H04L12/413—Bus networks with decentralised control with random access, e.g. carrier-sense multiple-access with collision detection [CSMA-CD]

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/382—Information transfer, e.g. on bus using universal interface adapter

- G06F13/385—Information transfer, e.g. on bus using universal interface adapter for adaptation of a particular data processing system to different peripheral devices

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

- H04L12/40006—Architecture of a communication node

- H04L12/40013—Details regarding a bus controller

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

- H04L12/40006—Architecture of a communication node

- H04L12/40032—Details regarding a bus interface enhancer

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L49/00—Packet switching elements

- H04L49/90—Buffering arrangements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L49/00—Packet switching elements

- H04L49/90—Buffering arrangements

- H04L49/9063—Intermediate storage in different physical parts of a node or terminal

- H04L49/9068—Intermediate storage in different physical parts of a node or terminal in the network interface card

- H04L49/9073—Early interruption upon arrival of a fraction of a packet

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Communication Control (AREA)

- Small-Scale Networks (AREA)

Abstract

本发明提供了一种将客户计算机连接到一个计算机网络上的网络接口适配器,包括经一个物理接口(PHY)连接到网络物理链路上的一个简化的硬件媒体访问控制器(MAC)。MAC功能的重要部分被实施为主客户计算机的处理器内的软件。优选的MAC实施的硬件部分提供在PHY与客户计算机之间缓冲通信的存储器。本发明的MAC的优选硬件方面还包括一个寄存器接口,用于在MAC的硬件部分与在客户计算机内实施的MAC的软件部分之间的寄存器驱动通信。通过在主计算机的软件中实施大部分MAC功能,该优选的MAC提供了低成本、低功耗以及通常是更灵活的网络接口适配器。

Description

发明背景

1.发明领域

本发明涉及计算机与网络之间的适配器、接口和连接。作为一个具体的示例,本发明是按照计算机与网络间的一种适配器和一种通信方法描述的,其中,所述计算机网络根据一个工业标准协议,比如IEEE 802.3或者其扩展运行。

2.相关技术的描述

本发明总体涉及一种用于将一个计算机(在这里被称作客户计算机)连接到一个网络的适配器。本发明将结合一个为目前使用最普通的网络配置(通常称作一个EthernetTM网络)所设计的特定实施来描述和解释本发明。这种类型的网络通常包括执行IEEE 802.3标准,或者执行关于该标准的变化、修改或改进的那些网络。为了便于说明,所有这些网络都被称作IEEE 802.3网络,尽管该称谓不够精确。这里所涉及的网络提供了一个理解本发明的框架,如用于这些网络开发的适配器或接口控制器。

一个局域网的诸多客户计算机经常通过一个公共物理链路,比如同轴电缆、未屏蔽双绞线或屏蔽双绞线连接在一起。客户计算机将信息按帧单位发送到物理链路上,所述的帧具有多个协议规定的数据结构的一种结构,和具有最小帧长和最大帧长范围内的数据量。最简格式的IEEE 802.3协议仅允许一个客户计算机在任何独特的物理链路上发送一次信息。如果两个客户计算机同时向物理链路提供数据,或者在十分接近的时间提供数据,致使在两个消息信号之间产生干扰,则使该数据恶化并且必须丢弃该恶化的数据。这种事件被称作碰撞,并且必须由客户计算机检测。IEEE 802.3网络使用载波检测多路接入/碰撞检测(CSMA/CD)管理对物理链路的接入。在客户计算机向物理链路发送一个消息之前,客户计算机检测载波信号是否出现在物理链路上。如果载波信号出现在物理链路上,则在发送消息之前,客户计算机等待发送,直至该载波信号不存在以及物理链路变得可用。

一旦客户计算机确定物理链路是可用的,该客户计算机就向物理链路发送消息,使其在网络上传送。该客户计算机监视物理链路,以检测在物理链路上发送消息的同时可能发生的任何碰撞。在后续消息进行时段期间(在该期间发送计算机等待该消息到达其目的地),发送计算机持续监视发送之后的碰撞。在传送持续至少一个对应于最小帧长的时段之前,客户计算机应当检测碰撞,客户计算机应当连续发送一个信号,有时将这种情形称作一个阻塞序列。客户计算机随后暂停一个预定的随机时间量,并且试图获得对物理链路的接入以便再次发送数据。试图接入物理链路的每个客户计算机执行一个相似的补偿算法,不同的是,随机地分配等待时间,使单个客户计算机获得对物理链路的接入,而其它的等候计算机依次接入网络。

信息通常被组织成在EthernetTM或者其它类型的CSMA/CD网络上传送的多个帧。图1示出了用于EthernetTM帧的数据的帧结构,图2示出了根据标准的IEEE 802.3定义的一个帧的结构。这两种类型的网络使用了一个由1和0的交替模式组成的前同步,以通知接收站一个帧到达。Ethernet前同步(图1)还包括一个附加字节,它是在IEEE 802.3网络中定义的帧字节字段的起始字节的等同物。帧字节的起始字节(图2中SOF)用两个连续的“1”位结束,并且用来使与物理链路连接的站的帧同步接收。

这些网络的信息的组帧都包括了消息的目的地地址和源地址。目的地地址可以是一个单个目标计算机(单点传送)、一组计算机(多点传送)或网络上的所有计算机(广播)。源地址是特定传送计算机。EthernetTM帧包括一个识别接收消息的一个上层应用的协议的类型字段。该字段不出现在用于IEEE 802.3网络的帧上,并且由指定消息中的数据的字节数的一个长度字段替代。两个帧结构提供了一个在可能的长度范围内的任意长度的数据字段,其后是帧检验序列(FCS),它是一个四字节的循环冗余检验值。该FCS由发送计算机产生,并且由检验损坏帧的接收装置重新计算。

在CSMA/CD网络上传送数据帧的客户计算机使用一个网络接口控制器执行载波检测、碰撞检测以及数据传送和接收控制等其它方面的工作。数据传送控制包括生成帧格式和计算FCS字节。数据接收控制包括帧的检测、检查目的地地址以确定该消息是否用于该计算机、以及执行CRC或其它帧检验处理以确定帧是否有效。可以执行有关帧的其它方式的分析,或者当数据帧中或接收操作中存在误差时必须执行其它方式的分析。例如,如果在传送期间检测到一个差错,则必须重新发送信息。所有的这些处理是众所周知的,并且在普通适配器或控制器中执行,该适配器或控制器将客户计算机链接到局域CSMA/CD网络。

网络接口控制器被实施为一个集成电路,例如被实施为一个专用集成电路(ASIC)。图3示意性地图示了美国专利第5,872,920号描述的一个ASIC中以太网控制器的一个配置的示例。网络控制器ASIC 10连接主计算机系统的总线20,并且连接属于网络物理链路30的一部分的双绞线或同轴电缆。信息由收发信机40经物理接口发送和接收,或者经一个辅助单元接口42发送和接收。经物理链路30发送的信息由编码器44编码,解码器46解码从物理链路接收的信息。通常,Manchester编码和解码用于IEEE 802.3网络。

控制器50可以是一个微控制器或其它类型的处理器。通常提供控制器50作为ASIC 10中的核心,它使用合适的发送控制52和接收控制54程序或状态机器控制发送和接收操作。这些程序处理发送和接收来自CSMA/CD网络的数据所需的各种数据控制操作,包括例如处理物理媒介上的碰撞的差错条件,以及必要时重新发送恶化的数据。期望实施可应用的标准,比如IEEE 802.3的主要功能被实施在控制器50中。控制器50的输入和输出数据由发送FIFO 56和接收FIFO 58缓冲。主机接口60管理主计算机的通信,包括向主计算机的总线20供应数据。通过改写或更新EEPROM 62中存储的数据集或程序来完成数据供应,以更新主机接口60。这些电路的细节和实施的功能已经在美国专利第5,872,920号中描述,这里作为参考引用。

应当理解的是,尽管图3的网络接口被实施为一个单个ASIC,但其它配置也是公用的。例如,由于用于一个特定网络的物理实施(包括驱动磁盘、数模转换电路和模数转换电路)可以有很多种,因此经常需要提供编码器、解码器、收发信机以及专用芯片中物理链路的接口的其它方面。这个结构可以被实施为一个独特的PHY芯片,允许有较高的灵活性等级,它通常比更多集成的单芯片网络接口控制器方案更经济有效。在提供独特PHY芯片的实施中,通常是在第二芯片上提供网络控制器的其它方式,一个媒体访问控制器(MAC)芯片。图3中所示的网络控制器的MAC包括具有其程序的控制器或处理器50、缓冲存储器,以及在大多数情况下包括主机接口60。

已经做出相当多的努力增加集成电路网络接口控制器内设置的功能,比如增加图3所示的ASIC 10内设置的功能。例如,附加功能和灵活性已经做到网络接口控制器芯片中,以适应网络通信标准的改进或修改。目前已经对基础IEEE 802.3技术的较高速度变换给予了特别关注。

附图简要描述

通过结合下列说明及其附图,以更好地理解本发明的上述和其它方面。

图1表示以太网的一个帧结构;

图2表示根据IEEE 802.3标准的网络的一个帧结构;

图3表示一个网络接口控制芯片,在该芯片上提供一个高级功能;

图4表示本发明的一个方面的结构概况;

图5表示本发明的网络控制器的一个特定优选实施;

图6表示将一个客户计算机链接到一个网络的图5所示的网络接口控制器;

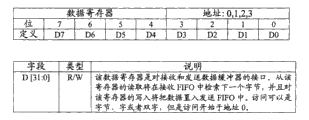

图7表示一个优选的寄存器组内诸多寄存器的地址和功能,该优选的寄存器组被设置在图5所示的控制器中;

图8表示图7所示的寄存器组的以太网数据寄存器的结构和功能;

图9表示图7所示的寄存器组的字节计数寄存器的结构和功能;

图10表示用于写操作的图7所示的寄存器组的命令/状态寄存器的结构和功能;

图11表示用于读操作的图7所示的寄存器组的命令/状态寄存器的结构和功能;

图12表示图7所示的寄存器组的MII(媒体独立接口)寄存器的结构和功能。

优选实施例的概述

本发明的优选实施例提供了一种简化的控制器,该控制器更适合于一个低成本、网络可兼容的计算机。通过提供一个相对简单的接口结构,和在主计算机的处理器内实施更多的网络接口控制功能,本发明的该优选实施例提供了网络接口的低成本、高灵活性的技术方案。

本发明的一个方面是提供了一种计算机通信系统,它具有一个至少连接一个发送数据线路的发送缓冲器。该发送缓冲器接收来自主计算机的数据,并且在经过发送数据线路向数据网络的物理链路发送数据之前暂时存储数据。一个接收缓冲器连接至少一个接收数据线路,该接收缓冲器适合于经接收数据线路接收来自数据网络的物理链路的数据,并且在向计算机提供数据之前暂时存储数据。此外,还提供了一个通信寄存器的阵列。该阵列包括连接接收缓冲器的数据寄存器,其中从数据寄存器重复的读取导致数据从接收缓冲器中读取。该阵列还包括一个状态寄存器,用于存储识别网络的物理链路上数据碰撞的数据,其中状态寄存器可从主计算机中读数据。该状态寄存器还包括至少一个位,用于表示读和写操作的至少一个操作的中断状态。

本发明的另一个方面是提供一种包括一个媒体访问控制器的计算机通信系统,该媒体访问控制器包括一个连接在媒体访问控制器上,用来接收来自数据网络并且在向主计算机提供数据之前暂时存储数据的接收缓冲器。媒体访问控制器具有通信寄存器,该寄存器包括连接所述接收缓冲器的一个数据寄存器,其中从数据寄存器重复读数据导致从接收缓冲器读数据。通信寄存器提供存储至少一个中断位的状态寄存器。该中断位被设置为:指示从数据网络接收并前往主计算机的数据的存在,并且指示待读取数据存在的该中断位可由主计算机读取。

本发明的另一个方面是提供一种包括一个媒体访问控制器的计算机通信系统,该媒体访问控制器包括多个通信寄存器。通信寄存器优选包括连接接收缓冲器的一个数据寄存器,其中从数据寄存器中重复读取数据导致读取从数据网络接收的数据。一个状态寄存器存储至少一个中断位,该中断位被设置成:指示从数据网络接收并前往主计算机的数据的存在,并且该中断位可由主计算机读取。一个媒体独立接口寄存器存储至少一个控制连接到媒体访问控制器的PHY电路的操作信号,其中来自主计算机的信号是从媒体独立接口寄存器传递的,以便当数据从数据网络读出时控制PHY电路。字节计数寄存器存储一个表示在媒体访问控制器中存储的向主计算机传送的字节数的值,其中当从媒体访问控制器读取数据时该字节计数寄存器被递减(计数值)。

优选实施例的详细说明

计算机与网络间的通信通常是经过网络接口控制器(NIC)或适配器实施的。本发明的优选实施例提供了网络接口控制器的一种简化的硬件实施。本发明的适配器的优选方面的实施可以向计算机提供比传统的控制器成本低功耗小的网络接口连接。本发明的一些方面能够以更容易修改的方式实施适配器,以便适应于技术的改变或者提供用于特殊的或特定的应用的解决方案。

本发明的特别优选的实施例向一个简化的硬件MAC提供了被实施为主客户计算机内的软件的MAC功能的一个有效部分。更优选的是,在客户计算机内实施的MAC功能被实施为客户计算机的一个处理器内的软件,更优选的是,该MAC功能被实施在个人计算机结构类型的主处理器内。优选的MAC实施的硬件部分提供了用于缓冲PHY与客户计算机之间通信的存储器。本发明的MAC的优选硬件方面还包括一个寄存器接口,用于MAC的硬件部分与客户计算机内实施的MAC的软件部分之间的寄存器驱动的通信。通过以主计算机内软件实施大多数MAC功能,优选的MAC提供了低成本、低功耗以及通常较大的灵活性。

本发明的一些方面可以在一个客户计算机或其它计算机与一个诸如根据定义的IEEE 802.3协议的任何方面操作的局域网络的网络之间提供一个接口。本发明的其它相关方面提供了一种传输信息的方法,或者提供了一种经过IEEE 802.3网络在一个计算机与一个或多个其它计算机之间传送信息的方法。术语IEEE 802.3在这里被广义地包含CSMA/CD网络,包括目前计划变更的包含千兆位EthernetTM的网络以及今后可能发展的其它变更的网络。本发明的这些方面被认为在与使用其他类型的协议的其它类型的网络进行连接和通信时具有优点。这里所提供的本发明的许多示例和解释是按照与IEEE 802.3网络通信进行说明的,这是因为这些网络是公知的(人们所通晓的)以及IEEE 802.3和EthernetTM网络目前很重要。然而,用于说明本发明的特定应用不应该限制本发明的范围。

同样,本发明的图示说明是在目前可用的并且使用的IEEE802.3协议的体系内作出的。IEEE 802.3的更先进的实施以及IEEE802.3的后继者将被开发并且带来市场前景。本发明的许多方面在应用于这种网络时,预计将具有诸多优点。

图4从概要结构的视角图示说明了客户计算机70的诸多方面,包括向/从一个网络传送信息。数据网络包括一个物理链路,比如向客户计算机和从客户计算机载送实际数据信号的线对或者同轴电缆。客户计算机70经图4所示的PHY 72表示的网络模型的物理层连接到该物理链路。PHY可以包括磁电路,用于将信号放置(耦合)到物理链路上以及从物理链路得到信号。PHY 72还包括适当的支持电路,比如模数变换器、数模变换器和锁相环检测电路,用于根据接收的或导出(得到)的时钟信号从物理链路恢复信号。通常,PHY 72还包括如图3所示的编码和解码电路。

PHY 72一般适合于特定的网络协议或定义。但是,同样地,以一种众所周知并且可被理解的方式,PHY 72的诸多方面在图4所示结构的不同应用之间可以变化很大。在不同的网络环境中采用多种方式,不论是作为一个独特的芯片还是作为设置在ASIC内的核心,PHY 72是商业可行的。

图4所示的下一个更高级的网络模型是媒体访问控制或MAC74。MAC 74可以包括一个功能范围,但是它通常服务于初始分析和格式化由PHY 72供应的数据位流的目的,使数据处于可由网络模式的上层立即使用的形式。MAC 74连接存储从网络接收数据的客户计算机70的操作系统76。MAC 74通常响应于经操作系统76通信的客户计算机的应用程序78,以生成用于信息传送或请求的消息。

MAC功能可以包括通信的多个不同的方面。例如,PHY 72可以以4位并行格式提供来自网络的数据。MAC优选将4位并行数据重新格式化成适合于客户计算机的字节或字,例如,8-位字节或32-位字。可以包含在MAC中的通信的其它方面是地址识别、帧识别、帧分析以及碰撞或其它形式的网络差错的检测和管理。如背景技术中的讨论和图3所示,MAC 74的传统的实施包括单个集成电路的各种功能。MAC的这种传统的实施提供了能够运行状态机器或执行这些功能的程序的一个处理器或其它形式的逻辑。

本发明的优选实施提供了至少从电路的观点看是简化的MAC。在大多数实施中,本发明的实施例将包括一个简化的硬件MAC以及一个补充软件MAC,它们优选在一个主处理器内,其组合将提供更多的功能,如果于图3所示的MAC所执行的功能不是更多的话。当然,根据本发明的一个实施例的MAC的实施可以提供较少的MAC功能,并且仍然实现本发明的诸多方面。与图3的MAC相对照,本发明的优选方面的MAC在客户计算机70的一个处理器中提供了最少一组电路并且实施了MAC功能的最多方面。在该实施中,本发明的一个MAC可以包括缓冲存储器和一个通信寄存器,该通信寄存器设有作为软件实施的MAC功能的其它方面,该软件由个人计算机或相似类型的客户计算机的微处理器运行。

图5说明了本发明的网络接口适配器79的优选硬件方面。如图所示,该适配器包括一个适合于目标网络物理链路的PHY 72和一个简化的硬件MAC。简化的硬件MAC包括用于缓冲数据的存储器,缓冲向PHY 72传送或从PHY 72接收的数据;优选的是,PHY72包括一个锁存器,用于存储也许仅仅出现在接收数据帧所需的总时间段的一个接收误差信号。所示的特定优选的MAC的剩余硬件方面是一组寄存器,用于处理指令、状态和误差信息的通信,并且促进适配器与客户计算机之间的数据传递。因而,所示的总线寄存器接口80优选包括完整的但相对最小的一组通信和数据寄存器,以便大部分通信功能在客户计算机内执行,并且优选在客户计算机的处理器中执行。

继续参见图5,顶部的两条线是与PHY 72内的媒体独立接口(MII)通信的信号线。信号线MDCK提供从接口80到PHY 72的数据时钟信号,并且用来读取和写入到PHY 72的MII的数据。MDIO是用于总线寄存器接口80与PHY 72之间MII通信的串行数据线。MDIO线路上供应的指令和其它信息的类型根据媒体独立接口的技术要求而定,这些技术要求是已知协议和工业标准。

图5所示的下两条线传送从PHY 72到总线寄存器接口80的网络条件。线路COL是一个在数据从PHY 72传送到物理链路期间在该物理链路上检测到碰撞时所传送的信号的线路。线路CRS载送一个在接收一个消息的时候识别物理链路上存在载波信号(载波检测)的信号。COL和CRS线路任一个上的信号被存储在接口80的命令/状态寄存器中,以便主客户计算机可以检测差错条件并执行适当的差错处理功能。

图5所示的下一条线路代表由PHY 72提供的到总线寄存器接口的信息,指示从物理链路接收的数据的有效性。线路RXER载送表现数据接收期间一个差错的信号。经线路RXER供应的信号可以是一个相对短暂的信号,至少与传送一个数据帧的时间量相比是一个短暂的信号。因此,优选沿着该线路设置一个锁存器82,以便在该锁存器内保持由PHY 72生成的一个差错信号,以确保在完成了数据帧的传送之后可利用总线寄存器接口80中的存储。线路TXER执行一个向物理链路传送数据的类似功能。当发现一个差错已经出现在向PHY 72传送数据并且位于物理线路之外时,接口80使一个信号供应到线路TXER上。例如,线路TXER可以用来指示一个下溢差错发生在MAC的发送缓冲器88上。

在所示的实施例中,总线寄存器接口80以8-位字节的单位存储数据。向和从PHY 72的供应的数据被安排为四个并行位。所以,需要将来自PHY的4位数据重新格式化成一个适当配置的寄存器84中的8位数据。寄存器84被显示为一个4-8位并行移位寄存器。寄存器84的输出被供应到一个接收缓冲器86,缓冲从物理线路接收的数据,然后经总线寄存器接口80读出数据进入客户计算机。来自客户计算机的数据以8-位字节供应给发送缓冲器88,经缓冲之后供应给寄存器90,寄存器90将8-位数据格式化成4-位数据项,并将该数据项供应给PHY 72。

接收缓冲器86和发送缓冲器88优选是字长适当的FIFO(先进先出存储器),以适应客户计算机的等待时间。由于图5所示的适配器的业务只是由客户计算机的优选微处理器执行的任务之一,因此会出现处理器不准备处理向物理链路发送的数据和从物理链路接收的数据的时候。因此,接收和发送FIFO需要具有足够的大小以适应典型的运行时间延迟。实际上,一般认为一个合适的缓冲器大小近似于一个信息包的大小或者相当于约2千字节。可以根据系统的设计选择适当的缓冲器大小。由于将要接收或者将发送数据的速率取决于适配器所服务的特定网络,因此缓冲器的大小在不同应用中变化非常明显。

图6图示说明了经一组双绞线对104将一个客户计算机100连接到一个网络102的适配器79的安装。所示的适配器79优选具有图5所示的结构,具体地说,设有包括图5所示的缓冲存储器和总线寄存器接口80的简化的硬件MAC 106。简化的硬件MAC 106优选经总线110连接客户计算机100的主处理器108。总线110优选是32位或更多位的总线,该总线以足够的速度操作,以便按照使等待时间最小化的预期速度传送(移动)进出MAC 106的数据。通过将MAC 106连接到一个适当的总线,比如PCI总线,或者在一个特定的优选实施例中,适于将PCMCIA卡连接到诸如笔记本或其它便携式计算机上的PC总线、卡总线或其它总线,可以容易地实现适当的总线速度。这些总线的典型实施对于允许像处理器108上运行的软件那样实施MAC功能的重要部分,是足够快的。适配器79的优选实施的精简尺寸和降低功耗对于本发明的便携式计算机实施是特别需要的。

当向网络102的物理链路发送信息和从该物理链路接收信息时,至少客户计算机的操作系统114的部分和MAC的软件方面116的部分应当在存储器112中获得。所示的存储器112可以部分位于处理器108中,部分位于DRAM的阵列中或者其它,包括例如在光盘驱动器上的较少的不稳定的存储器或者在快速或其它固态存储器中。在其它实施例中,所示的存储器112可以完全在处理器108的内部或外部。与特定存储器实施无关,MAC 116的软件方面优选通过对MAC 106内的通信寄存器80寻址,经过处理器108内的操作系统114与MAC的硬件方面进行通信。

通过使用一个优选的寄存器地址安排对总线寄存器接口80内的通信寄存器寻址。在图7部分图示的实施例中,一个3-位地址信号被用来对包含总共八个寄存器的一个最小寄存器实施寻址。如图所示,按四个最低地址设置四个数据寄存器,接下来两个寄存器和地址优选专用于字节计数寄存器,该字节计数寄存器存储可从接收FIFO 86读取得到的字节数。图8详细地说明了数据寄存器。来自数据寄存器的重复读取导致数据从接收FIFO 86中读出,并且对数字寄存器的重复写入将发送给网络102的数据充满发送FIFO 88。图9详细地表示了字节计数寄存器。这些字节计数寄存器用于读取操作,以指示是否剩余以及剩余了多少将要从网络102接收的数据。当数据被写入接收缓冲器时,字节计数寄存器存储的值递增,当数据从接收缓冲器86读出时,字节计数寄存器中存储的值递减。

应当注意的是,从网络接收的数据可以包括错误数据或者可以包括适当的帧数据。因而,通常不希望依赖传送的数据自身来指示是否剩余将要从网络接收的附加数据。

图10和图11分别示出了用于读/写操作的命令/状态寄存器,这两个寄存器具有相同的地址,但对于读和写操作的规定不同。位0被规定为,在写操作期间启动从适配器到客户计算机的操作系统的中断。命令/状态寄存器的位7由客户计算机设置,以复位适配器。该位借助适配器的复位自动清零。

当MAC软件116正在读适配器时,命令/状态寄存器(图11)将位0用作一个中断未决的位,以通知主客户计算机一个将要读出的中断未决。MAC软件116读命令/状态寄存器,以确定该中断需要采取什么动作、是否存在要读取的数据(BC)或者是否存在要处理的一个错误(COL,CRS)。一旦读取了该中断位,它就复位。剩余的位1-3提供载波检测、碰撞检测以及接收来自PHY的数据有效信号。当字节计数位BC不为零时,MAC软件开始读数据寄存器,以读取来自接收缓冲器86的数据。当COL或CRS位有效时,MAC软件116被访问,或者通过执行一个补偿算法(COL),或者通过放弃接收来处理差错条件,并且通过清洗错误数据的接收缓冲器来处理错误数据(CRS)。

图12说明了MII寄存器中位的定义,它占据了优选总线寄存器接口80中的最后的位置。MAC软件116使用MII或简化的媒体独立接口(RMII),以控制和监视PHY的操作。MII信息的通信经MII寄存器的MD位、经MDIO线路(图5)以及经PHY的MDIO引脚串行地进行。

MAC软件116控制适配器79的大量操作。通常,MAC软件可以被视作包括:一个处理中断和数据传送的底层段;一个上层段,用于执行更复杂的但较少直接的操作。MAC软件116的下层程序驱动接收操作中断,并且处理该中断。当操作系统114接收到来自适配器79的中断时,操作系统调用MAC软件的下层程序。

下层程序读命令/状态寄存器,以清零中断未决的位。如果有数据出现,则下层程序开始一个首次检验字节计数寄存器(图9)中字节计数的循环。如果字节计数为零,则下层程序退出该循环并且返回到备用装置,如果字节计数不为零,则从数据寄存器读取数据(图8)。该循环连续进行,直至字节计数达到零,然后下层程序退出循环并返回到备用状态直至检测到另一个中断。

由下层程序读出的数据被存储到处理器的缓冲器中或者存储到DRAM中。根据帧定义和有关IEEE 802.3的其它处理或者组织网络和通信进行的其它协议,进一步的处理是必要的。例如,用于IEEE 802.3网络的数据帧的处理可以包括检测帧头的处理器108,该处理器108检验帧长以确定该帧是否有一个有效帧长。该处理器使用FCS数据估算该帧,以估算该帧是否有效。例如,如果FCS数据是CRC数据,则使用定义检测多项式的协议对数据执行一个多项式除法,以确定数据是否有效。所有这些功能由MAC软件116的一个上层程序执行。该MAC软件还可以执行滤波,以检测信息包的地址是否与主客户计算机有关。

MAC软件还根据网络协议跟踪网络统计。这些统计包括成功发送的帧数以及发送错误帧的频度。这些统计可以由网络管理软件采用,比如可以由与一个简单的网络管理协议相一致的软件采用。

对网络的写数据的操作仍然是MAC软件116与适配器79之间的一个协作。MAC软件的上层程序将供应给网络的数据格式化成适当的帧,该上层程序计算FCS数据,比如一个适当的循环冗余检验(CRC)数据,并且将FCS添加到该帧上。数据帧被传送到MAC软件的下层程序,该程序将数据写入数据寄存器,进而写入适配器的发送FIFO 88。发送期间,MAC软件116的下层部分监视适配器,以保证数据从缓冲FIFO 88安全地传送到网络。例如,下层程序检验FIFO以查看FIFO是否被充满并且不能接收附加数据,或者查看FIFO是否已经完全空闲(一个下溢条件)。下层程序还监视命令/状态寄存器的COL位,以确定是否有一个碰撞。

MAC软件116的上层执行EthernetTM或IEEE 802.3网络的已知功能。这些功能按照惯例被实施为传统网络接口控制器的处理器内的软件或状态机器。因此,本领域的普通技术人员也能够将这些功能实施到微处理器中或者实施到主客户计算机的其它处理器中。因此将不进一步说明本发明的这些方面。

本发明的适配器的安装将通过把简化的硬件MAC安装到例如一个PCMCIA卡内进行,该PCMCIA卡也包括适合于目标网络的PHY电路。驱动软件以MAC软件能够被主计算机的操作系统访问的方式安装到主计算机上。

这里所讨论的设计的某些变更对于本领域的普通技术人员将是明显的。例如,可以容易地将图5所示的简化的硬件MAC实施为将要在一个ASIC中或者在PHY内实施的一个核心。有可能在一个芯片上将简化的硬件MAC实施为一个系统内的独特核心,而MAC的软件方面则实施在一个芯片的处理器的系统内。本发明的优选方面提供了网络接口适配器的一个灵活的结构。因此,本发明人期望本发明的适配器将在各种尚待完成的网络协议方面发现应用。此外,总线寄存器接口可以包括诸多寄存器的不同组合,以实现本发明的简化的硬件MAC。

本领域的普通技术人员将会明白,在不改变本发明的基本宗旨的情况下,可以对这里所述的特定实施例进行多种变化和修改。因此,本发明的范围不会被限制到这里所述的特定实施例上。更确定地说,本发明的范围由后面的权利要求确定。

Claims (26)

1.一种计算机通信系统,包括:

一个连接至少一个发送数据线路的发送缓冲器,所述的发送缓冲器适合于接收来自主计算机的数据,并且在经过发送数据线路向数据网络的物理链路发送数据之前暂时存储所述的数据;

一个连接至少一个接收数据线路的接收缓冲器,所述的接收缓冲器适合于经接收数据线路接收来自数据网络的物理链路的数据,并且在向计算机提供所述的数据之前暂时存储所述的数据;以及

一个通信寄存器的阵列,所述的阵列包括连接接收缓冲器的一个数据寄存器,其中,从所述的数据寄存器的重复读取导致从所述的接收缓冲器中读取数据;

所述的阵列还包括一个状态寄存器,用于存储识别数据网络的物理链路上数据碰撞的数据,所述的状态寄存器可从所述的主计算机读数据,所述的状态寄存器还包括至少一个表示读和写操作的至少一个操作的中断状态的位。

2.根据权利要求1所述的系统,还包括一个连接在阵列与到数据网络的连线之间的锁存器,所述的锁存器存储识别接收一个数据帧中的一个差错的差错信号,所述的锁存器保持所述的差错信号一个足以完整地接收所述的数据帧的时间段。

3.根据权利要求1所述的系统,其中,对数据寄存器的重复写入将数据存储在所述的发送缓冲器内。

4.根据权利要求1所述的系统,其中,所述的发送缓冲器经PHY电路连接所述的数据网络。

5.根据权利要求4所述的系统,其中,所述的阵列还包括一个媒体独立接口寄存器,存储至少一个用于控制所述的PHY电路的操作的信号,其中,在读写接入数据网络期间,诸多信号从所述的媒体独立接口寄存器传送,以控制所述的PHY。

6.根据权利要求1所述的系统,进一步包括媒体访问控制器,用于执行包括读取所述状态寄存器的媒体访问控制功能。

7.一种包括一个媒体访问控制器的计算机通信系统,所述的媒体访问控制器包括一个连接以接收来自数据网络的数据并且在向主计算机提供数据之前暂时存储所述的数据的接收缓冲器,

发送缓冲器,被连接以从所述主计算机接收数据,并在所述数据被传送给所述数据网络之前临时储存所述数据,

所述的媒体访问控制器还包括通信寄存器,所述的通信寄存器包括连接所述的接收缓冲器的一个数据寄存器,其中,从所述的数据寄存器重复读取导致从接收缓冲器读数据,以及

所述的通信寄存器还包括存储至少一个中断位的状态寄存器,所述的中断位被设置为:指示存在从所述的数据网络接收并前往主计算机的数据,并且指示存在待读取数据的所述的中断位可由主计算机读取。

8.根据权利要求7所述的系统,其中,所述的接收缓冲器经PHY电路连接所述的数据网络。

9.根据权利要求8所述的系统,其中,所述的通信寄存器包括一个媒体独立接口寄存器,存储至少一个控制所述的PHY电路的操作的信号,其中,当从所述的数据网络读取数据时,诸多来自主计算机的信号从所述的媒体独立接口寄存器传送,以控制所述的PHY。

10.根据权利要求7所述的系统,其中,所述的通信寄存器包括一个字节计数寄存器,用于存储一个指示在所述的接收缓冲器中存储的字节数的值,当从接收缓冲器读取数据时递减所述的字节计数寄存器。

11.根据权利要求10所述的系统,其中,驻留在所述的主计算机上的软件执行一序列步骤,包括检验所述的字节计数寄存器中存储的一个值,以及如果所述的字节计数寄存器存储了非零值,则从所述的数据寄存器读取数据。

12.根据权利要求8所述的系统,其中,进一步包括至少一个字节宽度的数据总线,用于将所述中断位读出到所述主计算机。

13.根据权利要求7所述的系统,还包括补充软件媒体访问控制器,与所述媒体访问控制器协作,以执行媒体访问控制。

14.根据权利要求8所述的系统,其中,所述的状态寄存器还包括多个可由所述的PHY电路置位的识别所述的数据网络的差错的位。

15.根据权利要求14所述的系统,其中,所述的多个位包括一个载波检测位。

16.根据权利要求15所述的系统,其中,所述的载波检测位能够由所述的主计算机的MAC程序直接读取。

17.一种包括一个媒体访问控制器的计算机通信系统,所述的媒体访问控制器包括多个通信寄存器,所述的通信寄存器包括:

一个连接所述的接收缓冲器的数据寄存器,其中,从所述的数据寄存器重复读取导致读取从所述的数据网络接收的数据,

一个包括至少一个中断位的状态寄存器,所述的中断位被设置成:指示从所述的数据网络接收并前往所述的主计算机的数据的存在,所述的中断位可由所述的主计算机读取,

一个媒体独立接口寄存器,存储至少一个用于控制与所述的媒体访问控制器连接的PHY电路操作的信号,其中,来自所述的主计算机的信号是从所述的媒体独立接口寄存器传递的,以便当数据从所述的数据网络读出时,控制PHY电路,以及

一个字节计数寄存器,存储一个指示在所述的媒体访问控制器中存储的用于传递到所述的主计算机的字节数的值,当从所述的媒体寄存器读取数据时递减所述的字节计数寄存器。

18.根据权利要求17所述的系统,其中,所述状态寄存器还包括多个识别所述数据网络的错误的位。

19.根据权利要求18所述的系统,其中,所述多个位包括一个载波检测位。

20.根据权利要求19所述的系统,其中,所述载波检测位能够由所述主计算机的MAC程序直接读取。

21.一种网络接口适配器,用于将客户计算机与计算机网络耦合,所述网络接口适配器包括:

一个简化的硬件媒体访问控制器,其通过一个物理接口与所述计算机网络相耦合,所述媒体访问控制器具有一个用于缓冲所述物理接口和所述客户计算机之间通信的存储器,所述媒体访问控制器进一步具有一个总线寄存器接口,用于处理所述网络接口适配器和所述客户计算机之间的通信。

22.根据权利要求21所述的适配器,其中,所述简化的硬件媒体访问控制器去除由所述适配器支持的整个硬件媒体访问控制器的功能性的显著部分。

23.根据权利要求21所述的适配器,其中,用于缓冲的所述存储器包括用于发送缓冲的存储器以及用于接收缓冲的存储器。

24.一种方法,包括:

通过一个发送缓冲器接收来自主计算机的数据,并且在经过发送数据线路向数据网络的物理链路发送所述数据之前暂时存储所述数据;

通过一个接收缓冲器接收所述数据,并且在向计算机提供所述数据之前暂时存储所述数据;

由于一个与所述接收缓冲器相耦合的数据寄存器的重复读取导致从所述接收缓冲器中读取所述数据;以及

使用一个状态寄存器,存储识别所述数据网络的物理链路上的数据碰撞的数据。

25.根据权利要求27所述的方法,其中,所述状态寄存器包括至少一个表示读和写操作的至少一个操作的中断状态的位。

26.根据权利要求27所述的方法,其中,所述数据寄存器和所述状态寄存器被包括在一个通信寄存器的阵列内。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/401,005 US6651107B1 (en) | 1999-09-21 | 1999-09-21 | Reduced hardware network adapter and communication |

| US09/401,005 | 1999-09-21 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1390417A CN1390417A (zh) | 2003-01-08 |

| CN100473066C true CN100473066C (zh) | 2009-03-25 |

Family

ID=23585878

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB008157006A Expired - Fee Related CN100473066C (zh) | 1999-09-21 | 2000-08-30 | 简化的硬件网络适配器和通信方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (3) | US6651107B1 (zh) |

| EP (1) | EP1216564A1 (zh) |

| JP (1) | JP4554863B2 (zh) |

| CN (1) | CN100473066C (zh) |

| AU (1) | AU8036500A (zh) |

| GB (1) | GB2369757B (zh) |

| WO (1) | WO2001022690A1 (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI817914B (zh) * | 2023-03-29 | 2023-10-01 | 智原科技股份有限公司 | 實體層模組與網路模組 |

Families Citing this family (42)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6651107B1 (en) | 1999-09-21 | 2003-11-18 | Intel Corporation | Reduced hardware network adapter and communication |

| US7143294B1 (en) * | 1999-10-29 | 2006-11-28 | Broadcom Corporation | Apparatus and method for secure field upgradability with unpredictable ciphertext |

| US6980563B2 (en) * | 2000-04-13 | 2005-12-27 | International Business Machines Corporation | Method and system for fast ethernet serial port multiplexing to reduce I/O pin count |

| US6963535B2 (en) * | 2000-12-28 | 2005-11-08 | Intel Corporation | MAC bus interface |

| US7039690B2 (en) * | 2001-08-01 | 2006-05-02 | Lucent Technologies Inc. | System and method for accessing registers of PHY device in network |

| US6865622B2 (en) * | 2002-05-13 | 2005-03-08 | Intel Corporation | System including real-time data communication features |

| CN100401731C (zh) * | 2002-06-15 | 2008-07-09 | 华为技术有限公司 | 高速数据链路控制协议接收处理模块及其数据处理方法 |

| CN1293739C (zh) * | 2002-06-15 | 2007-01-03 | 华为技术有限公司 | 高速数据链路控制协议发送处理模块及其数据处理方法 |

| US20040004974A1 (en) * | 2002-07-02 | 2004-01-08 | Harand Gaspar | Method and system for optimizing the design of a network controller |

| US7162564B2 (en) * | 2002-07-09 | 2007-01-09 | Intel Corporation | Configurable multi-port multi-protocol network interface to support packet processing |

| US7373561B2 (en) * | 2002-10-29 | 2008-05-13 | Broadcom Corporation | Integrated packet bit error rate tester for 10G SERDES |

| KR100481873B1 (ko) * | 2003-02-04 | 2005-04-11 | 삼성전자주식회사 | 절전모드를 갖는 매체 엑세스 제어기 |

| JP2004289561A (ja) * | 2003-03-24 | 2004-10-14 | Sony Corp | ネットワーク接続の管理方法および電子機器 |

| KR100489618B1 (ko) * | 2003-04-08 | 2005-05-17 | 엘지전자 주식회사 | 이더넷 링크 상태 관리 장치 및 방법 |

| US7373421B1 (en) * | 2003-06-12 | 2008-05-13 | Cisco Technology, Inc. | Method and apparatus of preventing physical layer from establishing unsupported links |

| JP2005012526A (ja) * | 2003-06-19 | 2005-01-13 | Mitsumi Electric Co Ltd | 通信方法、通信装置、及び、それを用いたゲームシステム、並びに、ゲームコントローラ |

| CN100338910C (zh) * | 2003-07-15 | 2007-09-19 | 中兴通讯股份有限公司 | 网络信息交换中多端口收发包数统计方法 |

| US8005055B2 (en) * | 2003-07-23 | 2011-08-23 | Interdigital Technology Corporation | Method and apparatus for determining and managing congestion in a wireless communications system |

| US20050128977A1 (en) * | 2003-07-23 | 2005-06-16 | Interdigital Technology Corporation | Method and apparatus for determining and managing congestion in a wireless communications system |

| CN1922846A (zh) * | 2004-02-19 | 2007-02-28 | 皇家飞利浦电子股份有限公司 | 使用介质访问控制动作表用于无线分组处理的方法和设备 |

| US20050213500A1 (en) * | 2004-03-29 | 2005-09-29 | Dan Gaur | Techniques to adaptively control flow thresholds |

| US7424553B1 (en) * | 2004-04-15 | 2008-09-09 | Xilinx, Inc. | Method and apparatus for communicating data between a network transceiver and memory circuitry |

| JP2006054853A (ja) * | 2004-07-14 | 2006-02-23 | Iwatsu Electric Co Ltd | 無線lanにおけるパケット伝送方法及び装置 |

| KR100738339B1 (ko) * | 2005-12-01 | 2007-07-12 | 한국전자통신연구원 | 인터넷 프로토콜 오프로드의 패킷 전송 장치 및 방법 |

| US20070260910A1 (en) * | 2006-04-04 | 2007-11-08 | Vinit Jain | Method and apparatus for propagating physical device link status to virtual devices |

| US8553720B2 (en) * | 2006-04-19 | 2013-10-08 | Marvell World Trade Ltd. | Adaptive speed control for MAC-PHY interfaces |

| US8346974B2 (en) | 2007-07-27 | 2013-01-01 | Microsoft Corporation | Hardware control interface for IEEE standard 802.11 |

| US8392637B2 (en) * | 2008-07-25 | 2013-03-05 | Broadcom Corporation | System and method for enabling legacy medium access control to do energy efficent ethernet |

| JP5602231B2 (ja) * | 2009-08-20 | 2014-10-08 | パーデュー・リサーチ・ファウンデーション | イベント駆動ワイヤレス・センサ・ネットワークのための予測的デューティ・サイクル順応方法 |

| US8289961B2 (en) * | 2009-08-20 | 2012-10-16 | Telefonaktiebolaget L M Ericsson (Publ) | Link state identifier collision handling |

| TWI416336B (zh) | 2009-11-10 | 2013-11-21 | Realtek Semiconductor Corp | 可共享緩衝器的網路介面卡與緩衝器共享方法 |

| CN102195783B (zh) * | 2010-03-11 | 2015-04-08 | 瑞昱半导体股份有限公司 | 可共享缓冲器的网络接口卡与缓冲器共享方法 |

| US8665895B2 (en) * | 2010-12-30 | 2014-03-04 | Broadcom Corporation | Advanced and dynamic physical layer device capabilities utilizing a link interruption signal |

| US9197584B2 (en) * | 2013-08-05 | 2015-11-24 | Globalfoundries Inc. | Increasing efficiency of data payloads to data arrays accessed through registers in a distributed virtual bridge |

| US9742689B1 (en) | 2013-12-27 | 2017-08-22 | Inphi Corporation | Channel negotiation for a high speed link |

| US9826019B2 (en) | 2014-10-27 | 2017-11-21 | Citrix Systems, Inc. | Input devices in high latency networks |

| US10007634B2 (en) * | 2015-12-07 | 2018-06-26 | Intel Corporation | Method to enable intel mini-mezz open compute project (OCP) plug-and-play network phy cards |

| CN108234252B (zh) * | 2016-12-22 | 2021-05-28 | 重庆川仪自动化股份有限公司 | 一种多路以太网通信系统 |

| CN108958453B (zh) * | 2018-07-03 | 2020-06-05 | 中国人民解放军国防科技大学 | 一种寄存器堆的低功耗访问方法及装置 |

| CN110247750B (zh) * | 2018-09-27 | 2022-07-08 | 浙江大华技术股份有限公司 | 一种网络传输装置及其状态同步方法 |

| US11805173B2 (en) * | 2021-05-05 | 2023-10-31 | Fluence Bioengineering, Inc. | Wireless network for horticultural systems |

| CN113572673A (zh) * | 2021-09-23 | 2021-10-29 | 深圳市迪壹六电子有限公司 | 一种基于总线的无感切换冗余通信实现方法及系统 |

Family Cites Families (73)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4672570A (en) | 1986-09-05 | 1987-06-09 | The United States Of America As Represented By The Secretary Of The Air Force | Network interface module and method |

| US4852088A (en) * | 1987-04-03 | 1989-07-25 | Advanced Micro Devices, Inc. | Packet-at-a-time reporting in a data link controller |

| US4965641A (en) * | 1989-02-21 | 1990-10-23 | Motorola, Inc. | Processor modem |

| DE3930316A1 (de) * | 1989-09-11 | 1991-03-21 | Carmelita Dr Rer Nat Goerg | Kanalzugriffsverfahren fuer ein als bus-system konfiguriertes lokales uebertragungsnetz |

| US5115432A (en) * | 1989-12-12 | 1992-05-19 | At&T Bell Laboratories | Communication architecture for high speed networking |

| US5299314A (en) | 1990-03-22 | 1994-03-29 | Xircom, Inc. | Network adapter using status inlines and data lines for bi-directionally transferring data between lan and standard p.c. parallel port |

| US5255187A (en) * | 1990-04-03 | 1993-10-19 | Sorensen Mark C | Computer aided medical diagnostic method and apparatus |

| US5103446A (en) * | 1990-11-09 | 1992-04-07 | Moses Computers, Inc. | Local area network adaptive throughput control for instantaneously matching data transfer rates between personal computer nodes |

| GB2264843B (en) | 1992-02-28 | 1995-09-20 | Texas Instruments Ltd | An interface device for coupling a host device having a network interface to a computer network having a predetermined communications medium |

| FI90710C (fi) | 1992-05-29 | 1994-03-10 | Icl Personal Systems Oy | Menetelmä paikallisverkkoon tarkoitetun TCP/IP-ohjelmiston sovittamiseksi etäyhteydelle |

| US5671355A (en) | 1992-06-26 | 1997-09-23 | Predacomm, Inc. | Reconfigurable network interface apparatus and method |

| US5412782A (en) | 1992-07-02 | 1995-05-02 | 3Com Corporation | Programmed I/O ethernet adapter with early interrupts for accelerating data transfer |

| US5414694A (en) * | 1993-02-19 | 1995-05-09 | Advanced Micro Devices, Inc. | Address tracking over repeater based networks |

| JP3503832B2 (ja) * | 1993-03-01 | 2004-03-08 | エスエス製薬株式会社 | 光学活性トリアゾール誘導体の製造法 |

| US5630061A (en) * | 1993-04-19 | 1997-05-13 | International Business Machines Corporation | System for enabling first computer to communicate over switched network with second computer located within LAN by using media access control driver in different modes |

| WO1995000914A1 (en) * | 1993-06-28 | 1995-01-05 | Scott & White Memorial Hospital And Scott, Sherwood And Brindley Foundation | Electronic medical record using text database |

| US5935060A (en) * | 1996-07-12 | 1999-08-10 | First Opinion Corporation | Computerized medical diagnostic and treatment advice system including list based processing |

| US5660176A (en) * | 1993-12-29 | 1997-08-26 | First Opinion Corporation | Computerized medical diagnostic and treatment advice system |

| US5678059A (en) * | 1994-02-18 | 1997-10-14 | Lucent Technologies Inc. | Technique for time-sharing a microprocessor between a computer and a modem |

| JPH07262152A (ja) * | 1994-03-24 | 1995-10-13 | Hitachi Ltd | コンピュータシステム |

| JP2801530B2 (ja) | 1994-08-17 | 1998-09-21 | 株式会社フジキカイ | 横型製袋充填包装機及びその制御方法 |

| US5784573A (en) | 1994-11-04 | 1998-07-21 | Texas Instruments Incorporated | Multi-protocol local area network controller |

| US5857075A (en) * | 1995-01-11 | 1999-01-05 | Sony Corporation | Method and integrated circuit for high-bandwidth network server interfacing to a local area network |

| US5812983A (en) * | 1995-08-03 | 1998-09-22 | Kumagai; Yasuo | Computed medical file and chart system |

| US5721830A (en) * | 1995-09-12 | 1998-02-24 | Pc-Tel, Inc. | Host signal processing communication system that compensates for missed execution of signal maintenance procedures |

| US5742603A (en) * | 1995-09-14 | 1998-04-21 | Level One Communications, Inc. | Method and apparatus for integrating repeater management, media access control, and bridging functions |

| US6064671A (en) * | 1995-12-08 | 2000-05-16 | Killian; Michael G. | Multi-homed end system for increasing computers network bandwidth |

| CA2166343C (en) * | 1995-12-29 | 1999-08-10 | Lee F. Hartley | Carrier sense collision avoidance with auto abort |

| US5974389A (en) * | 1996-03-01 | 1999-10-26 | Clark; Melanie Ann | Medical record management system and process with improved workflow features |

| EP1011419B1 (en) * | 1996-03-01 | 2002-05-02 | Medicomp Systems, Inc. | Method and apparatus to assist a user in creating a medical protocol |

| US5704371A (en) * | 1996-03-06 | 1998-01-06 | Shepard; Franziska | Medical history documentation system and method |

| US5812984A (en) * | 1996-05-13 | 1998-09-22 | Goltra; Peter S. | Method for entering information into an electronic patient chart, and protocol auto-negative capabilities |

| US5818826A (en) * | 1996-06-17 | 1998-10-06 | International Business Machines Corporation | Media access control protocols in a wireless communication network supporting multiple transmission rates |

| US5764896A (en) | 1996-06-28 | 1998-06-09 | Compaq Computer Corporation | Method and system for reducing transfer latency when transferring data from a network to a computer system |

| US5940459A (en) * | 1996-07-09 | 1999-08-17 | Pc-Tel, Inc. | Host signal processor modem and telephone |

| JP3688822B2 (ja) * | 1996-09-03 | 2005-08-31 | 株式会社東芝 | 電子カルテシステム |

| US6400715B1 (en) * | 1996-09-18 | 2002-06-04 | Texas Instruments Incorporated | Network address matching circuit and method |

| US5924074A (en) * | 1996-09-27 | 1999-07-13 | Azron Incorporated | Electronic medical records system |

| US6115776A (en) * | 1996-12-05 | 2000-09-05 | 3Com Corporation | Network and adaptor with time-based and packet number based interrupt combinations |

| US5950168A (en) * | 1996-12-18 | 1999-09-07 | Knowmed Systems | Collapsible flowsheet for displaying patient information in an electronic medical record |

| US6076115A (en) * | 1997-02-11 | 2000-06-13 | Xaqti Corporation | Media access control receiver and network management system |

| US6178483B1 (en) * | 1997-02-14 | 2001-01-23 | Advanced Micro Devices, Inc. | Method and apparatus for prefetching data read by PCI host |

| US5845152A (en) | 1997-03-19 | 1998-12-01 | Apple Computer, Inc. | Method for transmission of isochronous data with two cycle look ahead |

| US5970069A (en) * | 1997-04-21 | 1999-10-19 | Lsi Logic Corporation | Single chip remote access processor |

| US6172984B1 (en) * | 1997-06-19 | 2001-01-09 | Siemens Information And Communication Networks, Inc. | System and method for reducing the latency for time sensitive data over CSMA/CD networks |

| US6377998B2 (en) * | 1997-08-22 | 2002-04-23 | Nortel Networks Limited | Method and apparatus for performing frame processing for a network |

| US6226680B1 (en) * | 1997-10-14 | 2001-05-01 | Alacritech, Inc. | Intelligent network interface system method for protocol processing |

| US6434620B1 (en) * | 1998-08-27 | 2002-08-13 | Alacritech, Inc. | TCP/IP offload network interface device |

| US6122670A (en) * | 1997-10-30 | 2000-09-19 | Tsi Telsys, Inc. | Apparatus and method for constructing data for transmission within a reliable communication protocol by performing portions of the protocol suite concurrently |

| US6047001A (en) * | 1997-12-18 | 2000-04-04 | Advanced Micro Devices, Inc. | Apparatus and method in a network interface device for storing a data frame and corresponding tracking information in a buffer memory |

| US6061767A (en) * | 1997-12-18 | 2000-05-09 | Advanced Micro Devices, Inc. | Apparatus and method in a network interface device for storing status information contiguous with a corresponding data frame in a buffer memory |

| US6154750A (en) * | 1998-04-01 | 2000-11-28 | Cyberpulse Llc | Method and system for navigation and data entry in heirarchically-organized database views |

| US6275501B1 (en) * | 1998-04-21 | 2001-08-14 | Hewlett-Packard Company | Media access controller capable of connecting to a serial physical layer device and a media independent interface (MII) physical layer device |

| US6938040B2 (en) * | 1998-04-28 | 2005-08-30 | International Business Machines Corporation | Pattern matching in communications network where first memory stores set of patterns, and second memory stores mask data identifying patterns in the first memory |

| SE520101C2 (sv) * | 1998-05-13 | 2003-05-27 | Axis Ab | Integrerad krets och metod för att förmå en intgrerad krets att exekvera instruktioner |

| US6385208B1 (en) * | 1998-06-02 | 2002-05-07 | Cisco Technology, Inc. | Serial media independent interface |

| US6215764B1 (en) * | 1998-06-04 | 2001-04-10 | Silicon Integrated Systems Corp. | Method and apparatus for detecting the network link status of computer systems |

| US6349331B1 (en) * | 1998-06-05 | 2002-02-19 | Lsi Logic Corporation | Multiple channel communication system with shared autonegotiation controller |

| US6483846B1 (en) * | 1998-07-10 | 2002-11-19 | Honeywell Inc. | Middleware-based real-time communication system |

| US6393457B1 (en) * | 1998-07-13 | 2002-05-21 | International Business Machines Corporation | Architecture and apparatus for implementing 100 Mbps and GBPS Ethernet adapters |

| US6345310B1 (en) * | 1998-07-28 | 2002-02-05 | International Business Machines Corporation | Architecture for a multiple port adapter having a single media access control (MAC) with a single I/O port |

| US6373848B1 (en) * | 1998-07-28 | 2002-04-16 | International Business Machines Corporation | Architecture for a multi-port adapter with a single media access control (MAC) |

| US6065073A (en) * | 1998-08-17 | 2000-05-16 | Jato Technologies, Inc. | Auto-polling unit for interrupt generation in a network interface device |

| US6434165B1 (en) * | 1998-08-19 | 2002-08-13 | 3Com Corporation | Method and system to abort data communication traffic in a communication network |

| US6154796A (en) * | 1998-09-03 | 2000-11-28 | Advanced Micro Devices, Inc. | Apparatus and method in a network interface device for storing receiving frame status in a holding register |

| US7046625B1 (en) * | 1998-09-30 | 2006-05-16 | Stmicroelectronics, Inc. | Method and system for routing network-based data using frame address notification |

| US6408347B1 (en) * | 1998-12-10 | 2002-06-18 | Cisco Technology, Inc. | Integrated multi-function adapters using standard interfaces through single a access point |

| US6335938B1 (en) * | 1999-05-05 | 2002-01-01 | Advanced Micro Devices, Inc. | Multiport communication switch having gigaport and expansion ports sharing the same time slot in internal rules checker |

| US6725270B1 (en) * | 1999-05-21 | 2004-04-20 | Advanced Micro Devices, Inc. | Apparatus and method for programmably modifying a limit of a retry counter in a network switch port in response to exerting backpressure |

| US6338039B1 (en) * | 1999-07-20 | 2002-01-08 | Michael Lonski | Method for automated collection of psychotherapy patient information and generating reports and treatment plans |

| US6597683B1 (en) * | 1999-09-10 | 2003-07-22 | Pulse-Link, Inc. | Medium access control protocol for centralized wireless network communication management |

| US6651107B1 (en) | 1999-09-21 | 2003-11-18 | Intel Corporation | Reduced hardware network adapter and communication |

| US6816940B2 (en) * | 2000-02-17 | 2004-11-09 | Conexant Systems, Inc. | Cable modem having a programmable media access controller |

-

1999

- 1999-09-21 US US09/401,005 patent/US6651107B1/en not_active Expired - Lifetime

-

2000

- 2000-08-30 GB GB0206629A patent/GB2369757B/en not_active Expired - Fee Related

- 2000-08-30 JP JP2001525928A patent/JP4554863B2/ja not_active Expired - Fee Related

- 2000-08-30 CN CNB008157006A patent/CN100473066C/zh not_active Expired - Fee Related

- 2000-08-30 AU AU80365/00A patent/AU8036500A/en not_active Abandoned

- 2000-08-30 WO PCT/US2000/040775 patent/WO2001022690A1/en not_active Application Discontinuation

- 2000-08-30 EP EP00971075A patent/EP1216564A1/en not_active Withdrawn

-

2003

- 2003-10-08 US US10/682,572 patent/US7080162B2/en not_active Expired - Fee Related

-

2006

- 2006-04-06 US US11/399,628 patent/US20060184698A1/en not_active Abandoned

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI817914B (zh) * | 2023-03-29 | 2023-10-01 | 智原科技股份有限公司 | 實體層模組與網路模組 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20060184698A1 (en) | 2006-08-17 |

| US6651107B1 (en) | 2003-11-18 |

| JP4554863B2 (ja) | 2010-09-29 |

| GB2369757B (en) | 2004-03-24 |

| GB0206629D0 (en) | 2002-05-01 |

| GB2369757A (en) | 2002-06-05 |

| WO2001022690A1 (en) | 2001-03-29 |

| US20040139220A1 (en) | 2004-07-15 |

| US7080162B2 (en) | 2006-07-18 |

| EP1216564A1 (en) | 2002-06-26 |

| CN1390417A (zh) | 2003-01-08 |

| AU8036500A (en) | 2001-04-24 |

| JP2003510905A (ja) | 2003-03-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100473066C (zh) | 简化的硬件网络适配器和通信方法 | |

| US6839345B2 (en) | MAC/PHY interface | |

| US6016308A (en) | Method and system for increasing network information carried in a data packet via packet tagging | |

| EP0980612B1 (en) | Physical layer device having a media independent interface for connecting to either media access control entities or other physical layer devices | |

| US4590467A (en) | Local area network interface controller | |

| US5764896A (en) | Method and system for reducing transfer latency when transferring data from a network to a computer system | |

| US8452996B2 (en) | Operating mode for extreme power savings when no network presence is detected | |

| US6105079A (en) | Apparatus and method in a network interface device for selectively supplying long bit information related to a data frame to a buffer memory and a read controller for initiation of data transfers | |

| US6047001A (en) | Apparatus and method in a network interface device for storing a data frame and corresponding tracking information in a buffer memory | |

| JP4376329B2 (ja) | データストリームにおける所定のパターンを検出するための装置、データストリームにおける所定のパターンを検出するための方法、およびデータパケットにおける所定のパターンを識別するためのネットワークインターフェイスにおける方法 | |

| EP0459753A2 (en) | Network access controller having logical FIFO buffer | |

| US4593281A (en) | Local area network interframe delay controller | |

| WO1998045996A1 (en) | Power savings in multiple technology physical layer devices supporting autonegotiation | |

| US6229817B1 (en) | System and method for programming late collision slot time | |

| EP1401155B1 (en) | Method and system for wakeup packet detection at gigabit speeds | |

| US6061768A (en) | Apparatus and method in a network interface device for storing tracking information indicating stored data status between contending memory controllers | |

| US6516371B1 (en) | Network interface device for accessing data stored in buffer memory locations defined by programmable read pointer information | |

| US6012117A (en) | Methods and apparatus for arbitrating and controlling arbitration for access to a serial bus | |

| WO2001017166A2 (en) | Ethernet 10/100 media access controller core | |

| US7325167B2 (en) | System and method for using network interface card reset pin as indication of lock loss of a phase locked loop and brownout condition | |

| US6128308A (en) | Apparatus and method for determining a presence of a stored data frame in a random access memory independent of read and write clock domains | |

| US20060004926A1 (en) | Smart buffer caching using look aside buffer for ethernet | |

| EP1059590A1 (en) | Method for pre-processing packets in a bus interface | |

| JPH07131473A (ja) | データ通信装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20090325 Termination date: 20100830 |