BR122015017257B1 - Dispositivo de codificação de vídeo, dispositivo de decodificação de vídeo, método de codificação de vídeo e método de decodificação de vídeo - Google Patents

Dispositivo de codificação de vídeo, dispositivo de decodificação de vídeo, método de codificação de vídeo e método de decodificação de vídeo Download PDFInfo

- Publication number

- BR122015017257B1 BR122015017257B1 BR122015017257-8A BR122015017257A BR122015017257B1 BR 122015017257 B1 BR122015017257 B1 BR 122015017257B1 BR 122015017257 A BR122015017257 A BR 122015017257A BR 122015017257 B1 BR122015017257 B1 BR 122015017257B1

- Authority

- BR

- Brazil

- Prior art keywords

- inter

- size

- video

- prediction

- encoding

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/134—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the element, parameter or criterion affecting or controlling the adaptive coding

- H04N19/146—Data rate or code amount at the encoder output

- H04N19/147—Data rate or code amount at the encoder output according to rate distortion criteria

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/50—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using predictive coding

- H04N19/59—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using predictive coding involving spatial sub-sampling or interpolation, e.g. alteration of picture size or resolution

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/102—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the element, parameter or selection affected or controlled by the adaptive coding

- H04N19/103—Selection of coding mode or of prediction mode

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/102—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the element, parameter or selection affected or controlled by the adaptive coding

- H04N19/103—Selection of coding mode or of prediction mode

- H04N19/109—Selection of coding mode or of prediction mode among a plurality of temporal predictive coding modes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/102—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the element, parameter or selection affected or controlled by the adaptive coding

- H04N19/119—Adaptive subdivision aspects, e.g. subdivision of a picture into rectangular or non-rectangular coding blocks

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/134—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the element, parameter or criterion affecting or controlling the adaptive coding

- H04N19/157—Assigned coding mode, i.e. the coding mode being predefined or preselected to be further used for selection of another element or parameter

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/169—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the coding unit, i.e. the structural portion or semantic portion of the video signal being the object or the subject of the adaptive coding

- H04N19/17—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the coding unit, i.e. the structural portion or semantic portion of the video signal being the object or the subject of the adaptive coding the unit being an image region, e.g. an object

- H04N19/176—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the coding unit, i.e. the structural portion or semantic portion of the video signal being the object or the subject of the adaptive coding the unit being an image region, e.g. an object the region being a block, e.g. a macroblock

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/44—Decoders specially adapted therefor, e.g. video decoders which are asymmetric with respect to the encoder

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/46—Embedding additional information in the video signal during the compression process

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/70—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals characterised by syntax aspects related to video coding, e.g. related to compression standards

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/169—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the coding unit, i.e. the structural portion or semantic portion of the video signal being the object or the subject of the adaptive coding

- H04N19/184—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the coding unit, i.e. the structural portion or semantic portion of the video signal being the object or the subject of the adaptive coding the unit being bits, e.g. of the compressed video stream

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/50—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using predictive coding

- H04N19/503—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using predictive coding involving temporal prediction

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/60—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding

- H04N19/61—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding in combination with predictive coding

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/65—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using error resilience

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/90—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using coding techniques not provided for in groups H04N19/10-H04N19/85, e.g. fractals

- H04N19/91—Entropy coding, e.g. variable length coding [VLC] or arithmetic coding

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S348/00—Television

- Y10S348/91—Flicker reduction

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Compression Or Coding Systems Of Tv Signals (AREA)

- Two-Way Televisions, Distribution Of Moving Picture Or The Like (AREA)

Abstract

DISPOSITIVO DE CODIFICAÇÃO DE VÍDEO, DISPOSITIVO DE DECODIFICAÇÃO DE VÍDEO, MÉTODO DE CODIFICAÇÃO DE VÍDEO, MÉTODO DE DECODIFICAÇÃO DE VÍDEO E MEIO DE GRAVAÇÃO DE INFORMAÇÃO LEGÍVEL POR COMPUTADOR Um dispositivo de codificação de vídeo para codificação de vídeo usando interprevisão inclui o meio de controle de codificação (11) para ajustar valores capazes de uma partição de inter-PU de um CU a ser codificado, com base em uma relação entre um tamanho mínimo de inter-PU (PA) e um tamanho (PB) do CU a ser codificado. Um dispositivo de decodificação de vídeo inclui o meio de controle de decodificação para ajustar valores capazes de uma partição de inter-PU de um CU a ser decodificado, com base em uma relação entre o tamanho mínimo de inter-PU (PA) e o tamanho (PB) do CU a ser decodificado.

Description

[0001] A presente invenção refere-se a um dispositivo de codificação de vídeo, um dispositivo de decodificação de vídeo, um método de codificação de vídeo, um método de decodificação de vídeo e um programa que usa as unidades hierárquicas de codificação.

[0002] A Literatura de Não Patente (NPL) 1 revela o sistema típico de codificação de vídeo e sistema de decodificação de vídeo.

[0003] Um dispositivo de codificação de vídeo descrito em NPL 1 tem uma estrutura conforme mostrada na figura 15. O dispositivo de codificação de vídeo mostrado na figura 15 é denominado um dispositivo típico de codificação de vídeo abaixo.

[0004] Com referência à figura 15, a estrutura e operação do dispositivo típico de codificação de vídeo que recebe o quadro do vídeo digitalizado como entrada e produz a corrente de bit são abaixo descritas.

[0005] O dispositivo de codificação de vídeo mostrado na figura 15 inclui um transformador/quantizador 101, um codificador de entropia 102, um transformador inverso/quantizador inverso 103, um buffer 104, um previsor 105, um multiplexador 106 e um controlador de codificação 108.

[0006] O dispositivo de codificação de vídeo mostrado na figura 15 divide cada quadro em blocos de tamanho de 16x16 pixels denominado macro blocos (MBs), e criptografa cada MB sequencialmente da esquerda superior do quadro.

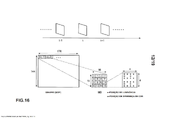

[0007] A figura 16 é um diagrama explicativo mostrando um exemplo de divisão de bloco no caso em que o quadro tenha uma resolução espacial de QCIF (Quarter Common Intermediate Format [Formato Intermediário Comum de Quarto]). O seguinte descreve a operação de cada unidade enquanto enfoca somente nos valores de pixel de luminância para fins de simplicidade.

[0008] Um sinal de previsão fornecido a partir do previsor 105 é subtraído do vídeo de entrada dividido por bloco, e o resultado é a entrada ao transformador/quantizador 101 como uma imagem de erro de previsão. Existem dois tipos de sinais de previsão, isto é, um sinal de intraprevisão e um sinal de interprevisão. O sinal de interprevisão também é denominado um sinal de interprevisão de quadro.

[0009] Cada um dos sinais de previsão é abaixo descrito. O sinal de intraprevisão é um sinal de previsão gerado com base em uma imagem de uma foto reconstruída que tem o mesmo tempo de display que uma foto atual armazenada no buffer 104.

[0010] Com referência ao processo de previsão 8.3.1 Intra_4x4 para amostras luma, processo de previsão 8.3.2 Intra_8x8 para amostras luma e processo de previsão 8.3.3 Intra_16x16 para amostras luma em NPL 1, a intraprevisão de três tamanhos de bloco, i.e., Intra_4x4, Intra_8x8 e Intra_16x16, estão disponíveis.

[0011] Intra_4x4 e Intra_8x8 são respectivamente intraprevisão de tamanho de bloco de 4x4 e tamanho de bloco de 8x8, conforme pode ser entendido a partir de (a) e (c) na figura 17. Cada círculo (o) no desenho representa um pixel de referência usado para intraprevisão, i.e., um pixel da foto reconstruída tendo o mesmo tempo de display que a foto atual.

[0012] Na intraprevisão de Intra_4x4, os pixels periféricos reconstruídos são diretamente definidos como pixels de referência, e usados para enchimento (extrapolação) em nove direções mostradas em (b) da figura 17 para formar o sinal de previsão. Na intraprevisão de Intra_8x8, os pixels obtidos ao uniformizar pixels periféricos da imagem da foto reconstruída por filtros passa-baixo (1/2, 1/4, 1/2) mostrados sob a seta direita em (c) da figura 17 são definidos como pixels de referência, e usados para extrapolação nas nove direções mostradas em (b) da figura 17 para formar o sinal de previsão.

[0013] De forma semelhante, Intra_16x16 é a intraprevisão do tamanho de bloco de 16 x 16, conforme pode ser entendido a partir de (a) na figura 18. Como na figura 17, cada círculo (o) no desenho representa um pixel de referência usado para intraprevisão, i.e., um pixel da foto reconstruída tendo o mesmo tempo de display que a foto atual. Na intraprevisão de Intra_16x16, os pixels periféricos da imagem da foto reconstruída são diretamente definidos como pixels de referência, e usados para extrapolação em quatro direções mostradas em (b) da figura 18 para formar o sinal de previsão.

[0014] Doravante, um MB e um bloco criptografado usando o sinal de intraprevisão são denominados um intra-MB e um intrabloco, respectivamente, i.e., um tamanho de bloco de intraprevisão é denominado um tamanho de bloco de intraprevisão, e uma direção de extrapolação é denominada uma direção de intraprevisão. O tamanho de bloco de intraprevisão e a direção de intraprevisão são parâmetros de previsão relacionados à intraprevisão.

[0015] O sinal de interprevisão é um sinal de previsão gerado a partir de uma imagem de uma foto reconstruída diferente no tempo de display daquele que a foto atual tem e é armazenado no buffer 104. Doravante, um MB e um bloco criptografado usando o sinal de interprevisão são denominados um inter-MB e um interbloco, respectivamente. Um tamanho de bloco de interprevisão (tamanho de bloco de interprevisão) pode ser selecionado a partir de, por exemplo, 16 x 16, 16 x 8, 8 x 16, 8 x 8, 8 x 4, 4 x 8 e 4 x 4.

[0016] A figura 19 é um diagrama explicativo mostrando um exemplo de interprevisão usando o tamanho de bloco de 16 x 16. Um vetor de movimento MV = (mvx, mvy) mostrado na figura 19 é um parâmetro de previsão de interprevisão, que indica a quantidade de tradução paralela de um bloco de interprevisão (sinal de interprevisão) de uma foto de referência relativa a um bloco a ser codificado. Em AVC, os parâmetros de previsão de interprevisão incluem não somente uma direção de interprevisão representando uma direção da foto de referência de um sinal de interprevisão relativo a uma foto a ser codificado do bloco a ser codificado, porém também um índice de foto de referência para identificar a foto de referência usada para interprevisão do bloco a ser codificado. Isso é devido, em AVC, múltiplas fotos de referência armazenadas no buffer 104 podem ser usadas para interprevisão.

[0017] Na interprevisão de AVC, um vetor de movimento pode ser calculado na exatidão de 1/4 de pixel. A figura 20 é um diagrama explicativo mostrando o processamento de interpolação para sinais de luminância na previsão compensada por movimento. Na figura 20, A representa um sinal de pixel em uma posição de pixel de número inteiro, b, c, d representam sinais de pixel nas posições decimais de pixel com exatidão de 1/2 de pixel, e e1, e2, e3 representamos sinais de pixel nas posições decimais de pixel com exatidão de 1/4 de pixel. O sinal de pixel b é gerado ao aplicar um filtro de seis derivações para pixels nas posições horizontais de pixel de número inteiro. Da mesma forma, o sinal de pixel c é gerado ao aplicar o filtro de seis derivações aos pixels nas posições verticais de pixel de número inteiro. O sinal de pixel d é gerado ao aplicar o filtro de seis derivações aos pixels nas posições horizontais ou verticais decimais de pixel com exatidão de 1/2 de pixel. Os coeficientes do filtro de seis derivações são representados como [1, -5, 20, 20, -5, 1]/32. Os sinais de pixel e1, e2, e e3 são gerados ao aplicar um filtro de duas derivações [1, 1]/2 para pixels nas posições adjacentes de pixel de número inteiro ou posições decimais de pixel, respectivamente.

[0018] Uma foto criptografada ao incluir somente intra- MBs é denominada uma foto I. Uma foto criptografada ao incluir não somente intra-MBs, porém também inter-MBs é denominada uma foto P. Uma foto criptografada ao incluir inter-MBs que usa não somente uma foto de referência, porém duas fotos de referência simultaneamente para interprevisão é denominada uma foto B. Na foto B, a interprevisão em que a direção da foto de referência do sinal de interprevisão relativo à foto a ser codificado do bloco a ser codificado é passada é denominada previsão avançada, a interprevisão em que a direção da foto de referência do sinal de interprevisão relativo à foto a ser codificado do bloco a ser codificado é futura é denominada previsão regressiva, e a interprevisão simultaneamente usando duas fotos de referência envolvendo tanto o passado quanto o futuro é denominada previsão bidirecional. A direção de interprevisão (direção de interprevisão) é um parâmetro de previsão de interprevisão.

[0019] Em conformidade com uma instrução do controlador de codificação 108, o previsor 105 compara um sinal de vídeo de entrada com um sinal de previsão para determinar um parâmetro de previsão que minimiza a energia de um bloco de imagem de erro de previsão. O controlador de codificação 108 fornece o parâmetro determinado de previsão ao codificador de entropia 102.

[0020] O transformador/quantizador 101 transforma por frequência a imagem (imagem de erro de previsão) a partir da qual o sinal de previsão foi subtraído para obter um coeficiente de transformação de frequência.

[0021] O transformador/quantizador 101 ainda quantiza o coeficiente de transformação de frequência com uma largura predeterminada de etapa de quantização Qs. Doravante, o coeficiente quantizado de transformação de frequência é denominado um valor de quantização de transformação.

[0022] O codificador de entropia 102 codifica por entropia os parâmetros de previsão e o valor de quantização de transformação. Os parâmetros de previsão são informações associadas à previsão de MB e bloco, tal como, modo de previsão (intraprevisão, interprevisão), tamanho de bloco de intraprevisão, direção de intraprevisão, tamanho de bloco de interprevisão e vetor de movimento acima mencionados.

[0023] O transformador inverso/quantizador inverso 103 quantiza de forma inversa o valor de quantização de transformação com a largura predeterminada de etapa de quantização Qs. O transformador inverso/quantizador inverso 103 ainda realiza a transformação de frequência inversa do coeficiente de transformação de frequência obtido pela quantização inversa. O sinal de previsão é adicionado à imagem reconstruída de erro de previsão obtido pela transformação de frequência inversa, e o resultado é fornecido ao buffer 104.

[0024] O buffer 104 armazena a imagem reconstruída fornecida. A imagem reconstruída para um quadro é denominada uma foto reconstruída.

[0025] O multiplexador 106 multiplexa e produz os dados de saída do codificador de entropia 102 e parâmetros de codificação.

[0026] Com base na operação acima descrita, o multiplexador 106 no dispositivo de codificação de vídeo gera uma corrente de bit.

[0027] Um dispositivo de decodificação de vídeo descrito em NPL 1 tem uma estrutura conforme mostrada na figura 21. Doravante, o dispositivo de decodificação de vídeo mostrado na figura 21 é denominado um dispositivo típico de decodificação de vídeo.

[0028] Com referência à figura 21, a estrutura e operação do dispositivo típico de decodificação de vídeo que recebe a corrente de bit como entrada e produz um quadro de vídeo decodificado são descritas.

[0029] O dispositivo de decodificação de vídeo mostrado na figura 21 inclui um desmultiplexador 201, um decodificador de entropia 202, um transformador inverso/quantizador inverso 203, um previsor 204 e um buffer 205.

[0030] O desmultiplexador 201 desmultiplexa a corrente de bit de entrada e extrai uma corrente de bit de vídeo codificada por entropia.

[0031] O decodificador de entropia 202 decodifica por entropia a corrente de bit de vídeo. O decodificador de entropia 202 decodifica por entropia os parâmetros de previsão de MB e bloco e o valor de quantização de transformação, e fornece os resultados ao transformador inverso/quantizador inverso 203 e previsor 204.

[0032] O transformador inverso/quantizador inverso 203 quantiza de forma inversa o valor de quantização de transformação com a largura de etapa de quantização. O transformador inverso/quantizador inverso 203 ainda realiza a transformação de frequência inversa do coeficiente de transformação de frequência obtido pela quantização inversa.

[0033] Após a transformação de frequência inversa, o previsor 204 gera um sinal de previsão usando uma imagem de uma foto reconstruída armazenada no buffer 205 com base nos parâmetros de previsão de MB e bloco codificados por entropia.

[0034] Após a geração do sinal de previsão, o sinal de previsão fornecido a partir do previsor 204 é adicionado a uma imagem reconstruída de erro de previsão obtido pela transformação de frequência inversa realizada pelo transformador inverso/quantizador inverso 203, e o resultado é fornecido ao buffer 205 como uma imagem reconstruída.

[0035] Então, a foto reconstruída armazenada no buffer 205 é produzida como uma imagem decodificada (vídeo decodificado).

[0036] Com base na operação acima descrita, o dispositivo típico de decodificação de vídeo gera a imagem decodificada.

[0037] NPL 1: ISO/IEC 14496-10 Codificação Adiantada de Vídeo

[0038] NPL 2: “Modelo de Teste sob Consideração,” Documento: JCTVC-B205, Equipe Colaborativa Conjunta sobre Codificação de Vídeo (JCT-VC) de ITU-T SG16 WP3 e ISO/IEC JTC1/SC29/WG11 2° Reunião: Genebra, CH, 21-28 de julho de 2010

[0039] NPL 2 revela o Modelo de Teste sob Consideração (TMuC). Diferente daquele revelado em NPL 1, o TMuC usa as unidades hierárquicas de codificação (Codificando Três Blocos (CTBs)) mostradas na figura 22. Nesta especificação, os blocos CTB são denominados Unidades de Codificação (CUs).

[0040] Aqui, o maior CU é denominado a Maior Unidade de Codificação (LCU), e o menor CU é denominado Menor Unidade de Codificação (SCU). No esquema TMuC, o conceito de Unidade de Previsão (PU) é introduzido como uma unidade de previsão para cada CU (ver figura 23). O PU é uma unidade básica de previsão, e oito tipos de partição de PU {2Nx2N, 2NxN, Nx2N, NxN, 2NxnU, 2NxnD, nLx2N, nRx2N} mostrados na figura 23 são definidos. O PU usado para interprevisão é denominado um inter-PU e o PU usado para intraprevisão é denominado intra- PU. A partição de PU para a qual a interprevisão é usada é denominada partição de inter-PU, e a partição de PU para a qual a intraprevisão é usada é denominada partição de intra- PU. Entre os formatos mostrados na figura 23, somente os quadrados de 2Nx2N e NxN são suportados como partições de intra-PU. Doravante, os comprimentos de um lado de um CU e um PU são denominados tamanho de CU e tamanho de PU, respectivamente.

[0041] O esquema TMuC pode usar um filtro com até doze derivações para buscar uma imagem prevista com uma exatidão decimal. A relação entre a posição de pixel e coeficiente de filtro é conforme segue. Tabela 1

[0042] A posição de pixel é descrita com referência à figura 24. Na figura 24, é presumido que A e E são pixels nas posições de pixel de número inteiro. Neste caso, b é um pixel na posição de pixel de 1/4, c é um pixel na posição de pixel de 1/2, e d é um pixel na posição de pixel de 3/4. O mesmo se aplica àqueles na direção vertical.

[0043] O pixel b ou pixel c mostrado na figura 20 é gerado ao aplicar um filtro para posição horizontal ou vertical de pixel de 1/2 uma vez. O pixel e1 é gerado ao aplicar um filtro para a posição de pixel de 1/4 uma vez.

[0044] Com referência à figura 25, uma descrição é feita de um exemplo de geração de pixels decimais, tais como, pixel e2 e pixel e3, cujas posições de pixel são posições de exatidão decimal em ambas as direções horizontais e verticais e pelo menos qualquer uma delas é a posição de pixel de 1/4. Na figura 25, é presumido que pixel A é um pixel em uma posição de pixel de número inteiro e o pixel c é um pixel em uma posição de pixel decimal a ser obtido. Neste caso, o pixel b é primeiramente gerado ao aplicar um filtro para posição vertical de pixel de 1/4. Então, o pixel c é gerado ao aplicar um filtro para a posição horizontal de pixel de 3/4 relativa ao pixel decimal b. Nos Métodos de Interpolação 8.3 de NPL 2, a geração de pixels decimais é descrita em mais detalhes.

[0045] No esquema TMuC, um indicativo de sintaxe de um tipo de partição de PU em cada cabeçote de PU de CUs em todos os níveis (de acordo com a sintaxe de unidade de previsão 4.1.10 em NPL 2, intra_split_flag no caso de intraprevisão e inter_partitioning_idc no caso de interprevisão) é embutido em uma corrente de bit de saída. Doravante, a sintaxe intra_split_flag é denominada uma sintaxe do tipo de partição de intra-PU, e a sintaxe inter_partitioning_idc é denominada uma sintaxe do tipo de partição de inter-PU.

[0046] Quando muitos CUs de pequeno tamanho existem dentro de cada LCU, a razão do número de bits da sintaxe do tipo de partição de inter-PU incluída na corrente de bit aumenta, causando um problema que a qualidade do vídeo comprimido é reduzida.

[0047] Além disso, no esquema TMuC, os acessos de memória às fotos de referência aumentam conforme o tamanho da partição de inter-PU torna-se menor, causando um problema de deformar a largura de banda de memória. Especificamente, já que o filtro de doze derivações é usado para gerar um pixel decimal no esquema TMuC, a largura de banda de memória é mais deformada.

[0048] A figura 26 é um diagrama explicativo para descrever as áreas de acesso de memória quando o filtro de doze derivações é usado. A figura 26(A) mostra uma área de acesso de memória de uma partição de inter-PU quando o tipo de partição de PU de NxN é selecionado, e a figura 26(B) mostra uma área de acesso de memória quando o tipo de partição de inter-PU de 2Nx2N é selecionado.

[0049] Quando NxN é selecionado, já que o acesso de memória de um tamanho cercado pela linha pontilhada na figura 26(A) é realizado quatro vezes no total para cada uma das partições de inter-PU 0, 1, 2, 3, a quantidade do acesso de memória tem um valor obtido ao multiplicar 4(N + 11)2 = 4N2 + 88N + 484 pela contagem de bit de uma foto de referência. Já que a quantidade do acesso de memória da partição de inter-PU 2Nx2N tem um valor obtido ao multiplicar (2N + 11)2 = 4N2 + 44N + 121 pela contagem de bit da foto de referência, a quantidade do acesso de memória da partição de inter-PU NxN torna-se maior do que a quantidade do acesso de memória de 2Nx2N.

[0050] Por exemplo, a quantidade do acesso de memória de inter-PUs em um CU 8x8 quando N =4, a previsão é a previsão unidirecional, e a exatidão de bit de cada valor de pixel é 8 bits é considerada. A quantidade do acesso de memória na partição de inter-PU 2Nx2N é de 19 x 19 x 1 x 8 bits = 2888 bits, enquanto a quantidade do acesso de memória na partição de inter-PU NxN é de 15 x 15 x 4 x 8 bits = 7200 bits, cuja quantidade do acesso de memória é cerca de 2,5 vezes.

[0051] Nas unidades de LCU, se o tamanho de bloco de LCU é de 128 x 128, a quantidade do acesso de memória quando o LCU é previsto por uma partição de inter-PU será 139 x 139 x 1 x 8 bits = 154568 bits, enquanto a quantidade do acesso de memória quando o LCU é todo previsto por partições de inter- PU 4x4 (i.e., quando o LCU é previsto por 1024 partições de inter-PU) será de 15 x 15 x 1024 x 8 bits = 1843200 bits, cuja quantidade do acesso de memória é cerca de doze vezes.

[0052] É um objeto da presente invenção reduzir a largura de banda de memória por ar pré-determinada e a predeterminada.

[0053] Um dispositivo de codificação de vídeo de acordo com a presente invenção é um dispositivo de codificação de vídeo para codificação de vídeo usando interprevisão, que inclui o meio de controle de codificação para ajustar valores capazes de uma partição de inter-PU de um CU a ser codificado, com base em uma relação entre um tamanho mínimo de inter-PU e um tamanho do CU a ser codificado.

[0054] Um dispositivo de decodificação de vídeo de acordo com a presente invenção é um dispositivo de decodificação de vídeo para decodificação de vídeo usando interprevisão, que inclui o meio de controle de decodificação ajustando valores capazes de uma partição de inter-PU de um CU a ser decodificado, com base em uma relação entre um tamanho mínimo de inter-PU e um tamanho do CU a ser decodificado.

[0055] Um método de codificação de vídeo de acordo com a presente invenção é um método de codificação de vídeo para codificação de vídeo usando interprevisão, que inclui ajustando valores capazes de uma partição de inter-PU de um CU a ser codificado, com base em uma relação entre um tamanho mínimo de inter-PU e um tamanho do CU a ser codificado.

[0056] Um método de decodificação de vídeo de acordo com a presente invenção é um método de decodificação de vídeo para decodificação de vídeo usando interprevisão, que inclui ajustar valores capazes de uma partição de inter-PU de um CU a ser decodificado, com base em uma relação entre um tamanho mínimo de inter-PU e um tamanho do CU a ser decodificado.

[0057] Um meio de gravação de informação legível por computador armazenando um programa de codificação de vídeo de acordo com a presente invenção faz com que um computador para codificação de vídeo usando interprevisão execute um método para um processo de configuração valores capazes de uma partição de inter-PU de um CU a ser codificado, com base em uma relação entre um tamanho mínimo de inter-PU e um tamanho do CU a ser decodificado.

[0058] Um meio de gravação de informação legível por computador armazenando um programa de decodificação de vídeo de acordo com a presente invenção faz com que um computador para decodificação de vídeo usando interprevisão execute um método para um processo de configuração valores capazes de uma partição de inter-PU de um CU a ser decodificado, com base em uma relação entre um tamanho mínimo de inter-PU e um tamanho do CU a ser decodificado.

[0059] De acordo com a presente invenção, o uso de pequenas partições de inter-PU pode ser restrito para reduzir a largura de banda de memória.

[0060] A figura 1 é um diagrama de bloco de um dispositivo de codificação de vídeo na Realização Exemplar 1;

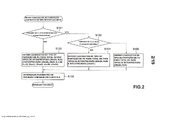

[0061] A figura 2 é um fluxograma mostrando um processo de determinar candidatos de tipo de partição de PU;

[0062] A figura 3 é um diagrama explicativo de uma lista indicativa das informações sobre o tamanho mínimo de inter-PU em um conjunto de parâmetro de sequência;

[0063] A figura 4 é um fluxograma mostrando a operação de escrita de cabeçote de PU;

[0064] A figura 5 é um diagrama explicativo de uma lista indicativa das informações sobre a sintaxe inter_partitioning_idc em uma sintaxe de PU;

[0065] A figura 6 é um diagrama de bloco de um dispositivo de decodificação de vídeo na Realização Exemplar 2;

[0066] A figura 7 é um fluxograma mostrando a operação de análise de cabeçote de PU;

[0067] A figura 8 é um diagrama explicativo de uma lista indicativa das informações sobre o tamanho mínimo de inter-PU em um conjunto de parâmetro de foto;

[0068] A figura 9 é um diagrama explicativo de uma lista indicativa das informações sobre o tamanho mínimo de inter-PU em um cabeçote dividido;

[0069] A figura 10 é um diagrama de bloco de um dispositivo de decodificação de vídeo na Realização Exemplar 4;

[0070] A figura 11 é um fluxograma mostrando uma operação de detecção de erro;

[0071] A figura 12 é um diagrama de bloco mostrando um exemplo de configuração de um sistema de processamento de informações capaz de implantar as funções de um dispositivo de codificação de vídeo e um dispositivo de decodificação de vídeo de acordo com a presente invenção;

[0072] A figura 13 é um diagrama de bloco mostrando a parte principal de um dispositivo de codificação de vídeo de acordo com a presente invenção;

[0073] A figura 14 é um diagrama de bloco mostrando a parte principal de um dispositivo de decodificação de vídeo de acordo com a presente invenção;

[0074] A figura 15 é um diagrama de bloco de um dispositivo típico de codificação de vídeo;

[0075] A figura 16 é um diagrama explicativo mostrando um exemplo da divisão de bloco;

[0076] A figura 17 é um diagrama explicativo para descrever intraprevisão de Intra_4x4 e Intra_8*8;

[0077] A figura 18 é um diagrama explicativo para descrever intraprevisão de Intra_16x16;

[0078] A figura 19 é um diagrama explicativo mostrando um exemplo de interprevisão;

[0079] A figura 20 é um diagrama explicativo mostrando o processamento de interpolação para os sinais de luminância na previsão compensada por movimento;

[0080] A figura 21 é um diagrama de bloco de um dispositivo típico de decodificação de vídeo;

[0081] A figura 22 é um diagrama explicativo para descrever

[0082] A figura 23 é um diagrama explicativo para descrever um PU;

[0083] A figura 24 é um diagrama explicativo para descrever posições decimais de pixel;

[0084] A figura 25 é um diagrama explicativo para descrever um método de geração de pixel decimal usando um filtro de doze derivações em um esquema TMuC; e

[0085] A figura 26 é um diagrama explicativo para descrever uma variação de acesso de memória quando um pixel decimal é gerado usando o filtro de doze derivações.

[0086] Com a finalidade de resolver os problemas técnicos das técnicas típicas acima mencionadas, a presente invenção restringe as partições de inter-PU com base na profundidade de CU (i.e., tamanho de CU) na codificação de vídeo usando unidades hierárquicas de codificação para resolver os problemas. Em um exemplo da presente invenção, o tamanho de CU capaz de usar partições de inter-PU, exceto 2Nx2N, é restrito para resolver os problemas. Em outro exemplo da presente invenção, a transmissão de uma sintaxe do tipo de partição de inter-PU em um cabeçote de PU é restrita para resolver os problemas. No exemplo acima da presente invenção, a razão do número de bits da sintaxe do tipo de partição de inter-PU incluída em uma corrente de bit pode ser mantida baixa para suprimir a largura de banda de memória enquanto melhora a qualidade do vídeo comprimido.

[0087] A Realização Exemplar 1 mostra um dispositivo de codificação de vídeo incluindo: meio de controle de codificação para ajustar valores capazes de uma partição de inter-PUcom base em um tamanho mínimo de inter-PU predeterminado definido a partir da parte externa; e meio para embutir, em uma corrente de bit, as informações sobre o tamanho mínimo de inter-PU para sinalizar as informações sobre o tamanho mínimo de inter-PU a um dispositivo de decodificação de vídeo.

[0088] Nesta realização exemplar, é presumido que os tamanhos disponíveis de CU são 128, 64, 32, 16, e 8 (i.e., o tamanho de LCU é 128 e o tamanho de SCU é 8), e o tamanho mínimo de inter-PU (minInterPredUnitSize) é 8.

[0089] Ainda é presumido na realização exemplar que as informações sobre o tamanho mínimo de inter-PU (min_inter_pred_unit_hierarchy_depth) são log de 2 bases (logaritmo) de um valor obtido ao dividir o tamanho mínimo de inter-PU (8) pelo tamanho de SCU (8). Dessa forma, na realização exemplar, o valor de min_inter_pred_unit_hierarchy_depth multiplexado na corrente de bit é de 0 (= log2(8/8)).

[0090] Conforme mostrado na figura 1, o dispositivo de codificação de vídeo na realização exemplar inclui um transformador/quantizador 101, um codificador de entropia 102, um transformador inverso/quantizador inverso 103, um buffer 104, um previsor 105, um multiplexador 106 e um controlador de codificação 107, como o dispositivo típico de codificação de vídeo mostrado na figura 15.

[0091] O dispositivo de codificação de vídeo na realização exemplar mostrado na figura 1 difere do dispositivo de codificação de vídeo mostrado na figura 15 de modo que minInterPredUnitSize é fornecido ao controlador de codificação 107 para transmitir uma sintaxe do tipo de partição de inter- PU em um tamanho de CU superior a minInterPredUnitSize, e minInterPredUnitSize também é fornecido ao multiplexador 106 para sinalizar minInterPredUnitSize ao dispositivo de decodificação de vídeo.

[0092] O controlador de codificação 107 tem o previsor 105 para calcular um custo (custo de Taxa-Distorção: custo RD) calculado a partir de uma distorção de codificação (uma energia de uma imagem de erro entre um sinal de entrada e uma foto reconstruída) e uma contagem gerada de bit. O controlador de codificação 107 determina um padrão de divisão de CU em que o custo R-D é minimizado (o padrão de divisão determinado por split_coding_unit_flag conforme mostrado na figura 22), e os parâmetros de previsão de cada CU. O controlador de codificação 107 fornece split_coding_unit_flag determinado e os parâmetros de previsão de cada CU ao previsor 105 e codificador de entropia 102. Os parâmetros de previsão são informações associadas à previsão de um CU a ser codificado, tal como, modo de previsão (pred_mode), tipo de partição de intra-PU (intra_split_flag), direção de intraprevisão, tipo de partição de inter-PU (inter_partitioning_idc) e vetor de movimento.

[0093] Como um exemplo, o controlador de codificação 107 na realização exemplar seleciona o tipo ideal de partição de PU como um parâmetro de previsão para um CU cujo tamanho seja superior a minInterPredUnitSize a partir de um total de dez tipos de intraprevisão {2NX2N, NxN}, e interprevisão {2NX2N, 2NXN, Nx2N, NXN, 2NxnU, 2NxnD, nLx2N, nRx2N}. Para um CU cujo tamanho seja igual a minInterPredUnitSize, o controlador de codificação 107 seleciona o tipo ideal de partição de PU como um parâmetro de previsão a partir de um total de três tipos de intraprevisão {2Nx2N, NxN} e interprevisão {2Nx2N}. Para um CU cujo tamanho seja inferior a minInterPredUnitSize, o controlador de codificação 107 seleciona o tipo ideal de partição de PU como um parâmetro de previsão a partir de dois tipos de intraprevisão {2Nx2N, NxN}.

[0094] A figura 2 é um fluxograma mostrando a operação do controlador de codificação 107 na realização exemplar para determinar candidatos de tipo de partição de PU.

[0095] Conforme mostrado na figura 2, ao determinar na etapa S101 que o tamanho de CU de um CU a ser codificado é superior do que minInterPredUnitSize, o controlador de codificação 107 define os candidatos de tipo de partição de PU na etapa S102 para um total de dez tipos de intraprevisão {2Nx2N, NxN} e interprevisão {2Nx2N, 2NxN, Nx2N, NxN, 2NxnU, 2NxnD, nLx2N, nRx2N}, e determina na etapa S106 um parâmetro de previsão com base no custo R-D.

[0096] Ao determinar na etapa S101 que o tamanho de CU do CU a ser codificado é inferior ou igual a minInterPredUnitSize, o controlador de codificação 107 prossegue para a etapa S103.

[0097] Ao determinar na etapa S103 que o tamanho de CU do CU a ser codificado é igual a minInterPredUnitSize, o controlador de codificação 107 define os candidatos de tipo de partição de PU na etapa S104 para um total de três tipos de intraprevisão {2NX2N, NxN} e interprevisão {2NX2N}, e determina na etapa S106 um parâmetro de previsão com base no custo R-D.

[0098] Ao determinar na etapa S103 que o tamanho de CU do CU a ser codificado é inferior a minInterPredUnitSize, o controlador de codificação 107 define os candidatos de tipo de partição de PU na etapa S105 para dois tipos de intraprevisão {2NX2N, NXN}, e determina na etapa S106 o tipo ideal de partição de PU como um parâmetro de previsão com base no custo R-D.

[0099] O previsor 105 seleciona um sinal de previsão correspondente aos parâmetros de previsão de cada CU determinados pelo controlador de codificação 107.

[0100] O sinal de previsão fornecido a partir do previsor 105 é subtraído do vídeo de entrada de cada CU em um formato determinado pelo controlador de codificação 107 para gerar uma imagem de erro de previsão, e a imagem de erro de previsão é entrada ao transformador/quantizador 101.

[0101] O transformador/quantizador 101 transforma por frequência a imagem de erro de previsão para obter um coeficiente de transformação de frequência.

[0102] O transformador/quantizador 101 ainda quantiza o coeficiente de transformação de frequência com uma largura predeterminada de etapa de quantização Qs para obter um valor de quantização de transformação.

[0103] O codificador de entropia 102 codifica por entropia split_coding_unit_flag (ver figura 22) fornecido a partir do controlador de codificação 107, os parâmetros de previsão e o valor de quantização de transformação fornecidos a partir do transformador/quantizador 101.

[0104] O transformador inverso/quantizador inverso 103 quantiza de forma inversa o valor de quantização de transformação com a largura predeterminada de etapa de quantização Qs. O transformador inverso/quantizador inverso 103 ainda realiza a transformação de frequência inversa do coeficiente de transformação de frequência obtido pela quantização inversa. O sinal de previsão é adicionado à imagem reconstruída de erro de previsão obtida pela transformação de frequência inversa, e o resultado é fornecido ao buffer 104.

[0105] O multiplexador 106 multiplexa e produz as informações sobre o tamanho mínimo de inter-PU (min_inter_pred_unit_hierarchy_depth) e dados de saída do codificador de entropia 102. De acordo com a sintaxe de conjunto de parâmetro de sequência RBSP 4.1.2 em NPL 2, o multiplexador 106 multiplexa a sintaxe log2_min_coding_unit_size_minus3 e sintaxe min_inter_pred_unit_hierarchy_depth após a sintaxe max_coding_unit_hierarchy_depth em um conjunto de parâmetro de sequência conforme listado na figura 3 (log de 2 bases (logaritmo) de um valor obtido ao dividir minInterPredUnitSize pelo tamanho de SCU, i.e., 0 na realização exemplar). A sintaxe log2_min_coding_unit_size_minus3 e a sintaxe max_coding_unit_hierarchy_depth são informações para determinar um tamanho de SCU (minCodingUnitSize) e um tamanho de LCU (maxCodingUnitSize), respectivamente. MinCodingUnitSize e maxCodingUnitSize são respectivamente calculados conforme segue. minCodingUnitSize = 1<< (log2_min_coding_unit_size_minus3 + 3) maxCodingUnitSize = 1<< (log2_min_coding_unit_size_minus3 + 3 + max_coding_unit_hierarchy_depth) A sintaxe min_inter_pred_unit_hierarchy_depth e minCodingUnitSize possuem a seguinte relação. min_inter_pred_unit_hierarchy_depth = log2(minInterPredUnitSize /minCodingUnitSize)

[0106] Com base na operação acima descrita, o dispositivo de codificação de vídeo de acordo com esta invenção gera uma corrente de bit.

[0107] Com base em um tamanho mínimo de inter-PU predeterminado e um tamanho de CU de um CU a ser codificado, o dispositivo de codificação de vídeo na realização exemplar controla a partição de inter-PU do CU a ser codificado de modo que nenhum inter-PU, cujo tamanho seja inferior ao tamanho mínimo de inter-PU, entrará em existência.

[0108] A largura de banda de memória é reduzida ao impedir qualquer inter-PU, cujo tamanho seja inferior ao tamanho mínimo de inter-PU, de entrar em existência. Além disso, já que o número de sintaxes do tipo de partição de inter-PU a ser sinalizado é reduzido ao impedir qualquer inter-PU, cujo tamanho seja inferior ao tamanho mínimo de inter-PU de entrar em existência, a porcentagem da quantidade do código de um cabeçote de PU na corrente de bit é reduzida, e, consequentemente, a qualidade do vídeo é melhorada.

[0109] O meio de controle de codificação no dispositivo de codificação de vídeo da realização exemplar controla as partições de inter-PU com base no tamanho mínimo de inter-PU predeterminado definido a partir da parte externa. Como um exemplo, o meio de controle de codificação controla tipos de partição de inter-PU, exceto 2Nx2N, a serem usados somente em CUs de tamanhos de CU superiores a um tamanho predeterminado. Portanto, já a probabilidade de ocorrência da partição de inter-PU 2N*2N aumenta para reduzir a entropia, a eficiência da codificação por entropia é melhorada. Dessa forma, a qualidade do vídeo comprimido pode ser mantida enquanto reduz a largura de banda de memória.

[0110] Da mesma forma, para decodificação de vídeo, o dispositivo de codificação de vídeo na realização exemplar inclui o meio para embutir, em uma corrente de bit, informações sobre o tamanho mínimo de inter-PU predeterminado definido a partir da parte externa de modo que a sintaxe do tipo de partição de inter-PU possa ser analisada a partir da corrente de bit. Dessa forma, já que o tamanho predeterminado é sinalizado ao dispositivo de decodificação de vídeo, a interoperabilidade do dispositivo de codificação de vídeo e o dispositivo de decodificação de vídeo pode ser aprimorada.

[0111] Um dispositivo de codificação de vídeo na Realização Exemplar 2 inclui: meio de controle de codificação para ajustar valores capazes de uma partição de inter-PUcom base em um tamanho mínimo de inter-PU predeterminado definido a partir da parte externa e para controlar codificação por entropia de uma sintaxe do tipo de partição de inter-PU com base no tamanho mínimo de inter-PU predeterminado acima; e meio para embutir, em uma corrente de bit, informações sobre o tamanho mínimo de inter-PU para sinalizar as informações sobre o tamanho mínimo de inter-PU acima a um dispositivo de decodificação de vídeo.

[0112] Nesta realização exemplar, é presumido que o tamanho de CU de um CU para transmitir a sintaxe do tipo de partição de inter-PU é superior do que o tamanho mínimo de inter-PU acima (minInterPredUnitSize). Também é presumido na realização exemplar que os tamanhos disponíveis de CU são 128, 64, 32, 16 e 8 (i.e., o tamanho de LCU é 128 e o tamanho de SCU é 8), e minInterPredUnitSize é 8. Dessa forma, na realização exemplar, os tamanhos de CU para embutir a sintaxe do tipo de partição de inter-PU na corrente de bit são de 128, 64, 32 e 16.

[0113] Ainda é presumido na realização exemplar que as informações sobre o tamanho mínimo de inter-PU (min_inter_pred_unit_hierarchy_depth) é log de 2 bases (logaritmo) de um valor obtido ao dividir o tamanho mínimo de inter-PU (8) pelo tamanho de SCU (8). Dessa forma, na realização exemplar, o valor de min_inter_pred_unit_hierarchy_depth multiplexado na corrente de bit é de 0(=log2(8/8)).

[0114] A estrutura do dispositivo de codificação de vídeo na realização exemplar é a mesma que a estrutura do dispositivo de codificação de vídeo na Realização Exemplar 1 mostrada na figura 1.

[0115] Conforme mostrado na figura 1, o dispositivo de codificação de vídeo nesta realização exemplar difere do dispositivo de codificação de vídeo mostrado na figura 15 de modo que minInterPredUnitSize é fornecido ao controlador de codificação 107 para transmitir um sintaxe do tipo de partição de inter-PU em um tamanho de CU superior a minInterPredUnitSize, e minInterPredUnitSize também é fornecido ao multiplexador 106 para sinalizar minInterPredUnitSize ao dispositivo de decodificação de vídeo.

[0116] O controlador de codificação 107 tem o previsor 105 para calcular o custo R-D calculado a partir de uma distorção de codificação (uma energia de uma imagem de erro entre um sinal de entrada e uma foto reconstruída) e uma contagem gerada de bit. O controlador de codificação 107 determina um padrão de divisão de CU em que o custo R-D é minimizado (o padrão de divisão determinado por split_coding_unit_flag conforme mostrado na figura 22), e parâmetros de previsão de cada CU. O controlador de codificação 107 fornece o split_coding_unit_flag determinado e parâmetros de previsão de cada CU ao previsor 105 e codificador de entropia 102. Os parâmetros de previsão são informações associadas à previsão de um CU a ser codificado, tal como, modo de previsão (pred_mode), tipo de partição de intra-PU (intra_split_flag), direção de intraprevisão, tipo de partição de inter-PU (inter_partitioning_idc) e vetor de movimento.

[0117] Como na Realização Exemplar 1, o controlador de codificação 107 na realização exemplar seleciona o tipo ideal de partição de PU como um parâmetro de previsão para um CU cujo tamanho seja superior a minInterPredUnitSize a partir de um total de dez tipos de intraprevisão {2Nx2N, NxN} e interprevisão {2Nx2N, 2NxN, Nx2N, NxN, 2NxnU, 2NxnD, nLx2N, nRx2N}. Para um CU cujo tamanho seja igual a minInterPredUnitSize, o controlador de codificação 107 seleciona o tipo ideal de partição de PU como um parâmetro de previsão a partir de um total de três tipos de intraprevisão {2Nx2N, NxN} e interprevisão {2Nx2N}. Para um CU cujo tamanho seja inferior a minInterPredUnitSize, o controlador de codificação 107 seleciona o tipo ideal de partição de PU como um parâmetro de previsão a partir de intraprevisão {2Nx2N, NxN} .

[0118] Quando o modo de previsão de um CU a ser criptografado por entropia é interprevisão e o tamanho de CU é inferior ou igual a minInterPredUnitSize, o controlador de codificação 107 na realização exemplar controla o codificador de entropia 102 para não criptografar por entropia inter_partitioning_idc.

[0119] O previsor 105 seleciona um sinal de previsão correspondente aos parâmetros de previsão de cada CU determinado pelo controlador de codificação 107.

[0120] O sinal de previsão fornecido a partir do previsor 105 é subtraído do vídeo de entrada de cada CU em um formato determinado pelo controlador de codificação 107 para gerar um imagem de erro de previsão, e a imagem de erro de previsão é entrada ao transformador/quantizador 101.

[0121] O transformador/quantizador 101 transforma por frequência a imagem de erro de previsão para obter um coeficiente de transformação de frequência.

[0122] O transformador/quantizador 101 ainda quantiza o coeficiente de transformação de frequência com uma largura predeterminada de etapa de quantização Qs para obter um valor de quantização de transformação.

[0123] O codificador de entropia 102 codifica por entropia split_coding_unit_flag (ver figura 22) fornecido a partir do controlador de codificação 107, os parâmetros de previsão e o valor de quantização de transformação fornecido a partir do transformador/quantizador 101. Conforme acima mencionado, quando o modo de previsão de um CU a ser criptografado por entropia é interprevisão e o tamanho de CU é inferior ou igual a minInterPredUnitSize, o codificador de entropia 102 na realização exemplar não criptografa por entropia inter_partitioning_idc.

[0124] O transformador inverso/quantizador inverso 103 quantiza de forma inversa o valor de quantização de transformação com a largura predeterminada de etapa de quantização Qs. O transformador inverso/quantizador inverso 103 ainda realiza a transformação de frequência inversa do coeficiente de transformação de frequência obtido pela quantização inversa. O sinal de previsão é adicionado à imagem reconstruída de erro de previsão obtida pela transformação de frequência inversa, e o resultado é fornecido ao buffer 104.

[0125] O multiplexador 106 multiplexa e produz as informações sobre o tamanho mínimo de inter-PU (min_inter_pred_unit_hierarchy_depth) e dados de saída do codificador de entropia 102. De acordo com a sintaxe de conjunto de parâmetro de sequência RBSP 4.1.2 em NPL 2, o multiplexador 106 multiplexa a sintaxe log2_min_coding_unit_size_minus3 e sintaxe min_inter_pred_unit_hierarchy_depth após a sintaxe max_coding_unit_hierarchy_depth em um conjunto de parâmetro de sequência conforme listado na figura 3 (log de 2 bases (logaritmo) de um valor obtido ao dividir minInterPredUnitSize pelo tamanho de SCU, i.e. 0 na realização exemplar). A sintaxe log2_min_coding_unit_size_minus3 e sintaxe max_coding_unit_hierarchy_depth são informações para determinar um tamanho de SCU (minCodingUnitSize) e um tamanho de LCU (maxCodingUnitSize), respectivamente. MinCodingUnitSize e maxCodingUnitSize são respectivamente calculados conforme segue. minCodingUnitSize = 1<< (log2_min_coding_unit_size_minus3 + 3) maxCodingUnitSize = 1<< (log2_min_coding_unit_size_minus3 + 3 + max_coding_unit_hierarchy_depth) A sintaxe min_inter_pred_unit_hierarchy_depth e minCodingUnitSize possuem a seguinte relação. min_inter_pred_unit_hierarchy_depth = log2(minInterPredUnitSize /minCodingUnitSize)

[0126] Com base na operação acima descrita, o dispositivo de codificação de vídeo na realização exemplar gera uma corrente de bit.

[0127] Com referência depois a um fluxograma da figura 4, a descrição é feita de uma operação de escrita da sintaxe do tipo de partição de inter-PU que é um recurso da realização exemplar.

[0128] Conforme mostrado na figura 4, o codificador de entropia 102 codifica por entropia split_coding_unit_flag na etapa S201. O codificador de entropia 102 ainda codifica por entropia o modo de previsão na etapa S202, i.e., o codificador de entropia 102 codifica por entropia a sintaxe pred_mode. Ao determinar na etapa S203 que o modo de previsão de um CU a ser codificado é interprevisão e determinar na etapa S204 que o tamanho de CU é inferior ou igual a minInterPredUnitSize, o controlador de codificação 107 controla o codificador de entropia 102 para omitir a codificação por entropia da sintaxe inter_partitioning_idc. Ao determinar na etapa S203 que o modo de previsão do CU a ser codificado é intraprevisão, ou ao determinar na etapa S204 que o tamanho de CU é superior a minInterPredUnitSize, o controlador de codificação 107 controla o codificador de entropia 102 para criptografar por entropia, na etapa S205, as informações do tipo de partição de PU sobre o CU a ser codificado.

[0129] De acordo com a sintaxe de unidade de previsão 4.1.10 em NPL 2, a sintaxe pred_mode acima mencionada e sintaxe inter_partitioning_idc são sinalizadas conforme representado em uma lista mostrada na figura 5. A realização exemplar retrata que a sintaxe inter_partitioning_idc somente é sinalizada nos cabeçotes de PU de CUs superior em tamanho que minInterPredUnitSize sob a seguinte condição: “se(currPredUnitSize > minInterPredUnitSize).”

[0130] Quando o tamanho de CU do CU a ser codificado é inferior ou igual ao tamanho mínimo de inter-PU predeterminado, o dispositivo de codificação de vídeo na realização exemplar não criptografa por entropia a sintaxe do tipo de partição de inter-PU na camada de cabeçote de PU do CU a ser codificado para reduzir o número de sintaxes do tipo de partição de inter- PU a ser sinalizado. Já que a redução no número de sintaxes do tipo de partição de inter-PU a ser sinalizado reduz a porcentagem da quantidade de código de um cabeçote de PU na corrente de bit, a qualidade do vídeo é ainda melhorada.

[0131] Quando o tamanho de CU do CU a ser codificado excede o tamanho mínimo de inter-PU predeterminado, o dispositivo de codificação de vídeo na realização exemplar define, em um tipo predeterminado de partição de inter-PU, a sintaxe do tipo de partição de inter-PU na camada de cabeçote de PU do CU a ser codificado, e codifica por entropia o tipo de partição de inter-PU de modo que nenhum inter-PU, cujo tamanho seja inferior ao tamanho mínimo de inter-PU, não entrará em existência. A largura de banda de memória é reduzida ao impedir qualquer inter-PU, cujo tamanho seja inferior ao tamanho mínimo de inter-PU, de entrar em existência.

[0132] Um dispositivo de decodificação de vídeo na Realização Exemplar 3 decodifica uma corrente de bit gerada pelo dispositivo de codificação de vídeo na Realização Exemplar 2.

[0133] O dispositivo de decodificação de vídeo nesta realização exemplar inclui: meio para desmultiplexar o tamanho mínimo das informações de inter-PU multiplexadas em uma corrente de bit; meio de determinação de tamanho de CU para determinar um tamanho de CU predeterminado, a partir do qual um tipo de partição de inter-PU é analisado, com base nas informações desmultiplexadas de tamanho mínimo de inter-PU ; e o meio de análise para analisar o tipo de partição de inter- PU a partir da corrente de bit no tamanho de CU determinado pelo meio de determinação de tamanho de CU.

[0134] Conforme mostrado na figura 6, o dispositivo de decodificação de vídeo na realização exemplar inclui um desmultiplexador 201, um decodificador de entropia 202, um transformador inverso/quantizador inverso 203, um previsor 204, um buffer 205 e um controlador de decodificação 206.

[0135] O desmultiplexador 201 desmultiplexa uma corrente de bit de entrada e extrai as informações de tamanho mínimo de inter-PU e uma corrente de bit de vídeo codificada por entropia. O desmultiplexador 201 desmultiplexa a sintaxe log2_min_coding_unit_size_minus3 e sintaxe min_inter_pred_unit_hierarchy_depth após a sintaxe max_coding_unit_hierarchy_depth nos parâmetros de sequência conforme listados na figura 3. O desmultiplexador 201 ainda usa os valores desmultiplexados de sintaxe para determinar um tamanho mínimo de inter-PU (minInterPredUnitSize), em que a sintaxe do tipo de partição de inter-PU (sintaxe inter_partitioning_idc) é transmitida, conforme segue.minInterPredUnitSize = 1<< (log2_min_coding_unit_size_minus3 + 3 + min_inter_pred_unit_hierarchy_depth)

[0136] Em outras palavras, o desmultiplexador 201 na realização exemplar também tem um papel ao determinar o tamanho de CU, em que a sintaxe do tipo de partição de inter-PU é analisada, com base nas informações desmultiplexadas de tamanho mínimo de inter-PU.

[0137] O desmultiplexador 201 ainda fornece o tamanho mínimo de inter-PU ao controlador de decodificação 206.

[0138] O decodificador de entropia 202 decodifica por entropia a corrente de bit de vídeo. O decodificador de entropia 202 fornece um valor de quantização de transformação decodificado por entropia ao transformador inverso/quantizador inverso 203. O decodificador de entropia 202 fornece split_coding_unit_flag decodificado por entropia e parâmetros de previsão ao controlador de decodificação 206.

[0139] Quando o modo de previsão de um CU a ser decodificado é interprevisão e o tamanho de CU é minInterPredUnitSize, o controlador de decodificação 206 na realização exemplar controla o decodificador de entropia 202 para omitir a decodificação por entropia da sintaxe do tipo de partição de inter-PU do CU a ser decodificado. O controlador de decodificação 206 ainda define, para 2Nx2N, o tipo de partição de inter-PU do CU a ser decodificado. Quando o tamanho de CU do CU a ser decodificado é inferior do que minInterPredUnitSize, o modo de previsão do CU é somente intraprevisão.

[0140] O transformador inverso/quantizador inverso 203 quantiza de forma inversa os valores de quantização de transformação da diferença de luminância e cor com uma largura predeterminada de etapa de quantização. O transformador inverso/quantizador inverso 203 ainda realiza a transformação de frequência inversa de um coeficiente de transformação de frequência obtido pela quantização inversa.

[0141] Após a transformação de frequência inversa, o previsor 204 gera um sinal de previsão usando um imagem de uma foto reconstruída armazenada no buffer 205 com base nos parâmetros de previsão fornecidos a partir do controlador de decodificação 206.

[0142] O sinal de previsão fornecido a partir do previsor 204 é adicionado a uma imagem reconstruída de erro de previsão obtida pela transformação de frequência inversa realizada pelo transformador inverso/quantizador inverso 203, e o resultado é fornecido ao buffer 205 como uma foto reconstruída.

[0143] A foto reconstruída armazenada no buffer 205 em então produzida como uma imagem decodificada.

[0144] Com base na operação acima descrita, o dispositivo de decodificação de vídeo na realização exemplar gera uma imagem decodificada.

[0145] Com referência depois a um fluxograma da figura 7, a descrição é feita de uma operação de analisar a sintaxe do tipo de partição de inter-PU que é um recurso da realização exemplar.

[0146] Conforme mostrado na figura 7, o decodificador de entropia 202 decodifica por entropia split_coding_unit_flag para decidir o tamanho de CU na etapa S301. Na etapa S302, o decodificador de entropia 202 decodifica por entropia o modo de previsão. Em outras palavras, o decodificador de entropia 202 decodifica por entropia pred_mode sintaxe. Ao determinar na etapa S303 que o modo de previsão é interprevisão e determinar na etapa S304 que o tamanho de CU decidido é menor do que ou igual a minInterPredUnitSize, o controlador de decodificação 206 controla o decodificador de entropia 202 na etapa S305 para omitir a decodificação por entropia do tipo de partição de inter-PU e definir o tipo de partição de PU do CU para 2Nx2N (inter_partitioning_idc = 0).

[0147] Ao determinar na etapa S303 que o modo de previsão é intraprevisão, ou ao determinar na etapa S304 que o tamanho de CU decidido é superior do que minInterPredUnitSize, o controlador de decodificação 206 controla o decodificador de entropia 202 na etapa S306 para não omitir a decodificação por entropia do tipo de partição de PU do CU a ser decodificado e definir o tipo de partição de PU do CU a um tipo de partição de PU obtido como um resultado da decodificação por entropia.

[0148] O dispositivo de codificação de vídeo na Realização Exemplar 1 e Realização Exemplar 2 pode multiplexar as informações de tamanho mínimo de inter-PU (min_inter_pred_unit_hierarchy_depth) usadas na Realização Exemplar 1 em um conjunto de parâmetro de foto ou um cabeçote dividido conforme representado em uma lista mostrada na figura 8 ou uma lista mostrada na figura 9. De forma semelhante, o dispositivo de decodificação de vídeo nesta realização exemplar pode desmultiplexar a sintaxe min_inter_pred_unit_hierarchy_depth a partir do conjunto de parâmetro de foto ou cabeçote dividido.

[0149] O dispositivo de codificação de vídeo na Realização Exemplar 1 e Realização Exemplar 2 pode definir a sintaxe min_inter_pred_unit_hierarchy_depth como log de 2 bases (logaritmo) de um valor obtido ao dividir o tamanho de LCU (maxCodingUnitSize) pelo tamanho mínimo de inter-PU (minInterPredUnitSize), i.e., a seguinte equação pode ser usada. min_inter_pred_unit_hierarchy_depth = log2(maxCodingUnitSize /minInterPredUnitSize)

[0150] Neste caso, o dispositivo de decodificação de vídeo nesta realização exemplar pode calcular o tamanho mínimo de inter-PU com base na sintaxe min_inter_pred_unit_hierarchy_depth conforme segue.minInterPredUnitSize = 1<< (log2_min_coding_unit_size_minus3 + 3 + max_coding_unit_hierarchy_depth - min_inter_pred_unit_hierarchy_depth)

[0151] No dispositivo de decodificação de vídeo nesta realização exemplar, já que nenhum inter-PU, cujo tamanho seja inferior ao tamanho mínimo de inter-PU, entra em existência, a largura de banda de memória é reduzida.

[0152] Um dispositivo de decodificação de vídeo na Realização Exemplar 4 decodifica uma corrente de bit gerada pelo dispositivo de codificação de vídeo na Realização Exemplar 1.

[0153] O dispositivo de decodificação de vídeo nesta realização exemplar inclui: meio para desmultiplexar as informações de tamanho mínimo de inter-PU multiplexadas em uma corrente de bit; e meio de detecção de erro para detectar, com base nas informações desmultiplexadas de tamanho mínimo de inter-PU, um erro em uma unidade de acesso acessando a corrente de bit incluindo um CU a ser decodificado. Conforme definido na unidade de acesso 3.1 de NPL 1, a unidade de acesso é a unidade de armazenar os dados codificados para uma foto. O erro significa violação das restrições com base no número de vetores de movimento permitido por área predeterminada.

[0154] Conforme mostrado na figura 10, o dispositivo de decodificação de vídeo na realização exemplar inclui um desmultiplexador 201, um decodificador de entropia 202, um transformador inverso/quantizador inverso 203, um previsor 204, um buffer 205 e um detector de erro 207.

[0155] O desmultiplexador 201 opera da mesma forma que o desmultiplexador 201 na Realização Exemplar 3 para desmultiplexar uma corrente de bit de entrada e extrair as informações de tamanho mínimo de inter-PU e uma corrente de bit de vídeo codificada por entropia. O desmultiplexador 201 ainda determina o tamanho mínimo de inter-PU e fornece o tamanho mínimo de inter-PU ao detector de erro 207.

[0156] O decodificador de entropia 202 decodifica por entropia a corrente de bit de vídeo. O decodificador de entropia 202 fornece um valor de quantização de transformação decodificado por entropia ao transformador inverso/quantizador inverso 203. O decodificador de entropia 202 então fornece split_coding_unit_flag decodificado por entropia e parâmetros de previsão ao detector de erro 207.

[0157] O detector de erro 207 realiza a detecção de erro sobre os parâmetros de previsão fornecidos a partir do decodificador de entropia 202 com base no tamanho mínimo de inter-PU fornecido a partir do desmultiplexador 201, e fornece o resultado ao previsor 204. A operação de detecção de erro será abaixo descrita. O detector de erro 207 também tem um papel como o controlador de decodificação 206 na Realização Exemplar 3.

[0158] O transformador inverso/quantizador inverso 203 opera da mesma forma que o transformador inverso/quantizador inverso 203 na Realização Exemplar 3.

[0159] O previsor 204 gera um sinal de previsão usando uma imagem de uma foto reconstruída armazenada no buffer 205 com base nos parâmetros de previsão fornecidos a partir do detector de erro 207.

[0160] O buffer 205 opera da mesma forma que o buffer 205 na Realização Exemplar 3.

[0161] Com base na operação acima descrita, o dispositivo de decodificação de vídeo na realização exemplar gera uma imagem decodificada.

[0162] Com referência a um fluxograma da figura 11, a descrição é feita da operação de detecção de erro do dispositivo de decodificação de vídeo na realização exemplar para detectar um erro em uma unidade de acesso acessando uma corrente de bit incluindo um CU a ser decodificado.

[0163] Na etapa S401, o detector de erro 207 decide o tamanho de CU, o modo de previsão e o tipo de partição de PU.

[0164] Na etapa S402, o detector de erro 207 determina o modo de previsão de um PU do CU a ser decodificado. Quando o modo de previsão é intraprevisão, o processo é terminado. Quando o modo de previsão é interprevisão, o procedimento prossegue para a etapa S403.

[0165] Na etapa S403, o detector de erro 207 compara o tamanho de PU do CU a ser decodificado com o tamanho mínimo de inter-PU. Quando o tamanho de PU do CU a ser decodificado é superior ou igual ao tamanho mínimo de inter-PU, o processo é terminado. Quando o tamanho de PU do CU a ser decodificado é inferior ao tamanho mínimo de inter-PU, o procedimento prossegue para a etapa S404.

[0166] Na etapa S404, o detector de erro 207 determina que existe um erro e notifica a parte externa do erro. Por exemplo, o detector de erro 207 produz o endereço do CU a ser decodificado e em que o erro ocorreu.

[0167] De acordo com a operação acima, o detector de erro 207 detecta o erro em uma unidade de acesso acessando a corrente de bit incluindo o CU a ser decodificado.

[0168] Cada uma das realizações exemplares acima mencionadas pode ser implantada em hardware ou em um programa de computador.

[0169] Um sistema de processamento de informações mostrado na figura 12 inclui um processador 1001, uma memória de programa 1002, uma mídia de armazenamento 1003 para armazenar dados de vídeo e uma mídia de armazenamento 1004 para armazenar uma corrente de bit. A mídia de armazenamento 1003 e a mídia de armazenamento 1004 podem ser mídias de armazenamento diferentes, ou áreas de armazenamento na mesma mídia de armazenamento. Uma mídia magnética, tal como, um disco rígido, pode ser usada como a mídia de armazenamento.

[0170] No sistema de processamento de informações mostrado na figura 12, um programa para realizar a função de cada bloco (exceto o bloco de buffer) mostrado em cada figura 1, figura 6 e figura 10 é armazenado na memória de programa 1002. O processador 1001 realiza o processamento de acordo com o programa armazenado na memória de programa 1002 para realizar as funções do dispositivo de codificação de vídeo ou dispositivo de decodificação de vídeo mostrado na figura 1, figura 6 ou figura 10, respectivamente.

[0171] A figura 13 é um diagrama de bloco mostrando uma parte principal de um dispositivo de codificação de vídeo de acordo com a presente invenção. Conforme mostrado na figura 13, o dispositivo de decodificação de vídeo de acordo com a presente invenção é um dispositivo de codificação de vídeo para codificação de vídeo usando interprevisão, incluindo o meio de controle de codificação 11 (o controlador de codificação 107 mostrado na figura 1 como um exemplo) para ajustar valores capazes de uma partição de inter-PUde um CU a ser codificado, com base em um tamanho mínimo de inter-PU predeterminado (PA) e um tamanho de CU (PB) do CU a ser codificado.

[0172] A figura 14 é um diagrama de bloco mostrando uma parte principal de um dispositivo de decodificação de vídeo de acordo com a presente invenção. Conforme mostrado na figura 14, o dispositivo de decodificação de vídeo de acordo com a presente invenção é um dispositivo de decodificação de vídeo para decodificação de vídeo usando interprevisão, incluindo o meio de controle de decodificação 21 (o controlador de decodificação 207 mostrado na figura 6 e figura 10 como um exemplo) para ajustar valores capazes de uma partição de inter- PU de um CU a ser decodificado, com base em um tamanho mínimo de inter-PU predeterminado (PA) e um tamanho (PB) do CU a ser decodificado.

[0173] Enquanto a presente invenção foi descrita com referência às realizações exemplares e exemplos, a presente invenção não é limitada às realizações exemplares e exemplos acima mencionados. Diversas alterações passíveis de entendimento por aqueles com habilidade na técnica dentro do escopo da presente invenção podem ser feitas às estruturas e detalhes da presente invenção.

[0174] Este pedido reivindica prioridade com base no Pedido de Patente Japonês N° 2011-4964, depositado em 13 de janeiro de 2011, cujas revelações são aqui incorporadas em sua totalidade. Lista de Sinais de Referência 11 meio de controle de codificação 21 meio de controle de decodificação 101 transformador/quantizador 102 codificador de entropia 103 transformador inverso/quantizador inverso 104 buffer 105 previsor 106 multiplexador 107, 108 controlador de codificação 201 desmultiplexador 202 decodificador de entropia 203 transformador inverso/quantizador inverso 204 previsor 205 buffer 206 controlador de decodificação 207 detector de erro 1001 processador 1002 memória de programa 1003 mídia de armazenamento 1004 mídia de armazenamento

Claims (4)

1. Dispositivo de codificação de vídeo, para codificação de vídeo usando interprevisão, caracterizado pelo fato de compreender: - meio de controle de codificação (11, 107) para ajustar valores capazes de uma partição de inter-PU de um CU a ser codificado, com base em uma relação entre um tamanho mínimo de inter-PU e um tamanho do CU a ser codificado.

2. Dispositivo de decodificação de vídeo, para decodificação de vídeo usando interprevisão, caracterizado pelo fato de compreender: - meio de controle de decodificação (21, 206) para ajustar valores capazes de uma partição de inter-PU de um CU a ser decodificado, com base em uma relação entre um tamanho mínimo de inter-PU e um tamanho do CU a ser decodificado.

3. Método de codificação de vídeo, para codificação de vídeo usando interprevisão, caracterizado pelo fato de compreender: - ajustar valores capazes de uma partição de inter-PU de um CU a ser codificado, com base em uma relação entre um tamanho mínimo de inter-PU e um tamanho do CU a ser codificado.

4. Método de decodificação de vídeo, para decodificação de vídeo usando interprevisão, caracterizado pelo fato de compreender: - ajustar valores capazes de uma partição de inter-PU de um CU a ser decodificado, com base em uma relação entre um tamanho mínimo de inter-PU e um tamanho do CU a ser decodificado.

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011-004964 | 2011-01-13 | ||

| JP2011004964 | 2011-01-13 | ||

| PCT/JP2012/000046 WO2012096147A1 (ja) | 2011-01-13 | 2012-01-05 | 映像符号化装置、映像復号装置、映像符号化方法、映像復号方法及びプログラム |

| BR112013017799-3A BR112013017799B1 (pt) | 2011-01-13 | 2012-01-05 | Dispositivo de decodificação de vídeo e método de decodificação de vídeo |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| BR122015017257A2 BR122015017257A2 (pt) | 2019-08-27 |

| BR122015017257B1 true BR122015017257B1 (pt) | 2022-08-02 |

Family

ID=46507056

Family Applications (5)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| BR122015024083-2A BR122015024083B1 (pt) | 2011-01-13 | 2012-01-05 | Dispositivo de decodificação de vídeo e método de decodificação de vídeo |

| BR112013017799-3A BR112013017799B1 (pt) | 2011-01-13 | 2012-01-05 | Dispositivo de decodificação de vídeo e método de decodificação de vídeo |

| BR122020018528-7A BR122020018528B1 (pt) | 2011-01-13 | 2012-01-05 | Dispositivo de decodificação de vídeo e método de decodificação de vídeo |

| BR122020018527-9A BR122020018527B1 (pt) | 2011-01-13 | 2012-01-05 | Dispositivo de criptografia de vídeo, dispositivo de decodificação de vídeo, método de criptografia de vídeo e método de decodificação de vídeo. |

| BR122015017257-8A BR122015017257B1 (pt) | 2011-01-13 | 2012-01-05 | Dispositivo de codificação de vídeo, dispositivo de decodificação de vídeo, método de codificação de vídeo e método de decodificação de vídeo |

Family Applications Before (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| BR122015024083-2A BR122015024083B1 (pt) | 2011-01-13 | 2012-01-05 | Dispositivo de decodificação de vídeo e método de decodificação de vídeo |

| BR112013017799-3A BR112013017799B1 (pt) | 2011-01-13 | 2012-01-05 | Dispositivo de decodificação de vídeo e método de decodificação de vídeo |

| BR122020018528-7A BR122020018528B1 (pt) | 2011-01-13 | 2012-01-05 | Dispositivo de decodificação de vídeo e método de decodificação de vídeo |

| BR122020018527-9A BR122020018527B1 (pt) | 2011-01-13 | 2012-01-05 | Dispositivo de criptografia de vídeo, dispositivo de decodificação de vídeo, método de criptografia de vídeo e método de decodificação de vídeo. |

Country Status (10)

| Country | Link |

|---|---|

| US (6) | US10841590B2 (pt) |

| EP (4) | EP3860125A1 (pt) |

| JP (5) | JP5673693B2 (pt) |

| KR (5) | KR101829515B1 (pt) |

| CN (5) | CN107105260B (pt) |

| BR (5) | BR122015024083B1 (pt) |

| ES (3) | ES2882882T3 (pt) |

| HK (3) | HK1208978A1 (pt) |

| PL (3) | PL3833026T3 (pt) |

| WO (1) | WO2012096147A1 (pt) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9762899B2 (en) * | 2011-10-04 | 2017-09-12 | Texas Instruments Incorporated | Virtual memory access bandwidth verification (VMBV) in video coding |

| GB2505169B (en) * | 2012-08-13 | 2016-03-16 | Gurulogic Microsystems Oy | decoder and method |