BR112016022266B1 - Método para controlar dinamicamente um domínio de potência em um dispositivo de computação portátil, domínio de potência disposto em um dispositivo de computação portátil e memória legível por computador - Google Patents

Método para controlar dinamicamente um domínio de potência em um dispositivo de computação portátil, domínio de potência disposto em um dispositivo de computação portátil e memória legível por computador Download PDFInfo

- Publication number

- BR112016022266B1 BR112016022266B1 BR112016022266-0A BR112016022266A BR112016022266B1 BR 112016022266 B1 BR112016022266 B1 BR 112016022266B1 BR 112016022266 A BR112016022266 A BR 112016022266A BR 112016022266 B1 BR112016022266 B1 BR 112016022266B1

- Authority

- BR

- Brazil

- Prior art keywords

- power domain

- power

- processing resources

- processing

- information

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/3296—Power saving characterised by the action undertaken by lowering the supply or operating voltage

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3206—Monitoring of events, devices or parameters that trigger a change in power modality

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/324—Power saving characterised by the action undertaken by lowering clock frequency

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/329—Power saving characterised by the action undertaken by task scheduling

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04W—WIRELESS COMMUNICATION NETWORKS

- H04W52/00—Power management, e.g. TPC [Transmission Power Control], power saving or power classes

- H04W52/02—Power saving arrangements

- H04W52/0209—Power saving arrangements in terminal devices

- H04W52/0251—Power saving arrangements in terminal devices using monitoring of local events, e.g. events related to user activity

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D30/00—Reducing energy consumption in communication networks

- Y02D30/70—Reducing energy consumption in communication networks in wireless communication networks

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Power Sources (AREA)

Abstract

APARELHO, SISTEMA E MÉTODO PARA GERENCIAMENTO DE POTÊNCIA DINÂMICA ATRAVÉS DE PROCESSADORES HETEROGÊNEOS EM UM DOMÍNIO DE POTÊNCIA COMPARTILHADO. Sistemas e métodos para ajustar dinamicamente um parâmetro de entrada para um domínio de potência em um dispositivo de computação portátil são divulgados. O domínio de potência inclui dois ou mais recursos de processamento que compartilham uma fonte de energia. Uso dinâmico dos dois ou mais recursos de processamento cria uma oportunidade para ajustar o parâmetro de entrada quando uma mudança de estado associada com um recurso de processamento no domínio de potência ocorre. Um controlador no domínio de potência inclui a lógica, que responde a um indicador de status associado a uma respectiva fonte de processamento no domínio de potência gerando um sinal de controle que dirige um dispositivo para ajustar uma ou ambas de tensão de entrada e frequência de relógio.

Description

[0001] O presente pedido reivindica prioridade e benefício da data do depósito do Pedido Provisório US No. 61/970.290, intitulado "Apparatus, System and Method for Dynamic Power Management Across Heterogeneous Processors in a Shared Power Domain" (Documento de Procuração No. 141870P1) depositado em 25 de Março de 2014, cuja totalidade é incorporada neste documento para referência.

[0002] Dispositivos de computação são onipresentes. Alguns dispositivos de computação são portáteis, tais como smartphones, tablets e computadores portáteis. Além da função principal destes dispositivos, muitos incluem elementos que suportam as funções periféricas. Por exemplo, um telefone celular pode incluir a função principal de permitir e suportar chamadas de telefonia celular e as funções periféricas de uma câmera fotográfica, uma câmera de vídeo, um leitor de música, navegação com sistema de posicionamento global (GPS), navegação de web, enviar e receber e-mails, enviar e receber mensagens de texto, capacidades de aperte para falar, etc.

[0003] Alguns modelos convencionais para dispositivos de computação portáteis de mão incluem múltiplos processadores e/ou processadores com múltiplos núcleos para suportar as várias funções primárias e periféricas desejadas para um dispositivo de computação particular. Tais projetos, muitas vezes integram ainda mais circuitos analógicos, digitais e de radiofrequência ou funções em um único substrato e são comumente referidos como um sistema em um chip (SoC). Estes diferentes circuitos e funções, muitas vezes, requerem diferentes frequências de operação e níveis de tensão e são, por vezes, segregados em função das exigências de entrada comuns. Quando essa segregação é baseada na tensão de entrada dos circuitos diferentes podem compartilhar uma fonte de potência comum.

[0004] O desejo de conservar a energia armazenada em uma bateria que provê potência a dispositivos portáteis levou à implementação de técnicas de gerenciamento de potência dinâmico. Essas técnicas incluem o ajuste da frequência de relógio, a tensão de entrada, ou ambos, para alcançar um desempenho de circuito desejado.

[0005] A tecnologia convencional de redução de potência de múltiplos núcleos aplicada em um projeto SoC dimensiona a tensão de entrada como uma função do desempenho de circuito medido para compensar a variação do processo de fabricação de semicondutor para atingir um desempenho alvo desejado. Quando os vários núcleos ou blocos funcionais em um único domínio de potência têm diferentes respostas para a mesma tensão de entrada, o núcleo ou bloco funcional que responde a mais lenta determinação da tensão de entrada que é necessária. Por conseguinte, a tensão de entrada necessária para alcançar o desempenho desejado é aplicada ao domínio de potência.

[0006] A figura 1 inclui um esquema 10 de tensão e frequência como aplicadas a um circuito de teste integrado em semicondutores separados. A tensão de entrada é mostrada ao longo do eixo horizontal, enquanto a resposta de frequência do circuito de teste é mostrada ao longo do eixo vertical. A capacidade de resposta de um circuito de teste em uma primeira matriz de semicondutor é representada pela linha 12, enquanto que a capacidade de resposta de um respectivo circuito de teste na segunda matriz de semicondutor é mostrada pela linha 14. O primeiro circuito de teste na primeira matriz de semicondutor responde em menos tempo e em uma tensão de entrada inferior a um circuito de teste idêntico na segunda matriz de semicondutor. Como mostrado no esquema, quando uma tensão de referência VREF é aplicada, o silício rápido pode alcançar uma frequência (por exemplo, F1_ medido) que excede uma frequência alvo, f_target. Como ainda mostrado no esquema, uma tensão de alimentação VREF - Vi aplicada ao circuito de teste da primeira matriz de semicondutor permite que o circuito de teste alcance a frequência operacional alvo. Por outro lado, quando VREF é aplicada à segunda matriz de semicondutor, o circuito de teste alcança uma frequência f2_measured que é inferior à frequência alvo. Uma tensão de alimentação VREF + V2 deve ser aplicada à segunda matriz de semicondutor para permitir que o circuito de teste alcance a frequência alvo. Sob estas circunstâncias, a primeira matriz de semicondutor é muitas vezes referida como tendo silício "rápido", enquanto que a segunda matriz de semicondutor é descrita como tendo silício "lento". Tal como adicionalmente ilustrado na figura 1, a variação entre a respectiva capacidade de resposta das primeira e segunda matrizes de semicondutor mostra que, a fim de conseguir uma frequência desejada ou alvo através de ambas as matrizes, a tensão de entrada necessária para o silício lento alcançar a frequência alvo é necessária. Assim, o silício rápido irá ser operado com uma tensão de margem que é o equivalente da soma de V1 e V2.

[0007] A potência de comutação dissipada por um semicondutor usando portas CMOS estáticas é CxV2xf, onde C é a capacitância de ser comutada por ciclo de relógio, V é a tensão de alimentação e f é a frequência de comutação, então esta parte do consumo de potência diminui de forma quadrática com as mudanças na tensão de alimentação. A fórmula não é exata, no entanto, como muitos processadores de sinal digital (DSPs) modernos e múltiplos processadores de núcleo não são implementados apenas com CMOS, mas também usam circuitos de memória especiais, de lógica dinâmica tal como a lógica domino, etc. Além disso, há também uma corrente de fuga estática, que se tornou cada vez mais acentuada conforme tamanhos dos recursos dos dispositivos semicondutores tornam-se menores e níveis de limite diminuem.

[0008] Em consequência, a escala de tensão dinâmica é amplamente utilizada em estratégias para gerenciamento de comutação de consumo de potência em dispositivos alimentados por bateria. Modos de baixa tensão são utilizados em conjunto com frequências de relógio reduzidas para minimizar o consumo de potência associado com componentes tais como múltiplos processadores de núcleo e DSPs. Quando um desempenho desejado exige potência computacional significativa, a tensão e frequência são aumentadas.

[0009] No entanto, estas técnicas convencionais são não responsivas ao uso de dispositivos de computação portáteis elas afetam os múltiplos núcleos ou blocos funcionais distintos dentro de um domínio de potência. Em um domínio de potência, cada recurso de processamento compartilha uma fonte de potência comum.

[0010] Por exemplo, no caso de um smartphone portátil, na maioria do tempo em que o dispositivo está ligado, muitas das unidades funcionais e núcleos de processamento estarão em um estado de baixo consumo de potência, ou podem mesmo ser desligados, enquanto núcleos de processamento selecionados ou circuitos funcionais selecionados são ligados e utilizados em um domínio de potência compartilhado. Durante alguns casos de uso, alguns núcleos ou circuitos funcionais serão ligados e usados e depois de um tempo podem não ser mais necessários e são desligados ou retornam a um estado de baixa potência.

[0011] A figura 2 ilustra um domínio de potência convencional 20, onde relógio compartilhado e tensões de entrada são distribuídos a vários recursos de processamento ou núcleos. Como mostrado, um barramento 18 provê um sinal periódico a uma respectiva entrada de relógio para núcleos de processamento 22-28. Um controlador de redução de potência de núcleo (ou controlador de RCP) 15 recebe uma primeira tensão de uma fonte de alimentação e, em resposta a um sinal de controle a partir de um ou mais sensores, provê uma tensão ajustada no barramento 16. A tensão ajustada é distribuída para cada um dos comutadores 21 - 27 dispostos para controladamente prover a tensão ajustada aos respectivos núcleos de processamento 22-28. Tal como indicado mais adiante na figura 2, o núcleo 22 requer uma tensão de entrada de VREF + V2 para alcançar a capacidade de resposta desejada correspondente ao f_target. Em contraste, o núcleo 24 requer uma tensão de entrada de VREF + V2 - X para alcançar a resposta desejada para o domínio de potência. Considerando que, o núcleo 26 e o núcleo 28 necessitam de uma tensão de entrada de VREF + V2 - 2X para alcançar a resposta desejada.

[0012] Em um dado instante, o dispositivo de computação portátil pode precisar dos recursos de computação de cada um dos núcleos a uma frequência de relógio desejada. Como mostrado na figura 1, a técnica de gerenciamento de potência convencional da figura 2 irá aplicar uma tensão de entrada VIN = (VREF + V2) de modo que cada núcleo no domínio de potência pode suportar a frequência alvo desejada. Em um momento mais tarde, o dispositivo de computação portátil pode não precisar dos recursos de computação de cada um dos núcleos. No entanto, o projeto de distribuição de potência convencional para um domínio de potência continua a aplicar uma maior tensão de entrada do que o exigido para estes núcleos mais rápidos. Esta tensão de entrada mais elevada é aplicada mesmo quando um ou mais núcleos estão em um modo de espera ou de baixa potência.

[0013] Assim, há uma necessidade de melhores mecanismos para a conservação de potência dentro de um domínio de potência.

[0014] Sistemas e métodos para ajustar dinamicamente uma entrada para um domínio de potência em um dispositivo de computação portátil são divulgados. O domínio de potência inclui dois ou mais recursos de processamento que compartilham uma fonte de potência. Uso dinâmico dos dois ou mais recursos de processamento cria uma oportunidade para ajustar a entrada quando uma mudança de estado associada com um recurso de processamento no domínio de potência ocorre. Um controlador no domínio de potência inclui lógica que responde a um indicador de status associado a uma respectiva fonte de processamento no domínio de potência. A lógica do controlador gera um sinal que direciona um dispositivo para ajustar uma ou ambas de uma tensão de entrada e uma frequência de relógio.

[0015] Uma modalidade exemplar inclui um dispositivo de computação portátil com um domínio de potência. O domínio de potência inclui recursos de processamento que recebem potência de entrada a partir de uma fonte de alimentação compartilhada. Um controlador, acoplado a pelo menos dois recursos de processamento, é configurado para receber informações de um gerenciador de potência. O controlador utiliza a lógica de estado de recurso para gerar um primeiro sinal de controle utilizado por uma fonte de alimentação para prover uma tensão de entrada desejada para o domínio de potência.

[0016] Uma modalidade exemplar inclui um dispositivo de computação portátil com um controlador de domínio de potência acoplado a recursos de processamento. O controlador de domínio de potência recebe informações de um protocolo de sinal de cadeia de sensor modificado. Os sensores na cadeia incorporam informação sobre o estado operacional de uma respectiva região de circuito ou bloco funcional. A informação inclui um ou ambos de um estado de potência e uma frequência de relógio. O controlador recebe a informação e responde em conformidade. Por exemplo, o controlador de domínio de potência pode mascarar ou ignorar informações de sensor provenientes de um recurso de processamento de seleção que está em um estado desligado. Em outro exemplo, o controlador de domínio de potência pode desligar o sensor ou ignorar o sensor quando o respectivo recurso de processamento está em um estado desligado.

[0017] Em ainda outra modalidade exemplar, o controlador inclui uma lógica de afinidade que identifica uma preferência para um ou mais recursos de processamento dentro do domínio de potência sob certas condições. O controlador gera um segundo sinal de controle que comunica esta informação para um programador que atribui tarefas aos recursos de processamento identificados. O programador pode ser usado para gerenciar blocos funcionais heterogêneos entre domínios distintos de potência e para os casos de uso que exigem a coordenação entre os recursos de processamento localizados em domínios de potência separados.

[0018] Um outro exemplo de modalidade é um método para dinamicamente controlar um domínio de potência em um dispositivo de computação portátil. O domínio de potência inclui recursos de processamento que compartilham uma fonte de potência. O método inclui as etapas de identificação de uma condição atual de pelo menos dois recursos de processamento de um domínio de potência em um dispositivo de computação portátil, em resposta a uma mudança na condição atual, iniciar um ajuste de uma entrada e aplicação da entrada ao domínio de potência.

[0019] Nos desenhos, números de referência iguais se referem a partes iguais ao longo das várias vistas, a menos que indicado de outra forma. Para números de referência com designações de caracteres de letra como "102A" ou "102B", as designações de caracteres de letra podem diferenciar duas partes iguais ou elementos presentes na mesma figura. As denominações de caracteres de letra para os numerais de referência podem ser omitidas quando pretende-se que um número de referência cubra todas as partes tendo o mesmo número de referência em todas as figuras.

[0020] A figura 1 é um esquema de potencial elétrico e frequência, tal como aplicado a um circuito de teste integrado em semicondutores separados.

[0021] A figura 2 é um diagrama esquemático que ilustra um exemplo de modalidade de uma técnica convencional de redução de potência de um domínio de potência, incluindo quatro processadores centrais.

[0022] A figura 3 é um diagrama esquemático que ilustra um exemplo de dispositivo de computação portátil.

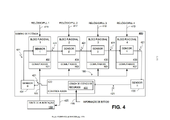

[0023] A figura 4 é um diagrama esquemático que ilustra uma modalidade de um domínio de potência modificado com lógica de estado de recurso.

[0024] A figura 5 é um diagrama esquemático de uma modalidade alternativa de um domínio de potência modificado.

[0025] A figura 6 é um diagrama esquemático de uma modalidade de um domínio de potência modificado acoplado a um programador.

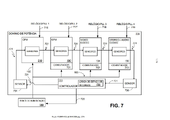

[0026] A figura 7 é um diagrama esquemático de um outro exemplo de modalidade de um domínio de potência modificado.

[0027] A figura 8 é um fluxograma que ilustra um exemplo de modalidade de um método para dinamicamente controlar uma entrada para um domínio de potência em um dispositivo de computação portátil.

[0028] A palavra "exemplar" é aqui utilizada para significar "servir como um exemplo, caso ou ilustração". Qualquer aspecto aqui descrito como "exemplar" não deve necessariamente ser interpretado como preferido ou vantajoso em relação a outros aspectos.

[0029] Nesta descrição, o termo "aplicação" também pode incluir arquivos com conteúdo executável, tais como: código de objeto, scripts, código de bytes, arquivos de linguagem de marcação, e patches. Além disso, uma "aplicação" aqui referida, pode também incluir arquivos que não são executáveis na natureza, tais como documentos que podem precisar de ser abertos ou outros arquivos de dados que precisam ser acessados.

[0030] O termo "conteúdo" pode também incluir arquivos tendo conteúdo executável, tais como: código de objeto, scripts, código de bytes, arquivos de linguagem de marcação, e patches. Além disso, "conteúdo" aqui referido, pode também incluir arquivos que não são executáveis na natureza, tais como documentos que podem precisar de ser abertos ou outros arquivos de dados ou valores de dados que precisam ser acessados.

[0031] Como usado nesta descrição, os termos "componentes", "banco de dados", "módulo", "sistema" e semelhantes pretendem referir-se a uma entidade relacionada com o computador, seja de hardware, firmware, uma combinação de hardware e software, software ou software em execução. Por exemplo, um componente pode ser, mas não está limitado a ser, um processo em execução em um processador, um processador, um objeto, um executável, um segmento de execução, um programa, e/ou um computador. A título de ilustração, tanto uma aplicação em execução em um dispositivo de computação quanto o dispositivo de computador podem ser um componente. Um ou mais componentes podem residir dentro de um processo e/ou sequência de execução, e um componente pode ser localizado em um computador e/ou distribuído entre dois ou mais computadores. Além disso, estes componentes podem ser executados a partir de vários meios legíveis por computador tendo várias estruturas de dados armazenadas no mesmo. Os componentes podem se comunicar por meio de processos locais e/ou remotos, tais como, de acordo com um sinal que tem um ou mais pacotes de dados (por exemplo, os dados a partir de um componente que interage com outro componente em um sistema local, sistema distribuído, e/ou através de uma rede tal como a Internet com outros sistemas por meio do sinal).

[0032] Na presente descrição, o termo "dispositivo de computação portátil" ou CPD é utilizado para descrever qualquer dispositivo de operação de uma fonte de potência recarregável de capacidade limitada, tal como uma bateria e/ou um condensador. Embora PCDs com fontes de potência recarregáveis têm sido utilizados há décadas, os avanços tecnológicos em baterias recarregáveis juntamente com o advento da tecnologia sem fio de terceira geração ("3G") e quarta geração ("4G") habilitaram inúmeros PCDs com múltiplas capacidades. Portanto, um PCD pode ser um telefone celular, um telefone satélite, um pager, um PDA, um smartphone, um dispositivo de navegação, um smartbook ou leitor, um reprodutor de mídia, uma combinação dos dispositivos acima mencionados, um computador portátil ou tablet com uma conexão sem fio, entre outros.

[0033] Os sistemas e métodos para ajustar dinamicamente um parâmetro de entrada para um domínio de potência em um dispositivo de computação portátil são divulgados. O domínio de potência inclui dois ou mais recursos de processamento que compartilham uma fonte de potência. Uso dinâmico dos dois ou mais recursos de processamento cria uma oportunidade para ajustar o parâmetro de entrada quando uma mudança de estado associada com um recurso de processamento no domínio de potência ocorre. Um controlador no domínio de potência inclui a lógica que responde a um indicador de status associado a um respectivo recurso de processamento no domínio de potência gerando um sinal de controle que direciona um dispositivo para ajustar uma ou ambas a tensão de entrada e a frequência de relógio.

[0034] Em uma primeira modalidade, o indicador de status é recebido a partir de uma fonte do lado de fora do domínio de potência. O indicador de status indica se um recurso de processamento correspondente é ligado, é desligado, ou está em um estado de baixa potência. Em uma variação desta primeira modalidade, um indicador de condição múltipla inclui informação responsiva à tensão de entrada e uma frequência de relógio comunicada ao domínio de potência. Em ainda outra variação, vários indicadores de condição incluem informação responsiva à tensão de entrada provida ao domínio de potência, bem como uma frequência de relógio provida para cada recurso de processamento separado no domínio de potência.

[0035] Em uma segunda modalidade, um protocolo utilizado para comunicar a informação a partir de uma série de sensores distribuídos em todo o domínio de potência, incluindo sensores integrados em cada um dos recursos de processamento no domínio de potência, é modificado para incluir informações responsivas a um estado de potência do respectivo recurso de processamento. As informações refletem se o recurso de processamento correspondente é ligado, é desligado ou está em um estado de baixo consumo. Além disso, a informação pode incluir ainda uma frequência de relógio que é provida a cada recurso de processamento. Quando um sensor está em um recurso de processamento que está desligado, o protocolo de sinal modificado pode incluir um bit de máscara que instrui o controlador de domínio de potência a ignorar ou mascarar a informação a partir do respectivo sensor. Em uma alternativa do segundo arranjo, os sensores em blocos funcionais inativos ou recursos de processamento, são desligados e desviados dentro da cadeia de sensores.

[0036] Em uma outra modalidade, um domínio de potência inclui um controlador disposto tanto com a lógica de estado de recurso quanto a lógica de sintonia por frequência. O controlador gera um segundo sinal de controle que inclui uma afinidade ou de preferência para um ou mais recursos de processamento, em vez de outros recursos de processamento no domínio de potência. O segundo sinal de controle é comunicado a um programador que usa as informações de afinidade ou preferência para determinar quais recursos de processamento são necessários para atender a demanda atual. O programador pode ser incorporado em circuitos (hardware) ou em software.

[0037] Em modalidades adicionais, vários recursos de processamento díspares ou heterogêneos que recebem potência através de um barramento de potência compartilhado definem um domínio de potência. Quando estas modalidades adicionais incluem um processador de vídeo e um processador de exibição, durante o tempo ocioso um controlador de domínio pode ajustar a tensão de entrada no barramento de potência compartilhado para reduzir a potência dispendida para alcançar um desempenho desejado.

[0038] Embora descritos com referência particular à operação dentro de um PCD, os sistemas de gerenciamento de potência e os métodos descritos são aplicáveis a qualquer sistema de computação com um ou mais domínios de potência separados que incluem circuitos funcionais com características de capacidade de resposta díspares para uma tensão de entrada. Dito de outra forma, os sistemas de gerenciamento de potência e os métodos são aplicáveis a computadores desktop, computadores servidores ou qualquer dispositivo eletrônico com recursos de processamento que são alimentados por uma fonte de alimentação compartilhada que provê uma única tensão de entrada para os recursos de processamento.

[0039] Referência é agora dirigida aos exemplos ilustrados. Referindo-se inicialmente à figura 3, um aspecto exemplar não limitativo de um dispositivo de computação portátil (PCD) é mostrado e é geralmente projetado 100. Como mostrado, o PCD 100 inclui um sistema sobre chip 120, que inclui uma CPU de vários núcleos 210. A CPU de vários núcleos 210 inclui um zero-ésimo núcleo 211, a 1-ésimo ou primeiro núcleo 212, e um N-ésimo núcleo 214. Os núcleos ou recursos de processamento 211-214 são elementos dentro de um domínio de potência melhorado 400.

[0040] O domínio de potência melhorado 400 pode operar de forma autônoma ou pode ser operado sob um esquema de controle ativado por um hipervisor 240. O hipervisor 240 registra informações de status associadas a elementos selecionados do sistema sobre chip 120, tais como, mas não limitados ao processador de sinal digital (DSP) 220 e a unidade de processamento gráfico (GPU) 190 e, em alguns arranjos outros elementos periféricos selecionados em suporte de uma ou mais técnicas de gerenciamento de potência que podem ser aplicadas em tempo real para reduzir o consumo de potência no dispositivo de computação portátil 100. A arquitetura e operação do domínio de potência melhorado 400 são ainda descritos em associação com a descrição de exemplos de modalidades mostradas nas figuras 4-7.

[0041] Tal como ilustrado na figura 3, um controlador de vídeo 128 e um controlador de tela de toque 130 são acoplados à CPU de vários núcleos 210. Por sua vez, display / tela de toque 132, externos ao sistema sobre chip 120, são acoplados ao controlador de exibição 128 e ao controlador de tela de toque 130. Um CODEC de vídeo 134, por exemplo, um codificador de linha alternada de fase (PAL), um codificador couleur a mémoire sequencial (SECAM), ou um codificador do comitê de sistema(s) de televisão nacional (NTSC), é acoplado à CPU de vários núcleos 210. Adicionalmente, um amplificador de vídeo 136 é acoplado ao CODEC de vídeo 134 e o display / tela de toque 132. Além disso, uma porta de vídeo 138 é acoplada ao amplificador de vídeo 136. Como representado na figura 3, um controlador de barramento serial universal (USB) 140 é acoplado à CPU de vários núcleos 210. Também, uma porta USB 142 é acoplada ao controlador USB 140. A memória de sistema 250 e um módulo de identificação de assinante (SIM) 146 podem também ser acoplados à CPU de vários núcleos 210. O hipervisor 240 executa um ou mais algoritmos, de acordo com instruções armazenadas na memória de sistema 250 ou em um elemento de memória não volátil alternativo (não mostrado). Além disso, como mostrado na figura 3, uma câmera digital 148 pode ser acoplada à CPU de vários núcleos 210. Em um aspecto exemplar, a câmera digital 148 é um dispositivo (CCD) de acoplamento de carga ou uma câmera de semicondutor complementar de óxido de metal (CMOS).

[0042] Tal como adicionalmente ilustrado na figura 3, um CODEC de áudio estéreo 150 pode ser acoplado à CPU de vários núcleos 210. Além disso, um amplificador de áudio 152 pode ser acoplado ao CODEC de áudio estéreo 150. Em um aspecto exemplar, um primeiro altofalante estéreo 154 e um segundo altofalante estéreo 156 são acoplados ao amplificador de áudio 152. A figura 3 mostra que um amplificador de microfone 158 pode também ser acoplado ao CODEC de áudio estéreo 150. Além disso, um microfone 116 pode ser acoplado ao amplificador de microfone 158. Em um aspecto particular, um sintonizador de rádio de modulação de frequência (FM) 162 pode ser acoplado ao CODEC de áudio estéreo 150. Além disso, uma antena FM 164 é acoplado ao sintonizador de rádio FM 162. Além disso, uma porta estéreo 166 pode ser acoplada ao CODEC de áudio estéreo 150.

[0043] A figura 3 também indica que um sistema de frequência de rádio (RF) ou transceptor 212 é acoplado à CPU de vários núcleos 210. Um comutador de RF 170 pode ser acoplado ao transceptor de RF 212 e uma antena de RF 172. Como mostrado na figura 3, um teclado 174 é acoplado à CPU de vários núcleos 210. Além disso, um aparelho telefônico mono com um microfone 176 pode ser acoplado à CPU de vários núcleos 210. Além disso, um dispositivo vibrador 178 pode ser acoplado à CPU de vários núcleos 210. A figura 3 mostra ainda que uma fonte de alimentação 180 pode ser acoplada ao sistema sobre chip 120 através do controlador de USB 140. Em um aspecto particular, a fonte de alimentação 180 é uma fonte de alimentação de corrente contínua (CC) que provê potência aos vários componentes do PCD 100 que precisam de potência. Além disso, em um aspecto particular, a fonte de alimentação é uma bateria recarregável CC ou uma fonte de potência CC que é derivada de uma corrente alternada (CA) para o transformador CC que está ligado a uma fonte de potência CA.

[0044] A figura 3 indica ainda que a PCD 100 pode também incluir uma placa de rede 188 que pode ser utilizada para acessar uma rede de dados, por exemplo, uma rede de área local, uma rede de área pessoal, ou qualquer outra rede. A placa de rede 188 pode ser uma placa de rede Bluetooth, uma placa de rede Wi-Fi, uma placa de rede pessoal (PAN), ou qualquer outra placa de rede bem conhecida na técnica. Além disso, a placa de rede 188 pode ser incorporada em um circuito integrado. Isto é, a placa de rede 188 pode ser uma solução completa de um chip, e pode não ser uma placa de rede separada 188.

[0045] Como representado na figura 3, o display / tela de toque 132, a porta de vídeo 138, a porta USB 142, a câmera 148, o primeiro altofalante estéreo 154, o segundo altofalante estéreo 156, o microfone 116, a antena de FM 164, a porta estéreo 166, o comutador de RF 170, a antena de RF 172, o teclado 174, o mono aparelho de ouvido 176, o vibrador 178, e a fonte de alimentação 180 são externos ao sistema no chip 120.

[0046] O "sistema de RF ou transceptor 212, que pode incluir um ou mais modems, pode suportar um ou mais de sistema global para comunicações móveis RF ("GSM"), Acesso Múltiplo por Divisão de Código ("CDMA"), Acesso Múltiplo por Divisão de Código de Banda larga ("W-CDMA"), por Acesso Múltiplo por Divisão de Código em Sincronia com Divisão de Tempo ("TDSCDMA"), evolução a longo prazo ("LTE"), e as variações de LTE, tais como, mas não limitadas a, FDB/LTE, DCP/LTE, e futuros protocolos sem fio. Na modalidade ilustrada, o sistema de RF 212 está integrado com o sistema em chip 120. Em modalidades alternativas, o sistema de RF 212 e o comutador de RF 170 pode ser suportado em um módulo de RF integrado de separado do sistema em chip 120. Em ainda outras modalidades, tanto o sistema de RF 212 quanto o comutador de RF 170 são separados do sistema em chip 120 e um do outro.

[0047] Na modalidade ilustrada, um único exemplo de um processador de vários núcleos 210 é representado. No entanto, deve ser entendido que qualquer número de CPUs com vários núcleos com configuração semelhante pode ser incluído para suportar os vários dispositivos periféricos e funções associadas com o PCD 100. Em alternativa, um processador único ou múltiplos processadores, cada um tendo uma unidade lógica aritmética ou núcleo pode ser implantado em um PCD 100 ou outros dispositivos de computação para suportar os vários dispositivos periféricos e funções associadas com o PCD 100 como pode ser desejado.

[0048] Em um aspecto particular, uma ou mais das etapas de processo aqui descritas podem ser habilitadas através de uma combinação de dados e instruções de processador armazenadas na memória do sistema 250. Estas instruções podem ser executadas pelo CPU de vários núcleos 210, a fim de executar os métodos aqui descritos. Além disso, o processador de vários núcleos 210, o sistema de memória 250, uma EEPROM (não mostrada) ou uma combinação dos mesmos, podem servir como um meio para armazenar uma representação não transitória da lógica de gerenciamento de potência, incluindo a lógica de estado de recurso, a lógica de sintonização de frequência, dados responsivos e parâmetros de configuração para a execução de uma ou mais das etapas de processo aqui descritas.

[0049] A figura 4 é um diagrama esquemático que ilustra um domínio de potência modificado ou melhorado ou domínio de potência 400. O domínio de potência 400 é acoplado a uma fonte de alimentação 180 e vários sinais de relógio. Na modalidade ilustrada, o domínio de potência 400 recebe um respectivo sinal de relógio para cada recurso de processamento. Cada um dos blocos funcionais 402-408 representa separadamente, pelo menos, um recurso de processamento. Uma primeira entrada de sinal de relógio 416 é acoplada a um primeiro bloco funcional 402. Uma segunda entrada de sinal de relógio 417 é acoplada a um segundo bloco funcional 404. Uma terceira entrada de sinal de relógio 418 é acoplada a um terceiro bloco funcional 406. Uma quarta entrada de sinal de relógio 419 é acoplada a um quarto bloco funcional 408. As respectivas entradas de sinal de relógio 416-419 são responsivas para controlar as entradas comunicadas a partir do hipervisor 240 para a respectiva fonte de relógio do loop travado por fase. Em modalidades alternativas, o domínio de potência 400 pode ser provido com dois, três ou mais de quatro blocos funcionais. Entre essas modalidades alternativas uma fonte de sinal de relógio pode ser compartilhada entre os blocos funcionais que respondem de forma semelhante às variações da tensão de entrada.

[0050] Na modalidade ilustrada, o domínio de potência 400 inclui um barramento 185, que provê uma tensão de entrada ajustável para blocos funcionais 402-408 quando um respectivo comutador 401-407 está configurado para transmitir a tensão de entrada para o bloco funcional correspondente. Um controlador 420 provê um sinal de controle através de uma conexão 425 para a fonte de alimentação 180. O sinal de controle é sensível à informação de estado comunicada na conexão 415 a partir de uma fonte externa para o domínio de potência 400. O controlador 420 inclui uma lógica de estado de recurso 422, que está disposta para alterar o sinal de controle de uma maneira que resulta em uma tensão desejada na fonte de alimentação. A lógica de estado de recurso 422 responde de uma maneira desejada e consistente para indicar informações recebidas sobre a conexão 415 executando circuitos lógicos e/ou instruções executáveis que iniciam ou dirigem um ajuste para o sinal de controle. Informações de estado incluem se cada um dos blocos funcionais 402-408 é ligado, desligado ou, em alternativa, quando for ligado, as informações de estado podem incluir adicionalmente se os blocos funcionais 402-408 estão em um estado de alta potência, intermediário, de espera ou de baixa potência. As informações de estado identificam uma condição atual dos recursos de processamento ou blocos funcionais 402-408 operando dentro do domínio de potência 400. Dito de outra forma, a lógica de estado de recurso 422 é responsiva à presença de uma respectiva tensão de alimentação para os recursos de processamento em um domínio de potência. As informações de estado comunicadas na conexão 415 podem ser geradas em um gerenciador de potência de sistema habilitado em um hardware ou software (por exemplo, em um hipervisor 240) no dispositivo de computação portátil 100.

[0051] Em algumas modalidades as informações de estado são um status binário (por exemplo, ligado ou desligado, ou seja, a potência é aplicada ou a potência não é aplicada). Por exemplo, um estado aplicado de potência pode ser comunicado quando um dos comutadores 401-407 está fechado. Seja qual for o estado atual identificado está associado em uma respectiva relação de um-para-um com recursos de processamento, tais como os blocos funcionais 402-408. Quando as informações de estado identificam ainda um estado de alta potência, intermediário espera ou de baixa potência em adição à condição de ligado, esta informação adicional é representada por mais do que um único bit. A tensão ajustada ou desejada é distribuída a cada um dos comutadores 401-407 para controladamente prover a tensão ajustada aos respectivos blocos funcionais 402-408. Utilização dinâmica dos blocos funcionais 402-408 cria uma oportunidade para ajustar um parâmetro de entrada, tais como a tensão de entrada, a frequência de um relógio, ou ambos quando uma mudança de status ou mudança no estado associadas com um bloco funcional (isto é, um recurso de processamento) no domínio de potência 400 ocorrem.

[0052] A informação de estado ou indicador de status é recebida a partir de uma fonte do lado de fora do domínio de potência 400. Em uma variação desta primeira modalidade, um indicador de condição múltipla inclui informação responsiva à tensão de entrada e uma frequência de relógio comunicada ao domínio de potência. Em ainda outra variação, vários indicadores de condição incluem informação responsiva à tensão de entrada provida ao domínio de potência 400, bem como uma frequência de relógio provida para cada recurso de processamento separado no domínio de potência 400.

[0053] O domínio de potência 400 é ainda organizado com um conjunto de sensores dispostos com circuitos de teste configurados para determinar a capacidade de resposta dos circuitos proximais para cada um dos respectivos sensores. Tal como ilustrado, o conjunto de sensores são acoplados em série um com o outro em um barramento de sensor 421 que se inicia e termina no controlador 420. Sensor 431 está localizado ao longo do barramento 421 em uma região de circuito entre o controlador 420 e o bloco funcional 402. De modo semelhante, sensor 436 está localizado ao longo do barramento 421 em uma região de circuito entre o bloco funcional 408 e o controlador 420. Os sensores localizados ao longo do barramento 421 estão dispostos para prover um indicador ou índice com os dados de capacidade de resposta. O indicador ou índice define uma região de circuito correspondente ou blocos funcionais no domínio de potência 400. As informações de resposta providas a partir das várias regiões de circuito fora dos blocos funcionais ou dentro dos blocos funcionais correspondentes 402-408 podem ser usadas pela lógica de estado de recurso ou outros circuitos de lógica no controlador 420 para ajustar o sinal de controle de conexão 425. Em algumas modalidades, a informação de resposta provida pode ser uma medida da capacidade de resposta relativa de uma primeira região de circuito ou blocos funcional para uma segunda região de circuito ou um segundo bloco funcional.

[0054] A figura 5 é um diagrama esquemático de uma modalidade alternativa de um domínio de potência modificado 500. O domínio de potência modificado 500 difere do domínio de potência 400 em que o domínio de potência 500 não está preparado para receber informações de estado a partir de uma fonte externa. Em vez de receber informações de estado a partir de uma fonte externa, como um aplicativo de gerenciamento de potência ou hipervisor 240, o domínio de potência modificado 500 recebe informações de estado e informações adicionais a partir de um protocolo de sinal de cadeia de sensor modificado. Os sensores na cadeia 521 incorporam informações sobre o estado operacional do respectivo bloco funcional ou, no caso de sensor 531 ou sensor 536 em uma região de circuito sem estar em um bloco funcional 402-408, mas ainda no domínio de potência 500. A informação inclui um ou ambos de um estado de potência e uma frequência de relógio. Neste exemplo, o controlador 520 recebe as informações de estado e de frequências de relógio e responde em conformidade ajustando o sinal de controle sobre a conexão 525 de uma maneira desejada para alcançar uma tensão de entrada desejada no barramento 185.

[0055] Por exemplo, o controlador 520 executa lógica de mascaramento para identificar nomeadamente as informações do sensor que devem ser mascaradas ou ignoradas. Quando assim mascaradas ou ignoradas, as informações do sensor de um recurso de processamento correspondente ou bloco funcional 402-408 que estão em um estado desligado. Em outro exemplo, o controlador 520 desliga o sensor selecionado e desvia o sensor quando o respectivo recurso de processamento está em um estado desligado. Apesar de um percurso de desvio ou circuito não ser mostrado por simplicidade de ilustração, deve ser entendido que um ou mais dos sensores distribuídos sobre o domínio de potência 500 podem ser aumentados por um circuito de desvio ou percurso. Quando assim provida, informação de estado incorporada e uma respectiva frequência de relógio, quando aplicável, serão comunicadas ao longo do barramento 521, para evitar o sensor ou sensores desviados, no caminho para o controlador 520.

[0056] As informações de estado identificam uma condição atual dos recursos de processamento ou blocos funcionais 402-408 que operam dentro do domínio de potência 500. Dito de outra maneira, a lógica de estado de recurso 522 é responsiva à presença de uma respectiva tensão de alimentação para os recursos de processamento em um domínio de potência. As informações de estado comunicadas no barramento 521 são comunicadas de acordo com um protocolo de sinal de cadeia de sensor modificado. Em algumas modalidades as informações de estado são um status binário (por exemplo, ligar / desligar, ou seja, a potência é aplicada ou a alimentação não é aplicada). Por exemplo, um estado aplicado de potência pode ser determinado quando um dos comutadores 401-407 controladamente é dirigido para uma posição fechada e uma tensão de entrada presente no barramento 185 é provida ou fornecida ao bloco funcional correspondente. A condição atual está associada em uma relação um-para-um com o respectivo bloco funcional. Quando as informações de estado identificam ainda um estado alto, intermediário ou de baixa potência ou condição em adição à potência na condição, a informação adicional é representada por mais do que um único bit binário.

[0057] A figura 6 é um diagrama esquemático de uma outra modalidade de um domínio de potência modificado 600. O domínio de potência modificado 600 diferente do domínio de potência 500 em que o domínio de potência 600 é arranjado com um controlador 620 com ambas a lógica de estado de recursos 622 e lógica de sintonização de frequência 624. O controlador 620 gera um primeiro sinal de controle que é encaminhado para a fonte de alimentação 180 na conexão 625. O controlador 620 gera adicionalmente um segundo sinal de controle comunicado na conexão 623 que inclui uma afinidade ou preferência para um ou mais recursos de processamento, em vez de outros recursos de processamento no domínio de potência 600. O segundo sinal de controle é comunicado a um programador 630 que utiliza a informação de afinidade ou preferência para determinar quais recursos de processamento ou blocos funcionais são necessários para atender a demanda atual de desempenho. O programador 630 pode ser incorporado em circuitos (hardware) ou em software como em um gerenciador de potência ou hipervisor. No entanto incorporado, o programador 630 aplica lógica para atribuir tarefas aos recursos de processamento. Atribuições de tarefas são comunicadas na forma de informação de controle comunicada na conexão 635 para cada um dos blocos funcionais 402-408 do domínio de potência 600 ou, em alternativa, para as fontes de sinal de relógio acopladas a cada uma da conexão 416-419.

[0058] Como ilustrado, um conjunto de sensores é acoplado em série uns com os outros em um barramento de sensor 521, que começa e termina no controlador 620. Sensor 631 está localizado ao longo do barramento 521 em uma região circuito entre o controlador 620 e bloco funcional 402. Da mesma forma, sensor 636 está localizado ao longo do barramento 521 em uma região de circuito entre o bloco funcional 408 e o controlador 620. Os sensores localizados ao longo do barramento 521 proveem um indicador ou índice com os dados de capacidade de resposta. O indicador ou índice definem uma região de circuito correspondente ou bloco funcional do domínio de potência 600. A informação de resposta provida a partir de várias regiões do circuito fora dos blocos funcionais ou dentro dos blocos funcionais 402408 correspondente é usada pela lógica de estado de recurso 622 no controlador 620 para ajustar o primeiro sinal de controle na conexão 625. Além disso, os sensores localizados dentro de um ou mais dos blocos funcionais podem prover 402408 informação de frequência de relógio ao longo do barramento 521 para a lógica de sintonização de frequência 624 no controlador 620. A lógica de sintonização de frequência 624 usa a informação de relógio de frequência em conjunto com a informação de estado para ajustar o segundo sinal de controle na conexão 623. Apesar de um percurso de desvio ou circuito não ser mostrado por simplicidade de ilustração, deve ser entendido que um ou mais dos sensores distribuídos sobre o domínio de potência 600 podem ser aumentados por um circuito ou caminho de desvio. Quando assim provida, informação de estado incorporada e uma respectiva de frequência de relógio, quando aplicável, serão comunicadas ao longo do barramento 521, evitando assim o sensor ou sensores desviados, no caminho para o controlador 620.

[0059] A figura 7 é um diagrama esquemático de um exemplo de modalidade de um domínio de potência modificado 700. O domínio de potência 700 inclui vários recursos de processamento díspares ou heterogêneos que recebem potência através de um barramento de potência compartilhado 185. O domínio de potência 700 inclui processador de vários núcleos 210, GPU 190, CODEC de Vídeo 134 e CODEC estéreo / áudio 150. Durante os tempos quando um ou mais destes recursos de processamento díspares estão ociosos, um controlador 720 pode ajustar a tensão de entrada no barramento de potência compartilhada 185 através da manipulação do sinal de controle na conexão 725 para a fonte de alimentação 180 para reduzir o gasto de potência enquanto ainda alcança um desempenho desejado.

[0060] O domínio de potência 700 recebe vários sinais de relógio. Na modalidade ilustrada, o domínio de potência 700 recebe um respectivo sinal de relógio de cada recurso de processamento. Uma primeira entrada de sinal de relógio 716 é acoplada à CPU 210. Uma segunda entrada de sinal de relógio 717 é acoplada a GPU 190. Uma terceira entrada de sinal de relógio 718 é acoplada ao CODEC de vídeo 134. Uma quarta entrada de sinal de relógio 719 é acoplada ao CODEC estéreo / áudio 150. As respectivas entradas de sinal de relógio 716-719 são responsivas para controlar entradas comunicadas do hipervisor 240 para a respectiva fonte de relógio de loop travado por fase. Em modalidades alternativas, o domínio de potência 700 pode ser disposto com mais ou menos blocos funcionais. Entre essas modalidades alternativas uma fonte de sinal de relógio pode ser compartilhada entre os blocos funcionais que respondem de forma semelhante às variações da tensão de entrada.

[0061] Na modalidade ilustrada, o domínio de potência 700 inclui um barramento 185, que provê uma tensão de entrada ajustável para a CPU 210, GPU 190, CODEC de vídeo 134, e CODEC estéreo / áudio 150. Na disposição ilustrada, a tensão de entrada no barramento 185 não é comutada, antes de ser provida para a CPU 210. Ao contrário, a CPU 210, a tensão de entrada no barramento 185 é transportada para a GPU 190, o CODEC vídeo 134 e CODEC de estéreo / áudio 150 através do comutador 701, comutador 702, e comutador 703, respectivamente. Um controlador 720 provê um sinal de controle através de uma conexão 725 para a fonte de alimentação 180. O sinal de controle é responsivo à informação de estado comunicada no barramento 721. O controlador 720 inclui uma lógica de estado de recurso 722, que está disposta para alterar o sinal de controle de forma que resulta em uma tensão desejada na saída da fonte de alimentação. A lógica de estado de recurso 722 responde de uma maneira desejada e consistente para a informação de estado recebida no barramento 721. A informação de estado inclui se cada um de GPU 190, o CODEC de vídeo 134, ou CODEC estéreo / áudio 150 está em um estado ligado, desligado ou em um intermediário, de espera ou baixa e. A tensão ajustada ou desejada é distribuída a cada um dos comutadores 701-703 para prover controladamente a tensão ajustada para a GPU 190, o CODEC de vídeo 134 e CODEC estéreo / áudio 150. Uso dinâmico desses recursos de processamento cria uma oportunidade para ajustar um parâmetro de entrada, tais como a tensão de entrada, a frequência de um relógio, ou ambos quando uma mudança de estado ou de mudança no estado relacionado com um recurso de processamento no domínio de potência 700 ocorre.

[0062] O domínio de potência 700 é ainda provido com um conjunto de sensores dispostos com circuitos de teste configurados para determinar a capacidade de resposta dos circuitos proximais para cada um dos respectivos sensores. Tal como ilustrado, o conjunto de sensores são acoplados em série sobre um barramento de sensor 721 que se inicia e termina no controlador 720. O sensor 731 está localizado ao longo do barramento 721 em uma região de circuito entre o controlador 720 e a CPU de vários núcleos 210. Do mesmo modo, o sensor 736 está localizado ao longo do barramento 721 em uma região de circuito entre CODEC estéreo / áudio 150 e o controlador 720. Sensores no barramento 721 estão dispostos para prover um indicador ou índice com os dados de capacidade de resposta. O indicador ou índice define uma região do circuito correspondente ou de blocos funcionais no domínio de potência 700. As informações proveem a capacidade de resposta das várias regiões do circuito fora dos recursos de processamento ou dentro da CPU correspondente 210, GPU 190, CODEC de vídeo 134 ou CODEC de estéreo / áudio 150 pode ser usado pela lógica de estado de recurso 722 ou outros circuitos lógicos no controlador 720 para ajustar o sinal de controle sobre a conexão 725. Apesar de um percurso de desvio ou circuito não ser mostrado por simplicidade de ilustração, deve ser entendido que um ou mais dos sensores distribuídos sobre o domínio de potência 700 podem ser aumentados por tal um circuito ou caminho de desvio. Quando assim providas, informações de estado incorporadas serão comunicadas ao longo do barramento 721, evitando assim o sensor ou sensores desviados, no caminho para o controlador 720.

[0063] A figura 8 é um fluxograma que ilustra um exemplo de modalidade um método 800 para dinamicamente controlar uma entrada para um domínio de potência em um dispositivo de computação portátil. No bloco 802, uma condição atual de pelo menos dois recursos de processamento de um domínio de potência do dispositivo de computação portátil é identificada. Conforme descrito, a condição atual inclui, pelo menos, um estado ligado / desligado para cada um dos recursos de processamento. Em algumas modalidades, a condição atual definirá um estado de baixo consumo de potência ou espera. Ainda alguns outros arranjos, a condição atual pode incluir informações adicionais, como uma frequência de relógio. No bloco 804, um parâmetro de entrada é ajustado em resposta a uma mudança no estado do domínio de potência identificado no bloco 802. O ajuste inclui um aumento ou diminuição no potencial elétrico aplicado por uma fonte de alimentação que está acoplada a uma calha de entrada no domínio de potência. Em algumas modalidades, o ajuste pode ainda incluir um aumento ou uma diminuição da frequência de um sinal de relógio acoplado a um respectivo dos recursos de processamento no domínio de potência. No bloco 806, o parâmetro de entrada é aplicado ao domínio de potência.

[0064] Determinadas etapas nos processos ou fluxos de processo descritos nesta divulgação naturalmente precedem outros para a invenção para funcionarem da forma descrita. No entanto, a invenção não está limitada à ordem das etapas descritas, se tal ordem ou sequência não alterar a funcionalidade da invenção. Isto é, é reconhecido que algumas etapas podem realizadas antes, depois, ou em paralelo (substancialmente simultaneamente) com outras etapas, sem se afastar do âmbito da invenção. Em alguns casos, certas etapas podem ser omitidas ou não realizadas sem se afastar da invenção. Além disso, palavras tais como "depois", "em seguida", "próximo", "posteriormente", etc., não se destinam a limitar a ordem das etapas. Estas palavras são simplesmente usadas para orientar o leitor através da descrição do método exemplar.

[0065] Além disso, um versado no gerenciamento de potência dentro de um dispositivo de computação portátil é capaz de identificar o hardware adequado e/ou circuitos e/ou identificar lógica e determinações apropriadas para implementar a invenção descrita sem dificuldade com base nos fluxogramas e descrição associadas nesta divulgação. Portanto, a divulgação de um determinado conjunto de instruções de código de programa, limites de decisão ou dispositivos de hardware detalhados não é considerada necessária para uma adequada compreensão de como fazer e usar a invenção. A funcionalidade inventiva e aspectos dos processos reivindicados habilitados por processador e arquiteturas de circuito são explicados em mais detalhes na descrição acima e em conjunto com os desenhos, os quais podem ilustrar vários fluxos do processo.

[0066] Em um ou mais aspectos exemplares como indicado acima, as funções descritas podem ser implementadas em hardware, software, firmware, ou qualquer combinação dos mesmos. E se implementadas em software, as funções podem ser armazenadas como uma ou mais instruções ou código em um meio legível por computador, tal como um meio legível por processador não transitório. Meios legíveis por computador incluem meios de armazenamento de dados.

[0067] Um meio de armazenamento pode ser qualquer meio disponível que pode ser acessado por um computador ou um processador. A título de exemplo, e não como limitação, tais meios legíveis por computador podem compreender RAM, ROM, EEPROM, CD-ROM ou outro armazenamento em disco óptico, armazenamento em disco magnético ou outros dispositivos de armazenamento magnéticos, ou qualquer outro meio que pode ser utilizado para portar ou armazenar código de programa desejado sob a forma de instruções ou estruturas de dados e que pode ser acessado por um computador. Disco e disquete, como aqui utilizado, inclui disco compacto ("CD"), disco laser, disco óptico, disco versátil digital ("DVD"), disquete e discos Blu-ray onde disquetes geralmente reproduzem dados magneticamente, enquanto que discos reproduzem dados opticamente com lasers. Combinações dos anteriores também devem ser incluídas no âmbito dos meios legíveis por computador não transitórios.

[0068] Embora os aspectos selecionados tenham sido ilustrados e descritos em detalhe, será entendido que diversas substituições e modificações podem ser aqui feitas sem se afastarem dos presentes sistemas e métodos, tal como definido pelas reivindicações seguintes.

Claims (15)

1. Método para controlar dinamicamente um domínio de potência (500) em um dispositivo de computação portátil (100), o domínio de potência (500) incluindo recursos de processamento (402,404,406,408) que compartilham uma fonte de alimentação, o método caracterizado pelo fato de que compreende: monitorizar condições atuais de pelo menos dois recursos de processamento (402, 404, 406, 408) no domínio de potência (500) no dispositivo de computação portátil (100); identificar uma mudança na condição atual de um de pelo menos dois recursos de processamento (402, 404, 406, 408) no domínio de potência (500) no dispositivo de computação portátil (100), em que a identificação de uma mudança na condição atual de um dos pelo menos dois recursos de processamento no domínio de potência é realizada ao processar informação recebida de uma cadeia de sensores, em que a informação compreende informação de estado e frequência de relógio dos respectivos recursos de processamento; determinar um ajuste em um parâmetro de entrada para o domínio de potência (500), em resposta à mudança identificada na condição atual de um dos pelo menos dois recursos de processamento (402, 404, 406, 408); e aplicar o ajuste determinado para o parâmetro de entrada ao domínio de potência (500), em que o ajuste aplicado para o parâmetro de entrada ao domínio de potência (500) é distribuído a cada um dos recursos de processamento (402, 404, 406, 408) dentro do domínio de potência (500).

2. Método, de acordo com a reivindicação 1, caracterizado pelo fato de que identificar uma mudança na condição atual de um dos pelo menos dois recursos de processamento (402, 404, 406, 408) compreende identificar uma mudança em um indicador de status binário associado a um dos pelo menos dois recursos de processamento (402, 404, 406, 408).

3. Método, de acordo com a reivindicação 1, caracterizado pelo fato de que identificar uma mudança na condição atual de um dos pelo menos dois recursos de processamento (402, 404, 406, 408) compreende identificar uma mudança em uma frequência de relógio associada a um dos pelo menos dois recursos de processamento (402, 404, 406, 408).

4. Método, de acordo com a reivindicação 1, caracterizado pelo fato de que identificar uma mudança na condição atual de um dos pelo menos dois recursos de processamento (402, 404, 406, 408) compreende receber um sinal que indica a mudança a partir de um gerenciador de potência de sistema.

5. Método, de acordo com a reivindicação 1, caracterizado pelo fato de que aplicar o ajuste determinado para o parâmetro de entrada ao domínio de potência (500) compreende utilizar lógica de estado de hardware de recurso.

6. Método, de acordo com a reivindicação 5, caracterizado pelo fato de que usar lógica de estado de hardware de recurso inclui gerar um sinal de controle dirigido para uma fonte de alimentação (180).

7. Método, de acordo com a reivindicação 1, caracterizado pelo fato de que identificar uma mudança na condição atual de um dos pelo menos dois recursos de processamento (402, 404, 406, 408) compreende receber um sinal proveniente de um sensor associado a um dos pelo menos dois recursos de processamento (402, 404, 406, 408).

8. Método, de acordo com a reivindicação 7, caracterizado pelo fato de que o sinal proveniente do sensor indica uma frequência de relógio.

9. Método, de acordo com a reivindicação 7, caracterizado pelo fato de que o sinal proveniente do sensor indica um estado ligado/desligado de uma fonte de alimentação (180).

10. Método, de acordo com a reivindicação 7, caracterizado pelo fato de que compreende adicionalmente executar lógica de mascaramento para filtrar um sinal recebido antes de determinar um ajuste para o parâmetro de entrada.

11. Método, de acordo com a reivindicação 7, caracterizado pelo fato de que o sinal proveniente do sensor desvia de um segundo sensor associado com um segundo recurso dos pelo menos dois recursos de processamento (402, 404, 406, 408).

12. Método, de acordo com a reivindicação 1, caracterizado pelo fato de que aplicar o ajuste determinado para o parâmetro de entrada ao domínio de potência (500) compreende comunicar informações para um programador (630) que aloca tarefas aos pelo menos dois recursos de processamento (402,404,406,408).

13. Método, de acordo com a reivindicação 12, caracterizado pelo fato de que a informação é selecionada a partir de um ou mais de uma margem de tensão e uma capacidade de resposta relativa de circuitos em uma relação de um-para- um com os pelo menos dois recursos de processamento (402, 404, 406, 408).

14. Domínio de potência (500) disposto em um dispositivo de computação portátil (100), caracterizado pelo fato de que compreende: pelo menos dois recursos de processamento (402, 404, 406, 408) que são alimentados por uma fonte de potência compartilhada; uma cadeia de sensores modificados; e um controlador (520) acoplado aos pelo menos dois recursos de processamento (402, 404, 406,408) e configurado para receber informações a partir de um gerenciador de potência, em que a informação compreende informação de estado e frequência de relógio dos respectivos recursos de processamento recebida de uma cadeia de sensores, o controlador (520) disposto para processar a informação com lógica de estado de hardware de recurso para gerar um primeiro sinal de controle utilizado por uma fonte de alimentação (180) para determinar uma tensão de entrada desejada para os pelo menos dois recursos de processamento (402, 404, 406, 408) no domínio de potência (500), em que a tensão de entrada desejada é distribuída a cada recurso de processamento (402, 404, 406, 408) dentro do domínio de potência (500).

15. Memória legível por computador, caracterizada pelo fato de que contém gravado na mesma o método conforme definido em qualquer uma das reivindicações 1 a 13.

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201461970290P | 2014-03-25 | 2014-03-25 | |

| US61/970,290 | 2014-03-25 | ||

| US14/266,642 US9671857B2 (en) | 2014-03-25 | 2014-04-30 | Apparatus, system and method for dynamic power management across heterogeneous processors in a shared power domain |

| US14/266,642 | 2014-04-30 | ||

| PCT/US2015/022326 WO2015148565A1 (en) | 2014-03-25 | 2015-03-24 | Apparatus, system and method for dynamic power management across heterogeneous processors in a shared power domain |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| BR112016022266A2 BR112016022266A2 (pt) | 2017-08-15 |

| BR112016022266B1 true BR112016022266B1 (pt) | 2022-10-18 |

Family

ID=54190265

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| BR112016022266-0A BR112016022266B1 (pt) | 2014-03-25 | 2015-03-24 | Método para controlar dinamicamente um domínio de potência em um dispositivo de computação portátil, domínio de potência disposto em um dispositivo de computação portátil e memória legível por computador |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US9671857B2 (pt) |

| EP (1) | EP3129855A1 (pt) |

| JP (1) | JP6203425B2 (pt) |

| KR (1) | KR20160136410A (pt) |

| CN (1) | CN106133641B (pt) |

| BR (1) | BR112016022266B1 (pt) |

| WO (1) | WO2015148565A1 (pt) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9671857B2 (en) | 2014-03-25 | 2017-06-06 | Qualcomm Incorporated | Apparatus, system and method for dynamic power management across heterogeneous processors in a shared power domain |

| US10488902B2 (en) | 2015-02-23 | 2019-11-26 | Qualcomm Innovation Center, Inc. | Dynamic multi-core processor voltage scaling based on online core count |

| US10142196B1 (en) | 2016-04-15 | 2018-11-27 | Senseware, Inc. | System, method, and apparatus for bridge interface communication |

| US10896138B2 (en) * | 2016-05-27 | 2021-01-19 | Apple Inc. | Dynamically controlling random access memory retention in a wireless device |

| US20180150256A1 (en) * | 2016-11-29 | 2018-05-31 | Intel Corporation | Technologies for data deduplication in disaggregated architectures |

| US10401938B1 (en) | 2017-04-10 | 2019-09-03 | Apple Inc. | Single power plane dynamic voltage margin recovery for multiple clock domains |

| US10417054B2 (en) * | 2017-06-04 | 2019-09-17 | Apple Inc. | Scheduler for AMP architecture with closed loop performance controller |

| KR102563648B1 (ko) * | 2018-06-05 | 2023-08-04 | 삼성전자주식회사 | 멀티 프로세서 시스템 및 그 구동 방법 |

| CN110442224A (zh) * | 2019-09-17 | 2019-11-12 | 联想(北京)有限公司 | 电子设备的电源功率分配方法、电子设备和可读存储介质 |

| TWI708957B (zh) * | 2019-12-12 | 2020-11-01 | 聚眾聯合科技股份有限公司 | 動態功率定位方法及其動態功率定位系統 |

| US20210200298A1 (en) * | 2019-12-30 | 2021-07-01 | Advanced Micro Devices, Inc. | Long-idle state system and method |

| CN113311934B (zh) * | 2021-04-09 | 2022-10-11 | 北京航空航天大学 | 一种多核异构域控制器动态功耗调整方法及系统 |

| KR20240044533A (ko) * | 2021-09-24 | 2024-04-04 | 애플 인크. | 전역 집적 회로 전력 제어 |

| CN114297131A (zh) * | 2021-11-15 | 2022-04-08 | 平头哥(上海)半导体技术有限公司 | 传感器控制系统、片上系统和计算装置 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3068394B2 (ja) * | 1993-12-16 | 2000-07-24 | 株式会社東芝 | センサシステム |

| US6802014B1 (en) * | 2000-10-26 | 2004-10-05 | Apple Computer, Inc. | Method and apparatus for managing power in computer systems |

| JPWO2002050645A1 (ja) * | 2000-12-20 | 2004-04-22 | 株式会社日立製作所 | 低消費電力の電子回路及び消費電力低減方法 |

| US6952748B1 (en) | 2001-01-02 | 2005-10-04 | Advanced Micro Devices, Inc. | Voltage request arbiter |

| US7302599B2 (en) * | 2004-02-12 | 2007-11-27 | Via Technologies, Inc. | Instantaneous frequency-based microprocessor power management |

| GB2403561A (en) | 2003-07-02 | 2005-01-05 | Advanced Risc Mach Ltd | Power control within a coherent multi-processor system |

| US7039539B2 (en) * | 2003-10-07 | 2006-05-02 | Hewlett-Packard Development Company, L.P. | Rack equipment environmental condition adjustment system and method |

| US7526661B2 (en) * | 2004-12-02 | 2009-04-28 | Intel Corporation | Performance state-based thread management |

| KR101054946B1 (ko) | 2005-02-23 | 2011-08-08 | 삼성전자주식회사 | 전압 레벨 조정 기능을 가진 시스템 온 칩 및 전압 레벨 조정 방법 |

| US8327158B2 (en) * | 2006-11-01 | 2012-12-04 | Texas Instruments Incorporated | Hardware voting mechanism for arbitrating scaling of shared voltage domain, integrated circuits, processes and systems |

| US8725488B2 (en) | 2007-07-26 | 2014-05-13 | Qualcomm Incorporated | Method and apparatus for adaptive voltage scaling based on instruction usage |

| JP4800289B2 (ja) | 2007-11-30 | 2011-10-26 | 富士通セミコンダクター株式会社 | 電源制御装置及びその電源制御装置を有するシステムlsi |

| US8051320B2 (en) | 2007-12-12 | 2011-11-01 | Mips Technologies, Inc. | Clock ratio controller for dynamic voltage and frequency scaled digital systems, and applications thereof |

| US8370663B2 (en) | 2008-02-11 | 2013-02-05 | Nvidia Corporation | Power management with dynamic frequency adjustments |

| KR101512493B1 (ko) | 2009-02-06 | 2015-04-15 | 삼성전자주식회사 | 저전력 시스템온칩 |

| US8904115B2 (en) | 2010-09-28 | 2014-12-02 | Texas Instruments Incorporated | Cache with multiple access pipelines |

| US8984313B2 (en) * | 2012-08-31 | 2015-03-17 | Intel Corporation | Configuring power management functionality in a processor including a plurality of cores by utilizing a register to store a power domain indicator |

| US9268382B2 (en) * | 2013-07-01 | 2016-02-23 | Oracle International Corporation | Method and system for monitoring resource usage of logical domains |

| US9671857B2 (en) | 2014-03-25 | 2017-06-06 | Qualcomm Incorporated | Apparatus, system and method for dynamic power management across heterogeneous processors in a shared power domain |

-

2014

- 2014-04-30 US US14/266,642 patent/US9671857B2/en active Active

-

2015

- 2015-03-24 KR KR1020167029506A patent/KR20160136410A/ko not_active Application Discontinuation

- 2015-03-24 WO PCT/US2015/022326 patent/WO2015148565A1/en active Application Filing

- 2015-03-24 CN CN201580015545.2A patent/CN106133641B/zh active Active

- 2015-03-24 EP EP15715920.3A patent/EP3129855A1/en not_active Withdrawn

- 2015-03-24 BR BR112016022266-0A patent/BR112016022266B1/pt active IP Right Grant

- 2015-03-24 JP JP2016558082A patent/JP6203425B2/ja active Active

- 2015-08-28 US US14/839,836 patent/US9733694B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2017511538A (ja) | 2017-04-20 |

| JP6203425B2 (ja) | 2017-09-27 |

| CN106133641A (zh) | 2016-11-16 |

| US9733694B2 (en) | 2017-08-15 |

| US9671857B2 (en) | 2017-06-06 |

| KR20160136410A (ko) | 2016-11-29 |

| EP3129855A1 (en) | 2017-02-15 |

| WO2015148565A1 (en) | 2015-10-01 |

| US20150370316A1 (en) | 2015-12-24 |

| CN106133641B (zh) | 2019-08-06 |

| BR112016022266A2 (pt) | 2017-08-15 |

| US20150277536A1 (en) | 2015-10-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| BR112016022266B1 (pt) | Método para controlar dinamicamente um domínio de potência em um dispositivo de computação portátil, domínio de potência disposto em um dispositivo de computação portátil e memória legível por computador | |

| US20240028094A1 (en) | Techniques To Enable Communication Between A Processor And Voltage Regulator | |

| JP6162262B2 (ja) | 最適な電力レベルを予測するために熱抵抗値を使用したポータブルコンピューティングデバイスにおける熱管理のためのシステムおよび方法 | |

| US9292076B2 (en) | Fast recalibration circuitry for input/output (IO) compensation finite state machine power-down-exit | |

| US8959576B2 (en) | Method, apparatus, system for qualifying CPU transactions with security attributes | |

| KR102190453B1 (ko) | 전력 관리 장치 및 이를 포함하는 시스템 온 칩 | |

| TWI596468B (zh) | 對於系統單晶片中的記憶體存取之功率管理的技術 | |

| CN108780349B (zh) | 用于在具有异构集群架构的片上系统中进行智能热管理的系统和方法 | |

| BR112020019436A2 (pt) | Sistema, aparelho e método para restrição otimizada de um processador | |

| US10491003B2 (en) | Multiple input single inductor multiple output regulator | |

| EP3345070B1 (en) | Systems and methods for dynamically adjusting memory state transition timers | |

| US9519041B2 (en) | System and method for providing an accurate and cost-effective current sensor calibration | |

| BR112017007876B1 (pt) | Sistema de processamento de processador múltiplo, aparelho, método de comutação de uma pluralidade de processadores entre um modo de processamento múltiplo simétrico (smp) e um modo de processamento múltiplo assimétrico (asmp), e método de processamento em um sistema de processador múltiplo que tem uma pluralidade de processadores | |

| JP6240225B2 (ja) | ポータブルコンピューティングデバイスにおける電圧モードの温度駆動型選択のためのシステムおよび方法 | |

| US10496298B2 (en) | Configurable flush of data from volatile memory to non-volatile memory | |

| US11656676B2 (en) | System, apparatus and method for dynamic thermal distribution of a system on chip | |

| US20220116322A1 (en) | Interconnect network for multi-tile system on chips | |

| US10234920B2 (en) | Controlling current consumption of a processor based at least in part on platform capacitance | |

| US20160077959A1 (en) | System and Method for Sharing a Solid-State Non-Volatile Memory Resource | |

| TWI772438B (zh) | 用於計算設備中的動態緩衝器大小設定的系統和方法 | |

| US20220199573A1 (en) | Modular low latency electrical sequence for die-to-die interface |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| B06U | Preliminary requirement: requests with searches performed by other patent offices: procedure suspended [chapter 6.21 patent gazette] | ||

| B350 | Update of information on the portal [chapter 15.35 patent gazette] | ||

| B09A | Decision: intention to grant [chapter 9.1 patent gazette] | ||

| B16A | Patent or certificate of addition of invention granted [chapter 16.1 patent gazette] |

Free format text: PRAZO DE VALIDADE: 20 (VINTE) ANOS CONTADOS A PARTIR DE 24/03/2015, OBSERVADAS AS CONDICOES LEGAIS |