WO2011108150A1 - 記録媒体、再生及び記録方法、再生及び記録装置 - Google Patents

記録媒体、再生及び記録方法、再生及び記録装置 Download PDFInfo

- Publication number

- WO2011108150A1 WO2011108150A1 PCT/JP2010/070020 JP2010070020W WO2011108150A1 WO 2011108150 A1 WO2011108150 A1 WO 2011108150A1 JP 2010070020 W JP2010070020 W JP 2010070020W WO 2011108150 A1 WO2011108150 A1 WO 2011108150A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- address

- bits

- data

- recording

- bit

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B20/00—Signal processing not specific to the method of recording or reproducing; Circuits therefor

- G11B20/10—Digital recording or reproducing

- G11B20/12—Formatting, e.g. arrangement of data block or words on the record carriers

- G11B20/1217—Formatting, e.g. arrangement of data block or words on the record carriers on discs

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B27/00—Editing; Indexing; Addressing; Timing or synchronising; Monitoring; Measuring tape travel

- G11B27/10—Indexing; Addressing; Timing or synchronising; Measuring tape travel

- G11B27/19—Indexing; Addressing; Timing or synchronising; Measuring tape travel by using information detectable on the record carrier

- G11B27/28—Indexing; Addressing; Timing or synchronising; Measuring tape travel by using information detectable on the record carrier by using information signals recorded by the same method as the main recording

- G11B27/32—Indexing; Addressing; Timing or synchronising; Measuring tape travel by using information detectable on the record carrier by using information signals recorded by the same method as the main recording on separate auxiliary tracks of the same or an auxiliary record carrier

- G11B27/322—Indexing; Addressing; Timing or synchronising; Measuring tape travel by using information detectable on the record carrier by using information signals recorded by the same method as the main recording on separate auxiliary tracks of the same or an auxiliary record carrier used signal is digitally coded

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B20/00—Signal processing not specific to the method of recording or reproducing; Circuits therefor

- G11B20/10—Digital recording or reproducing

- G11B20/12—Formatting, e.g. arrangement of data block or words on the record carriers

- G11B2020/1264—Formatting, e.g. arrangement of data block or words on the record carriers wherein the formatting concerns a specific kind of data

- G11B2020/1265—Control data, system data or management information, i.e. data used to access or process user data

- G11B2020/1267—Address data

- G11B2020/1268—Address in pregroove [ADIP] information

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B2220/00—Record carriers by type

- G11B2220/20—Disc-shaped record carriers

- G11B2220/23—Disc-shaped record carriers characterised in that the disc has a specific layer structure

- G11B2220/235—Multilayer discs, i.e. multiple recording layers accessed from the same side

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B2220/00—Record carriers by type

- G11B2220/20—Disc-shaped record carriers

- G11B2220/25—Disc-shaped record carriers characterised in that the disc is based on a specific recording technology

- G11B2220/2537—Optical discs

- G11B2220/2541—Blu-ray discs; Blue laser DVR discs

Definitions

- the present invention relates to a recording medium on which an address is recorded, for example, an optical disc, a reproducing and recording method of the optical disc, a reproducing apparatus for recording and reproducing data from the recording medium, and a recording apparatus.

- PSN Physical Sector PS Number

- PAA Physical ADIP Address

- An object of the present invention is to provide a recording medium, an address generation and detection method, a reproduction and recording apparatus capable of extending a wobble address without implementing a significant wobble structure modification.

- a virtual bit that is not recorded on the disk is generated, which is represented by the presence or absence of information embedded in part or all of the wobble address and the difference in rules.

- FIG. 3 is a correlation diagram of addresses of the multilayer optical disc that is the first embodiment of the present invention.

- FIG. 3 is a timing diagram of address detection in the first exemplary embodiment of the present invention.

- FIG. 3 is a detection circuit diagram of address detection in the first exemplary embodiment of the present invention.

- FIG. 6 is a correlation diagram of addresses of a multilayer optical disc that is a second embodiment of the present invention.

- FIG. 6 is a timing diagram of address detection in the second embodiment of the present invention.

- FIG. 6 is a detection circuit diagram for address detection in a second exemplary embodiment of the present invention.

- FIG. 6 is a correlation diagram of addresses of a multilayer optical disc that is a third embodiment of the present invention.

- FIG. 6 is an example of a scramble circuit according to a third embodiment of the present invention.

- FIG. 10 is a timing diagram of address detection in a third embodiment of the present invention.

- FIG. 10 is a detection circuit diagram for address detection in a third exemplary embodiment of the present invention.

- FIG. 10 is a correlation diagram of addresses of an optical disc that is a fourth embodiment of the present invention.

- 1 is an optical disc recording / reproducing apparatus according to a first embodiment of the present invention. It is an address field structure figure of a multilayer optical disk. It is a data structure of a multilayer optical disk, an ECC structure, and a frame structure diagram. It is an ADIP data structure figure of a multilayer optical disk. It is an ADIP word structure figure of a multilayer optical disk.

- FIG. 10 is an address correlation diagram of an optical disc that is a fifth embodiment of the present invention.

- FIG. 10 is a timing diagram of address detection in the fifth exemplary embodiment of the present invention.

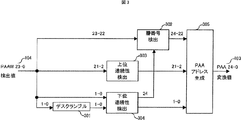

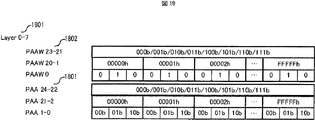

- FIG. 1 is a correlation diagram of addresses of a multilayer optical disk according to the first embodiment of the present invention.

- 101 is the physical sector number (hereinafter referred to as PSN) which is the physical sector number of the sector

- 102 is the address unit number (hereinafter referred to as AUN) which is the address embedded in the data of the cluster unit

- 103 is the physical ADIP address by wobble Is the actual address of the physical ADIP address (hereinafter referred to as PAA)

- PAAW the address actually embedded in the wobble of the physical ADIP address

- 105 is the scramble circuit

- 106 is the exclusive OR (Ex-OR) Show.

- scramble is one of arithmetic processes, and means a process for converting the value of each bit of an address or converting regularity.

- the upper 3 bits of PAA 103 are assigned to the layer number, and the conventional PAA An example of address extension from 24 bits to 1 bit is shown.

- the bit information of PAA bit 24, which is a virtual bit for address extension is assumed to be embedded in wobble in association with the lower 2 bits of PAA.

- a conventional PAA 24-bit configuration when assigned as a 3-bit layer number, 19-bit cluster number, and 2-bit intra-cluster count value, up to 8 layer numbers and 32 gigabytes per layer (64 kilobytes x 2 19 ) An address can be assigned to data having a data capacity of.

- the wobble address structure will be described.

- the ADIP address 24 bits (AA23-AA0) 104 recorded on the disc and the 12-bit auxiliary data (AUX data, AX11-AX0) 1301 for storing disc information are 36 bits.

- a structure having information bits is defined, and an error correction code addition and code conversion are performed on the information bits to generate a code string per unit data.

- This code string is embedded in the wobble structure per unit period.

- a wobble structure with different wobble periodicity and phase is arranged based on certain rules, and a bit structure called ADIP unit is generated by expressing synchronization signals and data “0” and “1” due to the difference in arrangement etc. To do.

- ADIP word structure diagram of Fig. 16 after the previous ADIP data 36 bit error correction code addition conversion to 1 bit ADIP word structure consisting of 83 bits (60 bits (4 ADIP bits x 15 blocks)) A code string having a value of 60 bits is arranged.

- the address structure Since the address structure is generated, it is possible to obtain an ADIP address that specifies a physical position on the disk by converting a code string obtained with a certain period of wobble. Therefore, the ADIP address recorded on the disc is 24 bits to the last, and when the bit number of the ADIP address is increased by 1 bit, the wobble address structure needs to be significantly modified. Either a 36-bit information bit structure, a parity addition method or conversion method for conversion into a code string, an arrangement period or wobble length, a correlation with a PSN, or a plurality of reviews is required. In this case, the structure becomes difficult to be compatible with the prior art, and the redundancy of the address generation / detection circuit and the complexity of the system control method become problems. Therefore, if the wobble address can be expanded without significantly modifying the wobble structure without changing the number of address bits embedded in the wobble, the control can be considerably facilitated.

- PAA 25 bits are allocated as the address range on the wobble.

- the number of bits of the address embedded in the disk using wobble is only 24 bits, so the most significant PAA bit 24 is information to other bits as a virtual address bit.

- the PAA bit 24 is input as a control bit for determining ON / OFF of the scramble process of the scramble circuit 105, and the lower two bits of the PAA bit 1-0 are subjected to scramble processing and embedded in the wobble.

- the PAA 1 bits 1-0 are the same as the conventional 0,1 , 2,0,1,2, ... and when PAA bit 24 is “1”, the value after exclusive OR operation is 3,2,1,3,2,1,... Will be counted. That is, the regularity of the count of the PAA bits 1-0 is changed according to the virtual bit PAA bits 24. Therefore, by actually embedding the PAAW bits 1-0, which are the output from the scramble circuit 105, in the wobble, it is possible to avoid embedding the virtual bits PAA bits 24 in the wobble. As an effect, it is possible to extend the address while maintaining the number of bits of the conventional wobble address.

- the descramble circuit 301 is scrambled by the exclusive OR 106 at the time of address generation, the result of the exclusive OR of “1” and the PAAW bits 1-0 is output after the descrambling operation.

- the virtual bit PAA bit 24 is assigned to the third bit of the layer number, the detection result differs depending on the layer number 0 to 3 (201) and the layer number 4 to 7 (202). Become.

- the PAAW bit 1-0 is input as 0,1,2,0,1,2, ... to the lower continuity detection circuit 304, so the PAA bit 24 is "0" “, PAA bits 1-0 will output PAAW bits 1-0 as they are.

- the PAAW bit 1-0 is input to the lower continuity detection circuit 304 as 3, 2, 1, 3, 2, 1,.

- the detection of the address detection value “3” and the decrement of continuity are detected to detect the presence of scramble processing at the time of address generation, and the PAA bit 24 is output as “1”.

- the lower PAA bits 1-0, 0, 1, 2, 0, 1, 2,... which are values after the descrambling process of the PAAW bits 1-0 are output.

- the in-cluster count value (PAA bits 1-0) is detected as the output of the lower continuity detection circuit 304, and further, the layer number detection circuit 302 from the generated PAA bit 24 and the PAAW bit 23-22 detected from the wobble.

- the generation of the layer number address (PAA bits 24-22) and the detection of the layer number are performed. Further, the higher address detection circuit 303 generates a cluster number address (PAA bit 21-2) and detects the cluster number from the PAAW bit 21-2 detected from the wobble. Therefore, the addresses obtained from the respective detection circuits 302, 303, and 304 are input to the PAA address generation circuit 305, and can be converted into addresses of PAA bits 24-0.

- the address structure of the wobble is not changed, and the physical address is not increased without increasing the number of bits of the address embedded in the wobble.

- the number of bits of the address indicating the target position can be expanded.

- the layer number address is expanded with virtual bits as the address assignment of the 2-bit layer number and the 20-bit cluster number, the layer number up to 8 layers and up to 64 GB Applicable to disk.

- it can be applied to disks with up to 16 layer numbers and 32 gigabytes per layer if used to expand the layer number address with the conventional 3-bit layer number and 19-bit cluster number address assignment.

- the virtual bits are controlled as scramble processing OFF in the case of layer numbers 0 to 3 as in this embodiment, the result is the same value as PAA bit 23-0 and PAAW bit 23-0. Compatibility with conventional optical discs can be maintained.

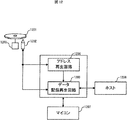

- FIG. 12 shows an example of a recording / reproducing apparatus that reproduces data from and records data from the optical disc created by the address generation described in this embodiment.

- Reference numeral 1201 denotes an optical disc

- 1202 denotes a pickup

- 1203 denotes a spindle motor

- 1204 denotes an address reproduction circuit

- 1205 denotes a data recording / reproduction circuit

- 1206 denotes an external host

- 1207 denotes a microcomputer that controls the entire system.

- a wobble signal read from the optical disk 1201 created using the address generation method shown in FIG. 1 via the pickup 1202 is input to the address reproduction circuit 1204 to detect address information.

- the address detection circuit described with reference to FIG. 3 it is possible to detect the position where data is recorded / reproduced, and to the host 1206 of the data obtained via the pickup 1202 and the data recording / reproduction circuit 1205. Data input / output and data recording / reproduction are possible.

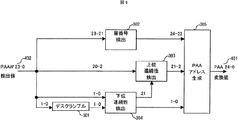

- FIG. 4 is a correlation diagram of addresses of the multilayer optical disk according to the second embodiment of the present invention.

- address expansion is performed using virtual bits that are not recorded on the disk while maintaining the ADIP data structure shown in FIG.

- the difference from FIG. 1 is that the virtual bit allocation is bit 21 instead of PAA bit 24.

- 401 is the actual address of Physical ADIP Address (hereinafter referred to as PAA)

- 402 is the wobble embedded address (hereinafter referred to as PAAW) of Physical ADIP Address, which is the same as in FIG.

- PAA Physical ADIP Address

- PAAW wobble embedded address

- the PAA bit 21 is input as a control bit for determining ON / OFF of the scramble process of the scramble circuit 105, and the lower 2 bits of the PAA bit 1-0 are scrambled. And embed in wobble. That is, the regularity of the count of the PAA bits 1-0 is changed according to the virtual bit PAA bits 21. As an effect, it is possible to extend the address while maintaining the number of bits of the conventional wobble address.

- the virtual bit PAA bit 21 is assigned not to the layer number address but to the cluster number address, so that address generation switching occurs in each layer.

- the low-order continuity detection circuit 304 detects the presence or absence of scramble processing as before. To generate a virtual bit PAA bit 21 and detect PAA 1-0.

- the count value in the cluster (PAA bits 1-0) is detected as an output of the lower continuity detection circuit 304, and the PAA bit 21 detected by the lower continuity detection circuit 304 and the PAAW bit 20- detected from the wobble. 2 is used to generate the cluster number address (PAA bits 21-2), detect the cluster number, and use the PAAW bits 23-22 detected from the wobble to generate the layer number address (PAA bits 24- 22) Detection is performed. Therefore, the addresses obtained from the respective detection circuits 302, 303, and 304 are input to the PAA address generation circuit 305, and can be converted into addresses of PAA bits 24-0.

- the address structure of the wobble is not changed, and the physical address is not increased without increasing the number of bits of the address embedded in the wobble.

- the number of bits of the address indicating the target position can be expanded.

- the virtual bit can be generated and detected in the same manner even if the virtual bit is assigned to the cluster number address of each layer instead of the layer number.

- the address detection circuit described in FIG. 6 is also used in the reproducing apparatus for reproducing data from the optical disk created by the address generation described in this embodiment and the recording apparatus for recording data on the optical disk. This makes it possible to detect the position where data is recorded and reproduced.

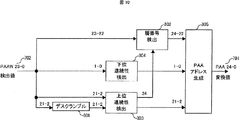

- FIG. 7 is a correlation diagram of addresses of the multilayer optical disk according to the third embodiment of the present invention.

- address expansion is performed using virtual bits that are not recorded on the disk while maintaining the ADIP data structure shown in FIG.

- the difference from FIG. 1 is that the scrambling method is applied not only to the lower 2 bits of PAA bit 1-0 but also to the entire PAA 23-0.

- 701 is the actual address of Physical ADIP Address (hereinafter referred to as PAA)

- 702 is the wobble embedded address (hereinafter referred to as PAAW) of Physical ADIP ⁇ Address

- 703 is a scramble circuit similar to Fig. 1, but only the bit assignment is different, and the others are the same

- FIG. 1 is the actual address of Physical ADIP Address (hereinafter referred to as PAA)

- PAAW wobble embedded address

- 703 is a scramble circuit similar to Fig. 1, but only the bit assignment is different, and the others are the same

- FIG. 1 is the actual address of Physical ADIP Address

- FIG. 8 shows an example of a scramble circuit 703 which is a calculation process for embedding information.

- the exclusive OR 106 with the PAA bit 24 is used for each bit of the PAA bit 21-2 corresponding to the cluster number address, and other bits are input / output as they are. Therefore, when PAA bit 24 is “0”, PAA bit 21-2 increments to 0,1,2,3,4,5,..., FFFFFh, and PAA bit 24 is “1”.

- it since it is a value after the scramble processing, it is decremented to FFFFFh, FFFFEh, FFFFDh,.

- the regularity of the count of the PAA bit 21-2 is changed according to the virtual bit PAA bit 24. As an effect, it is possible to extend the address while maintaining the number of bits of the conventional wobble address.

- the PAA bit 24 which is a virtual bit, checks the continuity of the higher address of the PAAW 1-2 bit 21-2 and performs restoration. Also, as the scrambling method, since the upper 20 bits of PAA bits 21-2 are multiplied by exclusive OR 106, the presence or absence of scrambling in the upper continuity detection circuit 303 (in this example, the difference in continuity between increment and decrement) ) To generate a virtual bit PAA bit 24 and detect PAA 21-2.

- PAAW bit 21-2 is input as 0,1,2,3,4,5, ..., FFFFFh to upper continuity detection circuit 303, so PAA bit 24 is “0” and PAA bit 21-2 output PAAW bit 21-2 as it is.

- PAAW bit 21-2 is input as FFFFFh, FFFFEh, FFFFDh, ..., 0 to upper continuity detection circuit 303, so decrement is detected and PAA bit 24 is output as “1”, and is 0,1,2,3,4,5, ... which is the value after descrambling (in this example, exclusive OR of “1” and PAAW bit 21-2) , FFFFFh is output.

- the cluster number address (PAA (bits 21-2) can be generated and the cluster number can be detected as the output of the upper continuity detection circuit 303.

- the layer number detection circuit 302 generates the layer number address (PAA bits 24-22) and detects the layer number from the generated PAA bits 24 and the PAAW bits 23-22 detected from the wobble.

- the lower address detection circuit 304 detects the in-cluster count value (PAA bits 1-0) from the PAAW bits 1-0 detected from the wobble. Therefore, the addresses obtained from the respective detection circuits 302, 303, and 304 are input to the PAA address generation circuit 305, and can be converted into addresses of PAA bits 24-0.

- the address structure of the wobble is not changed, and the physical address is not increased without increasing the number of bits of the address embedded in the wobble.

- the number of bits of the address indicating the target position can be expanded.

- the virtual bit information can be generated and detected in the same manner by embedding not only a part of the address but also the entire address.

- the address detection circuit described in FIG. 10 is also used in the reproducing apparatus for reproducing data from the optical disk created by the address generation described in the present embodiment and the recording apparatus for recording data on the optical disk. This makes it possible to detect the position where data is recorded and reproduced.

- FIG. 11 is an address correlation diagram of an optical disc according to the fourth embodiment of the present invention.

- address expansion is performed using virtual bits that are not recorded on the disk while maintaining the ADIP data structure shown in FIG.

- the difference from Fig. 7 is that 5 bits of PAA bits 28-24 are used as virtual bits corresponding to PSN bits 31-27, PAA bit 28-2 is the cluster number, and PAA bits 1-0 are set as the structure of PAA 103. It is a point assigned as a count value in the cluster.

- 1101 is the actual address of Physical ADIP Address (hereinafter referred to as PAA)

- 1102 is the wobble embedded address of Physical ADIP Address (hereinafter referred to as PAAW)

- 1103 is the same as in FIG.

- the address structure of the wobble is not changed, and the physical address is not increased without increasing the number of bits of the address embedded in the wobble.

- the number of bits of the address indicating the target position can be expanded.

- the addresses composed of the layer number and the cluster number are explained using addresses composed only of the cluster number in the present embodiment. Is possible.

- the reproducing apparatus for reproducing data from the optical disk created by the address generation described in the present embodiment and the recording apparatus for recording data on the optical disk the position of the data recording / reproducing is similarly detected. Is possible.

- FIG. 18 is a correlation diagram of addresses of the optical disc according to the fifth embodiment of the present invention.

- address expansion is performed using virtual bits that are not recorded on the disk while maintaining the ADIP data structure shown in FIG.

- the difference from Fig. 1 is that 2-bit information is generated from 3-bit information of PAA bits 2-0 instead of switching the presence or absence of conversion to lower 2 bits or switching of regularity by virtual bit PAA bit 24 ( 1 bit is a virtual bit).

- 1801 is the actual address of Physical ADIP Address (hereinafter referred to as PAA)

- PAAW wobble embedded address

- the encoding circuit 1803 uses the regularity of the PAA bits 2-0 to convert to PAAW bits 1-0 and embed them in the wobble. That is, the number of bits can be reduced by generating 2 bits by encoding the 3-bit information. As an effect, it is possible to expand the address without changing the wobble address structure while maintaining the number of bits of the conventional wobble address.

- PAAW bits 1-0 are input to the decoding circuit (not shown) as 00b, 01b, 00b, 10b, 11b, 10b, 00b, etc., so the PAAW bit 0 continuous regularity, PAAW bit 1 switching timing, etc.

- PAA bit 1 can be easily restored from the state transition. Therefore, PAA bit 2-0 is generated using the value of virtual bit PAA bit 1 and PAAW bit 1-0 obtained by the decoding process of PAAW bits 1-0, and converted to the address of PAA bits 24-0 it can.

- the address structure of the wobble is not changed without changing the address structure of the wobble.

- the number of bits of the address indicating the physical position can be expanded without increasing the number of bits.

- the PAA bit 1 has been described as a virtual bit, but any bit can be used as long as it can be easily restored from the regularity of other bits. Even if it is associated with a specific bit, it can be generated and detected in the same manner.

- the address in FIG. 18 is decoded to detect the address. By using this circuit, it is possible to detect the position where data is recorded / reproduced.

- FIGS. 13 and 14 are diagrams showing the AUN structure, data structure, ECC structure, and frame structure used in the sixth embodiment of the present invention.

- a cluster that is a recording / playback unit includes LDC (Long Distance Code) and BIS (Burst Indicator Subcode) for main data (1 sector 2048 bytes ⁇ 32 sectors).

- the main data 64 kilobytes shown in FIG. 14 (a) is ECC-encoded as shown in FIG. 14 (b).

- 4-byte EDC Error Detection Code

- LDC Error Detection Code

- BIS is ECC-encoded as shown in FIG. 14 (d) with respect to 720B data shown in FIG. 14 (c). Furthermore, the data of 248 x 304 bytes shown in Fig. 14 (b) is rearranged into LDC data of 152 x 496 bytes by a predetermined interleaving process, and the data of 62 x 24 bytes shown in Fig. 14 (d) is processed by a predetermined interleaving process. Sort by 3 ⁇ 496 bytes BIS data. Therefore, as shown in Fig.

- one frame is obtained by adding a sync signal (Frame SYNC, FS) to 38 ⁇ 3 bytes (152 bytes) of LDC data and 1 ⁇ 3 bytes (3 bytes) of BIS data. And a cluster is formed with data of all 496 frames.

- AUN as an address added to each cluster unit has an Address Field (hereinafter referred to as AF) structure shown in FIG. 13, and is included in the BIS data structure 720 bytes.

- AF5-AF8 1302 is added to the 4-byte AUN (AF0-AF3) 102 and 1-byte flagsbits (AF4) 1301 for storing various information. Configure the AF structure. Therefore, 16 AUNs are assigned to 32 sectors (32 PSNs) in the cluster structure.

- the address generation method for the two types of addresses assigned to each sector will be described using the address correlation diagram of the multilayer optical disk in FIG. For example, consider a case where addresses are assigned to layer numbers up to 8 layers and data having a data capacity of 64 gigabytes per layer. To assign a layer number of up to 8 layers and a data capacity of 64 gigabytes with PSN ⁇ ⁇ ⁇ ⁇ 101 allocated to one sector, all 28 bits are required, but since 32 bits are originally prepared as PSN, it is expressed in 27 bits It is not necessary to expand the address bits when the amount of data is larger than the amount of data to be processed, and it can be easily handled by shifting the allocation of the address bits indicating the layer number.

- PAA embedded in wobble PAAW ⁇ 1064

- PAAW ⁇ 104 PAA embedded in wobble

- PAAW ⁇ 1014 PAA embedded in wobble

- FIG. 1 by generating the address by embedding the virtual bits that are not recorded on the disc as information in other bits as it is not embedded in the wobble, and restoring the address at the time of detection, the address structure of the wobble is The periodicity can be maintained without change, and the address indicating the physical position can be expanded without increasing the number of bits of the address embedded in the wobble.

- scramble is used as an information embedding method, and examples (105 in FIG. 1, 105 in FIG. 4, 703 in FIG. 7 and FIG. 8) are used as scramble circuits.

- the present invention is not limited, and any circuit or method that can embed information and detect information using bit operations based on the presence or absence of scramble or a difference in scramble regularity can be similarly applied.

- scramble means one of arithmetic processing, and any processing that converts each bit of an address or regularity It is not limited to scramble.

- the encoding described in the fifth embodiment also means one of the arithmetic processes, and has been described using an example as an encoding circuit, but is not limited to this circuit, and each bit of the address is Any circuit or technique for embedding, associating, and converting information into other bits using regularity can be applied in the same manner and is not limited to encoding.

- the number of virtual bits, the position where the virtual bits are arranged, the bit position where information such as scramble information is embedded, and the bit configuration of the address are not limited to the present embodiment. However, it is better for the position where the virtual bit itself is arranged to change as an address considering the detection stability, and the bit position where information such as scramble information is embedded is changed as an address considering the detection time. More is better.

- the optical disk is used as a recording medium, and the address embedded in the wobble is used as the address.

- the present invention is not limited to this embodiment, and the address read from the generated address is not limited to this embodiment. If the idea of reducing bits so as to reduce the number of bits can be applied, the application can be similarly performed.

- the virtual bit is not embedded in the wobble, it may be stored in an area different from the read address area and used for address detection.

- Physical ADIP Address (PAAW), 1103 ... Scramble circuit, 1201 ... Optical disk, 1202 ... Pickup, 1203 ... Spindle motor, 1204 ... Address reproduction circuit, 1205 ... Data recording / reproduction circuit, 1206 ... Host, 1207 ... Microcomputer, 1301 ... flag bits, 1302 ... parities, 1501 ... AUX data, 1 801: Physical ADIP Address (PAA), 1802: Physical ADIP Address (PAAW), 1803: Encoding circuit.

- PAA Physical ADIP Address

- PAAW Physical ADIP Address

Landscapes

- Engineering & Computer Science (AREA)

- Signal Processing (AREA)

- Optical Recording Or Reproduction (AREA)

- Signal Processing For Digital Recording And Reproducing (AREA)

Abstract

Description

24ビットから1bitのアドレス拡張した場合の例を示す。また、アドレス拡張の仮想ビットであるPAA ビット24のビット情報は、PAAの下位2ビットに関連付けてウォブルに埋め込むものとする。従来のPAA 24ビット構成において、3ビットの層番号、19ビットのクラスタ番号、2ビットのクラスタ内カウント値として割り付けた場合、8層までの層番号と各層あたり32ギガバイト(64キロバイト×219)のデータ容量のデータに対してアドレスを割り当てることが出来る。しかし、各層あたり32ギガバイトを越える高密度な光ディスクの場合に、クラスタ番号を20ビットに拡張することで各層あたり64ギガバイト(64キロバイト×220)のデータ容量のデータに対してアドレスを割り付けることが出来るが、層番号のビットが2ビットに減ってしまうため5層以上のアドレス生成ができなくなってしまう。そこで、層番号として1ビット拡張し、従来と同等の3ビットにより8層までのアドレスを生成する。

Claims (6)

- 複数のデータを記録するクラスタを有する記録媒体において、

前記クラスタに同期してデータを記録するトラックにウォブリング重畳されて記録されているアドレスを有し、

前記アドレスは、該アドレスの一部に記録媒体に記録しないアドレス情報となる仮想ビットを有し、

前記仮想ビットを復元可能なようにエンコード処理された後のアドレスが記録されていることを特徴とする記録媒体。 - 複数のデータを記録するクラスタを有する記録媒体における記録方法であって、

前記クラスタに同期してデータを記録するトラックにウォブリング重畳されて記録されているアドレスを有し、

前記アドレスは、該アドレスの一部に記録媒体に記録しないアドレス情報となる仮想ビットを有し、

前記仮想ビットを復元可能なようにエンコード処理された後のアドレスが記録してある記録媒体にデータを記録する記録方法であって、

デコード処理により前記仮想ビットが復元された前記アドレスによりデータ位置を検出して記録することを特徴とする記録方法。 - 複数のデータを記録するクラスタを有する記録媒体における再生方法であって、

前記クラスタに同期してデータを記録するトラックにウォブリング重畳されて記録されているアドレスを有し、

前記アドレスは、該アドレスの一部に記録媒体に記録しないアドレス情報となる仮想ビットを有し、

前記仮想ビットを復元可能なようにエンコード処理された後のアドレスが記録してある記録媒体からデータを再生する再生方法であって、

デコード処理により前記仮想ビットが復元された前記アドレスによりデータ位置を検出して再生することを特徴とする再生方法。 - 複数のデータを記録するクラスタを有する記録媒体にデータを記録する記録方法であって、

前記クラスタに同期した、記録媒体の物理的な位置を示すアドレスは、

前記アドレスの一部に記録媒体に記録しないアドレス情報となる仮想ビットを有し、

前記仮想ビットを復元可能なようにエンコード処理された後のアドレスを、

データを記録するトラックにウォブリング重畳し、

記録媒体へ記録することを特徴とする記録方法。 - 複数のデータを記録するクラスタを有する記録媒体からデータを再生する再生装置において、

前記クラスタに同期してデータを記録するトラックにウォブリング重畳されて記録されているアドレスを有し、

前記アドレスは、該アドレスの一部に記録媒体に記録しないアドレス情報となる仮想ビットを有し、

前記仮想ビットを復元可能なようにエンコード処理された後のアドレスが記録してある記録媒体からデータを読み込む手段と、

ウォブルより検出されたアドレスから、デコード処理により仮想ビットを生成する手段と、

前記仮想ビットの生成結果より前記アドレスを検出する手段と、

検出した前記アドレスからデータ位置を検出する手段を具備することを特徴とする再生装置。 - 複数のデータを記録するエリアと前記データに対応して物理的な記録位置を示すアドレスを有する記録媒体において、

前記アドレスへのスクランブル有無や規則性を切り替えるための仮想ビットを前記アドレスの拡張ビットとして用い、

前記スクランブル後のアドレスが記録されていることを特徴とする記録媒体。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201080063235.5A CN102754156B (zh) | 2010-03-05 | 2010-11-10 | 再现和记录方法、再现和记录装置 |

| US13/577,359 US8588043B2 (en) | 2010-03-05 | 2010-11-10 | Recording medium, reproduction and recording method, reproduction and recording device |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010048580A JP5119286B2 (ja) | 2010-03-05 | 2010-03-05 | 記録媒体、再生及び記録方法、再生及び記録装置 |

| JP2010-048580 | 2010-03-05 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| WO2011108150A1 true WO2011108150A1 (ja) | 2011-09-09 |

Family

ID=44541826

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/JP2010/070020 WO2011108150A1 (ja) | 2010-03-05 | 2010-11-10 | 記録媒体、再生及び記録方法、再生及び記録装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8588043B2 (ja) |

| JP (1) | JP5119286B2 (ja) |

| CN (1) | CN102754156B (ja) |

| WO (1) | WO2011108150A1 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5011326B2 (ja) * | 2009-02-24 | 2012-08-29 | 株式会社日立製作所 | 情報記録媒体、アドレス生成及び検出方法、再生及び記録装置 |

| JP5119285B2 (ja) | 2010-03-05 | 2013-01-16 | 日立コンシューマエレクトロニクス株式会社 | 記録媒体、再生及び記録方法、再生及び記録装置 |

| JP5119284B2 (ja) | 2010-03-05 | 2013-01-16 | 日立コンシューマエレクトロニクス株式会社 | 記録媒体、再生及び記録方法、再生及び記録装置 |

| JP5119283B2 (ja) | 2010-03-05 | 2013-01-16 | 日立コンシューマエレクトロニクス株式会社 | 記録媒体、再生及び記録方法、再生及び記録装置 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2008060104A1 (en) * | 2006-11-17 | 2008-05-22 | Samsung Electronics Co, . Ltd. | Optical recording medium, apparatus and method of manufacturing optical recording medium, and apparatus and method of recording/reproducing data of optical recording medium |

| JP2008523534A (ja) * | 2004-12-08 | 2008-07-03 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 記録担体のアドレス空間を拡張する装置及び方法 |

| JP2010186507A (ja) * | 2009-02-12 | 2010-08-26 | Hitachi Ltd | 記録媒体、アドレス生成及び検出方法、再生及び記録装置 |

| JP2010198665A (ja) * | 2009-02-24 | 2010-09-09 | Hitachi Ltd | 情報記録媒体、アドレス生成及び検出方法、再生及び記録装置 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| MY126056A (en) * | 1999-09-29 | 2006-09-29 | Sony Corp | Data record medium, data recording and/or reproducing apparatus, and record medium determining method |

| JP2001243722A (ja) * | 2000-02-29 | 2001-09-07 | Sony Corp | ディスク記録媒体、及びディスクドライブ装置 |

| JP4576744B2 (ja) * | 2001-04-20 | 2010-11-10 | ソニー株式会社 | 記録媒体、及びその製造方法 |

| JP4300727B2 (ja) * | 2001-10-09 | 2009-07-22 | ソニー株式会社 | ディスク記録媒体、ディスクドライブ装置、再生方法、ディスク製造方法 |

| TWI359409B (en) | 2002-06-05 | 2012-03-01 | Lg Electronics Inc | High-density optical disc, method for recording an |

| RU2362217C2 (ru) * | 2002-08-22 | 2009-07-20 | Эл Джи Электроникс Инк. | Оптический диск с высокой плотностью записи и способ записи/считывания для него |

| JP2008523533A (ja) * | 2004-12-07 | 2008-07-03 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | ヘッド位置を用いたディスク記憶空間アドレス指定 |

| JP2006269077A (ja) * | 2006-06-05 | 2006-10-05 | Hitachi Ltd | 光情報記録媒体 |

| JP5018804B2 (ja) * | 2009-02-24 | 2012-09-05 | 株式会社日立製作所 | アドレス生成及び検出方法、再生及び記録装置 |

| JP5119284B2 (ja) | 2010-03-05 | 2013-01-16 | 日立コンシューマエレクトロニクス株式会社 | 記録媒体、再生及び記録方法、再生及び記録装置 |

| JP5119285B2 (ja) | 2010-03-05 | 2013-01-16 | 日立コンシューマエレクトロニクス株式会社 | 記録媒体、再生及び記録方法、再生及び記録装置 |

| JP5119283B2 (ja) | 2010-03-05 | 2013-01-16 | 日立コンシューマエレクトロニクス株式会社 | 記録媒体、再生及び記録方法、再生及び記録装置 |

-

2010

- 2010-03-05 JP JP2010048580A patent/JP5119286B2/ja active Active

- 2010-11-10 WO PCT/JP2010/070020 patent/WO2011108150A1/ja active Application Filing

- 2010-11-10 US US13/577,359 patent/US8588043B2/en not_active Expired - Fee Related

- 2010-11-10 CN CN201080063235.5A patent/CN102754156B/zh not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008523534A (ja) * | 2004-12-08 | 2008-07-03 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 記録担体のアドレス空間を拡張する装置及び方法 |

| WO2008060104A1 (en) * | 2006-11-17 | 2008-05-22 | Samsung Electronics Co, . Ltd. | Optical recording medium, apparatus and method of manufacturing optical recording medium, and apparatus and method of recording/reproducing data of optical recording medium |

| JP2010186507A (ja) * | 2009-02-12 | 2010-08-26 | Hitachi Ltd | 記録媒体、アドレス生成及び検出方法、再生及び記録装置 |

| JP2010198665A (ja) * | 2009-02-24 | 2010-09-09 | Hitachi Ltd | 情報記録媒体、アドレス生成及び検出方法、再生及び記録装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102754156B (zh) | 2014-04-30 |

| US20120307608A1 (en) | 2012-12-06 |

| JP2011187098A (ja) | 2011-09-22 |

| CN102754156A (zh) | 2012-10-24 |

| JP5119286B2 (ja) | 2013-01-16 |

| US8588043B2 (en) | 2013-11-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7881177B2 (en) | Recording medium, method and apparatus for reproducing data on the recording medium, and method and apparatus for recording data on the recording medium | |

| JP5119283B2 (ja) | 記録媒体、再生及び記録方法、再生及び記録装置 | |

| JP5119285B2 (ja) | 記録媒体、再生及び記録方法、再生及び記録装置 | |

| EP2219189B1 (en) | Address generating and detection method | |

| JP5018804B2 (ja) | アドレス生成及び検出方法、再生及び記録装置 | |

| JP5119284B2 (ja) | 記録媒体、再生及び記録方法、再生及び記録装置 | |

| JP5119286B2 (ja) | 記録媒体、再生及び記録方法、再生及び記録装置 | |

| JP5011326B2 (ja) | 情報記録媒体、アドレス生成及び検出方法、再生及び記録装置 | |

| JP2013051022A (ja) | 記録媒体、再生及び記録方法、再生及び記録装置 | |

| JP5544389B2 (ja) | アドレス生成及び検出方法、再生及び記録装置 | |

| JP2012256420A (ja) | 記録媒体、アドレス生成及び検出方法、再生及び記録装置 | |

| JP2012212501A (ja) | 情報記録媒体、アドレス生成及び検出方法、再生及び記録装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| WWE | Wipo information: entry into national phase |

Ref document number: 201080063235.5 Country of ref document: CN |

|

| 121 | Ep: the epo has been informed by wipo that ep was designated in this application |

Ref document number: 10847047 Country of ref document: EP Kind code of ref document: A1 |

|

| WWE | Wipo information: entry into national phase |

Ref document number: 13577359 Country of ref document: US |

|

| NENP | Non-entry into the national phase |

Ref country code: DE |

|

| 122 | Ep: pct application non-entry in european phase |

Ref document number: 10847047 Country of ref document: EP Kind code of ref document: A1 |