US20070077763A1 - Deposition technique to planarize a multi-layer structure - Google Patents

Deposition technique to planarize a multi-layer structure Download PDFInfo

- Publication number

- US20070077763A1 US20070077763A1 US11/240,707 US24070705A US2007077763A1 US 20070077763 A1 US20070077763 A1 US 20070077763A1 US 24070705 A US24070705 A US 24070705A US 2007077763 A1 US2007077763 A1 US 2007077763A1

- Authority

- US

- United States

- Prior art keywords

- layer

- recited

- substrate

- rotational movement

- flowable

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

- 238000000151 deposition Methods 0.000 title claims abstract description 8

- 239000000463 material Substances 0.000 claims abstract description 54

- 238000000034 method Methods 0.000 claims abstract description 54

- 239000000758 substrate Substances 0.000 claims abstract description 53

- 230000009969 flowable effect Effects 0.000 claims abstract description 30

- 239000011248 coating agent Substances 0.000 claims abstract description 11

- 238000000576 coating method Methods 0.000 claims abstract description 11

- 239000002904 solvent Substances 0.000 claims description 27

- 239000000203 mixture Substances 0.000 claims description 24

- 238000004528 spin coating Methods 0.000 claims description 14

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 7

- 229910052710 silicon Inorganic materials 0.000 claims description 7

- 239000010703 silicon Substances 0.000 claims description 7

- 230000007480 spreading Effects 0.000 claims description 2

- 238000003892 spreading Methods 0.000 claims description 2

- 238000009499 grossing Methods 0.000 description 55

- 239000013590 bulk material Substances 0.000 description 35

- 239000007789 gas Substances 0.000 description 16

- 230000008569 process Effects 0.000 description 16

- 238000005530 etching Methods 0.000 description 8

- 239000000126 substance Substances 0.000 description 8

- PSGCQDPCAWOCSH-UHFFFAOYSA-N (4,7,7-trimethyl-3-bicyclo[2.2.1]heptanyl) prop-2-enoate Chemical compound C1CC2(C)C(OC(=O)C=C)CC1C2(C)C PSGCQDPCAWOCSH-UHFFFAOYSA-N 0.000 description 7

- LNMQRPPRQDGUDR-UHFFFAOYSA-N hexyl prop-2-enoate Chemical compound CCCCCCOC(=O)C=C LNMQRPPRQDGUDR-UHFFFAOYSA-N 0.000 description 7

- NJPPVKZQTLUDBO-UHFFFAOYSA-N novaluron Chemical compound C1=C(Cl)C(OC(F)(F)C(OC(F)(F)F)F)=CC=C1NC(=O)NC(=O)C1=C(F)C=CC=C1F NJPPVKZQTLUDBO-UHFFFAOYSA-N 0.000 description 7

- 239000004593 Epoxy Substances 0.000 description 5

- 229920002120 photoresistant polymer Polymers 0.000 description 5

- 238000012545 processing Methods 0.000 description 5

- -1 Polysiloxane Polymers 0.000 description 4

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 4

- 230000008901 benefit Effects 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- 238000004132 cross linking Methods 0.000 description 4

- 239000001301 oxygen Substances 0.000 description 4

- 229910052760 oxygen Inorganic materials 0.000 description 4

- 238000006116 polymerization reaction Methods 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- XSTXAVWGXDQKEL-UHFFFAOYSA-N Trichloroethylene Chemical compound ClC=C(Cl)Cl XSTXAVWGXDQKEL-UHFFFAOYSA-N 0.000 description 3

- KUDUQBURMYMBIJ-UHFFFAOYSA-N ethylene glycol diacrylate Substances C=CC(=O)OCCOC(=O)C=C KUDUQBURMYMBIJ-UHFFFAOYSA-N 0.000 description 3

- CATSNJVOTSVZJV-UHFFFAOYSA-N heptan-2-one Chemical compound CCCCCC(C)=O CATSNJVOTSVZJV-UHFFFAOYSA-N 0.000 description 3

- 239000003999 initiator Substances 0.000 description 3

- 238000001459 lithography Methods 0.000 description 3

- 238000000059 patterning Methods 0.000 description 3

- 229920001296 polysiloxane Polymers 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 238000012876 topography Methods 0.000 description 3

- LBLYYCQCTBFVLH-UHFFFAOYSA-N 2-Methylbenzenesulfonic acid Chemical compound CC1=CC=CC=C1S(O)(=O)=O LBLYYCQCTBFVLH-UHFFFAOYSA-N 0.000 description 2

- XMLYCEVDHLAQEL-UHFFFAOYSA-N 2-hydroxy-2-methyl-1-phenylpropan-1-one Chemical compound CC(C)(O)C(=O)C1=CC=CC=C1 XMLYCEVDHLAQEL-UHFFFAOYSA-N 0.000 description 2

- BNCADMBVWNPPIZ-UHFFFAOYSA-N 2-n,2-n,4-n,4-n,6-n,6-n-hexakis(methoxymethyl)-1,3,5-triazine-2,4,6-triamine Chemical compound COCN(COC)C1=NC(N(COC)COC)=NC(N(COC)COC)=N1 BNCADMBVWNPPIZ-UHFFFAOYSA-N 0.000 description 2

- YXALYBMHAYZKAP-UHFFFAOYSA-N 7-oxabicyclo[4.1.0]heptan-4-ylmethyl 7-oxabicyclo[4.1.0]heptane-4-carboxylate Chemical compound C1CC2OC2CC1C(=O)OCC1CC2OC2CC1 YXALYBMHAYZKAP-UHFFFAOYSA-N 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- 239000003054 catalyst Substances 0.000 description 2

- 230000001419 dependent effect Effects 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 238000011066 ex-situ storage Methods 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 238000011065 in-situ storage Methods 0.000 description 2

- 238000012544 monitoring process Methods 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- 238000009987 spinning Methods 0.000 description 2

- 239000004094 surface-active agent Substances 0.000 description 2

- JTXMVXSTHSMVQF-UHFFFAOYSA-N 2-acetyloxyethyl acetate Chemical compound CC(=O)OCCOC(C)=O JTXMVXSTHSMVQF-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-M Acrylate Chemical compound [O-]C(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-M 0.000 description 1

- OHCFUWWIDZFTBK-UHFFFAOYSA-K C1=CC=C(SC2=CC([SH](C3=CC=CC=C3)C3=CC=CC=C3)=CC=C2)C=C1.C1=CC=C([S+](C2=CC=CC=C2)C2=CC=CC(SC3=CC=CC([S+](C4=CC=CC=C4)C4=CC=CC=C4)=C3)=C2)C=C1.FP(F)(F)(F)F.FP(F)(F)(F)F.FP(F)(F)(F)F.[F-].[F-].[F-] Chemical compound C1=CC=C(SC2=CC([SH](C3=CC=CC=C3)C3=CC=CC=C3)=CC=C2)C=C1.C1=CC=C([S+](C2=CC=CC=C2)C2=CC=CC(SC3=CC=CC([S+](C4=CC=CC=C4)C4=CC=CC=C4)=C3)=C2)C=C1.FP(F)(F)(F)F.FP(F)(F)(F)F.FP(F)(F)(F)F.[F-].[F-].[F-] OHCFUWWIDZFTBK-UHFFFAOYSA-K 0.000 description 1

- BAVIDSCVXNQEBA-UHFFFAOYSA-N C=CC(=O)OOC(=O)C=C Chemical compound C=CC(=O)OOC(=O)C=C BAVIDSCVXNQEBA-UHFFFAOYSA-N 0.000 description 1

- 229920003270 Cymel® Polymers 0.000 description 1

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 229920006243 acrylic copolymer Polymers 0.000 description 1

- 239000012080 ambient air Substances 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 239000006117 anti-reflective coating Substances 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 239000012952 cationic photoinitiator Substances 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 239000002826 coolant Substances 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 239000003431 cross linking reagent Substances 0.000 description 1

- 230000002939 deleterious effect Effects 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000000572 ellipsometry Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000012530 fluid Substances 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 239000007791 liquid phase Substances 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- JDSHMPZPIAZGSV-UHFFFAOYSA-N melamine Chemical compound NC1=NC(N)=NC(N)=N1 JDSHMPZPIAZGSV-UHFFFAOYSA-N 0.000 description 1

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 1

- 229910052753 mercury Inorganic materials 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- RUOJZAUFBMNUDX-UHFFFAOYSA-N propylene carbonate Chemical compound CC1COC(=O)O1 RUOJZAUFBMNUDX-UHFFFAOYSA-N 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 239000010421 standard material Substances 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/31051—Planarisation of the insulating layers

- H01L21/31053—Planarisation of the insulating layers involving a dielectric removal step

- H01L21/31055—Planarisation of the insulating layers involving a dielectric removal step the removal being a chemical etching step, e.g. dry etching

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y40/00—Manufacture or treatment of nanostructures

-

- C—CHEMISTRY; METALLURGY

- C09—DYES; PAINTS; POLISHES; NATURAL RESINS; ADHESIVES; COMPOSITIONS NOT OTHERWISE PROVIDED FOR; APPLICATIONS OF MATERIALS NOT OTHERWISE PROVIDED FOR

- C09D—COATING COMPOSITIONS, e.g. PAINTS, VARNISHES OR LACQUERS; FILLING PASTES; CHEMICAL PAINT OR INK REMOVERS; INKS; CORRECTING FLUIDS; WOODSTAINS; PASTES OR SOLIDS FOR COLOURING OR PRINTING; USE OF MATERIALS THEREFOR

- C09D183/00—Coating compositions based on macromolecular compounds obtained by reactions forming in the main chain of the macromolecule a linkage containing silicon, with or without sulfur, nitrogen, oxygen, or carbon only; Coating compositions based on derivatives of such polymers

- C09D183/04—Polysiloxanes

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/004—Photosensitive materials

- G03F7/09—Photosensitive materials characterised by structural details, e.g. supports, auxiliary layers

- G03F7/094—Multilayer resist systems, e.g. planarising layers

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/16—Coating processes; Apparatus therefor

- G03F7/162—Coating on a rotating support, e.g. using a whirler or a spinner

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02126—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material containing Si, O, and at least one of H, N, C, F, or other non-metal elements, e.g. SiOC, SiOC:H or SiONC

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02205—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition

- H01L21/02208—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si

- H01L21/02214—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si the compound comprising silicon and oxygen

- H01L21/02216—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si the compound comprising silicon and oxygen the compound being a molecule comprising at least one silicon-oxygen bond and the compound having hydrogen or an organic group attached to the silicon or oxygen, e.g. a siloxane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02282—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process liquid deposition, e.g. spin-coating, sol-gel techniques, spray coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/312—Organic layers, e.g. photoresist

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/312—Organic layers, e.g. photoresist

- H01L21/3121—Layers comprising organo-silicon compounds

- H01L21/3122—Layers comprising organo-silicon compounds layers comprising polysiloxane compounds

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/0002—Lithographic processes using patterning methods other than those involving the exposure to radiation, e.g. by stamping

Definitions

- This invention relates to spin-on coating of substrates. Specifically, the present invention is directed to a method to coat a substrate employing spin-on techniques in furtherance of lithographic patterning.

- Spin-coating is a well known technique employed to form a layer of material upon a substrate. Often the material is deposited upon a surface having anisotropic topography in furtherance of producing a film having a planar surface disposed opposite to the substrate surface.

- the planarity of the material surface is highly desirable for several processes, e.g., deposition of resist material in furtherance of patterning.

- studies have been undertaken to understand the behavior of films formed during spin-coating. Peurrung and Graves in Film Thickness Profiles over Topography in Spin Coating , Journal of the Electrochemical Society, Vol. 138 No. 7 (1991), set forth a theoretical analysis of spin-coating wet films over anisotropic surfaces. Peurrung and Graves conclude that the presence of anisotropicity of the substrate surface makes problematic production of a planar material surface. Many attempts have been undertaken to obtain a planar material surface from material spin-coated on an anisotropic surface.

- U.S. Pat. No. 4,038,110 discloses a technique to planarize an anisotropic substrate surface involves forming a photoresist pattern in registration that with a pattern of unelevated areas present on the substrate.

- the photoresist pattern has narrower lateral dimensions than an elevated pattern whereby registration is facilitated.

- the photoresist pattern is flowed to laterally expand the photoresist and mask the unelevated areas.

- one manner in which to overcome the drawbacks with multi-layer resists involve spreading a resin material over an anisotropic surface employing a dual spin cycle.

- the resin material is spread at a speed of approximately of not less than 4000 revolutions per minute (rpm), preferably from 6000 to 8000 rpm, until build-up of the coating is detectable on a side wall of a topographical feature facing the centrifugal center of the spinning substrate.

- the spin speed is immediately reduced to less than 4000 rpm, preferably from about 1000 to 3500 rpm, and spinning is continued for a time sufficient to dry the coating.

- U.S. Pat. No. 4,794,021 discloses a method of forming a planarized layer on a substrate by spin coating a polymer over the substrate. Before the layer dries the substrate is heated in a pressure-controlled environment to control solvent loss while maintaining the polymer in a liquid-state. After a predetermined interval of time, the substrate is cured in a standard convention bake oven.

- U.S. Pat. No. 5,736,424 discloses a method that includes contacting a material having a predetermined viscosity with an object having a flat surface.

- the material has a viscosity less than 1000 cp, and a flat surface is placed into contact with the material in such a manner that the material is planarized to a desired degree.

- the material is cured while in contact with the flat surface.

- the object is then separated from the material.

- the planarity of the planarizing material is then transferred into the underlying layer using conventional techniques.

- U.S. Pat. No. 5,893,750 discloses a method of forming a planarized interlevel dielectric layer over interconnects formed upon a frontside surface of an upper topography of a silicon wafer.

- An anisotropic silicon dioxide (oxide) layer is first deposited over the interconnects.

- a spin-on glass (SOG) layer is then formed over the anisotropic oxide layer.

- the liquid SOG material flows over the upper surface, filling narrow spaces without creating voids and producing a surface smoothing effect at isolated vertical edges.

- a chemical-mechanical polishing (CMP) process is applied to the frontside surface.

- the CMP process increases the planarity of the frontside surface by reducing surface heights of elevated features more so than surface heights in recessed areas.

- the present invention is directed to a method of coating a substrate having a solidified layer formed thereon, that features depositing a flowable material upon the solidified layer and forming an additional layer having a smooth flowable surface upon the substrate by imparting rotational movement upon the substrate followed by leveling of the flowable material in an absence of the rotational movement. After the additional layer is formed, the same is solidified.

- FIG. 1 is a cross-sectional view of a substrate having an anisotropic surface that is to be planarized in accordance with the present invention

- FIG. 2 is a cross-sectional view of the substrate shown in FIG. 1 having a planarized surface, in accordance with the present invention

- FIG. 3 is a cross-sectional view of the substrate shown in FIG. 1 having a semi-conformal layer deposited therein;

- FIG. 4 is a detailed cross-sectional view of a region of the substrate shown in FIG. 3 ;

- FIG. 5 is a cross-sectional view of the substrate shown in FIG. 4 having a smoothing layer deposited thereon;

- FIG. 6 is a cross-sectional view of a prior art etching chamber

- FIG. 7 is a cross-sectional view of substrate shown in FIG. 5 after being etched employing first etch conditions in accordance with the present invention

- FIG. 8 is a cross-sectional view of substrate shown in FIG. 7 after being etched employing second etch conditions in accordance with the present invention

- the anisotropic surface may include spaced-apart projections 14 and 16 , defining spaced-apart recessions 18 , which may result from any known previous patterning process.

- Projections 14 may be metal lines, photoresist, monocrystalline silicon and the like.

- substrate 10 is discussed as including a wafer 20 formed from standard materials, e.g., mono-crystalline silicon.

- Present upon wafer 20 is a patterned layer 22 in which projections 14 and 16 are formed.

- patterned layer 22 is formed from a solidified polymeric material employing imprint lithography techniques, with a primer layer 23 being disposed between patterned layer and wafer 20 .

- Primer layer 23 is typically formed from spin-coating a layer of DUV30J-16.

- DUV30J-16 is a bottom anti-reflective coating, BARC, available from Brewer Science in Rolla, Mo.

- An exemplary bulk material from which to form patterned layer 22 is as follows:

- the acrylate component isobornyl acrylate (IBOA)

- IBOA has the following structure: and comprises approximately 47% of bulk material by weight, but may be present in a range of 20% to 80%, inclusive.

- the mechanical properties of patterned layer 22 are primarily attributable to IBOA.

- An exemplary source for IBOA is Sartomer Company, Inc. of Exton, Pa. available under the product name SR 506.

- n-hexyl acrylate has the following structure: and comprises approximately 25% of bulk material by weight, but may be present in a range of 0% to 50%, inclusive. Also providing flexibility to patterned layer 22 , n-HA is employed to reduce the viscosity of the prior art bulk material so that bulk material, in the liquid phase, has a viscosity in a range of 2-9 Centipoises, inclusive.

- An exemplary source for the n-HA component is the Aldrich Chemical Company of Milwaukee, Wis.

- a cross-linking component ethylene glycol diacrylate, has the following structure: and comprises approximately 25% of bulk material by weight, and may be present in a range of 10% to 50%, inclusive.

- EGDA also contributes to the modulus and stiffness buildup, as well as facilitates cross-linking of n-HA and IBOA during polymerization of the bulk material.

- An initiator component 2-hydroxy-2-methyl-1-phenyl-propan-1-one is available from Ciba Specialty Chemicals of Tarrytown, N.Y. under the tradename DAROCUR® 1173, and has the following structure: and comprises approximately 3% of the bulk material by weight, and may be present in a range of 1% to 5%, inclusive.

- the actinic energy to which the initiator is responsive is broadband ultra-violet energy generated by a medium-pressure mercury lamp. In this manner, the initiator facilitates cross-linking and polymerization of the components of the bulk material.

- the component FS-2000 is a surfactant that provides preferential adhesion and release upon polymerization of the bulk material. FS-2000 is sold by Mason Chemical Company of Arlington Heights, Ill.

- MASURF® FS-2000 under the product name MASURF® FS-2000 and comprises approximately 2% of the bulk material by weight, and may be present in a range of 0.1% to 5%, inclusive.

- An exemplary imprint lithography technique to deposit patterned layer 22 is disclosed in co-pending U.S. patent application Ser. No. 11/068,171, filed Feb. 28, 2005, entitled “Composition to Reduce Adhesion Between a Conformable Region and a Mold,” having Frank Xu and Michael N. Miller listed as inventors, which is incorporated by reference herein.

- semi-conformal layer 29 is formed from a silicon-containing polyermizable material employing a Brewer Science Model CEE® 4000 spin-coating system.

- the polymerizable material is centrally disposed on substrate 10 before rotation occurs. After dispensing of the polymerizable material, substrate 10 is accelerated 3,000 revolutions per minute (rpm) per second to reach a maximum rotational velocity of approximately 1000 rpm.

- the maximum rotational velocity is maintained until substantially all of the solvent in the polymerizable material has been removed. This is detected optically by the unaided eye as the color of semi-conformal layer 29 remaining substantially unchanged during rotation of substrate 10 .

- substrate 10 is placed upon a heating device (not shown), such as a hot plate, to raise the temperature thereof, by conductive heating, to approximately 180° C. for 60 seconds.

- An exemplary bulk material to include in the semi-conformal composition to form semi-conformal layer 29 is as follows:

- the hydroxyl-functional polysiloxane component is present in SEMI-CONFORMAL BULK MATERIAL in amounts of approximately 80% by weight of SEMI-CONFORMAL BULK MATERIAL, but may be present in a range of 40 to 95%, inclusive by weight, depending on the thicknesses desired for semi-conformal layer 29 .

- An exemplary hydroxyl-functional polysiloxane component used in the present invention is a silicon T-resin intermediate available from Dow Corning® (Midland, Mich.) under the tradename Z-6018.

- HMMM hexamethoxymethylmelamine

- SEMI-CONFORMAL BULK MATERIAL a cross-linking agent component is present in SEMI-CONFORMAL BULK MATERIAL in amounts of approximately 19% by weight of SEMI-CONFORMAL BULK MATERIAL, but may be present in a range of 10 to 30%, inclusive by weight.

- An exemplary HMMM component is available from Cytec Industries, Inc. (West Paterson, N.J.) under the tradename CYMEL 303ULF.

- the toluenesulfonic acid component is a catalyst present in the SEMI-CONFORMAL LAYER BULK MATERIAL in an amount of component is present in SEMI-CONFORMAL BULK MATERIAL in amounts of approximately 1% by weight of SEMI-CONFORMAL BULK MATERIAL, but may be present in a range of 1 to 2%, inclusive by weight.

- An exemplary catalyst is available from Cytec Industries, Inc. (West Paterson, N.J.) under the tradename CYCAT 4040.

- the SEMI-CONFORMAL LAYER BULK MATERIAL is employed with a solvent to form the semi-conformal composition employed to form semi-conformal layer 29 .

- the solvent may be present in the semi-conformal composition in amounts of approximately 60% to 98% by weight, dependent upon the desired thicknesses of semi-conformal layer 29 , with the remaining portions of the semi-conformal composition being the SEMI-CONFORMAL LAYER BULK MATERIAL 58 .

- An example of a solvent used in the present invention is methyl amyl ketone available from Aldrich Co. (St. Louis, Mo.) under the tradename MAK.

- the anisotropy of surface of substrate 10 causes thickness variations in semi-conformal layer 29 that present as troughs 32 and hills 34 . It was observed that regions of a surface 30 of semi-conformal layer 29 in superimposition with projection 16 and recession 18 had a substantially smooth, if not planar surface, because projection 16 has small lateral dimension, w 1 . This results in a thickness t 1 , of semi-conformal layer 29 , measured between surface 30 and apex surface 26 of projection 16, being substantially equal to thickness t 2 -h 1 , with h 1 being the height of projection 16 .

- projections such as projection 16 , having a width, w 1 , of several microns or less, which is smaller than width, w 2 , of recession 18 .

- Projections, such as projection 14 having a width, w 3 , which is tens of microns or larger, were observed to produce hills, such as hill 34 .

- Hill 34 is defined by a region of semi-conformal layer 29 having a varying thickness measured with respect to apex surface 24 of projection 14 and surface 30 .

- the maximum thickness, t 3 of the region of semi-conformal layer 29 in superimposition with projection 14 , is approximately equal to thickness t 2 .

- the portion of surface 30 associated with the maximum thickness of hill 34 is spaced-apart from a plane P 1 in which the remaining regions of surface 30 lie, a distance d 1 .

- d 1 is approximately equal to height, h 2 , of projection 14 .

- smoothing layer 40 functions to further reduce non-planarity perturbations in surface 30 due, for example, to troughs 32 and hills 34 .

- smoothing layer 40 is typically disposed on surface 30 employing spin-on techniques to minimize the time required to form the same.

- the material from which smoothing layer 40 is formed includes a solvent. It is desired to form smoothing layer 40 from a material that maintains a fluidic state after spin-on coating has effectively removed substantially all of the solvent present therein.

- a ratio of centrifugal force (F c ) to capillary force (F p ) is proportional to the cubic of feature lateral dimension, (w) that may be expressed as follows: F c /F p ⁇ W 3 1 )

- the material from which smoothing layer 40 is formed maintains a fluidic state after spin-on coating has effectively removed substantially all of the solvent present therein.

- An exemplary bulk material from which to form smoothing layer 40 is as follows:

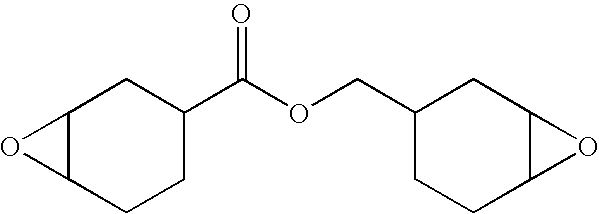

- the cycloaliphatic epoxy component has the following structure:

- the cycloaliphatic epoxy component comprises approximately 87% of bulk material by weight.

- the mechanical properties of smoothing layer 40 are primarily attributable to the cycloaliphatic epoxy component.

- An exemplary source of the cycloaliphatic epoxy component is sold by Dow Chemical Company of Midland, Mich. as chemical name 3,4-epoxycyclohexylmethyl-3,4-epoxycyclohexane carboxylate and sold under the tradename ERL-4221LV.

- the ⁇ -caprolactone triol component comprises approximately 10% of the bulk material by weight. This component increased the catioinic curing speed of SMOOTHING LAYER BULK MATERIAL 1.

- An exemplary source of the ⁇ -caprolactone triol component is sold by Dow Chemical Company of Midland, Mich. under the tradename Tone 0301.

- the photoinitiator component comprises approximately 3% of the bulk material by weight and facilitates cross-linking and polymerization of the remaining components of bulk material in response to actinic energy.

- An exemplary photoinitiator is a cationic photoinitiator comprising a mixture of triarylsulfonium hexafluorophosphate salts in a propylene carbonate.

- An exemplary source of the photoinitiator component has the following structure: and is sold by Dow Chemical Company of Midland, Mich. under the tradename UVI 6992.

- the fluorosurfactant component is a nonionic fluorinated acrylic copolymer based surfactant that comprises less than 1% of the bulk material by weight.

- An exemplary fluorosurfactant is available from Dainippon Ink & Chemical of Japan under the tradename MegaFaceTM R-08.

- the SMOOTHING LAYER BULK MATERIAL is employed with a solvent to form a smoothing composition employed to form smoothing layer 40 .

- the solvent may be present in the smoothing composition in amounts of approximately 20% to 98% by weight, dependent upon the desired thicknesses of smoothing layer 40 , with the remaining portions of the semi-conformal composition being the SMOOTHING LAYER BULK MATERIAL.

- An example of a solvent used in the present invention is methyl amyl ketone available from Aldrich Co. (St. Louis, Mo.) under the tradename MAK.

- Surface 30 is coated with the smoothing composition by spin-on techniques employing a Brewer Science Model CEE® 4000 spin-coating system to form smoothing layer 40 .

- the smoothing composition is centrally disposed on surface 30 before rotation occurs.

- substrate 10 is accelerated 5,000 revolutions per minute (rpm)/s to reach a maximum rotational velocity of approximately 4000 rpm.

- the maximum rotational velocity is maintained until substantially all of the solvent in the polymerizable composition has been removed. This is detected optically by the unaided eye as the color of semi-conformal layer 29 remaining substantially unchanged during rotation of substrate 10 . Thereafter, rotation of substrate 10 is ceased and leveling of smoothing surface 44 is allowed to occur in the absence of movement of substrate 10 .

- leveling occurs for 2-30 minutes and at ambient atmospheric conditions, i.e. ambient temperatures and pressures.

- ambient temperatures and pressures are 25° Celsius and 760 Torr, respectively.

- smoothing layer is exposed to broadband ultraviolet energy for approximately 120 seconds with a lamp intensity of 20 mW/cm 2 to polymerize and cross-link the smoothing composition. This is typically achieved employing a light source sold by OAI of San Jose, Calif. as Model 30 LS that may produce an 8 inch uniform beam.

- Hill 34 causes regions 46 of smoothing surface 44 to have a varying thickness measured with respect to surface 30 .

- the thickness, t 4 differs from a thickness, t 5 , of regions 48 of smoothing layer 40 outside of region 46 . This results in the portion of surface 44 associated with the maximum thickness of region 46 being spaced-apart from a plane, P 2 , in which the remaining regions of surface 46 lie, a distance d 2 .

- the bulk material from which smoothing layer 40 is fabricated facilitates, for a given deposition process, to ensure that thickness, t 4 , is less than thickness, t 5 ; hence, d 1 is greater than d 2 . This effectively reduces the thickness offset between exposed surfaces, in this case smoothing surface 44 and both, nadir surface 19 of recession 18 , and apex surface 24 .

- smoothing layer 40 and semi-conformal layer 29 have substantially similar etch characteristics, e.g., etch rate, for a given etch recipe, or groups of etch recipes

- the presence of smoothing layer 40 reduces the magnitude of over-etch to which the projection 16 is subject to when exposing apex surface 24 .

- the reduction would be the absolute value of the difference between d 1 and d 2 .

- height h 2 is 100 nanometers (nm)

- d 1 would be approximately 100 nm.

- d 2 is approximately 60 nm.

- DOP degree of planarization

- planarization benefit may be obtained by taking advantage of etch rate differential provided by differing etch recipes. For example, assuming that semi-conformal layer 29 had an etch rate, for a given etch recipe, that was 20% faster than the associated etch rate of smoothing layer 40 , it may be seen that the reduction in height, h 1 , may be further reduced increased by 12 nm, i.e., height h 1 of projection 16 is approximately 72 nm upon exposure of the entire area of surface 34 . This may be desirable. Conversely, were the etch rate associated with semi-conformal layer 29 , for a given etch recipe, 20% slower that the associated etch rate of smoothing layer 40 , the planarization benefits of smoothing layer may be reduced. The height, h 1 , of projection 16 would be reduced by 12 nm so that h 1 would be reduced to 48 nm upon exposure of the entire surface 34 .

- an etching system such as a magnetically-enhanced reactive ion etching (MERIE) reactor 50 is employed.

- Reactor 50 includes grounded walls 52 defining a chamber 54 and slit valve opening 56 allowing ingress to and egress from chamber 54 .

- Cathode pedestal 58 may include channels (not shown) through which coolant fluid (not shown), flows to facilitate control of the temperature of the chuck.

- An RF power supply 62 is in electrical communication with cathode pedestal 58 to facilitate control of the DC bias to chuck 40 and generation of a plasma within chamber 54 .

- a vacuum pump system 66 pumps the chamber 54 through an adjustable throttle valve 68 .

- Processing gases are supplied from gas sources 75 - 82 through respective mass flow controllers 83 - 90 to a quartz gas distribution plate 92 positioned opposite to chuck 60 .

- the distribution plate 92 includes a manifold 94 receiving the processing gas and communicating with chamber 54 through a showerhead having a large number of distributed apertures 96 so as to inject a more uniform flow of processing gas into chamber 54 .

- pump 66 is operated to establish a pressure in chamber 54 that is approximately 30 milliTorr (mT).

- Mass flow controllers 84 and 85 are operated to establish a flow rate from supplies 76 and 77 , respectively.

- supply 76 provides a flow of CF 4 gas into chamber 54 at approximately 90 standard cubic centimeters per minute (sccm).

- Supply 77 provides a flow of oxygen, O 2 , gas into processing region at approximately 10 sccm.

- Power supply 62 is operated at 300 Watts.

- This configuration results in semi-conformal layer 29 and smoothing layer 40 etching at substantially the same rates, e.g., semi-conformal layer 29 etches at approximately 161.3 nm/minute ⁇ 10 nm/minute, and smoothing layer 40 etches at approximately 167.4 nm/minute ⁇ 10 nm/minute. It is desired to minimize the time required to complete etching, i.e., to expose surfaces 32 and 34 .

- a sequential etch process is employed to maximize the etch rate of materials being etched while minimizing the etch rate differential among materials undergoing etch.

- the sequential etch process includes a first etch condition that minimizes the time required to remove portions of smoothing layer 40 .

- pump 66 operates to establish a pressure in chamber 54 that is approximately 40 mT.

- Mass flow controllers 83 , 85 and 87 are operated to establish a flow rate from supplies 75 , 77 and 79 , respectively.

- supply 75 provides a flow of C 2 H 4 gas into chamber 54 at approximately 40 sccm

- supply 77 provides a flow of oxygen, O 2 , gas into chamber 54 at approximately 100 sccm.

- Supply 79 provides a flow of nitrogen, N 2 , gas into chamber 54 at approximately 200 sccm.

- Supply 62 is operated at 500 Watts.

- Formation of semi-planar surface 65 may be determined from a priori knowledge in which the time required to expose the same is known and the process conditions are terminated after the required time had lapsed.

- a process conditions monitoring system 96 may be in communication with chamber 54 which is configured to measure performance of the etch process, e.g., measure an etch rate, an etch selectivity, an etch uniformity, feature profile angle, and critical dimension.

- System 96 may be an in-situ or ex-situ device.

- system 96 includes a scatterometer (not shown), incorporating beam profile ellipsometry and beam profile reflectometry.

- the scatterometer (not shown) may be positioned within a transfer chamber (not shown).

- system 96 includes a scanning electron microscope (not shown).

- controller 98 Operation of reactor 50 is achieved by a controller 98 in data communication therewith to control the operations of the systems associated with reactor 50 .

- controller 98 is in data communication with RF supply 62 , pump 66 , throttle valve 68 , mass flow controllers 83 - 90 , supplies 75 - 82 and process condition monitoring system 96 .

- Controller 102 includes a microprocessor (not shown), memory (not shown), and a digital i/0 port (not shown) that is capable of generating control voltages sufficient to communicate with reactor 50 .

- a program stored in the memory (not shown) and selectively operated on by microprocessor controls the operation of reactor 50 .

- the processing conditions in chamber 54 are established so that semi-conformal layer 29 and the remaining portions of smoothing layer 40 are etched at substantially the same rate.

- the chamber pressure is approximately 30 mT

- power supply 62 is operated at 300 Watts and oxygen, O 2 , gas is flowed into chamber at approximately 10 sccm and CF 4 gas is flowed into chamber 54 approximately 90 sccm.

- the DOP of 60% is maintained in a surface 130 , which is defined by the remaining portions of semi-conformal layer 29 .

- the maximum thickness of t 6 of the remaining portion of hill 34 is less than thickness t 3 .

- d 2 the greater the degree of planarization in multi-material semi-planar surface 65 afforded by smoothing layer 40 .

- etch conditions are changed to maximize the etch rate of the remaining portions of semi-conformal layer 29 while forming crown surface 25 and maximizing the planarity thereof.

- chamber 54 is pressurized to 50 mT, power supply 62 is operated at 500 Watts, and supply 75 provides C 4 F 8 gas into chambers 54 at approximately 10 sccm.

- Supply 77 provides oxygen gas into chamber 54 at approximately 20 sccm, and supply 78 provides Argon gas into chamber 54 at approximately 100 sccm.

- patterned layer 22 may be etched establishing conditions in chamber 54 such that chamber pressure is 15 mT, power supply 62 is operated at 120 Watts and supply 82 introduces CO gas into chamber 54 at a rate of 100 sccm.

- Supply 77 introduces oxygen, O 2 , gas into chamber 54 at a rate of approximately 20 sccm to take advantage of the etch differential provided by regions 24 and 28 , as discussed in U.S. patent application Ser. No. 10/789,319, filed Feb. 27, 2004, entitled, COMPOSITIONS FOR AN ETCHING MASK COMPRISING A SILICON-CONTAINING MATERIAL, having Frank Y. Xu, Michael N. Miller and Michael P. C. Watts listed as inventors, which is incorporated by reference herein.

- the Z-6018 smoothing composition is centrally disposed on surface 30 before rotation occurs.

- substrate 10 is accelerated to 5,000 rpm/s to reach a maximum rotational velocity of approximately 2,500 rpm.

- the maximum rotational velocity is maintained until substantially all of the solvent in the polymerizable composition has been removed. This is detected optically by the unaided eye as the color of semi-conformal layer 29 remains substantially unchanged during rotation of substrate 10 . At these process conditions semi-conformal layer 29 is solidified and will not level.

- the substrate 10 is baked in an oven at 120° Celsius for fifteen minutes during which time semi-conformal layer 29 becomes fluidic, e.g., reflows, to facilitate leveling of smoothing surface 44 . Cooling is achieved by placing the same on an air-cooled cold plate having flows of ambient air directed toward substrate 10 for two minutes to solidify semi-conformal layer 29 .

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Nanotechnology (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Crystallography & Structural Chemistry (AREA)

- Life Sciences & Earth Sciences (AREA)

- Mathematical Physics (AREA)

- General Chemical & Material Sciences (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Theoretical Computer Science (AREA)

- Materials Engineering (AREA)

- Wood Science & Technology (AREA)

- Organic Chemistry (AREA)

- Architecture (AREA)

- Structural Engineering (AREA)

- Application Of Or Painting With Fluid Materials (AREA)

- Drying Of Semiconductors (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

Abstract

The present invention is directed to a method of coating a substrate having a solidified layer formed thereon, that features depositing a flowable material upon the solidified layer and forming an additional layer having a smooth flowable surface upon the substrate by imparting rotational movement upon the substrate followed by leveling of the flowable material in an absence of the rotational movement. After the additional layer is formed, the same is solidified.

Description

- The present application is a divisional of U.S. patent application Ser. No. xx/xxx,xxx (Attorney Docket No. P234M1D238) filed herewith, entitled ETCHING TECHNIQUE TO PLANARIZE A MULTI-LAYER STRUCTURE, listing David C. Wang and Frank Y. Xu as inventors, which application is incorporated by reference herein.

- The United States government has a paid-up license in this invention and the right in limited circumstance to require the patent owner to license other on reasonable terms as provided by the terms 70NANB4H3012 awarded by the National Institute of Standards and Technology (NIST).

- This invention relates to spin-on coating of substrates. Specifically, the present invention is directed to a method to coat a substrate employing spin-on techniques in furtherance of lithographic patterning.

- Spin-coating is a well known technique employed to form a layer of material upon a substrate. Often the material is deposited upon a surface having anisotropic topography in furtherance of producing a film having a planar surface disposed opposite to the substrate surface. The planarity of the material surface is highly desirable for several processes, e.g., deposition of resist material in furtherance of patterning. As a result, studies have been undertaken to understand the behavior of films formed during spin-coating. Peurrung and Graves in Film Thickness Profiles over Topography in Spin Coating, Journal of the Electrochemical Society, Vol. 138 No. 7 (1991), set forth a theoretical analysis of spin-coating wet films over anisotropic surfaces. Peurrung and Graves conclude that the presence of anisotropicity of the substrate surface makes problematic production of a planar material surface. Many attempts have been undertaken to obtain a planar material surface from material spin-coated on an anisotropic surface.

- U.S. Pat. No. 4,038,110 discloses a technique to planarize an anisotropic substrate surface involves forming a photoresist pattern in registration that with a pattern of unelevated areas present on the substrate. The photoresist pattern has narrower lateral dimensions than an elevated pattern whereby registration is facilitated. The photoresist pattern is flowed to laterally expand the photoresist and mask the unelevated areas.

- In U.S. Pat. No. 4,741,926, one manner in which to overcome the drawbacks with multi-layer resists involve spreading a resin material over an anisotropic surface employing a dual spin cycle. The resin material is spread at a speed of approximately of not less than 4000 revolutions per minute (rpm), preferably from 6000 to 8000 rpm, until build-up of the coating is detectable on a side wall of a topographical feature facing the centrifugal center of the spinning substrate. The spin speed is immediately reduced to less than 4000 rpm, preferably from about 1000 to 3500 rpm, and spinning is continued for a time sufficient to dry the coating.

- U.S. Pat. No. 4,794,021 discloses a method of forming a planarized layer on a substrate by spin coating a polymer over the substrate. Before the layer dries the substrate is heated in a pressure-controlled environment to control solvent loss while maintaining the polymer in a liquid-state. After a predetermined interval of time, the substrate is cured in a standard convention bake oven.

- U.S. Pat. No. 5,736,424 discloses a method that includes contacting a material having a predetermined viscosity with an object having a flat surface. The material has a viscosity less than 1000 cp, and a flat surface is placed into contact with the material in such a manner that the material is planarized to a desired degree. The material is cured while in contact with the flat surface. The object is then separated from the material. The planarity of the planarizing material is then transferred into the underlying layer using conventional techniques.

- U.S. Pat. No. 5,893,750 discloses a method of forming a planarized interlevel dielectric layer over interconnects formed upon a frontside surface of an upper topography of a silicon wafer. An anisotropic silicon dioxide (oxide) layer is first deposited over the interconnects. A spin-on glass (SOG) layer is then formed over the anisotropic oxide layer. The liquid SOG material flows over the upper surface, filling narrow spaces without creating voids and producing a surface smoothing effect at isolated vertical edges. After curing of the SOG layer, a chemical-mechanical polishing (CMP) process is applied to the frontside surface. The CMP process increases the planarity of the frontside surface by reducing surface heights of elevated features more so than surface heights in recessed areas. A need exists, however, to provide improved planarization techniques.

- The present invention is directed to a method of coating a substrate having a solidified layer formed thereon, that features depositing a flowable material upon the solidified layer and forming an additional layer having a smooth flowable surface upon the substrate by imparting rotational movement upon the substrate followed by leveling of the flowable material in an absence of the rotational movement. After the additional layer is formed, the same is solidified. These and other embodiments are discussed more fully below.

-

FIG. 1 is a cross-sectional view of a substrate having an anisotropic surface that is to be planarized in accordance with the present invention; -

FIG. 2 is a cross-sectional view of the substrate shown inFIG. 1 having a planarized surface, in accordance with the present invention; -

FIG. 3 is a cross-sectional view of the substrate shown inFIG. 1 having a semi-conformal layer deposited therein; -

FIG. 4 is a detailed cross-sectional view of a region of the substrate shown inFIG. 3 ; -

FIG. 5 is a cross-sectional view of the substrate shown inFIG. 4 having a smoothing layer deposited thereon; -

FIG. 6 is a cross-sectional view of a prior art etching chamber; -

FIG. 7 is a cross-sectional view of substrate shown inFIG. 5 after being etched employing first etch conditions in accordance with the present invention; -

FIG. 8 is a cross-sectional view of substrate shown inFIG. 7 after being etched employing second etch conditions in accordance with the present invention; - Referring to

FIG. 1 , in certain patterning processes it is desired to form a planar surface upon substrates, such assubstrate 10, having an anisotropic surface. The anisotropic surface may include spaced-apart projections apart recessions 18, which may result from any known previous patterning process.Projections 14 may be metal lines, photoresist, monocrystalline silicon and the like. In the present example,substrate 10 is discussed as including awafer 20 formed from standard materials, e.g., mono-crystalline silicon. Present uponwafer 20 is apatterned layer 22 in whichprojections apex surface 24 ofprojections 14 and substantially the entire surface area of anapex surface 26 ofprojections 16 are exposed and coplanar with asurface 28 of a material deposited to fillrecessions 18. To that end, in an exemplary embodiment, patternedlayer 22 is formed from a solidified polymeric material employing imprint lithography techniques, with aprimer layer 23 being disposed between patterned layer andwafer 20.Primer layer 23 is typically formed from spin-coating a layer of DUV30J-16. DUV30J-16 is a bottom anti-reflective coating, BARC, available from Brewer Science in Rolla, Mo. An exemplary bulk material from which to form patternedlayer 22 is as follows: - The acrylate component, isobornyl acrylate (IBOA), has the following structure:

and comprises approximately 47% of bulk material by weight, but may be present in a range of 20% to 80%, inclusive. As a result, the mechanical properties of patternedlayer 22 are primarily attributable to IBOA. An exemplary source for IBOA is Sartomer Company, Inc. of Exton, Pa. available under the product name SR 506. - The component n-hexyl acrylate (n-HA) has the following structure:

and comprises approximately 25% of bulk material by weight, but may be present in a range of 0% to 50%, inclusive. Also providing flexibility to patternedlayer 22, n-HA is employed to reduce the viscosity of the prior art bulk material so that bulk material, in the liquid phase, has a viscosity in a range of 2-9 Centipoises, inclusive. An exemplary source for the n-HA component is the Aldrich Chemical Company of Milwaukee, Wis. - A cross-linking component, ethylene glycol diacrylate, has the following structure:

and comprises approximately 25% of bulk material by weight, and may be present in a range of 10% to 50%, inclusive. EGDA also contributes to the modulus and stiffness buildup, as well as facilitates cross-linking of n-HA and IBOA during polymerization of the bulk material. - An initiator component, 2-hydroxy-2-methyl-1-phenyl-propan-1-one is available from Ciba Specialty Chemicals of Tarrytown, N.Y. under the tradename DAROCUR® 1173, and has the following structure:

and comprises approximately 3% of the bulk material by weight, and may be present in a range of 1% to 5%, inclusive. The actinic energy to which the initiator is responsive is broadband ultra-violet energy generated by a medium-pressure mercury lamp. In this manner, the initiator facilitates cross-linking and polymerization of the components of the bulk material. The component FS-2000 is a surfactant that provides preferential adhesion and release upon polymerization of the bulk material. FS-2000 is sold by Mason Chemical Company of Arlington Heights, Ill. under the product name MASURF® FS-2000 and comprises approximately 2% of the bulk material by weight, and may be present in a range of 0.1% to 5%, inclusive. An exemplary imprint lithography technique to deposit patternedlayer 22 is disclosed in co-pending U.S. patent application Ser. No. 11/068,171, filed Feb. 28, 2005, entitled “Composition to Reduce Adhesion Between a Conformable Region and a Mold,” having Frank Xu and Michael N. Miller listed as inventors, which is incorporated by reference herein. - In furtherance of forming crown surface 25,

projections recessions 18 filled, with a polymerizable material, referred to herein as a semi-conformal composition, which is applied by spin-coating to formsemi-conformal layer 29. In the present example,semi-conformal layer 29 is formed from a silicon-containing polyermizable material employing a Brewer Science Model CEE® 4000 spin-coating system. The polymerizable material is centrally disposed onsubstrate 10 before rotation occurs. After dispensing of the polymerizable material,substrate 10 is accelerated 3,000 revolutions per minute (rpm) per second to reach a maximum rotational velocity of approximately 1000 rpm. The maximum rotational velocity is maintained until substantially all of the solvent in the polymerizable material has been removed. This is detected optically by the unaided eye as the color ofsemi-conformal layer 29 remaining substantially unchanged during rotation ofsubstrate 10. Following removal of the solvent,substrate 10 is placed upon a heating device (not shown), such as a hot plate, to raise the temperature thereof, by conductive heating, to approximately 180° C. for 60 seconds. - An exemplary bulk material to include in the semi-conformal composition to form

semi-conformal layer 29 is as follows: - The hydroxyl-functional polysiloxane component is present in SEMI-CONFORMAL BULK MATERIAL in amounts of approximately 80% by weight of SEMI-CONFORMAL BULK MATERIAL, but may be present in a range of 40 to 95%, inclusive by weight, depending on the thicknesses desired for

semi-conformal layer 29. An exemplary hydroxyl-functional polysiloxane component used in the present invention is a silicon T-resin intermediate available from Dow Corning® (Midland, Mich.) under the tradename Z-6018. - The hexamethoxymethylmelamine(HMMM) is a cross-linking agent component is present in SEMI-CONFORMAL BULK MATERIAL in amounts of approximately 19% by weight of SEMI-CONFORMAL BULK MATERIAL, but may be present in a range of 10 to 30%, inclusive by weight. An exemplary HMMM component is available from Cytec Industries, Inc. (West Paterson, N.J.) under the tradename CYMEL 303ULF.

- The toluenesulfonic acid component is a catalyst present in the SEMI-CONFORMAL LAYER BULK MATERIAL in an amount of component is present in SEMI-CONFORMAL BULK MATERIAL in amounts of approximately 1% by weight of SEMI-CONFORMAL BULK MATERIAL, but may be present in a range of 1 to 2%, inclusive by weight. An exemplary catalyst is available from Cytec Industries, Inc. (West Paterson, N.J.) under the tradename CYCAT 4040.

- Typically, the SEMI-CONFORMAL LAYER BULK MATERIAL is employed with a solvent to form the semi-conformal composition employed to form

semi-conformal layer 29. The solvent may be present in the semi-conformal composition in amounts of approximately 60% to 98% by weight, dependent upon the desired thicknesses ofsemi-conformal layer 29, with the remaining portions of the semi-conformal composition being the SEMI-CONFORMALLAYER BULK MATERIAL 58. An example of a solvent used in the present invention is methyl amyl ketone available from Aldrich Co. (St. Louis, Mo.) under the tradename MAK. - The anisotropy of surface of

substrate 10 causes thickness variations insemi-conformal layer 29 that present astroughs 32 andhills 34. It was observed that regions of asurface 30 ofsemi-conformal layer 29 in superimposition withprojection 16 andrecession 18 had a substantially smooth, if not planar surface, becauseprojection 16 has small lateral dimension, w1. This results in a thickness t1, ofsemi-conformal layer 29, measured betweensurface 30 andapex surface 26 ofprojection 16, being substantially equal to thickness t2-h1, with h1 being the height ofprojection 16. This was observed for projections, such asprojection 16, having a width, w1, of several microns or less, which is smaller than width, w2, ofrecession 18. Projections, such asprojection 14, having a width, w3, which is tens of microns or larger, were observed to produce hills, such ashill 34.Hill 34 is defined by a region ofsemi-conformal layer 29 having a varying thickness measured with respect toapex surface 24 ofprojection 14 andsurface 30. The maximum thickness, t3, of the region ofsemi-conformal layer 29 in superimposition withprojection 14, is approximately equal to thickness t2. The portion ofsurface 30 associated with the maximum thickness ofhill 34 is spaced-apart from a plane P1 in which the remaining regions ofsurface 30 lie, a distance d1. Typically, d1 is approximately equal to height, h2, ofprojection 14. As a result, a blanket etch to expose the entire area ofapex surface 30 andhill 34 would result inprojection 16 being lost (removed through the etching process) due to the presence ofhill 34 in furtherance of forming crown surface 25. This is undesirable. - Referring to both

FIGS. 2, 4 and 5, to minimize, if not prevent, the portion ofprojection 16 that is removed upon exposure of the entire area ofapex surface 34, an additional layer, referred to as smoothinglayer 40, is disposed uponsurface 30. Smoothinglayer 40 functions to further reduce non-planarity perturbations insurface 30 due, for example, totroughs 32 andhills 34. To that end, smoothinglayer 40 is typically disposed onsurface 30 employing spin-on techniques to minimize the time required to form the same. As a result, the material from which smoothinglayer 40 is formed includes a solvent. It is desired to form smoothinglayer 40 from a material that maintains a fluidic state after spin-on coating has effectively removed substantially all of the solvent present therein. This minimizes non-planarity perturbations present in a smoothingsurface 44 resulting from smoothinglayer 40 after formation thereof by maximizing leveling of smoothingsurface 44 in the absence of centrifugal forces. This is based upon the realization that conformal coating dominates in the presence of centrifugal forces and planarization dominates in the presence of capillary forces. A ratio of centrifugal force (Fc) to capillary force (Fp) is proportional to the cubic of feature lateral dimension, (w) that may be expressed as follows:

Fc/FpαW3 1)

To avoid the deleterious effects of centrifugal forces, the material from which smoothinglayer 40 is formed maintains a fluidic state after spin-on coating has effectively removed substantially all of the solvent present therein. - An exemplary bulk material from which to form smoothing

layer 40 is as follows: - The cycloaliphatic epoxy component has the following structure:

The cycloaliphatic epoxy component comprises approximately 87% of bulk material by weight. As a result, the mechanical properties of smoothinglayer 40 are primarily attributable to the cycloaliphatic epoxy component. An exemplary source of the cycloaliphatic epoxy component is sold by Dow Chemical Company of Midland, Mich. as chemical name 3,4-epoxycyclohexylmethyl-3,4-epoxycyclohexane carboxylate and sold under the tradename ERL-4221LV. - The ω-caprolactone triol component comprises approximately 10% of the bulk material by weight. This component increased the catioinic curing speed of SMOOTHING LAYER BULK MATERIAL 1. An exemplary source of the ω-caprolactone triol component is sold by Dow Chemical Company of Midland, Mich. under the tradename Tone 0301.

- The photoinitiator component comprises approximately 3% of the bulk material by weight and facilitates cross-linking and polymerization of the remaining components of bulk material in response to actinic energy. An exemplary photoinitiator is a cationic photoinitiator comprising a mixture of triarylsulfonium hexafluorophosphate salts in a propylene carbonate. An exemplary source of the photoinitiator component has the following structure:

and is sold by Dow Chemical Company of Midland, Mich. under the tradename UVI 6992. - The fluorosurfactant component is a nonionic fluorinated acrylic copolymer based surfactant that comprises less than 1% of the bulk material by weight. An exemplary fluorosurfactant is available from Dainippon Ink & Chemical of Japan under the tradename MegaFace™ R-08.

- Typically, the SMOOTHING LAYER BULK MATERIAL is employed with a solvent to form a smoothing composition employed to form smoothing

layer 40. The solvent may be present in the smoothing composition in amounts of approximately 20% to 98% by weight, dependent upon the desired thicknesses of smoothinglayer 40, with the remaining portions of the semi-conformal composition being the SMOOTHING LAYER BULK MATERIAL. An example of a solvent used in the present invention is methyl amyl ketone available from Aldrich Co. (St. Louis, Mo.) under the tradename MAK. -

Surface 30 is coated with the smoothing composition by spin-on techniques employing a Brewer Science Model CEE® 4000 spin-coating system to form smoothinglayer 40. The smoothing composition is centrally disposed onsurface 30 before rotation occurs. After dispensing of the smoothing composition,substrate 10 is accelerated 5,000 revolutions per minute (rpm)/s to reach a maximum rotational velocity of approximately 4000 rpm. The maximum rotational velocity is maintained until substantially all of the solvent in the polymerizable composition has been removed. This is detected optically by the unaided eye as the color ofsemi-conformal layer 29 remaining substantially unchanged during rotation ofsubstrate 10. Thereafter, rotation ofsubstrate 10 is ceased and leveling of smoothingsurface 44 is allowed to occur in the absence of movement ofsubstrate 10. Typically, leveling occurs for 2-30 minutes and at ambient atmospheric conditions, i.e. ambient temperatures and pressures. Exemplary ambient temperatures and pressures are 25° Celsius and 760 Torr, respectively. After the desired leveling time has occurred, smoothing layer is exposed to broadband ultraviolet energy for approximately 120 seconds with a lamp intensity of 20 mW/cm2 to polymerize and cross-link the smoothing composition. This is typically achieved employing a light source sold by OAI of San Jose, Calif. asModel 30 LS that may produce an 8 inch uniform beam. -

Hill 34 causesregions 46 of smoothingsurface 44 to have a varying thickness measured with respect tosurface 30. The thickness, t4, differs from a thickness, t5, ofregions 48 of smoothinglayer 40 outside ofregion 46. This results in the portion ofsurface 44 associated with the maximum thickness ofregion 46 being spaced-apart from a plane, P2, in which the remaining regions ofsurface 46 lie, a distance d2. The bulk material from which smoothinglayer 40 is fabricated facilitates, for a given deposition process, to ensure that thickness, t4, is less than thickness, t5; hence, d1 is greater than d2. This effectively reduces the thickness offset between exposed surfaces, in thiscase smoothing surface 44 and both,nadir surface 19 ofrecession 18, andapex surface 24. - Assuming smoothing

layer 40 andsemi-conformal layer 29 have substantially similar etch characteristics, e.g., etch rate, for a given etch recipe, or groups of etch recipes, the presence of smoothinglayer 40 reduces the magnitude of over-etch to which theprojection 16 is subject to when exposingapex surface 24. The reduction would be the absolute value of the difference between d1 and d2. For example, assuming height h2 is 100 nanometers (nm), d1 would be approximately 100 nm. It was found that depositing smoothinglayer 40 with a thickness, t5, being approximately 500 nm, provided thickness, t4, of approximately 440 nm. As a result, d2 is approximately 60 nm. This amounts to a 60% improvement of the degree of planarization (DOP). In the absence of smoothinglayer 40, the DOP may be defined as follows:

DOP=(t 2 −t 3)/h 2×100% 2)

with t2, t3 and h2 shown inFIG. 5 . With the presence of smoothinglayer 40, the DOP may be defined as follows:

DOP=[t2+(d 1 −d 2)−t 3 ]/h 2×100% 3)

Assumingprojection 16 has a height, h1, of 100 nm, the presence of smoothinglayer 40 would result inprojection 16 having a height, h1, of approximately 60 nm upon exposure ofsurface 34. - Further planarization benefit may be obtained by taking advantage of etch rate differential provided by differing etch recipes. For example, assuming that

semi-conformal layer 29 had an etch rate, for a given etch recipe, that was 20% faster than the associated etch rate of smoothinglayer 40, it may be seen that the reduction in height, h1, may be further reduced increased by 12 nm, i.e., height h1 ofprojection 16 is approximately 72 nm upon exposure of the entire area ofsurface 34. This may be desirable. Conversely, were the etch rate associated withsemi-conformal layer 29, for a given etch recipe, 20% slower that the associated etch rate of smoothinglayer 40, the planarization benefits of smoothing layer may be reduced. The height, h1, ofprojection 16 would be reduced by 12 nm so that h1 would be reduced to 48 nm upon exposure of theentire surface 34. - Referring to

FIGS. 5 and 6 , matching the etch characteristics of the materials ofsemi-conformal layer 29 and smoothinglayer 40 may be problematic. As a result, an etch recipe has been developed that compensates for the etch rate differential presented bysemi-conformal layer 29 and smoothinglayer 40 SO that both etch at substantially the same rates. To that end, an etching system, such as a magnetically-enhanced reactive ion etching (MERIE)reactor 50 is employed.Reactor 50 includes groundedwalls 52 defining achamber 54 and slit valve opening 56 allowing ingress to and egress fromchamber 54. Disposed withinchamber 54 is acathode pedestal 58 with anelectrostatic chuck 60 selectively clamping the wafer that may be coupled to a power source (not shown).Cathode pedestal 58 may include channels (not shown) through which coolant fluid (not shown), flows to facilitate control of the temperature of the chuck. AnRF power supply 62 is in electrical communication withcathode pedestal 58 to facilitate control of the DC bias to chuck 40 and generation of a plasma withinchamber 54. Avacuum pump system 66 pumps thechamber 54 through anadjustable throttle valve 68. - Processing gases are supplied from gas sources 75-82 through respective mass flow controllers 83-90 to a quartz

gas distribution plate 92 positioned opposite to chuck 60. Thedistribution plate 92 includes a manifold 94 receiving the processing gas and communicating withchamber 54 through a showerhead having a large number of distributedapertures 96 so as to inject a more uniform flow of processing gas intochamber 54. During operation, pump 66 is operated to establish a pressure inchamber 54 that is approximately 30 milliTorr (mT).Mass flow controllers supplies supply 76 provides a flow of CF4 gas intochamber 54 at approximately 90 standard cubic centimeters per minute (sccm).Supply 77 provides a flow of oxygen, O2, gas into processing region at approximately 10sccm. Power supply 62 is operated at 300 Watts. This configuration results insemi-conformal layer 29 and smoothinglayer 40 etching at substantially the same rates, e.g.,semi-conformal layer 29 etches at approximately 161.3 nm/minute±10 nm/minute, and smoothinglayer 40 etches at approximately 167.4 nm/minute±10 nm/minute. It is desired to minimize the time required to complete etching, i.e., to exposesurfaces - Referring to both