RU2419198C1 - Прецизионный операционный усилитель - Google Patents

Прецизионный операционный усилитель Download PDFInfo

- Publication number

- RU2419198C1 RU2419198C1 RU2010111605/09A RU2010111605A RU2419198C1 RU 2419198 C1 RU2419198 C1 RU 2419198C1 RU 2010111605/09 A RU2010111605/09 A RU 2010111605/09A RU 2010111605 A RU2010111605 A RU 2010111605A RU 2419198 C1 RU2419198 C1 RU 2419198C1

- Authority

- RU

- Russia

- Prior art keywords

- transistor

- output

- active load

- transistors

- collector

- Prior art date

Links

Images

Landscapes

- Amplifiers (AREA)

Abstract

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в решающих усилителях с малыми значениями напряжения смещения нуля UCM в условиях воздействия радиации или температуры). Технический результат: уменьшение абсолютного значения систематической составляющей UCM, ее температурного и радиационного дрейфа. Прецизионный операционный усилитель содержит входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, первый (4), второй (5) и третий (6) транзисторы активной нагрузки, первый (7) и второй (8) выходные транзисторы, причем коллектор первого (4) и база третьего (6) транзисторов активной нагрузки связаны с первым (2) токовым выходом входного дифференциального каскада (1), эмиттеры первого (4), второго (5) транзисторов активной нагрузки и второго (8) выходного транзистора связаны с шиной источника питания (9), коллектор второго (5) транзистора активной нагрузки соединен с эмиттером третьего (6) транзистора активной нагрузки, коллектор второго (8) выходного транзистора соединен с эмиттером первого (7) выходного транзистора и выходом устройства (10), базы первого (4), второго (5) транзисторов активной нагрузки и второго (8) выходного транзистора соединены друг с другом, а коллектор третьего (6) транзистора активной нагрузки и база первого (7) выходного транзистора соединены со вторым (3) токовым выходом входного дифференциального каскада (1). В схему введены первый (11) и второй (12) дополнительные транзисторы, база первого (11) дополнительного транзистора связана с �

Description

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в решающих усилителях с малыми значениями напряжения смещения нуля Uсм в условиях воздействия радиации или температуры).

Двухкаскадная архитектура операционных усилителей (ОУ) относится к числу наиболее перспективных для многих применений и поэтому широко используется в микроэлектронных устройствах. Для повышения коэффициента усиления по напряжению (Ку) в таких ОУ в качестве активной нагрузки (АН) применяется так называемое токовое зеркало Вильсона [1-7], а также каскодные токовые зеркала. (Другие известные варианты построения АН дают более низкие значения Ку.) В таких схемах согласование высокоимпедансного узла «А» (фиг.1) с нагрузкой ОУ обеспечивается эмиттерным повторителем, входной ток которого оказывает повышенное влияние на величину напряжения смещения нуля ОУ (UCM).

Наиболее близким по технической сущности к заявляемому схемотехническому решению является архитектура ОУ, которая сводится к чертежу фиг.1, представленная в патенте США 5.512.859, fig.1. Она также присутствует в других патентах и литературных источниках, например, [1-7].

Существенный недостаток известного ОУ (фиг.1) состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (UCM), зависящей от свойств его архитектуры.

Основная цель предлагаемого изобретения состоит в уменьшении абсолютного значения систематической составляющей UCM, ее температурного и радиационного дрейфа.

Поставленная цель достигается тем, что в операционном усилителе (фиг.1), содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый 4, второй 5 и третий 6 транзисторы активной нагрузки, первый 7 и второй 8 выходные транзисторы, причем коллектор первого 4 и база третьего 6 транзисторов активной нагрузки связаны с первым 2 токовым выходом входного дифференциального каскада 1, эмиттеры первого 4, второго 5 транзисторов активной нагрузки и второго 8 выходного транзистора связаны с шиной источника питания 9, коллектор второго 5 транзистора активной нагрузки соединен с эмиттером третьего 6 транзистора активной нагрузки, коллектор второго 8 выходного транзистора соединен с эмиттером первого 7 выходного транзистора и выходом устройства 10, базы первого 4, второго 5 транзисторов активной нагрузки и второго 8 выходного транзистора соединены друг с другом, а коллектор третьего 6 транзистора активной нагрузки и база первого 7 выходного транзистора соединены со вторым 3 токовым выходом входного дифференциального каскада 1, предусмотрены новые элементы и связи - в схему введены первый 11 и второй 12 дополнительные транзисторы, база первого 11 дополнительного транзистора связана с первым 2 выходом входного дифференциального каскада 1, эмиттер подключен к объединенным базам первого 4, второго 5 транзисторов активной нагрузки, второго 8 выходного транзистора, а также второго 12 дополнительного транзистора, эмиттер второго 12 дополнительного транзистора связан с шиной источника питания 9, а коллектор второго 12 дополнительного транзистора подключен к коллектору второго 8 выходного транзистора, причем коллекторы первого 7 выходного транзистора и первого 11 дополнительного транзистора соединены со второй 13 шиной источника питания.

Схема ОУ-прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

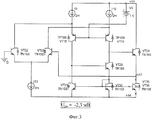

На чертеже фиг.3 показана схема операционного усилителя -прототипа, а на чертеже фиг.4 - заявляемого ОУ (фиг.2) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НЛП «Пульсар».

На чертеже фиг.5 приведены температурные зависимости напряжения смещения нуля сравниваемых схем фиг.3, фиг.4.

Прецизионный операционный усилитель (фиг.2) содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый 4, второй 5 и третий 6 транзисторы активной нагрузки, первый 7 и второй 8 выходные транзисторы, причем коллектор первого 4 и база третьего 6 транзисторов активной нагрузки связаны с первым 2 токовым выходом входного дифференциального каскада 1, эмиттеры первого 4, второго 5 транзисторов активной нагрузки и второго 8 выходного транзистора связаны с шиной источника питания 9, коллектор второго 5 транзистора активной нагрузки соединен с эмиттером третьего 6 транзистора активной нагрузки, коллектор второго 8 выходного транзистора соединен с эмиттером первого 7 выходного транзистора и выходом устройства 10, базы первого 4, второго 5 транзисторов активной нагрузки и второго 8 выходного транзистора соединены друг с другом, а коллектор третьего 6 транзистора активной нагрузки и база первого 7 выходного транзистора соединены со вторым 3 токовым выходом входного дифференциального каскада 1. В схему введены первый 11 и второй 12 дополнительные транзисторы, база первого 11 дополнительного транзистора связана с первым 2 выходом входного дифференциального каскада 1, эмиттер подключен к объединенным базам первого 4, второго 5 транзисторов активной нагрузки, второго 8 выходного транзистора, а также второго 12 дополнительного транзистора, эмиттер второго 12 дополнительного транзистора связан с шиной источника питания 9, а коллектор второго 12 дополнительного транзистора подключен к коллектору второго 8 выходного транзистора, причем коллекторы первого 7 выходного транзистора и первого 11 дополнительного транзистора соединены со второй 13 шиной источника питания. В частном случае входной каскад 1 выполнен на биполярных транзисторах 14 и 15. Однако он может иметь и более сложную структуру, главной особенностью которой должно быть наличие симметричных токовых выходов 2 и 3, для которых выходные токи I2=I3.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме фиг.2, т.е. зависящие от схемотехники ОУ.

Если выходные токи первого 2 (I2) и второго 3 (I3) токовых выходов входного каскада 1 равны величине I0, то токи эмиттеров и коллекторов транзисторов 4, 5, 6, 7, 8, 11, 12:

где Iб.р=Iэ.i/βi - ток базы n-p-n транзисторов 4, 5, 6, 7, 8, 12 при эмиттерном токе Iэ.i=I0;

Iб.11<<Iб.р - ток базы транзистора 11;

βi - коэффициент усиления по току базы n-p-n транзисторов при Iэ=I0.

Как следствие, разность токов в узле «А» при его коротком замыкании на эквипотенциальную общую шину

где Iб.7=2Iб.р - ток базы транзистора 7.

Подставляя (1)÷(8) в (9), находим, что в схеме фиг.2 разностный ток, определяющий Uсм ОУ

Таким образом, в заявляемом устройстве при выполнении условия (10) уменьшается систематическая составляющая Uсм, обусловленная конечной величиной β транзисторов и его радиационной (или температурной) зависимостью. Как следствие, это уменьшает Uсм, так как разностный ток Iр в узле «A» создает Uсм, зависящее от крутизны S преобразования входного дифференциального напряжения (uвх) ОУ в выходной ток узла «A». В частном случае для фиг.2:

где rэ14=rэ15 - сопротивления эмиттерных переходов входных транзисторов 14 и 15 входного каскада 1 при его построении по классической параллельно-балансной схеме.

Поэтому для схемы фиг.2

где φт=26 мВ - температурный потенциал.

В ОУ-прототипе I=Iб.7≠0, поэтому здесь систематическая составляющая Uсм получается более чем в 20 раз больше (Uсм=-2,3 мВ), чем в заявляемой схеме (Uсм=90,3 мкВ).

Компьютерное моделирование схем фиг.3, фиг.4 подтверждает (фиг.5) данные теоретические выводы.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

Литература

1. Патент США №6.268.769 fig.3.

2. Патент США №5.512.815.

3. Патент США №5.512.859 fig.1.

4. Патент США №5.479.133 fig.1.

5. Патент США №5.374.897.

6. Патент США №5.153.529 fig.1.

7. Патент США №6.483.382 fig.2.

Claims (1)

- Прецизионный операционный усилитель, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, первый (4), второй (5) и третий (6) транзисторы активной нагрузки, первый (7) и второй (8) выходные транзисторы, причем коллектор первого (4) и база третьего (6) транзисторов активной нагрузки связаны с первым (2) токовым выходом входного дифференциального каскада (1), эмиттеры первого (4), второго (5) транзисторов активной нагрузки и второго (8) выходного транзистора связаны с шиной источника питания (9), коллектор второго (5) транзистора активной нагрузки соединен с эмиттером третьего (6) транзистора активной нагрузки, коллектор второго (8) выходного транзистора соединен с эмиттером первого (7) выходного транзистора и выходом устройства (10), базы первого (4), второго (5) транзисторов активной нагрузки и второго (8) выходного транзистора соединены друг с другом, а коллектор третьего (6) транзистора активной нагрузки и база первого (7) выходного транзистора соединены со вторым (3) токовым выходом входного дифференциального каскада (1), отличающийся тем, что в схему введены первый (11) и второй (12) дополнительные транзисторы, база первого (11) дополнительного транзистора связана с первым (2) выходом входного дифференциального каскада (1), эмиттер подключен к объединенным базам первого (4), второго (5) транзисторов активной нагрузки, второго (8) выходного транзистора, а также второго (12) дополнительного транзистора, эмиттер второго (12) дополнительного транзистора связан с шиной источника питания (9), а коллектор второго (12) дополнительного транзистора подключен к коллектору второго (8) выходного транзистора, причем коллекторы первого (7) выходного транзистора и первого (11) дополнительного транзистора соединены со второй (13) шиной источника питания.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| RU2010111605/09A RU2419198C1 (ru) | 2010-03-25 | 2010-03-25 | Прецизионный операционный усилитель |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| RU2010111605/09A RU2419198C1 (ru) | 2010-03-25 | 2010-03-25 | Прецизионный операционный усилитель |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| RU2419198C1 true RU2419198C1 (ru) | 2011-05-20 |

Family

ID=44733825

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| RU2010111605/09A RU2419198C1 (ru) | 2010-03-25 | 2010-03-25 | Прецизионный операционный усилитель |

Country Status (1)

| Country | Link |

|---|---|

| RU (1) | RU2419198C1 (ru) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2568384C1 (ru) * | 2014-11-26 | 2015-11-20 | Федеральное Государственное Бюджетное Образовательное Учреждение Высшего Профессионального Образования "Донской Государственный Технический Университет" (Дгту) | Прецизионный операционный усилитель на основе радиационно стойкого биполярно-полевого технологического процесса |

-

2010

- 2010-03-25 RU RU2010111605/09A patent/RU2419198C1/ru not_active IP Right Cessation

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2568384C1 (ru) * | 2014-11-26 | 2015-11-20 | Федеральное Государственное Бюджетное Образовательное Учреждение Высшего Профессионального Образования "Донской Государственный Технический Университет" (Дгту) | Прецизионный операционный усилитель на основе радиационно стойкого биполярно-полевого технологического процесса |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| RU2412535C1 (ru) | Дифференциальный операционный усилитель | |

| RU2419198C1 (ru) | Прецизионный операционный усилитель | |

| RU2390916C1 (ru) | Прецизионный операционный усилитель | |

| RU2411637C1 (ru) | Прецизионный операционный усилитель с малым напряжением смещения нуля | |

| RU2416149C1 (ru) | Дифференциальный операционный усилитель с малым напряжением смещения нуля | |

| RU2416152C1 (ru) | Дифференциальный операционный усилитель | |

| RU2414808C1 (ru) | Операционный усилитель с малым напряжением смещения нуля | |

| RU2393629C1 (ru) | Комплементарный каскодный дифференциальный усилитель | |

| RU2411636C1 (ru) | Каскодный дифференциальный усилитель с малым напряжением смещения нуля | |

| RU2455757C1 (ru) | Прецизионный операционный усилитель | |

| RU2412530C1 (ru) | Комплементарный дифференциальный усилитель | |

| RU2449466C1 (ru) | Прецизионный операционный усилитель | |

| RU2412528C1 (ru) | Каскодный дифференциальный операционный усилитель с малым напряжением смещения нуля | |

| RU2449465C1 (ru) | Прецизионный операционный усилитель | |

| RU2412538C1 (ru) | Дифференциальный операционный усилитель | |

| RU2420863C1 (ru) | Дифференциальный операционный усилитель с малым напряжением смещения нуля | |

| RU2416150C1 (ru) | Дифференциальный операционный усилитель | |

| RU2416151C1 (ru) | Дифференциальный операционный усилитель | |

| RU2402152C1 (ru) | Каскодный дифференциальный усилитель с малым напряжением смещения нуля | |

| RU2412537C1 (ru) | Дифференциальный операционный усилитель | |

| RU2412529C1 (ru) | Каскодный дифференциальный усилитель | |

| RU2444119C1 (ru) | Прецизионный операционный усилитель | |

| RU2408975C1 (ru) | Каскодный дифференциальный усилитель | |

| RU2402153C1 (ru) | Дифференциальный усилитель с малым напряжением смещения нуля | |

| RU2402870C1 (ru) | Каскодный дифференциальный усилитель с малым напряжением смещения нуля |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| MM4A | The patent is invalid due to non-payment of fees |

Effective date: 20130326 |