RU2391769C1 - Дифференциальный операционный усилитель - Google Patents

Дифференциальный операционный усилитель Download PDFInfo

- Publication number

- RU2391769C1 RU2391769C1 RU2009110822/09A RU2009110822A RU2391769C1 RU 2391769 C1 RU2391769 C1 RU 2391769C1 RU 2009110822/09 A RU2009110822/09 A RU 2009110822/09A RU 2009110822 A RU2009110822 A RU 2009110822A RU 2391769 C1 RU2391769 C1 RU 2391769C1

- Authority

- RU

- Russia

- Prior art keywords

- output

- input

- current

- correction circuit

- gain correction

- Prior art date

Links

Images

Landscapes

- Amplifiers (AREA)

Abstract

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ). Технический результат: повышение коэффициента усиления. Дифференциальный операционный усилитель (ДОУ) содержит входной параллельно-балансный каскад (1), имеющий первый (2) и второй (3) основные входы, первый (4) и второй (5) токовые выходы, вспомогательное токовое зеркало (6), имеющее вход (7) и выход (8), первый выходной инвертирующий каскад по схеме с общим эмиттером на первом транзисторе (9), эмиттер которого связан с шиной (10) источника питания через первый (11) двухполюсник, база подключена ко второму (5) токовому выходу входного параллельно-балансного каскада (1), а коллектор подключен к двухполюснику нагрузки (12) и выходу (13) устройства. В схему введена цепь динамической коррекции коэффициента усиления (14), имеющая первый (15) и второй (16) входы, а также первый (17) и второй (18) выходы, причем второй выход (18) соединен со вторым (5) токовым выходом входного параллельно-балансного каскада (1), первый (17) выход подключен ко входу (7) токового зеркала (6), а второй (16) вход подключен к первому (4) токовому выходу входного параллельно-балансного каскада (1). 3 з.п. ф-лы, 6 ил.

Description

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ).

В современной радиоэлектронной аппаратуре находят применение операционные усилители с существенными различными параметрами. Особое место занимают ОУ с простейшей архитектурой, содержащие небольшое число элементов. На их основе выполняются, например, различные классы селективных цепей, где число маломощных усилителей может измеряться десятками единиц. Предполагаемое изобретение относится к данному типу ОУ).

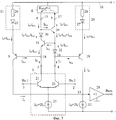

Наиболее близкой по технической сущности к заявляемому ОУ является двухкаскадная классическая схема ОУ фиг.1, представленная в патенте США 4.410.859, которая стала основой построения большого числа различных аналоговых устройств, в том числе выпускаемых ведущими микроэлектронными фирмами.

Операционный усилитель фиг.1 рассматривается в [1-13]. Основное достоинство его архитектуры - минимально возможный набор функциональных узлов, которые обеспечивают приемлемое для многих применений качество преобразования аналоговых сигналов. В настоящей заявке улучшается важнейший параметр ОУ - его коэффициент усиления без обратной связи.

Существенный недостаток известного ОУ фиг.1 состоит в том, что он имеет сравнительно невысокий коэффициент усиления по напряжению (Ку) без обратной связи. Это не позволяет реализовать на его основе различные решающие устройства с большим петлевым усилением и малой статической погрешностью.

Основная цель предлагаемого изобретения состоит в повышении Ку без существенного ухудшения токопотребления.

Поставленная цель достигается тем, что в операционном усилителе фиг.1, содержащем входной параллельно-балансный каскад 1, имеющий первый 2 и второй 3 основные входы, первый 4 и второй 5 токовые выходы, вспомогательное токовое зеркало 6, имеющее вход 7 и выход 8, первый выходной инвертирующий каскад по схеме с общим эмиттером на первом транзисторе 9, эмиттер которого связан с шиной 10 источника питания через первый 11 двухполюсник, база подключена ко второму токовому выходу 5 входного параллельно-балансного каскада 1, а коллектор подключен к двухполюснику нагрузки 12 и выходу 13 устройства, предусмотрены новые элементы и связи - в схему введена цепь динамической коррекции коэффициента усиления 14, имеющая первый 15 и второй 16 входы, а также первый 17 и второй 18 выходы, причем второй выход 18 соединен со вторым токовым выходом 5 входного параллельно-балансного каскада 1, первый выход 17 подключен ко входу 7 токового зеркала 6, а второй вход 16 подключен к первому 4 токовому выходу входного параллельно-балансного каскада 1.

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

На фиг.3 представлена схема заявляемого устройства в соответствии с п.1, п.2 и п.3 формулы изобретения.

На фиг.4 приведена схема ОУ фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Здесь же показаны параметры смещения нуля ДУ фиг.4.

На фиг.5 приведена зависимость дифференциального коэффициента усиления (дБ) от частоты (Гц) при изменении R2 в пределах R2=0.1 ÷ 0.99 кОм с шагом 0,1 кОм для случая, когда R1=0,9 кОм=const.

На фиг.6 показан дифференциальный коэффициент усиления (дБ) от частоты (Гц) при изменении R1 в пределах R1=0.1 ÷ 0.99 кОм с шагом 0,1 кОм для случая, когда R2=1 кОм=const.

Дифференциальный операционный усилитель фиг.2 содержит входной параллельно-балансный каскад 1, имеющий первый 2 и второй 3 основные входы, первый 4 и второй 5 токовые выходы, вспомогательное токовое зеркало 6, имеющее вход 7 и выход 8, первый выходной инвертирующий каскад по схеме с общим эмиттером на первом транзисторе 9, эмиттер которого связан с шиной 10 источника питания через первый 11 двухполюсник, база подключена ко второму токовому выходу 5 входного параллельно-балансного каскада 1, а коллектор подключен к двухполюснику нагрузки 12 и выходу 13 устройства. В схему введена цепь динамической коррекции коэффициента усиления 14, имеющая первый 15 и второй 16 входы, а также первый 17 и второй 18 выходы, причем второй выход 18 соединен со вторым токовым выходом 5 входного параллельно-балансного каскада 1, первый выход 17 подключен ко входу 7 токового зеркала 6, а второй вход 16 подключен к первому токовому выходу 4 входного параллельно-балансного каскада 1.

Кроме этого, на фиг.2 в соответствии с п.2 формулы изобретения к первому токовому выходу 4 входного параллельно-балансного каскада подключен второй выходной инвертирующий каскад по схеме с общим эмиттером на втором транзисторе 19, эмиттер которого связан с шиной источника питания 10 через второй двухполюсник 20.

В соответствии с п.3 формулы изобретения на фиг.2 цепь динамической коррекции коэффициента усиления 14 содержит первый вспомогательный p-n переход 21 и первый вспомогательный транзистор 22, база которого подключена к первому входу 15 цепи динамической коррекции коэффициента усиления 14 и через первый вспомогательный р-n переход 21 соединена со вторым выходом 18 цепи динамической коррекции коэффициента усиления 14, эмиттер соединен с ее вторым входом 16, а коллектор - с первым выходом 17 цепи динамической коррекции коэффициента усиления 14.

На фиг.3 в соответствии с п.4 формулы изобретения цепь динамической коррекции коэффициента усиления 14 содержит второй вспомогательный транзистор 29, коллектор которого подключен к выходу 17 цепи динамической коррекции коэффициента усиления, база подключена к первому входу 15 цепи динамической коррекции коэффициента усиления 14 и через второй вспомогательный p-n переход 30 соединена с коллектором третьего вспомогательного транзистора, база которого соединена со вторым выходом 18 цепи динамической коррекции коэффициента усиления 14, эмиттер соединен со вторым входом 16, а коллектор - с первым выходом 17 цепи динамической коррекции коэффициента усиления 14.

Рассмотрим работу схемы фиг.2 на переменном токе.

Замечательной особенностью предлагаемого усилителя является повышение (более чем на порядок) коэффициента усиления по напряжению Ку. Для ОУ прототипа фиг.1

где r5 - эквивалентное сопротивление в узле 5;

rвых - выходное сопротивление дифференциального каскада 1 относительно выхода 5;

r6 - выходное сопротивление токового зеркала 6;

Rвх.9=β9R11 - эквивалентное сопротивление двухполюсника 11, приведенное к узлу 5;

- крутизна входного дифференциального каскада 1 при коротком замыкании в узле 5, зависящая от сопротивлений эмиттерных переходов транзисторов 21 и 22 (rэ21, rэ22);

β9 - коэффициент усиления тока базы транзистора 9;

Ку2 - коэффициент усиления второго каскада на транзисторе 9.

В связи с тем что β9>50 при R11≥1 кОм эквивалентное сопротивление r5 в узле 5 определяется транзисторами 21 и 22:

где µ22≈10-3÷10-2 - коэффициент внутренней обратной связи транзистора 22.

Поэтому численные значения предельного коэффициента усиления по напряжению первого каскада ОУ фиг.1

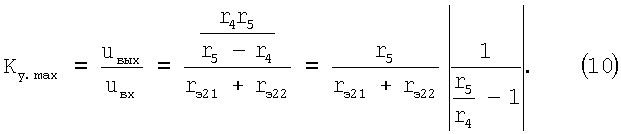

В предлагаемом устройстве (фиг.2) максимально возможный коэффициент усиления существенно повышается за счет взаимной компенсации эквивалентной проводимости в узле 5 эквивалентной проводимостью в узле 4. Для этого необходимо создать в узле 4 такое же эквивалентное сопротивление, что и в узле 5. То есть обеспечить

Если условие (7) выполняется, при изменении напряжения в узле (5) на величину u5 через r5 появится паразитный переменный ток i5=u5/r5. Однако в заявляемой схеме напряжение u5 передается и в узел 4 (u4=u5), что вызывает такое же изменение тока через r4:

Этот ток i4 поступает на вход 16 цепи динамической коррекции коэффициента усиления 14 и с единичным коэффициентом передачи передается на вход 7 токового зеркала 6 и, следовательно, на его выход 8. Далее, это приращение i4 поступает через цепь динамической коррекции коэффициента усиления 14 с ее входа 15 на выход 18. Как следствие, в узле 5 происходит вычитание токов i5 и i4:

Если r4=r5, то iΣ=0. Следовательно, от параллельно-балансного каскада 1 не требуется создавать дополнительное приращение тока в узле 5 за счет изменения входного дифференциального напряжения (между узлами 2 и 3). В этом случае Ку каскада существенно возрастает:

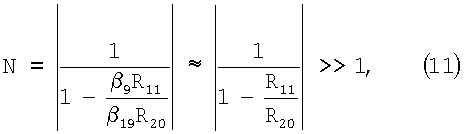

Таким образом, выигрыш по Ку, который дает заявляемая схема при β9=β19

где R11, R20 - сопротивление двухполюсников 11 и 20.

Действительно, компьютерное моделирование (фиг.5 и фиг.6) показывает, что заявляемый ОУ имеет более чем на 20 дБ большее усиление (Ky>104 или 82 дБ).

Таким образом, предлагаемое техническое решение характеризуется более высокими качественными показателями по усилению, что позволяет рекомендовать его для применения в архитектуре аналоговых микросхем.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №4.410.859 fig.1

2. Патент США №4.721.920

3. Патент США №4.783.637

4. А.св. СССР №678639

5. Патент США №4.560.948

6. А.св. №1193773

7. Патент США №4.463.319

8. Патент WO 03/063344A1

9. Патент США №5.343.164

10. Патент США №4.417.216

11. Патент США №5.365.191 fig.7

12. Патент США №4.163.908

13. Патент Японии №54-37561 fig.1

Claims (4)

1. Дифференциальный операционный усилитель, содержащий входной параллельно-балансный каскад (1), имеющий первый (2) и второй (3) основные входы, первый (4) и второй (5) токовые выходы, вспомогательное токовое зеркало (6), имеющее вход (7) и выход (8), первый выходной инвертирующий каскад по схеме с общим эмиттером на первом транзисторе (9), эмиттер которого связан с шиной (10) источника питания через первый (11) двухполюсник, база подключена ко второму (5) токовому выходу входного параллельно-балансного каскада (1), а коллектор подключен к двухполюснику нагрузки (12) и выходу (13) устройства, отличающийся тем, что в схему введена цепь динамической коррекции коэффициента усиления (14), имеющая первый (15) и второй (16) входы, а также первый (17) и второй (18) выходы, причем второй выход (18) соединен со вторым (5) токовым выходом входного параллельно-балансного каскада (1), первый (17) выход подключен ко входу (7) токового зеркала (6), а второй (16) вход подключен к первому (4) токовому выходу входного параллельно-балансного каскада (1).

2. Устройство по п.1, отличающееся тем, что к первому (4) токовому выходу входного параллельно-балансного каскада (1) подключен второй выходной инвертирующий каскад по схеме с общим эмиттером на втором (19) транзисторе, эмиттер которого связан с шиной источника питания (10) через второй (20) двухполюсник.

3. Устройство по п.1, отличающееся тем, что цепь динамической коррекции коэффициента усиления (14) содержит первый (21) вспомогательный p-n переход и первый (22) вспомогательный транзистор, база которого подключена к первому (15) входу цепи динамической коррекции коэффициента усиления (14) и через первый вспомогательный p-n переход (21) соединена со вторым (18) выходом цепи динамической коррекции коэффициента усиления (14), эмиттер соединен с ее вторым (16) входом, а коллектор - с первым (17) выходом цепи динамической коррекции коэффициента усиления (14).

4. Устройство по п.1, отличающееся тем, что цепь динамической коррекции коэффициента усиления (14) содержит второй (29) вспомогательный транзистор, коллектор которого подключен к выходу (17) цепи динамической коррекции коэффициента усиления, база подключена к первому (15) входу цепи динамической коррекции коэффициента усиления (14) и через второй вспомогательный p-n переход (30) соединена с коллектором третьего вспомогательного транзистора, база которого соединена со вторым (18) выходом цепи динамической коррекции коэффициента усиления (14), эмиттер соединен со вторым (16) входом, а коллектор - с первым (17) выходом цепи динамической коррекции коэффициента усиления (14).

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| RU2009110822/09A RU2391769C1 (ru) | 2009-03-24 | 2009-03-24 | Дифференциальный операционный усилитель |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| RU2009110822/09A RU2391769C1 (ru) | 2009-03-24 | 2009-03-24 | Дифференциальный операционный усилитель |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| RU2391769C1 true RU2391769C1 (ru) | 2010-06-10 |

Family

ID=42681697

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| RU2009110822/09A RU2391769C1 (ru) | 2009-03-24 | 2009-03-24 | Дифференциальный операционный усилитель |

Country Status (1)

| Country | Link |

|---|---|

| RU (1) | RU2391769C1 (ru) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2741055C1 (ru) * | 2020-09-02 | 2021-01-22 | федеральное государственное бюджетное образовательное учреждение высшего образования «Донской государственный технический университет» (ДГТУ) | Операционный усилитель с «плавающим» входным дифференциальным каскадом на комплементарных полевых транзисторах с управляющим p-n переходом |

-

2009

- 2009-03-24 RU RU2009110822/09A patent/RU2391769C1/ru not_active IP Right Cessation

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2741055C1 (ru) * | 2020-09-02 | 2021-01-22 | федеральное государственное бюджетное образовательное учреждение высшего образования «Донской государственный технический университет» (ДГТУ) | Операционный усилитель с «плавающим» входным дифференциальным каскадом на комплементарных полевых транзисторах с управляющим p-n переходом |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| RU2432669C1 (ru) | Широкополосный усилитель | |

| RU2364020C1 (ru) | Дифференциальный усилитель с отрицательной обратной связью по синфазному сигналу | |

| RU2421879C1 (ru) | Дифференциальный усилитель с высокочастотной коррекцией | |

| CN116009641A (zh) | 一种电流镜电路、保护电路、偏置电路及电子设备 | |

| RU2391769C1 (ru) | Дифференциальный операционный усилитель | |

| RU2390916C1 (ru) | Прецизионный операционный усилитель | |

| RU2331971C1 (ru) | Дифференциальный усилитель с расширенным диапазоном активной работы | |

| RU2346388C1 (ru) | Дифференциальный усилитель | |

| RU2354041C1 (ru) | Каскодный дифференциальный усилитель | |

| RU2416155C1 (ru) | Дифференциальный операционный усилитель | |

| RU2396699C1 (ru) | Каскодный дифференциальный усилитель с повышенным входным дифференциальным сопротивлением | |

| RU2475941C1 (ru) | Дифференциальный усилитель с комплементарным входным каскадом | |

| RU2390912C2 (ru) | Каскодный дифференциальный усилитель | |

| RU2411636C1 (ru) | Каскодный дифференциальный усилитель с малым напряжением смещения нуля | |

| RU2421893C1 (ru) | Каскодный дифференциальный усилитель | |

| RU2432667C1 (ru) | Дифференциальный операционный усилитель с малым напряжением питания | |

| RU2421888C1 (ru) | Дифференциальный усилитель | |

| RU2446554C1 (ru) | Дифференциальный операционный усилитель с парафазным выходом | |

| RU2446555C2 (ru) | Дифференциальный операционный усилитель | |

| RU2432666C1 (ru) | Дифференциальный операционный усилитель с малым напряжением питания | |

| RU2436226C1 (ru) | Дифференциальный операционный усилитель с парафазным выходом | |

| RU2432668C1 (ru) | Дифференциальный операционный усилитель с парафазным выходом | |

| RU2432665C1 (ru) | Дифференциальный операционный усилитель с малым напряжением питания | |

| RU2374757C1 (ru) | Каскодный дифференциальный усилитель | |

| RU2421896C1 (ru) | Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| MM4A | The patent is invalid due to non-payment of fees |

Effective date: 20130325 |