KR20200144192A - 난수 생성 장치 및 이의 동작 방법 - Google Patents

난수 생성 장치 및 이의 동작 방법 Download PDFInfo

- Publication number

- KR20200144192A KR20200144192A KR1020190071664A KR20190071664A KR20200144192A KR 20200144192 A KR20200144192 A KR 20200144192A KR 1020190071664 A KR1020190071664 A KR 1020190071664A KR 20190071664 A KR20190071664 A KR 20190071664A KR 20200144192 A KR20200144192 A KR 20200144192A

- Authority

- KR

- South Korea

- Prior art keywords

- values

- binary count

- count values

- value

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/14—Details of the phase-locked loop for assuring constant frequency when supply or correction voltages fail

- H03L7/146—Details of the phase-locked loop for assuring constant frequency when supply or correction voltages fail by using digital means for generating the oscillator control signal

- H03L7/148—Details of the phase-locked loop for assuring constant frequency when supply or correction voltages fail by using digital means for generating the oscillator control signal said digital means comprising a counter or a divider

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/58—Random or pseudo-random number generators

- G06F7/588—Random number generators, i.e. based on natural stochastic processes

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/08—Clock generators with changeable or programmable clock frequency

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/12—Synchronisation of different clock signals provided by a plurality of clock generators

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/353—Generators characterised by the type of circuit or by the means used for producing pulses by the use, as active elements, of field-effect transistors with internal or external positive feedback

- H03K3/356—Bistable circuits

- H03K3/356104—Bistable circuits using complementary field-effect transistors

- H03K3/356113—Bistable circuits using complementary field-effect transistors using additional transistors in the input circuit

- H03K3/356147—Bistable circuits using complementary field-effect transistors using additional transistors in the input circuit using pass gates

- H03K3/356156—Bistable circuits using complementary field-effect transistors using additional transistors in the input circuit using pass gates with synchronous operation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/84—Generating pulses having a predetermined statistical distribution of a parameter, e.g. random pulse generators

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/089—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Computational Mathematics (AREA)

- Mathematical Analysis (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- Measurement Of Radiation (AREA)

Abstract

Description

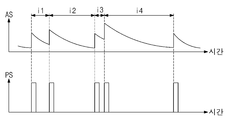

도 2는 도 1의 펄스 생성기의 동작에 따른 증폭 신호 및 펄스 신호의 예시적인 파형을 도시한 그래프이다.

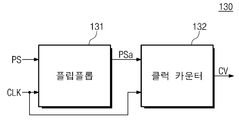

도 3은 도 1의 카운터의 예시적인 블록도이다.

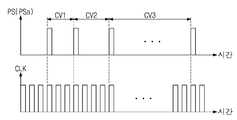

도 4는 도 1 및 도 3의 카운터의 동작을 설명하기 위한 그래프이다.

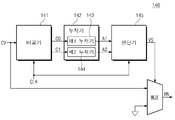

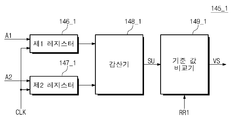

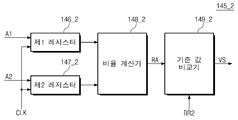

도 5는 도 1의 검증 회로의 예시적인 블록도이다.

도 6은 도 5의 판단기의 예시적인 블록도이다.

도 7은 도 5의 판단기의 예시적인 블록도이다.

도 8은 도 1의 난수 생성 장치의 동작 방법의 예시적인 순서도이다.

120: 펄스 생성기 121: 전치 증폭기

122: 아날로그-디지털 변환기 130: 카운터

131: 플립플롭 132: 클럭 카운터

140: 검증 회로 141: 비교기

142: 누적기 145, 145_1, 145_2: 판단기

150: 컨트롤러 MUX: 멀티플렉서

Claims (20)

- 소스로부터 방출된 입자들을 검출하여 검출 신호를 생성하는 소스 검출기;

상기 검출 신호에 기초하여 상기 검출된 입자들에 대응되는 펄스들을 생성하는 펄스 생성기;

상기 펄스들 사이의 시간 간격들을 측정하고, 상기 시간 간격들에 각각 대응되는 이진 카운트 값들을 생성하는 카운터; 및

상기 이진 카운트 값들에 포함된 0 값들의 개수 및 1 값들의 개수에 기초하여 상기 이진 카운트 값들의 출력을 결정하는 검증 회로를 포함하는 난수 생성 장치. - 제1 항에 있어서,

상기 검증 회로는,

상기 이진 카운트 값들에서 상기 0 값들 및 상기 1 값들을 추출하는 비교기;

상기 0 값들의 개수에 대응되는 제1 누적 값을 생성하고, 상기 1 값들의 개수에 대응되는 제2 누적 값을 생성하는 누적기;

상기 제1 누적 값 및 상기 제2 누적 값의 차이에 기초하여 상기 이진 카운트 값들의 유효성을 검증하기 위한 검증 신호를 생성하는 판단기; 및

상기 검증 신호에 기초하여 상기 이진 카운트 값들을 출력하는 멀티플렉서를 포함하는 난수 생성 장치. - 제2 항에 있어서,

상기 차이가 기준 범위 이내인 경우, 상기 판단기는 활성화 값을 갖는 상기 검증 신호를 생성하고, 상기 멀티플렉서는 상기 활성화 값에 응답하여 상기 이진 카운트 값들을 출력하는 난수 생성 장치. - 제2 항에 있어서,

상기 차이가 기준 범위를 벗어난 경우, 상기 판단기는 비활성화 값을 갖는 상기 검증 신호를 생성하고, 상기 멀티플렉서는 상기 비활성화 값에 응답하여 상기 이진 카운트 값들의 출력을 차단하는 난수 생성 장치. - 제2 항에 있어서,

상기 판단기는,

상기 제1 누적 값 및 상기 제2 누적 값의 상기 차이를 계산하는 감산기; 및

상기 차이를 기준 범위와 비교하고, 비교 결과에 기초하여 상기 검증 신호를 생성하는 기준 값 비교기를 포함하는 난수 생성 장치. - 제2 항에 있어서,

상기 누적기는,

상기 0 값들을 수신할 때 상기 제1 누적 값을 증가시키는 제1 누적기; 및

상기 1 값들을 수신할 때 상기 제2 누적 값을 증가시키는 제2 누적기를 포함하고,

상기 비교기는 상기 0 값들 및 상기 1 값들을 분리하고, 상기 0 값들을 상기 제1 누적기로 출력하고, 상기 1 값들을 상기 제2 누적기로 출력하는 난수 생성 장치. - 제1 항에 있어서,

상기 카운터는,

상기 펄스들을 클럭 신호에 동기화하여 출력하는 플립플롭; 및

상기 동기화된 펄스들 사이의 시간 간격들 동안, 상기 클럭 신호에 포함된 클럭들의 개수를 카운트하여 상기 이진 카운트 값들을 생성하는 클럭 카운터를 포함하는 난수 생성 장치. - 제1 항에 있어서,

기준 시간 동안 생성된 상기 펄스들에 기초하여 상기 이진 카운트 값들을 생성하도록 상기 카운터를 제어하고, 상기 이진 카운트 값들의 출력을 결정하도록 상기 검증 회로를 제어하는 컨트롤러를 더 포함하는 난수 생성 장치. - 제1 항에 있어서,

상기 이진 카운트 값들의 총 비트 수가 기준 개수일 때까지 상기 이진 카운트 값들을 생성하도록 상기 카운터를 제어하고, 상기 이진 카운트 값들의 출력을 결정하도록 상기 검증 회로를 제어하는 컨트롤러를 더 포함하는 난수 생성 장치. - 제1 항에 있어서,

상기 펄스 생성기는,

상기 검출 신호를 증폭하는 전치 증폭기; 및

상기 증폭된 검출 신호를 상기 펄스들로 변환하는 아날로그-디지털 변환기를 포함하는 난수 생성 장치. - 제1 항에 있어서,

상기 소스는 베타선 소스이고, 상기 입자들 각각은 베타선에 대응되는 난수 생성 장치. - 소스로부터 방출된 입자들을 검출하여 검출 신호를 생성하는 소스 검출기;

상기 검출 신호를 상기 검출된 입자들에 대응되는 펄스들로 변환하는 펄스 생성기;

상기 펄스들 사이의 시간 간격들 동안 클럭들의 개수를 카운트하여 이진 카운트 값들을 생성하는 카운터; 및

상기 이진 카운트 값들의 총 비트 수에 대한 타겟 값들의 개수의 비율에 기초하여 상기 이진 카운트 값들의 출력을 결정하는 검증 회로를 포함하는 난수 생성 장치. - 제12 항에 있어서,

상기 타겟 값들의 개수는 상기 이진 카운트 값들에 포함된 0 값들의 개수이거나, 상기 이진 카운트 값들에 포함된 1 값들의 개수인 난수 생성 장치. - 제12 항에 있어서,

상기 검증 회로는,

상기 이진 카운트 값들에서 상기 타겟 값들을 추출하는 비교기;

상기 타겟 값들의 개수에 대응되는 누적 값을 생성하는 누적기;

상기 누적 값에 기초하여 상기 비율을 계산하고, 상기 비율에 기초하여 상기 이진 카운트 값들의 유효성을 검증하기 위한 검증 신호를 생성하는 판단기; 및

상기 검증 신호에 기초하여 상기 이진 카운트 값들을 출력하는 멀티플렉서를 포함하는 난수 생성 장치. - 제14 항에 있어서,

상기 비율이 기준 범위 이내인 경우, 상기 판단기는 활성화 값을 갖는 상기 검증 신호를 생성하고, 상기 멀티플렉서는 상기 활성화 값에 응답하여 상기 이진 카운트 값들을 출력하는 난수 생성 장치. - 제14 항에 있어서,

상기 비율이 기준 범위를 벗어난 경우, 상기 판단기는 비활성화 값을 갖는 상기 검증 신호를 생성하고, 상기 멀티플렉서는 상기 비활성화 값에 응답하여 상기 이진 카운트 값들의 출력을 차단하는 난수 생성 장치. - 난수 생성 장치의 동작 방법에 있어서,

소스로부터 방출되는 입자들이 검출된 시간 간격들에 대응되는 이진 카운트 값들을 생성하는 단계;

상기 이진 카운트 값들에서 0 값들 및 1 값들을 추출하는 단계;

상기 0 값들의 개수에 대응되는 제1 누적 값을 생성하는 단계;

상기 1 값들의 개수에 대응되는 제2 누적 값을 생성하는 단계;

상기 제1 누적 값 및 상기 제2 누적 값의 차이에 기초하여 상기 이진 카운트 값들의 유효성을 검증하기 위한 검증 신호를 생성하는 단계; 및

상기 검증 신호에 기초하여 상기 이진 카운트 값들의 출력여부를 판단하는 단계를 포함하는 방법. - 제17 항에 있어서,

상기 검증 신호를 생성하는 단계는,

상기 제1 누적 값 및 상기 제2 누적 값의 차이를 계산하는 단계;

상기 차이와 기준 범위를 비교하는 단계; 및

상기 차이가 상기 기준 범위 이내인지 판단하는 단계를 포함하는 방법. - 제18 항에 있어서,

상기 이진 카운트 값들의 출력여부를 판단하는 단계는,

상기 차이가 상기 기준 범위 이내인 경우 상기 이진 카운트 값들을 난수로 출력하는 단계를 포함하는 방법. - 제18 항에 있어서,

상기 이진 카운트 값들의 출력여부를 판단하는 단계는,

상기 차이가 상기 기준 범위를 벗어난 경우 상기 이진 카운트 값들의 출력을 차단하는 단계를 포함하는 방법.

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020190071664A KR102792398B1 (ko) | 2019-06-17 | 2019-06-17 | 난수 생성 장치 및 이의 동작 방법 |

| US16/891,405 US11177817B2 (en) | 2019-06-17 | 2020-06-03 | Random number generating device and operating method of the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020190071664A KR102792398B1 (ko) | 2019-06-17 | 2019-06-17 | 난수 생성 장치 및 이의 동작 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20200144192A true KR20200144192A (ko) | 2020-12-29 |

| KR102792398B1 KR102792398B1 (ko) | 2025-04-10 |

Family

ID=73745312

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020190071664A Active KR102792398B1 (ko) | 2019-06-17 | 2019-06-17 | 난수 생성 장치 및 이의 동작 방법 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US11177817B2 (ko) |

| KR (1) | KR102792398B1 (ko) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20230053343A (ko) * | 2021-10-14 | 2023-04-21 | 충북대학교 산학협력단 | 진성 난수 발생기의 성능 개선 방법 |

| KR20230090116A (ko) * | 2021-12-14 | 2023-06-21 | 한국원자력연구원 | 엔트로피 생성 장치 및 방법 |

| KR20230112336A (ko) * | 2022-01-20 | 2023-07-27 | 충남대학교산학협력단 | 진성 난수 생성 장치 및 방법 |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102372740B1 (ko) * | 2019-04-09 | 2022-03-14 | 한국전자통신연구원 | 난수 생성 장치 및 이의 동작 방법 |

| US11329811B1 (en) * | 2021-03-15 | 2022-05-10 | Motorola Mobility Llc | Quantum-based security for hardware devices |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20030050943A1 (en) * | 2001-09-07 | 2003-03-13 | Nec Corporation | Random number generating method and random number generating device |

| US6697829B1 (en) * | 1998-02-12 | 2004-02-24 | Aea Technology Plc | Method of and apparatus for generating random numbers |

| US20050198091A1 (en) * | 2002-08-14 | 2005-09-08 | Takeshi Saito | Apparatus and method for generating random numbers |

| US20160328211A1 (en) * | 2011-09-30 | 2016-11-10 | Los Alamos National Security, Llc | Quantum random number generators |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5911009A (en) * | 1996-01-25 | 1999-06-08 | Dainippon Screen Mfg. Co., Ltd. | Method and apparatus for binary coding of image data including adding error accumulated for a target pixel and a pixel in the vicinity to be later coded |

| JP2980576B2 (ja) | 1997-09-12 | 1999-11-22 | 株式会社東芝 | 物理乱数発生装置及び方法並びに物理乱数記録媒体 |

| JPH11161473A (ja) | 1997-11-25 | 1999-06-18 | Norihei Tsuyusaki | 乱数発生装置と確率発生装置 |

| KR101488270B1 (ko) | 2013-05-27 | 2015-01-30 | 한국전자통신연구원 | 난수 발생기용 잡음원 엔트로피 획득 장치 및 방법 |

| KR101557761B1 (ko) | 2014-02-12 | 2015-10-06 | 한국전자통신연구원 | 실난수 발생기의 출력 수열 안정화 장치 및 방법 |

| US10387804B2 (en) * | 2014-09-30 | 2019-08-20 | BoonLogic | Implementations of, and methods of use for a pattern memory engine applying associative pattern memory for pattern recognition |

| DE102015102602A1 (de) | 2015-02-24 | 2016-08-25 | Infineon Technologies Ag | Zufallszahlengenerator |

| KR102200221B1 (ko) | 2015-05-13 | 2021-01-11 | 한국전자통신연구원 | 다중 출력 양자 난수 발생기 |

-

2019

- 2019-06-17 KR KR1020190071664A patent/KR102792398B1/ko active Active

-

2020

- 2020-06-03 US US16/891,405 patent/US11177817B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6697829B1 (en) * | 1998-02-12 | 2004-02-24 | Aea Technology Plc | Method of and apparatus for generating random numbers |

| US20030050943A1 (en) * | 2001-09-07 | 2003-03-13 | Nec Corporation | Random number generating method and random number generating device |

| US20050198091A1 (en) * | 2002-08-14 | 2005-09-08 | Takeshi Saito | Apparatus and method for generating random numbers |

| US20160328211A1 (en) * | 2011-09-30 | 2016-11-10 | Los Alamos National Security, Llc | Quantum random number generators |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20230053343A (ko) * | 2021-10-14 | 2023-04-21 | 충북대학교 산학협력단 | 진성 난수 발생기의 성능 개선 방법 |

| KR20230090116A (ko) * | 2021-12-14 | 2023-06-21 | 한국원자력연구원 | 엔트로피 생성 장치 및 방법 |

| KR20230112336A (ko) * | 2022-01-20 | 2023-07-27 | 충남대학교산학협력단 | 진성 난수 생성 장치 및 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| US11177817B2 (en) | 2021-11-16 |

| KR102792398B1 (ko) | 2025-04-10 |

| US20200395947A1 (en) | 2020-12-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102792398B1 (ko) | 난수 생성 장치 및 이의 동작 방법 | |

| US5987483A (en) | Random number generator based on directional randomness associated with naturally occurring random events, and method therefor | |

| Barbashina et al. | The URAGAN wide-aperture large-area muon hodoscope | |

| US11372623B2 (en) | Random number generating device and operating method of the same | |

| US4864140A (en) | Coincidence detection system for positron emission tomography | |

| US11080022B2 (en) | Random number generator, in particular improved true random number generator | |

| CN101980146A (zh) | 基于光子数可分辨探测的真随机数发生器 | |

| WO2016016741A1 (en) | True random number generator | |

| JP2002533800A (ja) | 自発α崩壊に基づく乱数発生器 | |

| Balygin et al. | A quantum random number generator based on the 100-Mbit/s Poisson photocount statistics | |

| Beissel et al. | The trigger and timing system of the Double Chooz experiment | |

| Akerib et al. | FPGA-based trigger system for the LUX dark matter experiment | |

| Park et al. | QEC: A quantum entropy chip and its applications | |

| US12217022B2 (en) | Systems and methods for direct random information generation from quantum random events | |

| US20210344488A1 (en) | Device and method for generating random bit sequences | |

| US12535993B1 (en) | System and method for preprocessing and conditioning cosmic ray data for randomness generation | |

| Hedges et al. | First 3D vector tracking of helium recoils for fast neutron measurements at SuperKEKB | |

| Vacheret et al. | The front end readout system for the T2K-ND280 detectors | |

| Rohe | RANDy-A true-random generator based on radioactive decay | |

| Basso et al. | A Starry Byte—proton beam measurements of single event upsets and other radiation effects in ABCStar ASIC Versions 0 and 1 for the ITk strip tracker | |

| KR20210097265A (ko) | 머신 러닝 알고리즘을 이용하는 난수 생성 장치 | |

| RU192980U1 (ru) | Устройство регистрации ионизирующего излучения для позиционно-чувствительных систем | |

| Zhang et al. | Track identification and reconstruction in fast neutron detection by MPGD | |

| Tsyganov | Automation of experiments at Dubna Gas-Filled Recoil Separator | |

| Naumov et al. | The digital trigger system for the RED-100 detector |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

Patent event code: PA01091R01D Comment text: Patent Application Patent event date: 20190617 |

|

| PG1501 | Laying open of application | ||

| PA0201 | Request for examination |

Patent event code: PA02012R01D Patent event date: 20220504 Comment text: Request for Examination of Application Patent event code: PA02011R01I Patent event date: 20190617 Comment text: Patent Application |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20240528 Patent event code: PE09021S01D |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

Patent event code: PE07011S01D Comment text: Decision to Grant Registration Patent event date: 20250123 |

|

| PG1601 | Publication of registration |