KR20170077943A - 접근 제어 유닛을 포함하는 시스템 온 칩 및 시스템 온 칩을 포함하는 모바일 장치 - Google Patents

접근 제어 유닛을 포함하는 시스템 온 칩 및 시스템 온 칩을 포함하는 모바일 장치 Download PDFInfo

- Publication number

- KR20170077943A KR20170077943A KR1020150187774A KR20150187774A KR20170077943A KR 20170077943 A KR20170077943 A KR 20170077943A KR 1020150187774 A KR1020150187774 A KR 1020150187774A KR 20150187774 A KR20150187774 A KR 20150187774A KR 20170077943 A KR20170077943 A KR 20170077943A

- Authority

- KR

- South Korea

- Prior art keywords

- processor

- access

- access control

- secure

- address

- Prior art date

Links

- 238000004891 communication Methods 0.000 claims abstract description 45

- 230000015654 memory Effects 0.000 claims description 62

- 238000000034 method Methods 0.000 claims description 37

- 238000013507 mapping Methods 0.000 claims description 9

- 230000008859 change Effects 0.000 claims description 7

- 230000000903 blocking effect Effects 0.000 claims description 5

- 238000013519 translation Methods 0.000 claims description 4

- 238000010586 diagram Methods 0.000 description 26

- 230000003936 working memory Effects 0.000 description 26

- 238000012545 processing Methods 0.000 description 21

- 230000006870 function Effects 0.000 description 10

- 238000005516 engineering process Methods 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 238000013459 approach Methods 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000000638 solvent extraction Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0629—Configuration or reconfiguration of storage systems

- G06F3/0637—Permissions

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/14—Protection against unauthorised use of memory or access to memory

- G06F12/1458—Protection against unauthorised use of memory or access to memory by checking the subject access rights

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/0292—User address space allocation, e.g. contiguous or non contiguous base addressing using tables or multilevel address translation means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/10—Address translation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/14—Protection against unauthorised use of memory or access to memory

- G06F12/1416—Protection against unauthorised use of memory or access to memory by checking the object accessibility, e.g. type of access defined by the memory independently of subject rights

- G06F12/1425—Protection against unauthorised use of memory or access to memory by checking the object accessibility, e.g. type of access defined by the memory independently of subject rights the protection being physical, e.g. cell, word, block

- G06F12/1441—Protection against unauthorised use of memory or access to memory by checking the object accessibility, e.g. type of access defined by the memory independently of subject rights the protection being physical, e.g. cell, word, block for a range

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/14—Protection against unauthorised use of memory or access to memory

- G06F12/1458—Protection against unauthorised use of memory or access to memory by checking the subject access rights

- G06F12/1466—Key-lock mechanism

- G06F12/1475—Key-lock mechanism in a virtual system, e.g. with translation means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/40—Bus structure

- G06F13/4063—Device-to-bus coupling

- G06F13/4068—Electrical coupling

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/78—Architectures of general purpose stored program computers comprising a single central processing unit

- G06F15/7807—System on chip, i.e. computer system on a single chip; System in package, i.e. computer system on one or more chips in a single package

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/10—Protecting distributed programs or content, e.g. vending or licensing of copyrighted material ; Digital rights management [DRM]

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/062—Securing storage systems

- G06F3/0622—Securing storage systems in relation to access

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0673—Single storage device

- G06F3/0679—Non-volatile semiconductor memory device, e.g. flash memory, one time programmable memory [OTP]

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/10—Providing a specific technical effect

- G06F2212/1052—Security improvement

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/65—Details of virtual memory and virtual address translation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2213/00—Indexing scheme relating to interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F2213/0038—System on Chip

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Computer Security & Cryptography (AREA)

- Software Systems (AREA)

- Human Computer Interaction (AREA)

- Technology Law (AREA)

- Multimedia (AREA)

- Computing Systems (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Storage Device Security (AREA)

Abstract

본 발명의 실시 예에 따른 시스텝 온 칩은, 통신 프로세서, 제어 버스를 통해 상기 통신 프로세서의 보안 모드를 설정하는 응용 프로세서, 그리고 상기 통신 프로세서의 어드레스 영역(address region) 및 접근 권한(access permission)을 기반으로, 상기 통신 프로세서의 접근 제어(access control)를 설정하거나 변경하는 접근 제어 유닛을 포함한다. 본 발명의 실시 예에 따른 시스템 온 칩(SoC)은 접근 제어 유닛(access control unit)을 통해, 각 하드웨어 블록의 접근 제어 동작(access control operation)을 수행할 수 있다. 본 발명에 의하면, 다양한 시스템이 하나의 시스템 온 칩으로 통합되는 경우에, 각 시스템의 보안 속성 및 접근 권한(access permission)에 따라 접근 제어 동작을 수행할 수 있다.

Description

본 발명은 전자 장치에 관한 것으로, 좀 더 구체적으로는 접근 제어 유닛(access control unit)을 포함하는 시스템 온 칩 및 그의 동작 방법에 관한 것이다.

스마트 폰이나 테블릿 PC와 같은 모바일 장치의 이용이 증가하고 있다. 모바일 장치에는 다양한 종류의 콘텐츠를 처리하기 위한 응용 프로그램(Application Program)이 구동된다. 그리고 다양한 콘텐츠들은 비합법적인 사용자의 접근을 차단하기 위한 보안 기술이 적용된다. 이러한 콘텐츠를 보안 콘텐츠라 한다. 보안 콘텐츠의 제공자는 콘텐츠가 허가되지 않은 불법 사용이나 불법 복제로부터 보호될 수 있고, 합법적 사용자에 의해서만 재생될 수 있는 모바일 장치의 지원을 요구한다.

이러한 보안 기술은 모바일 장치의 하드웨어뿐 아니라 소프트웨어를 포함하는 시스템 전반에 걸쳐 필요하다. 이를 위해 디지털 콘텐츠 권리 관리(Digital Right Management: 이하 'DRM')라는 요구 사항이 지정되었다. 그리고 DRM은 대부분의 모바일 장치에서 구현이 의무화되어 있다. DRM의 핵심 요구 사항들을 준수하기 위해서는 허가되지 않은 접근(access)으로부터 모바일 장치의 특정 소프트웨어나 하드웨어를 보호해야 한다. 이러한 기능을 지원하는 콘텐츠 보안 방식으로 트러스트존(TrustZone)이 있다. 하지만, 운영 체제(OS)의 구조 및 코드가 공개된 스마트 폰에서는 상대적으로 보안 콘텐츠를 공격하기 용이한 면이 있다. 또한, 이러한 보안 해결책(security solution)은 TrustZone 기능을 제공하는 업체의 CPU 및 SoC 환경에 적합하며, 다른 업체의 CPU 및 SoC 환경에서 사용하는 데에는 여전히 문제가 있다.

본 발명은 상술한 기술적 과제를 해결하기 위한 것으로, 본 발명의 목적은, 다양한 시스템이 통합되는 경우 다양한 요구 조건에 대응할 수 있는 시스템 온 칩 및 그것을 포함하는 모바일 장치를 제공하는 데 있다.

본 발명의 실시 예에 따른 시스템 온 칩은, 통신 프로세서, 제어 버스를 통해 상기 통신 프로세서의 보안 모드를 설정하는 응용 프로세서, 그리고 상기 통신 프로세서의 어드레스 영역(address region) 및 접근 권한(access permission)을 기반으로, 상기 통신 프로세서의 접근 제어(access control)를 설정하거나 변경하는 접근 제어 유닛을 포함한다.

상기 접근 제어 유닛은 상기 통신 프로세서로부터 제공된 어드레스와 상기 통신 프로세서의 보안 속성을 기반으로, 외부 메모리의 메모리 영역에 대한 접근 제어를 수행한다. 상기 접근 제어 유닛은 상기 통신 프로세서가 접근하려고 하는 상기 외부 메모리의 어드레스를 입력받고, 상기 외부 메모리의 메모리 영역이 보안 영역(secure region)인지 비보안 영역(non-secure region)인지를 결정하는 어드레스 디코더를 포함한다.

상기 접근 제어 유닛은 상기 통신 프로세서로부터 제공되는 가상 주소를 상기 외부 메모리의 물리 주소로 맵핑하는 어드레스 리맵퍼를 포함한다. 상기 어드레스 리맵퍼는 가상 주소를 물리 주소로 맵핑하기 위한 변화 테이블을 포함하며, 상기 변환 테이블을 통해 상기 통신 프로세서의 접근 제어 동작을 제어한다.

상기 접근 제어 유닛은 상기 통신 프로세서의 어드레스 영역 및 접근 권한에 따라, 상기 통신 프로세서가 상기 외부 메모리로 접근하는 것을 차단하기 위한 접근 제어기를 포함한다. 상기 통신 프로세서가 아닌 제 1 프로세서를 더 포함하고, 상기 접근 제어기는 상기 통신 프로세서가 보안 마스터(secure master)인 경우에, 상기 통신 프로세서가 상기 외부 메모리의 보안 영역 중에서 상기 제 1 프로세서의 보안 영역으로 접근하는 것을 차단한다.

본 발명의 실시 예에 따른 모바일 장치는, 복수의 프로세서를 포함하는 시스템 온 칩과, 상기 시스템 온 칩에 연결되는 메모리 장치를 포함한다. 상기 시스템 온 칩은 제 1 및 제 2 프로세서를 포함하는, 상기 제 1 프로세서는 제어 버스를 통해 제 2 프로세서의 보안 모드를 설정하는, 그리고 상기 제 2 프로세서의 어드레스 영역(address region) 및 접근 권한(access permission)을 기반으로 상기 제 2 프로세서의 접근 제어(access control)를 설정하거나 변경하는 접근 제어 유닛을 포함한다. 상기 제 1 프로세서는 응용 프로세서이고, 상기 제 2 프로세서는 통신 프로세서일 수 있다. 상기 접근 제어 유닛은 상기 제 2 프로세서로부터 제공된 어드레스와 상기 제 2 프로세서의 보안 속성을 기반으로, 상기 메모리 장치의 메모리 영역에 대한 접근 제어를 수행한다.

상기 접근 제어 유닛은 어드레스 디코더, 어드레스 리맵퍼, 그리고 접근 제어기를 포함한다. 어드레스 디코더는 상기 제 2 프로세서가 접근하려고 하는 상기 메모리 장치의 어드레스를 입력 받고, 상기 메모리 장치의 메모리 영역이 보안 영역(secure region)인지 비보안 영역(non-secure region)인지를 결정한다. 상기 어드레스 리맵퍼는 상기 제 2 프로세서로부터 제공되는 가상 주소를 상기 메모리 장치의 물리 주소로 맵핑한다. 상기 접근 제어기는 상기 제 2 프로세서의 어드레스 영역 및 접근 권한에 따라, 상기 제 2 프로세서가 상기 메모리 장치로 접근하는 것을 차단한다.

본 발명의 실시 예에 따른 시스템 온 칩(SoC)은 접근 제어 유닛(access control unit)을 통해, 각 하드웨어 블록의 접근 제어 동작(access control operation)을 수행할 수 있다. 본 발명에 의하면, 다양한 시스템이 하나의 시스템 온 칩으로 통합되는 경우에, 각 시스템의 보안 속성 및 접근 권한(access permission)에 따라 접근 제어 동작을 수행할 수 있다.

도 1은 시스템 온 칩(SoC)을 포함하는 모바일 장치를 개략적으로 보여주는 블록도이다.

도 2는 도 1에 도시된 시스템 온 칩의 내부 자원을 예시적으로 보여주는 블록도이다.

도 3은 본 발명의 실시 예에 따른 모바일 장치를 보여주는 블록도이다.

도 4는 도 3에 도시된 시스템 온 칩(SoC)의 접근 제어 방법을 설명하기 위한 블록도이다.

도 5는 도 3에 도시된 시스템 온 칩의 접근 제어 방법을 예시적으로 보여주는 개념도이다.

도 6은 도 3에 도시된 시스템 온 칩의 접근 제어 방법의 다른 실시 예를 보여주는 개념도이다.

도 7은 본 발명의 다른 실시 예에 따른 모바일 장치를 보여주는 블록도이다.

도 8은 도 7에 도시된 시스템 온 칩의 접근 제어 방법을 설명하기 위한 블록도이다.

도 9는 도 7 및 도 8에 도시된 접근 제어 유닛을 예시적으로 보여주는 블록도이다.

도 10은 도 9에 도시된 접근 제어 유닛(340)의 동작 방법을 보여주는 개념도이다.

도 11은 도 9에 도시된 접근 제어 유닛(340)의 동작 방법을 예시적으로 보여주는 개념도이다.

도 12는 도 7에 도시된 모바일 장치의 접근 제어 동작을 보여주는 순서도이다.

도 13은 본 발명의 실시 예에 따른 시스템 온 칩을 포함하는 모바일 장치를 보여주는 블록도이다.

도 14는 본 발명의 실시 예에 따른 보안 기능을 수행하는 컴퓨터 시스템을 보여주는 블록도이다.

도 2는 도 1에 도시된 시스템 온 칩의 내부 자원을 예시적으로 보여주는 블록도이다.

도 3은 본 발명의 실시 예에 따른 모바일 장치를 보여주는 블록도이다.

도 4는 도 3에 도시된 시스템 온 칩(SoC)의 접근 제어 방법을 설명하기 위한 블록도이다.

도 5는 도 3에 도시된 시스템 온 칩의 접근 제어 방법을 예시적으로 보여주는 개념도이다.

도 6은 도 3에 도시된 시스템 온 칩의 접근 제어 방법의 다른 실시 예를 보여주는 개념도이다.

도 7은 본 발명의 다른 실시 예에 따른 모바일 장치를 보여주는 블록도이다.

도 8은 도 7에 도시된 시스템 온 칩의 접근 제어 방법을 설명하기 위한 블록도이다.

도 9는 도 7 및 도 8에 도시된 접근 제어 유닛을 예시적으로 보여주는 블록도이다.

도 10은 도 9에 도시된 접근 제어 유닛(340)의 동작 방법을 보여주는 개념도이다.

도 11은 도 9에 도시된 접근 제어 유닛(340)의 동작 방법을 예시적으로 보여주는 개념도이다.

도 12는 도 7에 도시된 모바일 장치의 접근 제어 동작을 보여주는 순서도이다.

도 13은 본 발명의 실시 예에 따른 시스템 온 칩을 포함하는 모바일 장치를 보여주는 블록도이다.

도 14는 본 발명의 실시 예에 따른 보안 기능을 수행하는 컴퓨터 시스템을 보여주는 블록도이다.

앞의 일반적인 설명 및 다음의 상세한 설명 모두 예시적이라는 것이 이해되어야 하며, 청구된 발명의 부가적인 설명이 제공되는 것으로 여겨져야 한다. 참조 부호들이 본 발명의 바람직한 실시 예들에 상세히 표시되어 있으며, 그것의 예들이 참조 도면들에 표시되어 있다. 가능한 어떤 경우에도, 동일한 참조 번호들이 동일한 또는 유사한 부분을 참조하기 위해서 설명 및 도면들에 사용된다.

이하에서는, 시스템 온 칩(SoC)이 본 발명의 특징 및 기능을 설명하기 위한 단위의 예로서 사용될 것이다. 하지만, 이 기술 분야에서 통상의 지식을 가진 사람은 여기에 기재된 내용에 따라 본 발명의 다른 이점들 및 성능을 쉽게 이해할 수 있을 것이다. 본 발명은 다른 실시 예들을 통해 또한, 구현되거나 적용될 수 있을 것이다. 게다가, 상세한 설명은 본 발명의 범위, 기술적 사상 그리고 다른 목적으로부터 상당히 벗어나지 않고 관점 및 응용에 따라 수정되거나 변경될 수 있다.

도 1은 시스템 온 칩(SoC)을 포함하는 모바일 장치를 개략적으로 보여주는 블록도이다. 도 1은 시스템 온 칩(SoC)의 기술 발달로 인해, 별도의 칩으로 존재한 시스템들이 하나의 시스템 온 칩으로 통합되는 예를 보여준다.

도 1을 참조하면, 도 1(A)의 모바일 장치(10)는 응용 프로세서(11), 모뎀(12), 블루투스(13), GNSS(Global Navigation Satellite System, 14), 와이파이(15)를 포함한다. 도 1(A)의 모바일 장치(10)에서는 각각의 시스템들이 별도의 칩으로 존재한다. 도 1(A)의 모바일 장치(10) 내에서 별도의 칩으로 존재한 여러 시스템들이, 기술의 발달로 인해, 도 1(B)에서 보는 바와 같이 하나의 시스템 온 칩(110)으로 통합되고 있다. 도 1(B)의 모바일 장치(100)에서는 하나의 시스템 온 칩(110) 내에, 응용 프로세서(AP), 모뎀(120), 블루투스(130), GNSS(140), 그리고 Wifi(150) 등이 포함되어 있다.

도 1(B)의 모바일 장치(100)는 이들 시스템들의 동작을 위해 필요한 내부 자원(internal resource)을 포함할 수 있다. 내부 자원에는 시스템 온 칩(110)의 내부 메모리(internal memory) 또는 각 시스템의 동작을 위한 슬레이브 셋팅 레지스터(slave setting registers)들이 포함될 수 있다. 그리고 시스템 온 칩(110)의 외부에는 DRAM과 같은 외부 메모리(external memory) 또는 플래시 메모리를 기반으로 하는 저장 장치(storage device) 등이 포함될 수 있다.

도 2는 도 1에 도시된 시스템 온 칩의 내부 자원을 예시적으로 보여주는 블록도이다. 시스템 온 칩(110)에는 응용 프로세서(AP, 111), 모뎀(120), 블루투스(130), GNSS(140), 그리고 Wifi(150) 등과 같은 하드웨어 블록(H/W block)이 포함될 수 있다. 이들 하드웨어 블록은 시스템 온 칩(110)에서 마스터(master)로 동작할 수 있다.

또한, 시스템 온 칩(110)의 하드웨어 블록에는 마스터(master)의 동작에 필요한 여러 슬레이브(slave)가 포함될 수 있다. 슬레이브(slave)는 버스를 통해 마스터(master)와 연결될 수 있다. 예로서, 슬레이브(slave)에는 공통 보안 슬레이브(common secure slave, 151), AP 전용 슬레이브(AP only slave, 152), 모뎀 전용 슬레이브(modem only slave, 153), GNSS 전용 슬레이브(GNSS only slave, 154), 공통 슬레이브(common slave, 155) 등이 포함될 수 있다.

도 2에 도시된 시스템 온 칩(110)의 각각의 하드웨어 블록에는 보안 속성(secure property) 또는 접근 권한(access permission)이 설정될 수 있다. 즉, 각각의 하드웨어 블록은 비보안 모드(non-secure mode) 또는 보안 모드(secure mode)로 설정될 수 있다. 마스터들은 비보안 모드로 설정된 슬레이브에 접근할 수 있다. 그러나 슬레이브가 보안 모드로 설정된 경우에는, 마스터의 보안 속성에 따라 접근이 제한될 수 있다.

예를 들면, 공통 보안 슬레이브(common secure slave, 151)는 보안 모드(secure mode)로 설정되어 있다. 보안 마스터(secure master)는 비보안 슬레이브(non-secure slave)나 보안 슬레이브(secure slave)에 접근할 수 있다. 모뎀(120)이 보안 마스터인 경우에, 모뎀(120)은 공통 보안 슬레이브(151)에 접근할 수 있다.

AP 전용 슬레이브(152), 모뎀 전용 슬레이브(153), 그리고 GNSS 전용 슬레이브(154)는 비보안 모드(non-secure mode)로 설정되어 있다. AP(111)는 AP 전용 슬레이브(152)를 독점하여 사용할 수 있다. 마찬가지로, 모뎀(120)은 모뎀 전용 슬레이브(153)를 독점하여 사용할 수 있고, GNSS(140)는 GNSS 전용 슬레이브(154)를 독점하여 사용할 수 있다. 한편, 공통 슬레이브(common slave, 155)는 비보안 모드로 설정되어 있기 때문에, 모든 마스터들은 공통 슬레이브(155)를 공유하여 사용할 수 있다.

도 1 및 도 2에 도시된 바와 같이, 하나의 시스템 온 칩(110)에 응용 프로세서(111), 모뎀(120), 블루투스(130), GNSS(140), 그리고 와이파이(150) 등과 같은 여러 가지 시스템이 통합되고 있다. 여러 시스템들이 통합되면서, 보안 문제도 복잡하고 중요해지고 있다. 보안 문제로 인해, 시스템 온 칩(110)의 내부 자원에 대한 접근 제어(access control)가 필요하다.

본 발명의 실시 예에 따른 시스템 온 칩(SoC)은 여러 시스템들이 통합된 환경에서, 그 용도가 단순한 경우에 어드레스 영역(address region)을 기반으로 접근 제어(access control)를 수행할 수 있다. 또한, 본 발명의 실시 예에 따른 시스템 온 칩(SoC)은 어드레스 영역(address region)뿐만 아니라 접근 권한(access permission)을 기반으로 접근 제어를 수행할 수 있다. 본 발명의 시스템 온 칩(SoC)은 동작 모드에 따라 어드레스 영역(address region)을 기반으로 접근 제어를 하거나, 또는 어드레스 영역 및 접근 권한(address region and access permission)을 기반으로 접근 제어를 수행할 수도 있다.

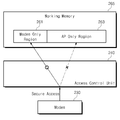

도 3은 본 발명의 실시 예에 따른 모바일 장치를 보여주는 블록도이다. 도 3을 참조하면, 본 발명의 실시 예에 따른 모바일 장치(200)는 시스템 온 칩(SoC, 201), 워킹 메모리(265), 그리고 저장 장치(275)를 포함한다. 도 3에 도시된 시스템 온 칩(201)은 어드레스 영역(address region)을 기반으로 접근 제어를 수행할 수 있다.

시스템 온 칩(201)은 프로세싱 유닛(210), 하드웨어 블록(230), 접근 제어 유닛(240), 그리고 내부 메모리(280)를 포함할 수 있다. 또한, 시스템 온 칩(201)은 외부의 워킹 메모리(265)를 제어하기 위한 메모리 컨트롤러(260)와, 외부의 저장 장치(275)를 제어하기 위한 스토리지 컨트롤러(270)를 포함할 수 있다. 여기에서, 워킹 메모리(265)는 DRAM과 같은 랜덤 액세스 메모리(RAM)로 구현되고, 저장 장치(275)는 플래시 메모리를 기반으로 하는 메모리 카드나 USB 등과 같은 저장 매체로 구현될 수 있다.

계속해서 도 3을 참조하면, 프로세싱 유닛(processing unit, 210)은 애플리케이션(application) 또는 운영 체제(OS)와 같은 소프트웨어를 동작하기 위한 중앙처리장치(CPU)일 수 있다. 프로세싱 유닛(210)은 소프트웨어나 프로그램을 동작시킬 뿐 아니라, 다양한 하드웨어 블록(230)을 직접 구동하거나, 하드웨어 블록(230)을 구동하기 위한 하드웨어 드라이버(Hardware driver)를 제어할 수 있다.

프로세싱 유닛(210)은 하드웨어 블록(230)을 보안 모드(secure mode) 또는 비보안 모드(non-secure mode)로 설정할 수 있다. 또한, 프로세싱 유닛(210)은 메모리 컨트롤러(260)를 제어함으로, 워킹 메모리(265)의 어드레스 영역을 보안 영역(secure region) 또는 비보안 영역(non-secure region)으로 설정할 수 있다. 마찬가지로, 프로세싱 유닛(210)은 외부의 저장 장치(275)나 내부 메모리(280)의 어드레스 영역을 보안 영역이나 비보안 영역으로 설정할 수 있다.

프로세싱 유닛(210)은 보안 상태 비트(secure state bit)를 참조하여 하드웨어 블록(230)에 대한 보안 모드를 설정할 수 있다. 프로세싱 유닛(210)의 보안 모드 설정은 제어 버스(220)를 통해서 이루어질 수 있다. 제어 버스(220)는 프로세싱 유닛(210)이 하드웨어 블록(230)을 제어하는 제어 경로를 제공한다. 프로세싱 유닛(210)은 제어 버스(220)를 통해 하드웨어 블록(230)의 접근 제어(access control)를 제어할 수 있다.

하드웨어 블록(230)은 도 2에 도시된, 모뎀(modem), GNSS, 와이파이, 블루투스와 같은 프로세서(processor) 또는 시스템일 수도 있다. 이러한 시스템들은 시스템 온 칩(201)에서 마스터(master)로 동작할 수 있다. 하드웨어 블록(230)은 마스터의 동작에 필요한 슬레이브들을 포함할 수 있다. 이러한 하드웨어 블록(230)은 보안 모드와 비보안 모드로 나뉘어 관리될 수 있다.

한편, 하드웨어 블록(230)은 제공된 콘텐츠를 실질적으로 재생하기 위한 구성일 수 있다. 예를 들면, 하드웨어 블록(230)은 압축된 콘텐츠 데이터(Contents data)를 디코딩하고 그 결과로 동영상이나 음원 신호로 출력하는 코덱일 수 있다. 하드웨어 블록(230)은 이미지의 포맷이나 크기를 모바일 장치에 적합한 형태로 변환하는 이미지 컨버터일 수 있다.

접근 제어 유닛(240)은 하드웨어 블록(230)과 데이터 버스(250) 사이에서 하드웨어 블록(230)이 접근하는 영역을 제어할 수 있다. 접근 제어 유닛(240)은 보안 영역에서 전적으로 관리될 수 있다. 그리고 접근 제어 유닛(240)은 어드레스 맵핑 테이블(address mapping Table)을 포함할 수 있다. 어드레스 맵핑 테이블에는 하드웨어 블록(230)이 접근하려는 어드레스 영역이 맵핑되어 있다. 접근 제어 유닛(240)은 보안 운영 체제(secure OS)가 수행 중인 때에, 보안 모드로 동작하는 하드웨어 블록에 대한 접근을 허용하거나 차단할 수 있다.

접근 제어 유닛(240)은 프로세싱 유닛(210)의 제어에 따라 하드웨어 블록(230)의 보안 속성을 설정하거나 변경할 수 있다. 또한, 접근 제어 유닛(240)은 프로세싱 유닛(210)의 제어에 따라, 내부 메모리(280)뿐만 아니라, 외부의 워킹 메모리(265)나 저장 장치(275)의 보안 속성도 설정하거나 변경할 수 있다. 접근 제어 유닛(240)은 시스템 온 칩 내부의 하드웨어 블록들의 보안 속성을 설정하기 위한 기능을 포함한다.

접근 제어 유닛(240)은 시스템 온 칩(SOC)에 의해서 접근되는 워킹 메모리(DRAM, 165)의 보안 속성도 선택적으로 제어할 수 있다. 예를 들면, 접근 제어 유닛(240)은 ARM사의 TrustZone의 기능을 포함할 수 있다. 접근 제어 유닛(240)은 하드웨어 IP에 대한 보안 속성과 워킹 메모리(DRAM, 165)에 대한 보안 속성을 보안 모드와 비보안 모드로 구분해서 관리할 수 있다.

데이터 버스(250)는 프로세싱 유닛(210)이나 하드웨어 블록(230)에 의한 접근 경로를 제공한다. 데이터 버스(250)를 통해서 프로세싱 유닛(210)과 하드웨어 블록(230)은 시스템 온 칩(201) 외부의 워킹 메모리(DRAM, 265)에 접근할 수 있다. 보안 콘텐츠를 처리하기 위해서, 하드웨어 블록(230)은 데이터 버스(250)를 통해 데이터를 읽어와 처리할 수 있다. 처리된 데이터는 데이터 버스(250)를 통해 워킹 메모리(DRAM, 265)의 지정된 어드레스 영역에 저장될 수 있다.

메모리 컨트롤러(260)는 시스템 온 칩(SoC, 201) 외부의 워킹 메모리(DRAM, 265)의 동작을 제어할 수 있다. 메모리 컨트롤러(260)를 통해, 워킹 메모리(265)에는 다양한 데이터가 로드될 수 있다. 예를 들면, 운영 체제나 하드웨어를 구동하기 위한 드라이버들이 로드될 수 있다.

워킹 메모리(265)의 메모리 영역은 보안 영역과 비보안 영역으로 구별될 수 있다. 이러한 영역의 분리는 접근 제어 유닛(240)의 워킹 메모리 속성을 정의하는 기능을 통해서 구현될 수 있다. 보안 콘텐츠는 디코딩 과정을 거친 후에는 워킹 메모리(265)의 보안 영역(secure region)에 저장될 수 있다.

스토리지 컨트롤러(270)는 시스템 온 칩(SoC, 201) 외부의 저장 장치(275)의 동작을 제어할 수 있다. 여기에서, 저장 장치(275)는 이미지 데이터나 동영상 데이터 등과 같은 대용량의 사용자 데이터를 저장할 수 있다. 저장 장치(275)는 모바일 장치(200) 내에 집적되거나, 모바일 장치(200)와 착탈 가능한 형태로 구현될 수 있다. 저장 장치(275)는 플래시 메모리를 기반으로 하는 저장 매체일 수 있다.

내부 메모리(internal memory, 280)는 시스템 온 칩(201)의 내부에 위치한 메모리로, SRAM이나 ROM 등을 포함한다. 워킹 메모리(265)와 마찬가지로, 내부 메모리(280)와 저장 장치(275)의 메모리 영역은 보안 영역과 비보안 영역으로 나뉘어 관리될 수 있다. 이러한 메모리 영역의 분리는 접근 제어 유닛(240)의 메모리 속성을 정의하는 기능을 통해서 구현될 수 있다.

도 3에 도시된 시스템 온 칩(SoC, 201)의 하드웨어 블록(230)은 외부의 워킹 메모리(265)나 저장 장치(275), 또는 내부 메모리(280)를 공유(share)하여 사용할 수 있다. 예를 들면, 하드웨어 블록(230)의 마스터는 외부의 워킹 메모리(265)를 공유하여 사용할 수 있다. 또는, 시스템 온 칩(SoC)의 하드웨어 블록(예를 들면, 모뎀)은 위의 메모리 자원(memory resource)들과 내부의 여러 자원들(예를 들면, peripheral IP)을 공유하여 사용할 수 있다. 시스템 온 칩(SoC)이 어떤 용도로 사용되고 어떤 기능을 지원하느냐에 따라, 내부 시스템 구성 및 자원의 공유 구조가 달라질 수 있다.

도 4는 도 3에 도시된 시스템 온 칩(SoC)의 접근 제어 방법을 설명하기 위한 블록도이다. 도 4를 참조하면, 접근 제어 유닛(240)은 어드레스 영역을 기반으로, 워킹 메모리(265)에 대한 접근 제어를 수행할 수 있다.

예로서, 워킹 메모리(265)의 메모리 영역은 모뎀 전용 영역(modem only region, 261), 공통 보안 영역(common secure region, 262), AP 전용 영역(AP only region, 263), 비보안 영역(non-secure region, 264)으로 구분될 수 있다. 여기에서, 공통 보안 영역(262)은 보안 영역(secure region)이고, 나머지 메모리 영역은 비보안 영역(non-secure region)이다.

모뎀 전용 영역(261)은 모뎀이 독점하여 사용할 수 있고, AP 전용 영역(263)은 응용 프로세서(AP)가 독점하여 사용할 수 있다. 공통 보안 영역(262)은 보안 마스터(secure master)가 사용할 수 있다. 그리고 비보안 영역(264)은 모든 마스터가 공유하여 사용할 수 있다.

도 5는 도 3에 도시된 시스템 온 칩의 접근 제어 방법을 예시적으로 보여주는 개념도이다. 도 5는 어드레스 영역(address region)을 기반으로 워킹 메모리(265)에 대한 접근 제어 동작을 수행하는 방법을 보여준다.

도 5를 참조하면, 모뎀(230)은 접근 제어 유닛(240)을 통해 워킹 메모리(265)의 메모리 영역에 접근할 수 있다. 모뎀(230)이 보안 마스터(secure master)인 경우에도, 접근 제어 유닛(240)은 워킹 메모리(265)에 대한 접근을 허용하거나 차단할 수 있다. 예를 들어, 워킹 메모리(265)의 메모리 영역은 모뎀 전용 영역(261)과 AP 전용 영역(263)을 포함할 수 있다. 접근 제어 유닛(240)은 모뎀(230)이 접근하려고 하는 메모리 영역이 모뎀 전용 영역(261)인 경우에는 보안 접근(secure access)를 허용하고, AP 전용 영역(263)인 경우에는 보안 접근을 차단할 수 있다.

도 6은 도 3에 도시된 시스템 온 칩의 접근 제어 방법의 다른 실시 예를 보여주는 개념도이다. 도 6은 접근 제어 유닛(240)이 어드레스 영역을 기반으로 슬레이브에 대한 접근 제어 동작을 수행하는 방법을 보여준다.

도 6을 참조하면, 모뎀(230)은 접근 제어 유닛(240)을 통해, 슬레이브에 접근할 수 있다. 모뎀(230)이 보안 마스터(secure master)인 경우에도, 접근 제어 유닛(240)은 슬레이브에 대한 접근을 허용하거나 차단할 수 있다. 예로서, 슬레이브는 모뎀 전용 슬레이브(251)와 AP 전용 슬레이브(252)를 포함할 수 있다. 접근 제어 유닛(240)은 모뎀(230)이 접근하려고 하는 슬레이브가 모뎀 전용 슬레이브(251)인 경우에는 보안 접근(secure access)을 허용하고, AP 전용 슬레이브(252)인 경우에는 보안 접근을 차단할 수 있다.

도 7은 본 발명의 다른 실시 예에 따른 모바일 장치를 보여주는 블록도이다. 도 7을 참조하면, 본 발명의 실시 예에 따른 모바일 장치(300)는 시스템 온 칩(SoC, 301), 워킹 메모리인 DRAM(365), 그리고 저장 장치(375)를 포함한다. 도 7에 도시된 시스템 온 칩(301)은 어드레스 영역(address region) 및 접근 권한(access permission)을 기반으로 접근 제어를 수행할 수 있다.

시스템 온 칩(301)은 응용 프로세서(AP, 310)와 통신 프로세서(CP, 330)를 포함할 수 있다. 통신 프로세서(CP, 330)는 모뎀일 수 있다. 여기에서, 시스템 온 칩(301)의 동작 방법은 모뎀(330) 이외에, 와이파이(Wif)나 GNSS 등과 같은 다른 하드웨어 블록에 대해서도 적용될 수 있다.

응용 프로세서(310)는 제어 버스(320)를 통해 서브 시스템인 통신 프로세서(CP, 330)의 보안 모드(secure mode)를 설정할 수 있다. 예를 들면, 응용 프로세서(AP, 310)는 제어 버스(320)를 통해 모뎀(330)을 보안 마스터(secure master)로 설정할 수 있다. 응용 프로세서(310)는 처리할 콘텐츠의 종류 또는 서브 시스템의 종류에 따라 제어 유닛들(TZPC, TZASC)을 설정할 수 있다.

TZPC는 하드웨어 블록들의 보안 속성을 설정하기 위한 제어 유닛이다. TZPC는 보안 소프트웨어와 일반 소프트웨어에 의한 논리적 분할을 주변 장치(Peripheral IP)에 적용하기 위한 트러스트존(TrustZone) 방식의 시스템 온 칩의 구성이다. TZPC를 통해 하드웨어 블록들의 보안 속성이 보안 모드 또는 비보안 모드로 설정될 수 있다.

TZASC는 워킹 메모리의 보안 설정을 위한 제어 유닛이다. TZASC는 DRAM(365)의 메모리 영역별 속성을 보안 영역과 비보안 영역으로 분리하기 위한 구성이다. DRAM(365)에 저장되는 데이터 중에는, 보안 영역으로 관리되어야 하는 데이터와 비보안 영역으로 관리되어도 되는 데이터가 있다. 디코딩된 모든 보안 콘텐츠에 대응하는 데이터는 TZASC에 의해서 보안 영역에서 관리된다. 그리고 접근 제어 유닛들(340)의 접근 경로를 정의하는 변환 테이블(translation table)도 DRAM(365)의 보안 영역에서 관리될 수 있다.

모뎀(330)과 데이터 버스(350) 사이에는 접근 제어 유닛(340)이 위치할 수 있다. 접근 제어 유닛(340)은 모뎀(330)의 접근 제어(access control)를 관리할 수 있다. 마찬가지로, 하드웨어 블록이 와이파이인 경우에는 와이파이와 데이터 버스(350) 사이에는 와이파이용 접근 제어 유닛이 위치할 수 있다. 그리고 GNSS와 데이터 버스(350) 사이에는 GNSS용 접근 제어 유닛이 위치할 수 있다. 또한, 접근 제어 유닛(340)은 각각의 하드웨어 블록에 대한 접근 제어 동작을 개별적으로 관리하거나, 여러 하드웨어 블록을 통합하여 포괄적으로 관리할 수 있다.

데이터 버스(350)는 응용 프로세서(310)나 모뎀(330) 등의 메모리 접근 경로를 제공한다. 데이터 버스(350)를 통해서 시스템 온 칩(301)의 외부에 위치하는 DRAM(365)이나 저장 장치(375)에 대한 접근이 이루어진다. 물론, 데이터 버스(350)는 시스템 온 칩(301)의 내부 메모리(380)에 대한 접근 경로를 제공할 수 있다.

시스템 온 칩(301)은 외부의 DRAM(365)를 제어하기 위한 DRAM 컨트롤러(360), 외부의 저장 장치(375)를 제어하기 위한 스토리지 컨트롤러(370), 그리고 내부 메모리(380)를 포함할 수 있다. 여기에서, 저장 장치(375)는 플래시 메모리를 기반으로 하는 메모리 카드나 USB 등과 같은 저장 매체일 수 있다. 그리고 내부 메모리(380)는 SRAM과 같은 랜덤 접근 메모리, ROM, 또는 PRAM과 같은 불휘발성 메모리로 구현될 수 있다.

도 8은 도 7에 도시된 시스템 온 칩의 접근 제어 방법을 설명하기 위한 블록도이다. 도 8을 참조하면, 모뎀(330)은 접근 제어 유닛(340)을 통해 DRAM(365)에 접근할 수 있다. 접근 제어 유닛(340)은 어드레스 영역(address region) 및 접근 권한(access permission)을 기반으로, DRAM(365)의 메모리 영역에 대한 접근 제어(access control)를 수행할 수 있다.

예를 들면, DRAM(365)의 메모리 영역은 GNSS 보안 전용 영역(GNSS secure only region, 366), AP 전용 영역(AP only region, 367), 공유된 영역(shared region, 368), 및 모뎀 보안 전용 영역(modem secure only region, 369)으로 구분될 수 있다. 여기에서, 보안 영역(secure region)에는 보안 마스터(secure master)가 접근할 수 있다. 그리고 비보안 영역(non-secure region)에는 보안 마스터뿐만 아니라 비보안 마스터(non-secure master)도 접근할 수 있다.

GNSS 보안 전용 영역(366)은 보안 영역(secure region)이고, GNSS가 보안 마스터(secure master)인 경우에 접근할 수 있다. 모뎀(330)이 보안 마스터(secure master)인 경우라 하더라도, 모뎀(330)은 GNSS 보안 전용 영역(366)에 접근할 수 없다. AP 전용 영역(367)은 비보안 영역이고 AP만이 접근할 수 있다. 공유된 영역(368)은 비보안 영역이고, 모든 마스터들이 접근할 수 있다. 모뎀 보안 전용 영역(369)은 보안 영역(secure region)이고, 모뎀(330)이 보안 마스터(secure master)인 경우에 접근할 수 있다.

도 9는 도 7 및 도 8에 도시된 접근 제어 유닛을 예시적으로 보여주는 블록도이다. 접근 제어 유닛(340)은 어드레스 영역(address region) 및 접근 권한(access permission)을 기반으로, 모뎀(330)의 접근 제어(access control)를 수행할 수 있다.

도 9를 참조하면, 접근 제어 유닛(340)은 어드레스 디코더(341), 어드레스 리맵퍼(342), 접근 제어기(345), 선택기(348), 그리고 제어부(349)을 포함한다. 접근 제어 유닛(340)은 모뎀(330)으로부터 제공된 어드레스(address)와 모뎀(330)의 보안 속성을 기반으로, DRAM(365)의 메모리 영역에 대한 접근 제어(access control)를 수행할 수 있다.

어드레스 디코더(341)는 모뎀(330)이 접근하려는 DRAM(365)의 어드레스를 입력받고, 보안 영역(secure region)인지 비보안 영역(non-secure region)을 결정한다. 비보안 영역인 경우에는, A 경로를 통해, 비보안 접근 제어(non-secure access control) 동작이 수행된다. 보안 영역인 경우에는, B 경로를 통해, 보안 접근 제어(secure access control) 동작이 수행된다.

어드레스 리맵퍼(342)는 보안 어드레스 리맵퍼(343)과 비보안 어드레스 리맵퍼(344)를 포함한다. 어드레스 리맵퍼(342)는 가상 주소를 물리 주소로 맵핑하기 위한 어드레스 맵핑 테이블을 포함할 수 있다. 어드레스 리맵퍼(342)는 모뎀(330)으로부터 출력되는 가상 주소를 DRAM(365)의 물리 주소로 맵핑할 수 있다.

만일, 일반 운영 체제(OS)의 수행 중에, 응용 프로세서(310)가 비보안 마스터(non-secure master)인 상태로 모뎀(330)에 접근하더라도, 모뎀(330)의 보안 트랜잭션이 실제로 접근할 수 있는 곳은 어드레스 리맵퍼(342)에 의해서 맵핑된 메모리 영역에 국한된다. 따라서, 모뎀(330)의 접근 제어(access control)는 어드레스 리맵퍼(342)의 변환 테이블(translation table)의 설정을 통해서 차단될 수 있다. 여기서, 어드레스 리맵퍼(342)의 변환 테이블(translation table)은 DRAM(365)의 보안 영역(secure region)에서 관리될 수 있다.

접근 제어기(345)는 모뎀(330)의 어드레스 영역(address region) 및 접근 권한(access permission)에 따라, 모뎀(330)의 접근을 차단할 수 있다. 접근 제어기(345)는 제어부(349)에 의해 제어된다. 접근 제어기(345)는 보안 접근 제어기(346)과 비보안 접근 제어기(347)를 포함한다. 모뎀(330)이 보안 접근(secure access)인 경우에, 보안 접근 제어기(346)는 모뎀(330)이 아닌 다른 시스템(예를 들면, GNSS)의 보안 접근을 차단할 수 있다.

선택기(348)는 어드레스 디코더(341) 또는 제어부(349)으로부터 모뎀(330)이 접근하려는 어드레스 영역을 입력 받을 수 있다. 선택기(348)는 모뎀(330)의 보안 접근 제어 동작 또는 비보안 접근 제어 동작 중에서 어느 하나를 선택적으로 제공할 수 있다. 제어부(349)는 어드레스 디코더(341), 어드레스 리맵퍼(342), 접근 제어기(345), 그리고 선택기(348)의 동작을 제어할 수 있다.

도 10은 도 9에 도시된 접근 제어 유닛(340)의 동작 방법을 보여주는 개념도이다. 도 10에서, 모뎀(330)은 보안 접근(secure access)을 수행하는 것으로 가정한다. 모뎀(330)이 보안 마스터(secure master)인 경우에는 도 9에 도시된 B 경로를 통해 보안 접근 동작이 수행된다.

도 10을 참조하면, 모뎀(330)은 접근 제어 유닛(340)을 통해 DRAM(365)의 메모리 영역에 접근할 수 있다. 예로서, DRAM(365)의 메모리 영역은 GNSS 보안 전용 영역(366), AP 전용 영역(367), 공유된 영역(shared region, 368), 및 모뎀 보안 전용 영역(modem secure only region, 369)을 포함한다. 여기에서, 모뎀(330)은 보안 마스터(secure master)이기 때문에, DRAM(365)의 비보안 영역(non-secure region)과 보안 영역(secure region)에 접근할 수 있다.

그러나 GNSS 보안 전용 영역(366)은 보안 영역(secure region)이고, GNSS만 접근할 수 있다. 따라서 모뎀(330)이 보안 마스터(secure master)인 경우라 하더라도, 모뎀(330)은 GNSS 보안 전용 영역(366)에 접근할 수 없다. 접근 제어 유닛(340)은 모뎀(330)이 GNSS 보안 전용 영역(366)에 접근하려고 하는 경우에 이를 차단할 수 있다. 이때 접근 제어 유닛(340)은 보안 접근 제어기(346)를 통해 모뎀(330)의 접근을 차단할 수 있다.

AP 전용 영역(367)은 비보안 영역(non-secure region)이지만, AP만이 접근할 수 있다. 접근 제어 유닛(340)은 모뎀(330)의 AP 전용 영역(367)으로 접근을 차단할 수 있다. 이때 접근 제어 유닛(340)은 보안 어드레스 리맵퍼(343)를 이용하여 모뎀(330)의 접근을 차단할 수 있다. 또한, 접근 제어 유닛(340)은 보안 접근 제어기(346)를 통해 모뎀(330)의 접근을 차단할 수도 있다.

공유된 영역(368)은 비보안 영역이고, 모든 마스터들이 접근할 수 있다. 따라서 모뎀(330)은 공유된 영역(368)에 접근할 수 있다. 모뎀 보안 전용 영역(369)은 보안 영역(secure region)이고, 모뎀(330)이 보안 마스터(secure master)이기 때문에 접근할 수 있다.

도 11은 도 9에 도시된 접근 제어 유닛(340)의 동작 방법을 예시적으로 보여주는 개념도이다. 도 11에서, 모뎀(330)은 보안 접근(secure access)을 수행하는 것으로 가정한다. 모뎀(330)이 보안 마스터(secure master)인 경우에는 도 9에 도시된 B 경로를 통해 보안 접근 동작이 수행된다.

도 11을 참조하면, 모뎀(330)은 접근 제어 유닛(340)을 통해 슬레이브 들에 접근할 수 있다. 예로서, 슬레이브에는 GNSS 보안 전용 슬레이브(351), AP 전용 슬레이브(352), 공통 보안 전용 슬레이브(353), 그리고 모뎀 전용 슬레이브(354)가 있다. 모뎀(330)은 보안 마스터(secure master)이기 때문에, 보안 슬레이브(secure slave)와 비보안 슬레이브(non-secure slave)에 접근할 수 있다.

그러나 GNSS 보안 전용 슬레이브(351)은 보안 슬레이브(secure slave)이고, GNSS만 접근할 수 있다. 따라서 모뎀(330)이 보안 마스터(secure master)인 경우라 하더라도, 모뎀(330)은 GNSS 보안 전용 슬레이브(351)에 접근할 수 없다. 접근 제어 유닛(340)은 모뎀(330)이 GNSS 보안 전용 슬레이브(351)에 접근하려고 하는 경우에 이를 차단할 수 있다. 이때 접근 제어 유닛(340)은 보안 접근 제어기(346)를 이용하여 모뎀(330)의 접근을 차단할 수 있다.

AP 전용 슬레이브(352)는 비보안 슬레이브(non-secure slave)이고, AP만이 접근할 수 있다. 접근 제어 유닛(340)은 모뎀(330)의 AP 전용 슬레이브(352)로 접근하는 것을 차단할 수 있다. 이때 접근 제어 유닛(340)은 보안 어드레 리맵퍼(343)를 이용하여 모뎀(330)의 접근을 차단할 수 있다. 또한, 접근 제어 유닛(340)은 보안 접근 제어기(346)를 통해 모뎀(330)의 접근을 차단할 수도 있다.

공통 보안 전용 슬레이브(353)는 보안 슬레이브이고, 모든 마스터들이 접근할 수 있다. 따라서 모뎀(330)은 공통 보안 전용 슬레이브(353)에 접근할 수 있다. 모뎀 전용 슬레이브(354)는 비보안 슬레이브이고, 모뎀(330)은 접근할 수 있다.

도 12는 도 7에 도시된 모바일 장치의 접근 제어 동작을 보여주는 순서도이다. 모바일 장치(300)가 파워 온 되면, OS 부팅 동작이 수행된다. 그리고 보안 OS(secure OS)가 준비된다.

S110 단계에서, 보안 정책(secure policy)을 결정한다. 보안 정책은 ROT(root of trust)에 의해 수행된다. 접근 제어 유닛(340)은 ROT의 보안 정책에 따라, 보안 접근(secure access)인지 비보안 접근(non-secure access)인지를 결정한다.

S120 단계에서, 자원 오너(resource owner)는 각각의 하드웨어 블록을 위한 공유 자원(sharable resources)를 체크한다. 여기에서, 자원 오너(resource owner)는 ROT이거나, 보안 마스터(secure master)일 수 있다. 보안 마스터는 ROT로부터 접근 권한(access permission)을 얻을 수 있다.

비보안 마스터(non-secure master)는 기본적으로 비보안 자원들(non-secure resources)을 셋팅할 수 있다. 다만, 자원 오너(resource owner)는 비보안 마스터(non-secure master)인 경우에도, ROT가 추가로 필요한 경우에 비보안 마스터에 접근 권한을 줄 수 있다.

S130 단계에서, 공유 자원(sharable resource)의 접근을 인에블하기 위해 각 하드웨어 블록의 셋팅을 제어한다. S140 단계에서, 하드웨어 블록의 동작을 시작한다. S150 단계에서, 공유 자원(sharable resources)에 변화가 있는지를 판단한다. 공유 자원에 변화가 없는 경우(No)에는 S160 단계가 수행된다. 공유 자원에 변화가 있는 경우(Yes)에는 S120 단계가 다시 수행된다. S160 단계에서, 마지막 동작인지를 판단한다. 마지막 동작이면(Yes) 파워 오프하고, 마지막 동작이 아니면(No), S140 단계가 다시 수행된다.

본 발명의 실시 예에 따른 시스템 온 칩(SoC)은 접근 제어 유닛(access control unit)을 통해, 각 하드웨어 블록의 접근 제어 동작(access control operation)을 수행할 수 있다. 본 발명에 의하면, 다양한 시스템이 하나의 시스템 온 칩으로 통합되는 경우에, 각 시스템의 보안 속성 및 접근 권한(access permission)에 따라 접근 제어 동작을 수행할 수 있다. 본 발명은 다양한 시스템이 통합되는 경우, 다양한 요구 조건에 대응할 수 있는 유연한 접근 방법 및 장치를 제공할 수 있다.

도 13은 본 발명의 실시 예에 따른 시스템 온 칩을 포함하는 모바일 장치를 보여주는 블록도이다. 도 13을 참조하면, 본 발명의 실시 예에 따른 휴대용 단말기(1000)는 이미지 처리부(1100), 무선 송수신부(1200), 오디오 처리부(1300), 이미지 파일 생성부(1400), SRAM(1500), 유저 인터페이스(1600), 그리고 컨트롤러(1700)를 포함한다.

이미지 처리부(1100)는 렌즈(1110), 이미지 센서(1120), 이미지 프로세서(1130), 그리고 디스플레이부(1140)를 포함한다. 무선 송수신부(1200)는 안테나(1210), 트랜시버(1220), 모뎀(1230)을 포함한다. 오디오 처리부(1300)는 오디오 프로세서(1310), 마이크(1320), 그리고 스피커(1330)를 포함한다. 휴대용 단말기(1000)에는 다양한 종류의 반도체 장치들이 포함될 수 있다. 특히, 컨트롤러(1700)의 기능을 수행하는 시스템 온 칩의 경우 저전력, 고성능이 요구된다.

도 14는 본 발명의 실시 예에 따른 보안 기능을 수행하는 컴퓨터 시스템을 보여주는 블록도이다. 도 14를 참조하면, 컴퓨터 시스템(2000)은 시스템 버스(2060)에 전기적으로 연결되는 비휘발성 메모리 장치(2010), 중앙처리장치(2020), 램(2030)을 포함할 수 있다. 그리고 컴퓨팅 시스템(2000)은 시스템 버스(2060)에 전기적으로 연결된 사용자 인터페이스(2040), 베이스밴드 칩셋(Baseband chipset)과 같은 모뎀(2050)을 포함한다.

본 발명에 따른 컴퓨팅 시스템(2000)이 모바일 장치인 경우, 컴퓨팅 시스템(2000)의 동작 전압을 공급하기 위한 배터리(미도시됨)가 추가적으로 제공될 것이다. 비록 도면에는 도시되지 않았지만, 본 발명에 따른 컴퓨팅 시스템(2000)에는 응용 칩셋(Application chipset), 카메라 이미지 프로세서(Camera Image Processor: CIS), 모바일 디램, 등이 더 제공될 수 있음은 이 분야의 통상적인 지식을 습득한 자들에게 자명하다.

이상에서와 같이 도면과 명세서에서 최적 실시 예가 개시되었다. 여기서 특정한 용어들이 사용되었으나, 이는 단지 본 발명을 설명하기 위한 목적에서 사용된 것이지 의미 한정이나 특허청구범위에 기재된 본 발명의 범위를 제한하기 위하여 사용된 것은 아니다. 그러므로 본 기술 분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시 예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호 범위는 첨부된 특허청구범위의 기술적 사상에 의해 정해져야 할 것이다.

100, 200, 300: 모바일 장치

110, 210, 310: 응용 프로세서

220, 250, 320, 350: 제어 버스, 데이터 버스

230, 330: 하드웨어 블록

240, 340: 접근 제어 유닛

260, 360: 메모리 컨트롤러, DRAM 컨트롤러

265, 365: 워킹 메모리, DRAM

270, 370: 스토리지 컨트롤러

275, 375: 저장 장치

280, 380: 내부 메모리

110, 210, 310: 응용 프로세서

220, 250, 320, 350: 제어 버스, 데이터 버스

230, 330: 하드웨어 블록

240, 340: 접근 제어 유닛

260, 360: 메모리 컨트롤러, DRAM 컨트롤러

265, 365: 워킹 메모리, DRAM

270, 370: 스토리지 컨트롤러

275, 375: 저장 장치

280, 380: 내부 메모리

Claims (20)

- 통신 프로세서;

제어 버스를 통해 상기 통신 프로세서의 보안 모드를 설정하는 응용 프로세서; 및

상기 통신 프로세서의 어드레스 영역(address region) 및 접근 권한(access permission)을 기반으로, 상기 통신 프로세서의 접근 제어(access control)를 설정하거나 변경하는 접근 제어 유닛을 포함하는 시스템 온 칩. - 제 1 항에 있어서,

상기 통신 프로세서는 모뎀인 것을 특징으로 하는 시스템 온 칩. - 제 1 항에 있어서,

외부 메모리를 제어하기 위한 메모리 컨트롤러를 더 포함하고,

상기 접근 제어 유닛은 상기 통신 프로세서로부터 제공된 어드레스와 상기 통신 프로세서의 보안 속성을 기반으로, 상기 외부 메모리의 메모리 영역에 대한 접근 제어를 수행하는 시스템 온 칩. - 제 3 항에 있어서,

상기 접근 제어 유닛은 상기 통신 프로세서가 접근하려고 하는 상기 외부 메모리의 어드레스를 입력받고, 상기 외부 메모리의 메모리 영역이 보안 영역(secure region)인지 비보안 영역(non-secure region)인지를 결정하는 어드레스 디코더를 포함하는 시스템 온 칩. - 제 4 항에 있어서,

상기 접근 제어 유닛은 상기 통신 프로세서로부터 제공되는 가상 주소를 상기 외부 메모리의 물리 주소로 맵핑하는 어드레스 리맵퍼를 더 포함하는 시스템 온 칩. - 제 5 항에 있어서,

상기 어드레스 리맵퍼는 가상 주소를 물리 주소로 맵핑하기 위한 변화 테이블을 포함하며, 상기 변환 테이블을 통해 상기 통신 프로세서의 접근 제어 동작을 제어하는 시스템 온 칩. - 제 4 항에 있어서,

상기 접근 제어 유닛은 상기 통신 프로세서의 어드레스 영역 및 접근 권한에 따라, 상기 통신 프로세서가 상기 외부 메모리로 접근하는 것을 차단하기 위한 접근 제어기를 더 포함하는 시스템 온 칩. - 제 7 항에 있어서,

상기 통신 프로세서가 아닌 제 1 프로세서를 더 포함하고,

상기 접근 제어기는 상기 통신 프로세서가 보안 마스터(secure master)인 경우에, 상기 통신 프로세서가 상기 외부 메모리의 보안 영역 중에서 상기 제 1 프로세서의 보안 영역으로 접근하는 것을 차단하는 시스템 온 칩. - 제 1 항에 있어서,

마스터의 동작을 위한 적어도 하나 이상의 슬레이브를 더 포함하고,

상기 접근 제어 유닛은 상기 통신 프로세서로부터 제공된 어드레스와 상기 통신 프로세서의 보안 속성을 기반으로, 상기 슬레이브에 대한 접근 제어를 수행하는 시스템 온 칩. - 제 9 항에 있어서,

상기 접근 제어 유닛은 상기 통신 프로세서가 접근하려고 하는 슬레이브의 어드레스를 입력 받고, 상기 슬레이브가 보안 슬레이브인지 비보안 슬레이브인지를 결정하는 어드레스 디코더를 포함하는 시스템 온 칩. - 제 10 항에 있어서,

상기 접근 제어 유닛은 상기 통신 프로세서의 어드레스 영역 및 접근 권한에 따라, 상기 통신 프로세서가 특정 슬레이브로 접근하는 것을 차단하기 위한 접근 제어기를 더 포함하는 시스템 온 칩. - 제 11 항에 있어서,

상기 통신 프로세서가 아닌 제 1 프로세서를 더 포함하고,

상기 접근 제어기는 상기 통신 프로세서가 보안 마스터(secure master)인 경우에, 상기 통신 프로세서가 상기 적어도 하나의 슬레이브 중에서 상기 제 1 프로세서의 전용 슬레이브로 접근하는 것을 차단하는 시스템 온 칩. - 복수의 프로세서를 포함하는 시스템 온 칩; 및

상기 시스템 온 칩에 연결되는 메모리 장치를 포함하되,

상기 시스템 온 칩은 제 1 및 제 2 프로세서를 포함하는, 상기 제 1 프로세서는 제어 버스를 통해 제 2 프로세서의 보안 모드를 설정하는, 그리고 상기 제 2 프로세서의 어드레스 영역(address region) 및 접근 권한(access permission)을 기반으로 상기 제 2 프로세서의 접근 제어(access control)를 설정하거나 변경하는 접근 제어 유닛을 포함하는 모바일 장치. - 제 13 항에 있어서,

상기 제 1 프로세서는 응용 프로세서이고, 상기 제 2 프로세서는 통신 프로세서인 모바일 장치. - 제 13 항에 있어서,

상기 접근 제어 유닛은 상기 제 2 프로세서로부터 제공된 어드레스와 상기 제 2 프로세서의 보안 속성을 기반으로, 상기 메모리 장치의 메모리 영역에 대한 접근 제어를 수행하는 모바일 장치. - 제 15 항에 있어서,

상기 접근 제어 유닛은,

상기 제 2 프로세서가 접근하려고 하는 상기 메모리 장치의 어드레스를 입력 받고, 상기 메모리 장치의 메모리 영역이 보안 영역(secure region)인지 비보안 영역(non-secure region)인지를 결정하는 어드레스 디코더;

상기 제 2 프로세서로부터 제공되는 가상 주소를 상기 메모리 장치의 물리 주소로 맵핑하는 어드레스 리맵퍼; 및

상기 제 2 프로세서의 어드레스 영역 및 접근 권한에 따라, 상기 제 2 프로세서가 상기 메모리 장치로 접근하는 것을 차단하기 위한 접근 제어기를 포함하는 모바일 장치. - 제 16 항에 있어서,

제 3 프로세서를 더 포함하고,

상기 접근 제어기는 상기 제 2 프로세서가 보안 마스터(secure master)인 경우에, 상기 제 2 프로세서가 상기 메모리 장치의 보안 영역 중에서 상기 제 3 프로세서의 보안 영역으로 접근하는 것을 차단하는 모바일 장치. - 제 15 항에 있어서,

상기 제 1 및 제 2 프로세서의 동작을 위한 적어도 하나 이상의 슬레이브를 더 포함하고,

상기 접근 제어 유닛은 상기 제 2 프로세서로부터 제공된 어드레스와 상기 제 2 프로세서의 보안 속성을 기반으로, 상기 슬레이브에 대한 접근 제어를 수행하는 모바일 장치. - 제 18 항에 있어서,

상기 접근 제어 유닛은,

상기 제 2 프로세서가 접근하려고 하는 슬레이브의 어드레스를 입력 받고, 상기 슬레이브가 보안 슬레이브인지 비보안 슬레이브인지를 결정하는 어드레스 디코더; 및

상기 제 2 프로세서의 어드레스 영역 및 접근 권한에 따라, 상기 제 2 프로세서가 특정 슬레이브로 접근하는 것을 차단하기 위한 접근 제어기를 포함하는 모바일 장치. - 제 19 항에 있어서,

상기 제 3 프로세서를 더 포함하고,

상기 접근 제어기는 상기 제 2 프로세서가 보안 마스터(secure master)인 경우에, 상기 제 2 프로세서가 상기 적어도 하나의 슬레이브 중에서 상기 제 1 프로세서의 전용 슬레이브로 접근하는 것을 차단하는 모바일 장치.

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020150187774A KR20170077943A (ko) | 2015-12-28 | 2015-12-28 | 접근 제어 유닛을 포함하는 시스템 온 칩 및 시스템 온 칩을 포함하는 모바일 장치 |

| US15/345,572 US20170185345A1 (en) | 2015-12-28 | 2016-11-08 | System-on-chip incuding access control unit and mobile device including system-on-chip |

| DE102016123744.2A DE102016123744A1 (de) | 2015-12-28 | 2016-12-08 | Ein-Chip-System mit Zugriffssteuereinheit und mobile Vorrichtung mit Ein-Chip-System |

| TW105142844A TW201724811A (zh) | 2015-12-28 | 2016-12-23 | 片上系統及包括片上系統的系統及移動裝置 |

| CN201611216813.XA CN106919521A (zh) | 2015-12-28 | 2016-12-26 | 片上系统及包括片上系统的系统及移动装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020150187774A KR20170077943A (ko) | 2015-12-28 | 2015-12-28 | 접근 제어 유닛을 포함하는 시스템 온 칩 및 시스템 온 칩을 포함하는 모바일 장치 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20170077943A true KR20170077943A (ko) | 2017-07-07 |

Family

ID=59010691

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020150187774A KR20170077943A (ko) | 2015-12-28 | 2015-12-28 | 접근 제어 유닛을 포함하는 시스템 온 칩 및 시스템 온 칩을 포함하는 모바일 장치 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20170185345A1 (ko) |

| KR (1) | KR20170077943A (ko) |

| CN (1) | CN106919521A (ko) |

| DE (1) | DE102016123744A1 (ko) |

| TW (1) | TW201724811A (ko) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN107562689A (zh) * | 2016-07-01 | 2018-01-09 | 华为技术有限公司 | 一种系统级芯片和终端 |

| US10303621B1 (en) * | 2017-03-07 | 2019-05-28 | Amazon Technologies, Inc. | Data protection through address modification |

| CN107729601B (zh) * | 2017-09-01 | 2022-01-11 | 北京物芯科技有限责任公司 | 仿真过程中配置ram的方法、装置及计算机存储介质 |

| DE102017219242A1 (de) | 2017-10-26 | 2019-05-02 | Audi Ag | Ein-Chip-System, Verfahren zum Betrieb eines Ein-Chip-Systems und Kraftfahrzeug |

| DE102017220764A1 (de) | 2017-11-21 | 2019-05-23 | Audi Ag | Ein-Chip-System für ein Fahrzeug |

| CN108197503B (zh) * | 2017-12-15 | 2020-09-15 | 杭州中天微系统有限公司 | 一种为间接访问存储控制器增加保护功能的装置 |

| CN109840411B (zh) * | 2018-02-27 | 2021-01-08 | 中国科学院计算技术研究所 | 一种应用的保护方法及系统 |

| CN112262374A (zh) * | 2018-06-12 | 2021-01-22 | 华为技术有限公司 | 一种内存管理方法、装置及系统 |

| FR3089322B1 (fr) | 2018-11-29 | 2020-12-18 | St Microelectronics Rousset | Gestion des restrictions d’accès au sein d’un système sur puce |

| US11281810B1 (en) * | 2018-12-11 | 2022-03-22 | Xilinx, Inc. | Memory access protection in programmable logic device |

| CN109669527A (zh) * | 2018-12-18 | 2019-04-23 | Oppo广东移动通信有限公司 | 数据处理方法和电子设备 |

| CN114041133A (zh) * | 2019-06-21 | 2022-02-11 | 华为技术有限公司 | 一种集成芯片及数据处理方法 |

| KR102281601B1 (ko) * | 2019-08-09 | 2021-07-23 | 엘지전자 주식회사 | 시스템 온 칩과 이를 이용한 정보 보호 방법 및 장치 |

| US12079379B2 (en) * | 2020-12-03 | 2024-09-03 | Huawei Technologies Co., Ltd. | Peripheral component interconnect express protection controller |

| EP4092556A1 (en) * | 2021-05-20 | 2022-11-23 | Nordic Semiconductor ASA | Bus decoder |

-

2015

- 2015-12-28 KR KR1020150187774A patent/KR20170077943A/ko unknown

-

2016

- 2016-11-08 US US15/345,572 patent/US20170185345A1/en not_active Abandoned

- 2016-12-08 DE DE102016123744.2A patent/DE102016123744A1/de not_active Withdrawn

- 2016-12-23 TW TW105142844A patent/TW201724811A/zh unknown

- 2016-12-26 CN CN201611216813.XA patent/CN106919521A/zh active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| TW201724811A (zh) | 2017-07-01 |

| CN106919521A (zh) | 2017-07-04 |

| US20170185345A1 (en) | 2017-06-29 |

| DE102016123744A1 (de) | 2017-06-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20170077943A (ko) | 접근 제어 유닛을 포함하는 시스템 온 칩 및 시스템 온 칩을 포함하는 모바일 장치 | |

| KR101954733B1 (ko) | 보안 콘텐츠를 처리하는 시스템 온 칩 및 그것을 포함하는 모바일 장치 | |

| US9170957B2 (en) | Distributed dynamic memory management unit (MMU)-based secure inter-processor communication | |

| US9607177B2 (en) | Method for securing content in dynamically allocated memory using different domain-specific keys | |

| US9026712B2 (en) | USB device control using endpoint type detection during enumeration | |

| US20160088109A1 (en) | Method and Apparatus for Remotely Running Application Program | |

| JP7042552B2 (ja) | マルチプロセッサによって共有されるメモリを含むマルチプロセッサシステム | |

| KR20150143708A (ko) | 스토리지 디바이스 보조 인라인 암호화 및 암호해독 | |

| US9331988B2 (en) | System and method for provisioning secrets to an application (TA) on a device | |

| US20180365425A1 (en) | Systems and methods for securely booting a system on chip via a virtual collated internal memory pool | |

| CN112149144A (zh) | 聚合密码引擎 | |

| US20170317832A1 (en) | Virtual Secure Elements in Computing Systems based on ARM Processors | |

| US20190228159A1 (en) | Technologies for filtering memory access transactions received from one or more accelerators via coherent accelerator link | |

| JP7201686B2 (ja) | 間接アクセスメモリコントローラ向けの保護機能を追加するための機器 | |

| US20190138755A1 (en) | Technologies for filtering memory access transactions received from one or more i/o devices | |

| US10628611B2 (en) | Exclusive execution environment within a system-on-a-chip computing system | |

| US10586038B2 (en) | Secure stack overflow protection via a hardware write-once register | |

| US20070011096A1 (en) | Method and apparatus for managing DRM rights object in low-performance storage device | |

| KR102218202B1 (ko) | 반도체 장치 | |

| US20060143411A1 (en) | Techniques to manage partition physical memory | |

| JP2007109053A (ja) | バスアクセス制御装置 | |

| CN109937407B (zh) | 用于smm传输监控器的扩展存储器 |