KR20110066106A - 프로그램 가능한 crc 계산을 위한 명령어 집합 구조 - Google Patents

프로그램 가능한 crc 계산을 위한 명령어 집합 구조 Download PDFInfo

- Publication number

- KR20110066106A KR20110066106A KR1020100125762A KR20100125762A KR20110066106A KR 20110066106 A KR20110066106 A KR 20110066106A KR 1020100125762 A KR1020100125762 A KR 1020100125762A KR 20100125762 A KR20100125762 A KR 20100125762A KR 20110066106 A KR20110066106 A KR 20110066106A

- Authority

- KR

- South Korea

- Prior art keywords

- bit

- operand

- polynomial

- crc

- series

- Prior art date

Links

- 125000004122 cyclic group Chemical group 0.000 title claims abstract description 4

- 238000004364 calculation method Methods 0.000 claims abstract description 12

- 230000009467 reduction Effects 0.000 claims description 27

- 238000000034 method Methods 0.000 claims description 22

- 239000003607 modifier Substances 0.000 description 14

- 238000010586 diagram Methods 0.000 description 11

- 230000006870 function Effects 0.000 description 5

- 230000005540 biological transmission Effects 0.000 description 3

- 238000004422 calculation algorithm Methods 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 206010009944 Colon cancer Diseases 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 230000006835 compression Effects 0.000 description 1

- 238000007906 compression Methods 0.000 description 1

- 238000004590 computer program Methods 0.000 description 1

- 230000006837 decompression Effects 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000006855 networking Effects 0.000 description 1

- 230000008672 reprogramming Effects 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30145—Instruction analysis, e.g. decoding, instruction word fields

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

- G06F9/30018—Bit or string instructions

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1004—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's to protect a block of data words, e.g. CRC or checksum

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/22—Microcontrol or microprogram arrangements

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/09—Error detection only, e.g. using cyclic redundancy check [CRC] codes or single parity bit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/09—Error detection only, e.g. using cyclic redundancy check [CRC] codes or single parity bit

- H03M13/091—Parallel or block-wise CRC computation

Abstract

복수의 다른 n비트 다항식을 사용하여 데이터 블록에 대하여 CRC 연산을 행하는 방법 및 장치가 제공된다. 유연한 CRC 명령어는 프로그램 가능한 n비트 다항식을 사용하여 CRC 연산을 행한다. n비트 다항식을 두 연산자 중 하나에 저장함으로써 CRC 명령어에 n비트 다항식이 제공된다.

Description

본 발명은 에러 체크에 관한 것이고, 특히 에러 체크를 위한 CRC의 사용에 관한 것이다.

다항식은 하나 이상의 대수항(예컨대 각각이 비음수의 정수승인 하나 이상의 변수(x)가 곱해지는 상수(a, b 또는 c)로 구성되는 "a+bx+cx2")의 수학적 표현이다. n비트 다항식에 의한 데이터 블록의 2진 제산(binary division)의 고정된 크기의 나머지는, 소스로부터 목적지까지 데이터 블록을 송신할 때 송신 에러가 없었다는 것을 확인하기 위해 사용될 수 있다. 임의의 길이의 데이터 블록에 적용된 n비트 다항식은 n비트보다 작거나 같은 모든 하나의 에러 버스트를 검출한다.

고정된 크기의 나머지는 소스에서 데이터 블록을 위해 계산되어 데이터 블록과 함께 송신된다. 목적지에서 고정된 크기의 나머지를 재계산하기 위해 n비트 다항식은 수신된 데이터 블록에 적용된다. 송신 에러가 없었는지 확인하기 위해, 재계산된 고정된 크기의 나머지는 데이터 블록과 함께 송신된 고정된 크기의 나머지와 비교된다.

CRC는 고정된 크기의 나머지(고정된 크기의 다항식에 의한 임의의 길이의 데이터 블록의 2진 제산의 레지듀(residue)) 및 그러한 고정된 크기의 나머지를 생성하기 위한 기능에 주어진 용어이다.

이하의 상세한 설명이 진행됨에 따라, 또한 도면을 참조하여, 주장된 대상의 실시예의 특징은 분명해질 것이며, 같은 숫자는 같은 부분을 표현한다.

도 1은 본 발명의 원리에 따른 일반적 목적의 프로세서에서 CRC를 행하기 위한 명령어의 실시예를 포함하는 시스템의 블록도이다.

도 2는 도 1에 나타낸 프로세서의 실시예의 블록도이다.

도 3은 본 발명의 원리에 따른 유연한 CRC를 행하기 위한 도 2에 나타낸 실행 유닛의 실시예를 나타내는 블록도이다.

도 4는 도 3에 나타낸 확장 다항식 마이크로 연산의 실시예를 나타낸다.

도 5는 도 3에 나타낸 셔플 워드 마이크로 연산의 실시예를 나타낸다.

도 6은 도 3에 나타낸 CRC 감소 마이크로 연산의 실시예를 나타낸다.

도 7은 도 6에 나타낸 계산 CRC 기능의 실시예를 나타내는 블록도이다.

도 8은 도 7에 나타낸 4비트 감소 스테이지를 나타내는 블록도이다.

도 9는 본 발명의 원리에 따른 CRC를 행하는 방법의 실시예를 나타내는 흐름도이다.

이하의 상세한 설명은 주장된 대상의 예시적인 실시예를 참조하여 진행될 것이지만, 그 여러 대안, 수정, 변형은 당업자에게 명백할 것이다. 따라서, 주장된 대상은, 보다 넓게 보이도록, 또한 첨부한 청구항에서 설명한 것에 의해서만 규정되도록 의도되었다.

도 1은 본 발명의 원리에 따른 일반적 목적의 프로세서에서 CRC를 행하기 위한 명령어의 실시예를 포함하는 시스템의 블록도이다.

도 2는 도 1에 나타낸 프로세서의 실시예의 블록도이다.

도 3은 본 발명의 원리에 따른 유연한 CRC를 행하기 위한 도 2에 나타낸 실행 유닛의 실시예를 나타내는 블록도이다.

도 4는 도 3에 나타낸 확장 다항식 마이크로 연산의 실시예를 나타낸다.

도 5는 도 3에 나타낸 셔플 워드 마이크로 연산의 실시예를 나타낸다.

도 6은 도 3에 나타낸 CRC 감소 마이크로 연산의 실시예를 나타낸다.

도 7은 도 6에 나타낸 계산 CRC 기능의 실시예를 나타내는 블록도이다.

도 8은 도 7에 나타낸 4비트 감소 스테이지를 나타내는 블록도이다.

도 9는 본 발명의 원리에 따른 CRC를 행하는 방법의 실시예를 나타내는 흐름도이다.

이하의 상세한 설명은 주장된 대상의 예시적인 실시예를 참조하여 진행될 것이지만, 그 여러 대안, 수정, 변형은 당업자에게 명백할 것이다. 따라서, 주장된 대상은, 보다 넓게 보이도록, 또한 첨부한 청구항에서 설명한 것에 의해서만 규정되도록 의도되었다.

CRC 계산을 행하기 위한 많은 알려진 방법이 있다. 한 방법은 특정한 n비트 다항식을 구현하기 위해 전용 CRC 회로를 사용하는 것이다. 다른 방법은 소정의 n비트 다항식에 대한 모든 가능한 CRC 결과 및 데이터 입력 및 나머지의 집합을 저장하기 위해 CRC 룩업 테이블을 사용하는 것이다. 이 방법에서, CRC 결과를 결정하기 위해 CRC 룩업 테이블에서 한 테이블 룩업이 행해진다.

그러나, CRC를 계산하기 위해 사용되는 n비트 다항식은 여러 가지가 있다. 예컨대, iSCSI(Internet Small Computer Systems Interface)와 같은 스토리지 프로토콜, 압축 및 압축 해제, MPEG(Moving Pictures Experts Group) 및 JPEG(Joint Photographic Experts Group)와 같은 그래픽 처리를 위한 CRC를 계산하기 위해 서로 다른 n비트 다항식이 사용된다. 따라서, 서로 다른 n비트 다항식 각각에 대하여 CRC를 계산하기 위해서는 전용 CRC 회로 또는 독립된 룩업 테이블이 필요하게 된다.

CRC 계산은 전용 CPU 명령어의 사용을 통해 하드웨어에서 행해질 수도 있다. 그러나, CPU 명령어는 피연산자의 수 및 사이즈에 의해 제한된다. CRC 명령어는 한 특정한 고정된 n비트 다항식에 대한 CRC를 계산하도록 되어있다.

본 발명의 실시예에서, 복수의 서로 다른 n비트 다항식을 사용하여 CRC 처리를 행하기 위해 명령어 집합 구조가 제공된다. 실시예에서, 유연한 CRC 명령어는 최대 차수 32까지의 n비트 다항식을 지원한다(즉, 논리적인 '1'로 설정된 비트 xn(n+1번째 비트)을 갖는 n비트 다항식이 지원된다). 유연한 CRC 명령어는 데이터/레지듀에서 비트/바이트 리플렉트를 지원한다.

도 1은 본 발명의 원리에 따른 일반적 목적의 프로세서에서 CRC 처리를 행하기 위한 명령어의 실시예를 포함하는 시스템(100)의 블록도이다. 시스템(100)은 프로세서(101), 메모리 컨트롤러 허브(MCH)(102), 입력/출력(I/O) 컨트롤러 허브(ICH)(104)를 포함한다. MCH(102)는 프로세서(101)와 메모리(108) 사이의 통신을 제어하는 메모리 컨트롤러(106)를 포함한다. 프로세서(101)와 MCH(102)는 시스템 버스(116)를 통해서 통신한다.

프로세서(101)는, 싱글코어 인텔펜티엄Ⅳ 프로세서, 싱글코어 인텔 셀러론 프로세서, 인텔엑스스케일 프로세서 또는 인텔펜티엄 D, 인텔제온프로세서와 같은 멀티코어 프로세서, 또는 인텔코어듀오 프로세서 또는 다른 모든 타입의 프로세서와 같은 복수의 프로세서 중 하나일 수 있다.

메모리(108)는, DRAM(Dynamic Random Access Memory), SRAM(Static Random Access Memory), SDRAM(Synchronized Dynamic Random Access Memory), DDR2(Double Data Rate 2) RAM, 또는 RDRAM(Rambus Dynamic Random Access Memory) 또는 다른 모든 타입의 메모리일 수 있다.

ICH(104)는 DMI(Direct Media Interface)와 같은 고속의 칩투칩(chip-to-chip) 연결(114)을 사용하여 MCH(102)에 연결될 수 있다. DMI는 두 단방향 레인을 통해 2기가비트/초의 동시 전송률을 지원한다.

ICH(104)는 ICH(104)에 연결된 적어도 하나의 스토리지 장치(112)와의 통신을 제어하는 스토리지 I/O 컨트롤러(110)를 포함할 수 있다. 스토리지 장치는, 예컨대 디스크 드라이브, DVD(Digital Video Disk) 드라이브, CD(Compact Disk) 드라이브, RAID(Redundant Array of Independent Disks), 테이프 드라이브 또는 다른 스토리지 장치일 수 있다. ICH(104)는 SAS(Serial Attached Small Computer System Interface) 또는 SATA(Serial Advanced Technology Attachment)와 같은 직렬 스토리지 프로토콜을 사용하여 스토리지 프로토콜 연결(118)을 통해 스토리지 장치(112)와 통신할 수 있다.

프로세서(101)는 CRC 처리를 행하기 위해 CRC 유닛(103)을 포함한다. CRC 유닛(103)은 메모리(108) 및/또는 스토리지 장치(112)에 저장된 데이터에 대한 복수의 서로 다른 n비트 다항식을 사용하여 CRC를 계산하기 위해 사용될 수 있다.

CRC 처리는 복수의 서로 다른 n비트 다항식 중 하나를 사용하여 데이터 블록에 대하여 행해진다. 유연한 CRC 명령어는 프로그램 가능한 n비트 다항식을 사용하여 CRC 처리를 행한다. CRC 유닛(103)에 저장된 고정된 다항식에 대한 CRC 처리를 행하는 대신에, 유연한 CRC 명령어를 제공하기 위해 두 피연산자 중 하나에 n비트 다항식을 저장함으로써 CRC 명령어를 통해 CRC 유닛(103)에 n비트 다항식이 제공된다.

도 2는 도 1에 나타낸 프로세서(101)의 실시예의 블록도이다. 프로세서(101)는 레벨 1(L1) 명령어 캐시(202)로부터 수신된 프로세서 명령어를 복호하는 인출 및 복호 유닛(202)을 포함한다. 명령어를 실행하기 위해 사용되는 데이터(예컨대, 명령어에 의해 사용되는 입력 피연산자)는 레지스터 파일(208)에 저장될 수 있다. 한 실시예에서, 레지스터 파일(208)은 유연한 CRC 명령어에 의해 사용할 데이터(피연산자)를 저장하기 위해 유연한 CRC 명령어에 의해 사용되는 복수의 레지스터를 포함한다.

한 실시예에서, 최대 차수 32까지의 n비트 다항식을 지원하는 명령어 집합에 대하여, 레지스터 파일은 복수의 64비트 레지스터를 갖는다. 다른 실시예에서, 레지스터는 64비트 이상을 가질 수 있다. 예컨대, 레지스터 파일은, 최대 차수 m까지의 m비트 다항식을 지원할 수 있는 유연한 CRC 명령어 집합에 대하여 복수의 2m비트 레지스터를 포함할 수 있다.

인출 및 복호 유닛(202)은 L1 명령어 캐시(202)로부터 매크로 명령어를 인출하고, 매크로 명령어를 복호하여 마이크로 연산(μops)이라고 불리는 간단한 연산으로 나눈다. 실행 유닛(210)은 마이크로 연산을 스케줄링하고 실행한다. 나타낸 실시예에서, 실행 유닛(210) 내의 CRC 유닛(103)은 유연한 CRC 명령어를 위한 마이크로 연산을 포함한다. 리타이어 유닛(212)은 실행된 매크로 명령어의 결과를 레지스터 또는 메모리(108)(도 1)에 기입한다.

도 3은 본 발명의 원리에 따른 유연한 CRC 명령어를 실행하는 도 2에 나타낸 실행 유닛(210)의 실시예를 나타내는 블록도이다.

인출 및 복호 유닛(206)에 의해 유연한 CRC 명령어가 복호된 후에, 실행 유닛(210)에 의한 유연한 CRC 명령어의 실행은, 유연한 CRC 명령어와 관련된 CRC 유닛(103)에서의 마이크로 연산을 행하는 것을 포함한다.

소스("입력") 피연산자에 제공된 프로그램 가능한 n비트 다항식을 사용하여 CRC 유닛(103)에서 CRC를 행하기 위한 유연한 CRC 명령어(매크로 명령어)는 상징적으로 이하와 같이 규정될 수 있다.

Flex_CRC32 r64, r/m64

유연한 CRC 명령어는 두 소스 피연산자를 갖는다. 제 1 피연산자("op1")는 레지스터 파일(304) 내의 제 1 64비트 레지스터(r64)에 저장되고, CRC 처리를 위한 32비트 다항식 및 초기 32비트 CRC 레지듀("초기 CRC")를 저장하기 위해 사용된다. 레지스터 파일(304)에 저장된 제 2 피연산자("op2")는 64비트 데이터(감소될 데이터 블록) 또는 64비트 포인터를 64비트 데이터(감소될 데이터 블록)가 저장되는 메모리(108)(도 1) 내의 메모리 위치에 저장할 수 있다.

유연한 CRC 명령어는 64비트 데이터 블록에서 제 1 소스 피연산자에 제공된 초기 CRC 레지듀 및 제 1 소스 피연산자에 제공된 다항식을 사용하여 CRC 처리를 행한다. 소스 피연산자 중 하나에 다항식이 제공되는 것을 허용함으로써, CRC 명령어는, CRC 유닛(103)에 저장된 고정된 다항식을 사용하는 CRC 명령어와는 대조적으로 유연하다. 제 1 피연산자에서 식별된 64비트 레지스터는 CRC 처리의 결과를 저장하기 위한 목적지 피연산자로서 사용된다. CRC 처리의 결과는 "새로운 레지듀"라고도 불려진다. 32비트 "새로운 레지듀" 및 32비트 프로그램 가능한 다항식은 제 1 피연산자에 의해 식별된 64비트 레지스터에 저장된다.

"초기 레지듀" 및 프로그램 가능한 다항식은 유연한 CRC 명령어를 발행하기 전에 제 1 피연산자에 의해 식별된 64비트 레지스터에 저장된다. 실시예에서, 다항식은 32의 최대 차수, 즉 x32항을 갖는다(33비트 다항식의 비트 33은 논리적인 '1'로 설정된다). 실시예에서, 피연산자 1의 32 최하위 비트(즉, 비트[31:0])는 초기 레지듀를 저장하고 피연산자 1의 32 최상위 비트(즉, 비트 63:32)는 33비트 프로그램 가능한 다항식의 최하위 비트 32비트를 저장한다. 제 1 피연산자의 32 최상위 비트에 저장하기 전에, 33비트 프로그램 가능한 다항식은 "함축된" 리딩(leading) '1'과 함께 좌측 정렬되고(즉, 다항식은 32의 최대 차수를 가지므로, 비트 33은 논리적인 '1'로 설정되는 것이 함축된다), 비트 33은 버려진다. 64비트보다 큰 레지스터(304)를 갖는(예컨대, 레지스터 파일에) 실시예에서, 유연한 CRC 명령어는 32보다 큰 최대 차수를 갖는 다항식을 지원할 수 있다.

CRC 처리는 파일(스토리지 내의) 또는 네트워크 패킷(네트워킹에서)과 같은 큰 데이터 블록의 다이제스트(일반적으로 32비트)를 생성하기 위해 사용되는 해시 함수의 특별한 형태이다. 다이제스트는 계산되어 저장 또는 송신 전에 데이터 블록에 첨부되고, 그 후 데이터 블록이 메모리 또는 스토리지 매체에 저장되는 동안 또는 네트워크를 통해 송신되는 동안 변경되지 않았는지 확인하기 위해 데이터 블록으로부터 재계산되어 원본과 비교된다.

CRC는 한 2진 다항식을 다른 2진 다항식으로 나눈 나머지이다. 비트스트림(데이터 블록/메시지)은 2진 계수를 갖는 다항식으로서 볼 수 있고, 여기서 스트림에서 논리적인 '1'로 설정된 비트는 다항식의 '1' 계수에 해당하고, 스트림의 최하위 비트는 다항식의 자유 계수에 해당한다. 이들 다항식/비트열에 대하여 연산이 규정된다.

예컨대, iSCSI(Internet SCSI)(RFC(Request for Comments) 3385에서 규정됨)는 단말 상호간(end-to-end)의 데이터 보호를 위해 CRC(Cyclic Redundancy Check)를 사용한다. iSCSI CRC는 33비트 다항식 11EDC6F41(16진수 형태)을 사용한다. 33비트 iSCSI(Internet Small Computer Systems Interface) 다항식 11EDC6F41H는 33비트 2진수로 쓰면 100011110110111000110111101000001이다. 이 33비트 2진수는 이하의 다항식에 해당한다.

다항식 가산은 비트 단위의 배타적 논리합(XOR) 연산에 해당한다. XOR은 피연산자 중 하나만이 논리값 '1'을 가지면 논리값 '1'이 되는 두 피연산자에 대한 논리적 연산이다. 두 논리값이 같으면(모두 '0' 또는 모두 '1') 결과는 논리값 '0'이다. 예컨대, 값 '11001010'을 갖는 제 1 피연산자와 값 '10000011'을 갖는 제 2 피연산자의 XOR은 값 '01001001'을 갖는 결과를 제공한다.

다항식 승산은 비트열의 올림이 없는(carry-less) 승산에 해당한다. 예컨대, 2진열의 t 위치의 좌측 시프트(left shift)은 xt에 의한 다항식 승산에 해당한다. P(x), Q(x), R(x), W(x)가 P(x)=W(x)*Q(x)+R(x)를 만족하고 R(x)의 차수가 P(x)의 차수보다 작으면, R(x)는 P(x)를 W(x)로 나눈 나머지이다.

이러한 조건을 사용하여, 2진 다항식 M(x)에 해당하는 임의의 비트 길이의 메시지 M의 CRC값은 CRC M(x)=x32*M(x) mod P(x)로 규정될 수 있고 다항식 P(x)는 CRC 알고리즘을 규정한다. 32비트 CRC 알고리즘에 대하여, P(x)는 차수 32의 다항식이다.

실시예에서, 유연한 CRC 명령어는 세 개의 서로 다른 마이크로 연산의 조합을 사용하여 실행 유닛(210) 내의 CRC 유닛(103)에서 구현된다. 도 3에 나타낸 세 마이크로 연산은 (1) 확장 다항식(314), (2) 셔플 워드(316), (3) CRC 감소(318)이다.

확장 다항식 마이크로 연산(314)은 도 3에 나타낸 실시예에서 레지스터 파일(304) 내의 레지스터(306)에 저장된 제 1 피연산자("op1")의 최상위 비트(MSB)에 저장된 다항식을 수신한다. 확장 다항식 마이크로 연산(314)은 op1에 제공된 n비트 프로그램 가능한 다항식으로부터 미리 계산된 다항식 K를 얻는다. 미리 계산된 다항식 K의 32 최하위 비트는 CRC 감소 마이크로 연산(318)에서 나중에 사용하기 위해 CRC 유닛(103)에 의해 저장된다. 미리 계산된 다항식 K는 동시에 계산이 행해지도록 허용함으로써 CRC 레지듀를 결정하기 위해 요구되는 게이트 지연의 수를 감소시킨다.

확장 다항식 마이크로 연산(314)은 상징적으로 이하와 같이 규정될 수 있다.

dest :=crc_expand_poly (-, source1), select_modifier

확장 다항식 마이크로 연산(314)은 32비트 미리 계산된 다항식 K=x36MOD POLY를 계산하고 K의 32 최하위 비트를 저장한다. 갈로아 필드(Galois Field)(GF(2))에 걸쳐 다항식의 제산(division)으로서 모듈로(modulo) 감소가 규정된다.

갈로아 필드(GF(2))에 걸쳐 미리 계산된 다항식 K는 32비트 CRC 다항식의 배수이다. 미리 계산된 다항식 K의 형태는 감소될 데이터 블록의 상호 배타적 영역을 동시에 처리함으로써 많은 계산이 동시에 행해지도록 허용한다. 동시에 계산을 행하면 CRC 레지듀를 계산하는 시간이 감소된다. 예컨대, CRC 감소 마이크로 연산(318)에 의해 사용되는 미리 계산된 다항식 K는 감소될 4 최상위 비트(40비트 입력 데이터의 비트 39~36)를 동시에 허용한다. 예컨대, 최대 차수 32의 다항식에 대하여, 32비트를 갖는 k와 함께, 40비트 입력 데이터에 K의 32 최하위 비트를 적용하면 40비트 입력 데이터를 36비트 레지듀로 감소시킨다.

실시예에서, 셔플 워드 마이크로 연산(316)은 레지스터 파일(304) 내의 레지스터(306)로부터 소스 피연산자 1("op1")을, 레지스터(312)로부터(또는 레지스터(312)에 저장된 메모리 포인터에 의해 식별된 메모리 위치로부터) 소스 피연산자 2("op2")를 수신하고, 즉시 바이트(immediate byte)에 저장된 수식자(modifier)에 따라 피연산자의 각각에서 64비트의 32비트 부분 중 하나를 선택한다. 마이크로 연산은 상징적으로 이하와 같이 규정될 수 있다.

dest :=shuffle_word(source2, source1), imm8

셔플 워드 마이크로 연산(316)은 64비트 데이터 경로의 두 절반 사이에서 워드 레벨 데이터(32비트)의 셔플을 행한다. 이 마이크로 연산은 각각의 64비트 피연산자의 각각으로부터 32비트 최상위 비트(위의 절반) 또는 32비트 최하위 비트(아래의 절반)를 선택한다. 선택된 절반 내의 비트도 셔플될 수 있다. 각 피연산자 내의 비트의 셔플은 즉시 데이터(immediate data)(imm8)에 저장된 4비트 셔플 선택 수식자(SHUFFLE SELECT MODIFIER)에 따라 결정된다. 셔플의 결과는 목적지 레지스터("dest")에 저장된다.

이것이 유연한 CRC 명령어에 대한 셔플 워드 마이크로 연산(316)으로의 첫 번째 콜이라면, 즉시 데이터("imm8")는 유연한 CRC 매크로 명령어에 의해 수신된 64비트 제 2 피연산자("op2")로부터 최상위 32비트가 선택되어야 하는 것을 나타낸다.

CRC 감소 마이크로 연산(318)은 셔플 워드 마이크로 연산(316)에 의해 제공된 32비트 데이터 내의 4바이트의 각각에 대하여 행해진다. CRC 감소 마이크로 연산(318)은 셔플 워드 마이크로 연산(316)으로부터 수신된 32비트 초기 레지듀, 프로그램 가능한 다항식, 확장 다항식 마이크로 연산에 의해 계산된 미리 계산된 다항식 K를 사용하여 레지듀(RES)를 계산한다.

유연한 CRC 명령어의 실행이 완료된 후, 축적된 레지듀 및 다항식은 피연산자 1(매크로 명령어에 대하여 목적지 및 소스 레지스터임)에 저장되는데, 도 3에 나타낸 실시예에서는 레지스터 파일(304) 내의 레지스터(306)에 저장될 수 있다.

도 4는 도 3에 나타낸 확장 다항식 마이크로 연산(314)의 실시예를 나타낸다. CRC 다항식이 x32=p31.x31+p30.x30+ … p0 형태의 32비트 다항식(POLY)인 실시예에서, [p31 … p0]으로 표현되는 32비트 다항식은 소스 레지스터(400)의 32 최상위 비트(위의 절반)에 저장된다. x32에 해당하는 함축된 리딩 "1"은 삭제된다.

모듈로 연산(MOD)은 POLY에 의해 x36의 제산의 나머지를 계산한다. 예컨대, 나머지 r=a mod n에서, 나머지 r은 a가 n에 의해 나누어졌을 때의 나머지이다. 그 경우에 a는 10이고 n은 3이고 r은 1이다.

확장 다항식 마이크로 연산(314)은 K=x36 MOD POLY의 레지듀를 계산하여 미리 계산된 다항식 상수 K로서 목적지 레지스터(406)에 저장한다. 모듈로 감소는 갈로아 필드(GF(2))에 걸쳐 다항식의 제산으로서 규정된다.

원래의 32비트 다항식도 목적지 레지스터(406)에 저장된다. 레지듀를 계산하기 위해 행해지는 배타적 OR(XOR) 연산의 수를 삭감하기 위해, 미리 계산된 다항식 상수(레지듀) K 및 원래의 32비트 다항식(다항식)이 다음의 CRC 감소(삭감) 연산에서 사용된다. 유연한 CRC 매크로 명령어에 제공된 64비트 데이터 블록을 32비트 레지듀로 삭감하기 위해 XOR 연산이 32비트 다항식을 사용하여 행해진다.

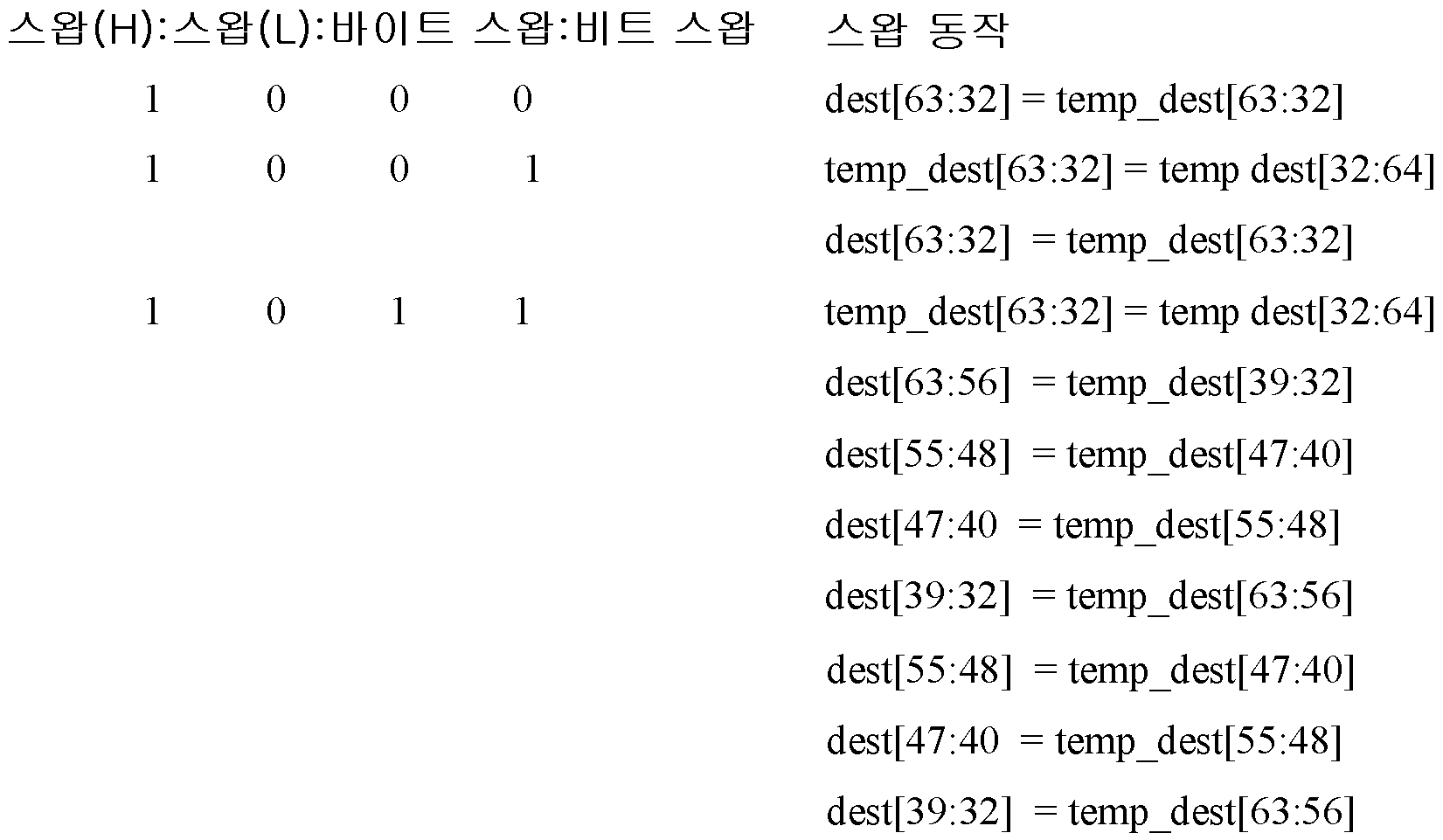

도 5는 도 3에 나타낸 셔플 워드 마이크로 연산(316)의 실시예를 나타낸다.

도 5에 나타낸 실시예에서, 제어 로직(504)는 셔플 워드 마이크로 연산(316)에서 제공된 즉시 바이트(510) 내의 상태 수식자 및 스왑 비트의 상태에 따라 프로그램 가능하다. 즉시 바이트(510)는 제어 로직(504)에 의해 사용되어 데이터/레지듀에 대하여 비트/바이트 리플렉트를 행한다. 즉, 바이트/비트를 소스 1(500) 및 소스 2(502)에 맵핑하고 바이트/비트를 목적지(506)에 맵핑한다. 나타낸 실시예에서, 소스 1(500), 소스 2(502), 목적지(506)는 모두 64비트를 갖는다. 다른 실시예에서, 소스 1(500), 소스 2(502), 목적지(506)는 64비트 이상을 가질 수 있다.

일 실시예에서, 즉시 바이트(510)의 4 최하위 비트, 즉 셔플 선택 수식자[3:0]는 제어 로직(504)에 의해 사용되어 64비트 소스 1(500) 및 64비트 소스 2(502)의 어떤 32비트 부분이 64비트 목적지(506)의 32비트 부분에 전송될지 선택한다. 2 최하위 비트로, 즉 셔플 선택 수식자[1:0]은 네 32비트 부분의 어느 것을 목적지의 하위 32비트에 전송할지 선택하고, 2 최상위 비트, 즉 셔플 선택 수식자[2:3]은 네 32비트 부분의 어느 것을 목적지의 상위 32비트에 전송할지 선택한다.

이하의 표 1 및 2는 셔플 선택 수식자[3:0]의 상태에 따라 소스 피연산자의 32비트 워드가 어떻게 목적지의 32비트 워드에 맵핑되는지 나타낸다.

즉시 바이트(510)의 비트 스왑 비트가 유효해지면(예컨대, 논리적인 '1'로 설정되면), 32비트의 자릿수가 스왑되고, 예컨대 소스 중 하나의 비트 [31:0]이 목적지에 비트 [0:31]로서 저장되어, 최상위 비트 31이 목적지의 최상위 비트 위치에 저장된다. 하이 스왑/로우 스왑 비트의 상태는 비트 스왑이 목적지(506)의 최하위 32비트에 대하여 행해지는지 또는 목적지(506)의 최상위 32비트에 대하여 행해지는지 나타낸다. 바이트 스왑 비트('1' 또는 '0')의 상태는, 데이터를 목적지(506)로 이동시킬 때, 소스(500, 502)의 32비트 절반의 4바이트가 스왑되는지 나타낸다. 예컨대, 소스(502)의 32 최하위 비트의 바이트 스왑은 소스(502)의 최상위 바이트(비트 31:24)를 목적지(506)의 최하위 비트(비트 7:0)에 저장한다.

이하의 표 3 및 4는 즉시 바이트의 비트 7:5의 상태에 따라 셔플 워드 마이크로 연산(314)에 의해 행해지는 데이터/레지듀에 대한 비트/바이트 리플렉트를 요약한다. 나타낸 실시예에서, 비트 7(스왑(H))(스왑(L))은 목적지의 높은 절반에 대한 스와핑을 유효/무효로 하고, 비트 6은 목적지의 낮은 절반에 대한 스와핑을 유효/무효로 하고, 비트 5(바이트 스왑)는 바이트 스왑 인에이블을 유효/무효로 하고, 비트 4(비트 스왑)는 비트 스왑 인에이블을 유효/무효로 한다.

한 실시예에서 마이크로 연산으로 즉시 바이트를 제공하는 대신에, 항상 소스 1의 32 최하위 비트에 저장된 CRC 레지듀를 목적지의 32 최하위 비트에 맵핑하기 위해 제어 로직이 하드웨어에 내장된다. 또한 유연한 CRC 매크로 명령어에서 셔플 워드 마이크로 연산이 첫 번째 또는 두 번째로 호출되는지 여부에 따라, 소스 2로부터의 데이터의 최상위 32비트를 목적지의 최상위 32비트에 또는 소스 2로부터의 데이터의 최하위 32비트를 목적지의 최상위 32비트에 맵핑하기 위해 제어 로직이 하드웨어에 내장된다.

도 6은 도 3에 나타낸 CRC 감소 마이크로 연산(318)의 실시예를 나타낸다. CRC 감소 마이크로 연산(318)은 32비트 다항식 및 32비트 미리 계산된 다항식 K를 사용하여 데이터 블록(데이터 스트림)으로부터 8비트의 삭감을 행한다.

소스(506)에 제공된 32비트 데이터로부터 선택되는 데이터의 8비트 블록에 대하여 소스(406)에 제공된 다항식을 사용하여 CRC 감소 기능이 행해진다. 도 4와 관련하여 설명되고 소스(406)의 32 최상위 비트에 제공된 확장된 다항식 마이크로 연산(316)에 의해 계산된 추가적인 미리 계산된 다항식 K는 CRC 감소 기능에 의해서도 사용된다. CRC 다항식이 x32=p31.x31+p30.x30+…p0의 형태의 32비트 다항식(POLY)이면, [p31…p0]으로 표시되는 32비트 다항식은 소스(406)의 32 최상위 비트에 입력으로서 주어진다(x32에 해당하는 함축된 리딩 "1"은 삭제된다). 소스(406)의 32 최하위 비트는 미리 계산된 다항식 K=x36 MOD POLY를 저장한다.

64비트 소스 레지스터(506)는 데이터를 저장하는 32 최상위 비트 및 현재의 CRC 레지듀를 저장하는 32 최하위 비트와 함께 초기 데이터(DH 또는 DL) 및 현재의 CRC 축적 레지듀("현재의 레지듀")를 저장한다. 계산 CRC 마이크로 연산의 결과("레지듀")는 목적지 레지스터(606)의 32 최하위 비트에 저장된다.

CRC를 계산하는 것은 생성기 값에 의한 입력 데이터의 제산에 따른 나머지를 산출하는 것을 필요로 한다. CRC는 소스 레지스터(506)에 저장되는 데이터 스트림의 32비트 세그먼트를 위해 계산된다. 32비트 데이터는 시프트 로직(602)에 있어서 8비트 시프트되고, 시프트된 데이터는 목적지 레지스터(606)에 "갱신된 데이터"로서 저장되어 다음의 CRC 감소 마이크로 연산(318)에서 사용된다. CRC 연산은 소스 레지스터(506)에 "초기 데이터"로서 저장되는 데이터의 8 최상위 비트에 대하여 행해진다. 미리 계산된 다항식 K 및 다항식은 목적지 레지스터(606)에 저장되는 CRC 레지듀를 계산하기 위해 사용된다.

도 7은 도 6에 나타낸 계산 CRC 로직(604)의 실시예를 나타내는 블록도이다.

계산 CRC 로직(604)은 8비트 세그먼트(702)의 데이터 스트림의 연속적인 부분(세그먼트)에 대한 CRC 연산을 행한다. 8비트 세그먼트는 32비트 시프트되고, 시프트된 8비트 세그먼트 및 8비트 시프트되는 이미 존재하는 모든 레지듀(나머지)로 XOR 연산이 행해진다. XOR 연산된 40비트 결과(입력 데이터) 및 32비트 미리 계산된 다항식 K는 다음 스테이지에서 32비트 CRC 레지듀를 계산하기 위해 사용된다. 4비트 감소 스테이지(712)에서, 36비트 레지듀를 제공하기 위해 32비트 미리 계산된 다항식 K를 사용하여 40비트 입력 데이터는 4비트 감소된다. 36비트 레지듀는, 각각이 36비트 레지듀를 1비트 삭감하기 위해 1비트 감소 연산을 행하는 네 개의 독립된 1비트 감소 스테이지를 포함하는 스테이지 712에 입력된다. 결국 네 번의 1비트 감소 연산이 스테이지 712에서 행해졌고, 32비트 레지듀는 데이터 스트림의 다음 8비트 세그먼트를 처리하기 위해 피드백된다.

이것이 데이터 스트림의 마지막 32비트 데이터 블록의 마지막 8비트 세그먼트이면, 이것은, 데이터 스트림이 송신되고 있는 중인 경우 데이터 스트림에 첨부될 수 있고, 또는 데이터 스트림이 파손되지 않았음을 확인하기 위해 수신된 CRC와 비교될 수 있는 마지막 레지듀이다.

스테이지 710, 712는 마지막 레지듀에 대하여 스테이지 출력 및 초기 입력이 서로 합치하도록 구성된다. 다른 다항식에 대한 재프로그래밍은 단지 다른 미리 계산된 다항식 K를 계산하는 것을 필요로 한다. 미리 계산된 다항식 K는 다항식 생성의 순서의 데이터의 i-0 및 k 비트가 뒤따르는 리딩 1비트 (i+kth)비트를 갖는다. 데이터의 k 최하위 비트만이 저장되어 상술한 바와 같이 다른 마이크로 연산에서 사용된다. 피연산자가 2n비트를 갖는 실시예에서, k는 n비트이다. 예컨대, 64비트 피연산자를 갖는 실시예에서, k는 미리 계산된 다항식 K의 32 최하위 비트이다.

도 8은 도 7에 나타낸 4비트 감소 스테이지(710)를 나타내는 블록도이다. 4비트 감소 스테이지(710)는 40비트 입력을 수신하고, 32비트 K 미리 계산된 다항식을 사용하여 입력 데이터 세그먼트를 36비트 출력으로 삭감한다. 우선, 40비트 입력 데이터 세그먼트 T[39:36]의 4 최상위 비트 및 32비트 K 미리 계산된 다항식 K[31:0]을 사용하여 4×32 곱셈 연산이 곱셈 로직(800)에서 행해진다. 다음으로, 32비트 레지듀를 계속 계산하기 위해 다음 감소 스테이지(712)(도 7)로 전송되는 36비트 출력 T[3:0]을 제공하기 위해, 곱셈 연산의 36비트 결과 및 40비트 입력 데이터 세그먼트의 36 최하위 비트에 대하여 XOR 연산이 XOR 로직(802)에서 행해진다.

실시예에서, 4×32 곱셈 로직(800)은 AND 게이트의 어레이 및 복수의 XOR 게이트를 갖는 시프트 로직을 포함한다. AND 게이트의 어레이는 32 AND 게이트의 네 세트 및 40비트 입력 데이터 세그먼트의 4 최상위 비트의 각 하나에 대한 32 AND 게이트의 한 세트를 포함한다. 4 최상위 비트의 각각의 하나는 복수의 AND 게이트의 세트 중 하나에 있어서의 32비트 AND 게이트의 각각의 한 입력에 제공된다. 예컨대, T[39]는 제 1 세트에 있어서의 모든 32비트 AND 게이트 중 하나의 입력에 연결되고, T[38]은 제 2 세트에 있어서의 모든 32 NAND 게이트 중 하나의 입력에 연결된다. 각각의 최상위 비트는 32비트 K 미리 계산된 다항식 K[31:0]의 각각의 비트와 함께 AND 연산된다. 예컨대, 32 AND 게이트의 제 1 세트에서, 32 AND 게이트의 각각의 한 입력은 40비트 입력 데이터 세그먼트의 최상위 비트를 수신하고, 32 AND 게이트의 각각은 32비트 K 미리 계산된 다항식의 32비트의 각각의 하나를 수신한다.

AND 게이트 (128(32×4)) AND 게이트의 4 세트의 출력은 입력 데이터의 각각의 비트 위치에 따라 출력을 시프트(곱셈)하기 위해 시프트 로직에 연결된다. 최상위 비트(비트 39)에 대하여 동작하는 AND 게이트의 세트의 출력은 3비트 시프트되고, AND 게이트의 각 다음 세트는 0비트 시프트하는 마지막 세트로 이 시프트를 1비트 감소시킨다.

시프트된 36비트 결과는 스테이지 712로의 36비트 입력을 제공하기 위해 XOR 로직(802)에서(복수의 XOR 게이트를 사용하여) 입력 데이터(T[35:0])의 36 최하위 비트로부터 감산된다.

도 9는 본 발명의 원리에 따른 유연한 프로그램 가능한 CRC 연산을 행하는 방법의 실시예를 나타내는 흐름도이다. 도 9는 도 2 및 도 3과 함께 설명될 것이다.

유연한 CRC 명령어가 인출 및 복호 유닛(206)(도 2)에 의해 복호된 후, 실행 유닛(210)에 의한 유연한 CRC 명령어의 실행은 CRC 유닛(103)에서 유연한 CRC 명령어에 관련된 복수의 마이크로 연산을 행하게 한다.

상술한 바와 같이, CRC 유닛에서 CRC 연산을 행하기 위한 유연한 CRC 명령어(매크로 명령어)는 상징적으로 이하와 같이 규정될 수 있다.

Flex_CRC32 r64, r/m64

도 9를 참조하면, 블록 900에서, 확장 다항식 마이크로 연산(314)(도 3)은 레지스터 파일(304) 내의 레지스터(306)에 저장된 제 1 연산자에 있어서의 최상위 비트에 저장된 다항식을 수신한다. 확장 다항식 마이크로 연산(314)은 주어진 다항식에 대하여 CRC 확장 기능을 행하고, 유연한 CRC 명령어에 대한 CRC 감소(삭감) 마이크로 연산(318)에 의해 사용되는 미리 계산된 다항식 K를 제공한다. 실시예에서, 미리 계산된 다항식 K의 32 최하위 비트는 레지스터, 예컨대 레지스터 파일(304) 내의 레지스터(308) 또는 레지스터(310)에 저장되어 CRC 감소 마이크로 연산(318)에서 사용된다. 확장 다항식 마이크로 연산(314)은 상징적으로 이하와 같이 규정될 수 있다.

dest :=crc_expand_poly (-, source1), select_modifier

확장 다항식 마이크로 연산(314)은 32비트 미리 계산된 다항식 K=x36 MOD POLY를 계산한다. 갈로아 필드(GF(2))에 걸쳐 다항식의 제산으로서 모듈로 감소가 규정된다. 미리 계산된 다항식 K는 CRC 감소 마이크로 연산(318)(도 3)에 의해 사용된다. 처리는 블록 902에서 계속된다.

블록 902에서, 셔플 워드 마이크로 연산(316)은 레지스터 파일(304) 내의 레지스터(306)에 저장된 피연산자 1 및 레지스터(312)에 저장된(또는 레지스터(312)에 저장된 메모리 포인터에 의해 식별된 메모리 위치로부터) 피연산자 2를 수신한다. 셔플 워드 마이크로 연산(316)은 즉시 바이트에 저장된 수식자("선택 수식자")에 따라 피연산자의 각각에 있어서의 64비트의 32비트 부분 중 하나를 선택한다. 셔플 워드 마이크로 연산(316)은 상징적으로 이하와 같이 규정될 수 있다.

dest :=shuffle_word(source2, source1), imm8

셔플 워드 마이크로 연산(316)은 64비트 데이터 경로의 두 32비트 절반 사이에서 워드 레벨 데이터(32비트)의 셔플을 이행한다. 셔플 워드 마이크로 연산(316)은 각각의 64비트 피연산자로부터 최상위 32비트 또는 최하위 32비트를 선택한다. 선택된 절반 내의 비트(32 최상위 비트 또는 3 최하위 비트)는 스왑될 수 있다. 각 피연산자 내의 비트의 셔플은 즉시 데이터(imm8)에 저장되는 4비트 셔플 선택 수식자에 의존한다. 셔플 워드 마이크로 연산(316)의 결과는 목적지 레지스터(dest)에 저장된다. 실시예에서, 결과는 다른 마이크로 연산에서의 사용을 위해 레지스터 파일(304) 내의 레지스터, 예컨대 레지스터(308) 또는 레지스터(310)에 저장될 수 있다.

이것이 유연한 CRC 매크로 명령어에서 셔플 워드 마이크로 연산(316)으로의 첫 번째 호출이면, 즉시 데이터는 최상위 32비트(DH)가 매크로 명령어에 의해 수신되는 64비트 제 2 연산자(op2)로부터 선택되는 것을 나타낸다. 처리는 블록 904에서 계속된다.

블록 904에서, 셔플 워드 마이크로 연산(316)으로부터의 32비트 데이터 출력에 있어서의 각 4바이트의 각각에 대하여 독립된 CRC 감소 마이크로 연산(318)이 행해진다. 셔플 워드 마이크로 연산(DH)으로부터의 32비트 초기 레지듀, 프로그램 가능한 다항식, 확장 다항식 마이크로 연산(314)에 의해 계산된 미리 계산된 다항식 K가 사용된다. 처리는 블록 906에서 계속된다.

블록 906에서, 감소되어야 할 32비트 데이터 블록(세그먼트) DH의 다른 바이트가 있다면, 처리는 블록 904에서 계속된다. 그렇지 않으면, 처리는 블록 908에서 계속된다.

블록 908에서, 셔플 워드 마이크로 연산(316)은 피연산자 1 및 피연산자 2를 수신하고, 즉시 바이트에 저장되는 수식자에 따라 피연산자의 각각에 있어서 64비트의 32비트의 하나를 선택한다. 이것은 유연한 CRC 감소 매크로 명령어에 대한 셔플 워드 마이크로 연산(316)으로의 두 번째 호출이므로, 최하위 32비트(DL)는 매크로 명령어에 의해 수신되는 제 2 피연산자(op2)로부터 선택된다. 처리는 블록 910에서 계속된다.

블록 910에서, 확장 다항식 마이크로 연산(314)에 의해 계산된 미리 계산된 다항식 K를 사용하여 셔플 워드 마이크로 연산(316)에 의한 32비트 데이터 출력에 있어서의 각 4바이트의 각각에 대하여 독립된 CRC 감소 마이크로 연산(318)이 행해진다. 처리는 블록 912에서 계속된다.

블록 912에서, 삭감할 32비트 데이터 블록(DL)에 다른 바이트가 있다면, 처리는 블록 910에서 계속된다. 그렇지 않으면, 처리는 블록 910에서 계속된다.

블록 914에서, 셔플 워드 마이크로 연산(316)은 두 CRC 감소 마이크로 연산(318)의 결과를 수신하고, 결과 및 n비트 다항식을 목적지(op1)에 저장한다.

축적된 레지듀 및 피연산자 1(유연한 CRC 매크로 명령어에 있어서 목적지 및 소스 레지스터이다)에 저장된 다항식으로, 유연한 CRC 명령어의 실행이 완료된다.

본 발명의 실시예에 관련된 방법은 컴퓨터 사용 가능한 매체를 포함하는 컴퓨터 프로그램 제품으로 구체화될 수 있음이 당업자에게 분명할 것이다. 예컨대, 그러한 컴퓨터 사용 가능한 매체는 CDROM(Compact Disk Read Only Memory) 디스크와 같은 ROM 장치, 또는 저장된 컴퓨터 판독 가능한 프로그램 코드를 갖는 컴퓨터 디스켓으로 이루어질 수 있다.

본 발명의 실시예는 특히 그 실시예를 참조하여 예시되고 설명되었지만, 첨부된 청구의 범위에 포함되는 본 발명의 실시예의 범위로부터 벗어나지 않고서 형태 및 세부 사항에 있어서 다양한 변경이 이루어질 수 있음이 당업자에 의해 이해될 것이다.

Claims (20)

- CRC(Cyclic Redundancy Check) 명령어에 대한 일련의 연산을 행하는 실행 유닛을 포함하고,

상기 CRC 명령어는 제 1 피연산자(operand) 및 제 2 피연산자를 갖고,

상기 일련의 연산은 상기 제 1 피연산자에 저장된 복수의 다른 n비트 다항식 중 하나를 사용하여 상기 제 2 피연산자에 저장된 2n비트 데이터 블록에 대하여 CRC 연산을 행하고, 상기 실행 유닛이, 미리 계산된 다항식 K를 제공하기 위해 n비트 다항식을 확장하고, 상기 제 1 피연산자에 저장된 상기 n비트 다항식 및 현재의 n비트 레지듀(residue)와 상기 미리 계산된 다항식 K를 사용하여 상기 2n비트 데이터 블록에 대하여 n비트 레지듀를 제공하기 위해 상기 2n비트 데이터 블록에 대하여 일련의 마이크로 연산을 행하도록 하는

장치.

- 제 1 항에 있어서,

상기 n비트 다항식은 n+1의 최대 차수를 갖는 장치.

- 제 1 항에 있어서,

상기 제 1 피연산자는 2n비트를 갖고, 상기 제 2 피연산자는 2n비트를 갖는 장치.

- 제 3 항에 있어서,

n은 32인 장치.

- 제 1 항에 있어서,

상기 제 1 피연산자는 소스 및 목적지이고, 상기 n비트 레지듀는 상기 제 1 피연산자에 저장되는 장치.

- 제 1 항에 있어서,

상기 일련의 마이크로 연산은 2n비트 목적지 피연산자에 저장하기 위해 상기 2n비트 제 1 피연산자로부터 n비트 부분을 선택하고 상기 2n비트 제 2 피연산자로부터 n비트 부분을 선택함으로써 셔플을 행하는 셔플 워드 마이크로 명령어를 포함하는 장치.

- 제 6 항에 있어서,

상기 셔플 워드 마이크로 명령어는 상기 각각의 n비트 부분 내의 비트를 셔플하는 장치.

- 제 1 항에 있어서,

상기 일련의 마이크로 연산은, n+4비트 중간 레지듀를 제공하기 위해 또한 상기 n비트 다항식을 사용하여 상기 n+4 중간 레지듀를 n비트 레지듀로 감소시키기 위해, 상기 미리 계산된 다항식 K를 사용하여 n+8비트 데이터를 감소시키는 CRC 감소 마이크로 명령어를 포함하는 장치.

- CRC 명령어에 대한 일련의 연산을 행하는 단계를 포함하고,

상기 CRC 명령어는 제 1 피연산자 및 제 2 피연산자를 갖고,

상기 일련의 연산은 상기 제 1 피연산자에 저장된 복수의 다른 n비트 다항식 중 하나를 사용하여 상기 제 2 피연산자에 저장된 2n비트 데이터 블록에 대하여 CRC 연산을 행하고, 상기 일련의 연산을 행하는 단계는 미리 계산된 다항식 K를 제공하기 위해 n비트 다항식을 확장하는 단계와, 상기 제 1 피연산자에 저장된 상기 n비트 다항식 및 현재의 n비트 레지듀와 상기 미리 계산된 다항식 K를 사용하여 상기 2n비트 데이터 블록에 대하여 n비트 레지듀를 제공하기 위해 상기 2n비트 데이터 블록에 대하여 일련의 마이크로 연산을 행하는 단계를 포함하는

방법.

- 제 9 항에 있어서,

상기 n비트 다항식은 n+1의 최대 차수를 갖는 방법.

- 제 9 항에 있어서,

상기 제 1 피연산자는 2n비트를 갖고, 상기 제 2 피연산자는 2n비트를 갖는 방법.

- 제 11 항에 있어서,

n은 32인 방법.

- 제 9 항에 있어서,

상기 제 1 피연산자는 소스 및 목적지이고, 상기 n비트 레지듀는 상기 제 1 피연산자에 저장되는 방법.

- 제 9 항에 있어서,

상기 일련의 마이크로 연산을 행하는 단계는 2n비트 목적지 피연산자에 저장하기 위해 상기 2n비트 제 1 피연산자로부터 n비트 부분을 선택하고 상기 2n비트 제 2 피연산자로부터 n비트 부분을 선택함으로써 셔플을 행하는 단계를 포함하는 방법.

- 제 14 항에 있어서,

상기 셔플을 행하는 단계는 상기 각각의 n비트 부분 내의 비트를 셔플하는 방법.

- 제 9 항에 있어서,

상기 일련의 마이크로 연산을 행하는 단계는, n+4비트 중간 레지듀를 제공하기 위해 또한 상기 n비트 다항식을 사용하여 상기 n+4 중간 레지듀를 n비트 레지듀로 감소시키기 위해, 상기 미리 계산된 다항식 K를 사용하여 n+8비트 데이터를 감소시키는 단계를 포함하는 방법. - 관련된 정보를 갖고 머신으로 액세스할 수 있는 매체를 포함하는 물품으로서,

상기 정보는, 액세스되었을 때, 머신이 CRC 명령어에 대한 일련의 연산을 행하는 단계를 행하게 하고,

상기 CRC 명령어는 제 1 피연산자 및 제 2 피연산자를 갖고,

상기 일련의 연산은 상기 제 1 피연산자에 저장된 복수의 다른 n비트 다항식 중 하나를 사용하여 상기 제 2 피연산자에 저장된 2n비트 데이터 블록에 대하여 CRC 연산을 행하고, 상기 일련의 연산을 행하는 단계는 미리 계산된 다항식 K를 제공하기 위해 n비트 다항식을 확장하는 단계와, 상기 제 1 피연산자에 저장된 상기 n비트 다항식 및 현재의 n비트 레지듀와 상기 미리 계산된 다항식 K를 사용하여 상기 2n비트 데이터 블록에 대하여 n비트 레지듀를 제공하기 위해 상기 2n비트 데이터 블록에 대하여 일련의 마이크로 연산을 행하는 단계를 포함하는

물품.

- 제 17 항에 있어서,

상기 일련의 마이크로 연산을 행하는 단계는, n+4비트 중간 레지듀를 제공하기 위해 또한 상기 n비트 다항식을 사용하여 상기 n+4 중간 레지듀를 n비트 레지듀로 감소시키기 위해, 상기 미리 계산된 다항식 K를 사용하여 n+8비트 데이터를 감소시키는 단계를 포함하는 물품.

- 데이터 및 명령어를 저장하기 위한 동적인 랜덤 액세스 메모리와,

상기 명령어를 실행하기 위한 상기 메모리에 연결된 프로세서

를 포함하고,

상기 프로세서는 CRC 명령어에 대한 일련의 연산을 행하는 실행 유닛을 포함하고,

상기 CRC 명령어는 제 1 피연산자 및 제 2 피연산자를 갖고,

상기 일련의 연산은 상기 제 1 피연산자에 저장된 복수의 다른 n비트 다항식 중 하나를 사용하여 상기 제 2 피연산자에 저장된 2n비트 데이터 블록에 대하여 CRC 연산을 행하고, 상기 실행 유닛이, 미리 계산된 다항식 K를 제공하기 위해 n비트 다항식을 확장하고, 상기 제 1 피연산자에 저장된 상기 n비트 다항식 및 현재의 n비트 레지듀와 상기 미리 계산된 다항식 K를 사용하여 상기 2n비트 데이터 블록에 대하여 n비트 레지듀를 제공하기 위해 상기 2n비트 데이터 블록에 대하여 일련의 마이크로 연산을 행하도록 하는

시스템.

- 제 19 항에 있어서,

상기 일련의 마이크로 연산을 행하는 것은, n+4비트 중간 레지듀를 제공하기 위해 또한 상기 n비트 다항식을 사용하여 상기 n+4 중간 레지듀를 n비트 레지듀로 감소시키기 위해, 상기 미리 계산된 다항식 K를 사용하여 n+8비트 데이터를 감소시키는 것을 포함하는 시스템.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/653,249 | 2009-12-10 | ||

| US12/653,249 US8464125B2 (en) | 2009-12-10 | 2009-12-10 | Instruction-set architecture for programmable cyclic redundancy check (CRC) computations |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020130014281A Division KR101374958B1 (ko) | 2009-12-10 | 2013-02-08 | 프로그램 가능한 crc 계산을 위한 명령어 집합 구조 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20110066106A true KR20110066106A (ko) | 2011-06-16 |

| KR101266746B1 KR101266746B1 (ko) | 2013-05-28 |

Family

ID=43993029

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020100125762A KR101266746B1 (ko) | 2009-12-10 | 2010-12-09 | 프로그램 가능한 crc 계산을 위한 명령어 집합 구조 |

| KR1020130014281A KR101374958B1 (ko) | 2009-12-10 | 2013-02-08 | 프로그램 가능한 crc 계산을 위한 명령어 집합 구조 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020130014281A KR101374958B1 (ko) | 2009-12-10 | 2013-02-08 | 프로그램 가능한 crc 계산을 위한 명령어 집합 구조 |

Country Status (6)

| Country | Link |

|---|---|

| US (3) | US8464125B2 (ko) |

| JP (1) | JP5226062B2 (ko) |

| KR (2) | KR101266746B1 (ko) |

| CN (1) | CN102096609B (ko) |

| DE (1) | DE102010049322B4 (ko) |

| TW (1) | TWI464579B (ko) |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7958436B2 (en) * | 2005-12-23 | 2011-06-07 | Intel Corporation | Performing a cyclic redundancy checksum operation responsive to a user-level instruction |

| US8607129B2 (en) | 2011-07-01 | 2013-12-10 | Intel Corporation | Efficient and scalable cyclic redundancy check circuit using Galois-field arithmetic |

| JP2013210837A (ja) * | 2012-03-30 | 2013-10-10 | Fujitsu Ltd | 演算回路及び演算方法 |

| US9904591B2 (en) * | 2014-10-22 | 2018-02-27 | Intel Corporation | Device, system and method to restrict access to data error information |

| US9740558B2 (en) | 2015-05-31 | 2017-08-22 | Intel Corporation | On-die ECC with error counter and internal address generation |

| US10127101B2 (en) | 2015-08-28 | 2018-11-13 | Intel Corporation | Memory device error check and scrub mode and error transparency |

| US9384086B1 (en) * | 2015-11-30 | 2016-07-05 | International Business Machines Corporation | I/O operation-level error checking |

| US9354967B1 (en) | 2015-11-30 | 2016-05-31 | International Business Machines Corporation | I/O operation-level error-handling |

| EP3217287A1 (de) * | 2016-03-11 | 2017-09-13 | Siemens Aktiengesellschaft | Verfahren und einrichtung zur erkennung von fehlern bei der speicherung oder übertragung von daten |

| US10243583B2 (en) * | 2017-06-16 | 2019-03-26 | Western Digital Technologies, Inc. | CPU error remediation during erasure code encoding |

| CN108038014B (zh) * | 2017-11-30 | 2021-06-04 | 中国人民解放军国防科技大学 | 一种图像压缩多核并行容错方法、计算机、处理器 |

| CN108628698B (zh) * | 2018-05-08 | 2019-11-05 | 华为技术有限公司 | 计算crc编码的方法和装置 |

| CN109861788B (zh) * | 2019-01-11 | 2021-12-10 | 中电海康集团有限公司 | 一种并行crc计算的实现方法及装置 |

| CN110515656B (zh) * | 2019-08-28 | 2021-07-16 | 中国人民解放军国防科技大学 | 一种casp指令的执行方法、微处理器及计算机设备 |

| CN112036117B (zh) * | 2020-08-28 | 2023-06-20 | 西安微电子技术研究所 | 一种适用于多种位宽并行输入数据的crc校验控制系统 |

| CN112954523B (zh) * | 2021-01-29 | 2023-06-02 | 佳禾智能科技股份有限公司 | 一种tws耳机的校验方法 |

| CN115408574A (zh) | 2021-05-28 | 2022-11-29 | 南宁富联富桂精密工业有限公司 | 数据分析方法、装置及计算机可读存储介质 |

| CN114443347B (zh) * | 2021-12-23 | 2022-11-22 | 湖南毂梁微电子有限公司 | 一种可配置crc码计算方法 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3175759B2 (ja) | 1997-01-31 | 2001-06-11 | 日本電気株式会社 | 無線ネットワークインタフェースカード及び無線ネットワークインタフェースカードのためのキュー管理方法 |

| JPH10320221A (ja) * | 1997-05-16 | 1998-12-04 | Hitachi Ltd | プロセッサ |

| JP3255130B2 (ja) * | 1998-12-16 | 2002-02-12 | 村田機械株式会社 | データ検査方法及び装置並びに記録媒体 |

| US6848072B1 (en) | 2000-09-19 | 2005-01-25 | Bbn Solutions Llc | Network processor having cyclic redundancy check implemented in hardware |

| US6836869B1 (en) * | 2001-02-02 | 2004-12-28 | Cradle Technologies, Inc. | Combined cyclic redundancy check (CRC) and Reed-Solomon (RS) error checking unit |

| US7216285B2 (en) * | 2001-11-09 | 2007-05-08 | Marvell International Ltd. | System and method for generating cyclic redundancy check |

| US20040098655A1 (en) | 2002-11-19 | 2004-05-20 | Sharma Debendra Das | Rolling CRC scheme for improved error detection |

| CN100493075C (zh) * | 2003-11-06 | 2009-05-27 | 西安电子科技大学 | 变长数据分组与定长信元混合传送的方法与适配装置 |

| US7171604B2 (en) | 2003-12-30 | 2007-01-30 | Intel Corporation | Method and apparatus for calculating cyclic redundancy check (CRC) on data using a programmable CRC engine |

| EP1973554B1 (en) * | 2005-12-07 | 2015-01-14 | Isto Technologies Inc. | Cartilage repair methods |

| US7958436B2 (en) | 2005-12-23 | 2011-06-07 | Intel Corporation | Performing a cyclic redundancy checksum operation responsive to a user-level instruction |

| US7925957B2 (en) * | 2006-03-20 | 2011-04-12 | Intel Corporation | Validating data using processor instructions |

| US7827471B2 (en) * | 2006-10-12 | 2010-11-02 | Intel Corporation | Determining message residue using a set of polynomials |

| US9361104B2 (en) * | 2010-08-13 | 2016-06-07 | Freescale Semiconductor, Inc. | Systems and methods for determining instruction execution error by comparing an operand of a reference instruction to a result of a subsequent cross-check instruction |

-

2009

- 2009-12-10 US US12/653,249 patent/US8464125B2/en active Active

-

2010

- 2010-10-13 TW TW099134899A patent/TWI464579B/zh not_active IP Right Cessation

- 2010-10-22 DE DE102010049322.8A patent/DE102010049322B4/de active Active

- 2010-12-03 JP JP2010269989A patent/JP5226062B2/ja not_active Expired - Fee Related

- 2010-12-06 CN CN201010581502.XA patent/CN102096609B/zh active Active

- 2010-12-09 KR KR1020100125762A patent/KR101266746B1/ko active IP Right Grant

-

2013

- 2013-02-08 KR KR1020130014281A patent/KR101374958B1/ko active IP Right Grant

- 2013-03-11 US US13/793,358 patent/US8732548B2/en active Active

-

2014

- 2014-04-16 US US14/254,233 patent/US9047082B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN102096609A (zh) | 2011-06-15 |

| KR101374958B1 (ko) | 2014-03-17 |

| TWI464579B (zh) | 2014-12-11 |

| TW201137600A (en) | 2011-11-01 |

| JP5226062B2 (ja) | 2013-07-03 |

| KR101266746B1 (ko) | 2013-05-28 |

| DE102010049322A1 (de) | 2011-06-16 |

| US8732548B2 (en) | 2014-05-20 |

| KR20130031863A (ko) | 2013-03-29 |

| US20110145683A1 (en) | 2011-06-16 |

| CN102096609B (zh) | 2017-04-12 |

| US9047082B2 (en) | 2015-06-02 |

| DE102010049322B4 (de) | 2022-09-15 |

| US20130191699A1 (en) | 2013-07-25 |

| JP2011123884A (ja) | 2011-06-23 |

| US8464125B2 (en) | 2013-06-11 |

| US20140229807A1 (en) | 2014-08-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101374958B1 (ko) | 프로그램 가능한 crc 계산을 위한 명령어 집합 구조 | |

| US7562283B2 (en) | Systems and methods for error correction using binary coded hexidecimal or hamming decoding | |

| US7313583B2 (en) | Galois field arithmetic unit for use within a processor | |

| US9680605B2 (en) | Method of offloading cyclic redundancy check on portions of a packet | |

| US7343472B2 (en) | Processor having a finite field arithmetic unit utilizing an array of multipliers and adders | |

| US20050010630A1 (en) | Method and apparatus for determining a remainder in a polynomial ring | |

| WO1999035575A1 (en) | A physical block address recovery apparatus, system and method for cyclic error correction codes | |

| WO1997000559A1 (en) | Dedicated alu architecture for 10-bit reed-solomon error correction module | |

| US7403964B2 (en) | Galois field multiplier array for use within a finite field arithmetic unit | |

| Kounavis et al. | Novel table lookup-based algorithms for high-performance CRC generation | |

| JP2001524274A (ja) | 短縮ファイア符号エラートラッピング復号方法および装置 | |

| WO2013104960A1 (en) | Incremental modification of an error detection code | |

| JP2004159333A (ja) | 巡回冗長検査(crc)符号を用いたデータを交換するための構成、ならびにデータバス上で交換されているデータからcrc符号を自動的に生成するための方法および装置 | |

| JP2020524930A (ja) | 短縮レイテンシ誤り訂正復号 | |

| US20080140740A1 (en) | Systems and methods for processing data sets in parallel | |

| US8700688B2 (en) | Polynomial data processing operation | |

| JP2004206798A (ja) | 光ディスク装置のエンコードデータ符号回路 | |

| US6405339B1 (en) | Parallelized programmable encoder/syndrome generator | |

| JP2008146828A (ja) | 光ディスク装置のエンコードデータ符号回路 | |

| JP2005216477A (ja) | 選択的なpo補正を利用したdvdデコーディング方法及び装置 | |

| US11848686B2 (en) | Accelerated polynomial coding system and method | |

| US8381080B2 (en) | Reducing a degree of a polynomial in a polynomial division calculation | |

| EP2830226A1 (en) | Encoding and decoding methods and devices | |

| Viraktamath et al. | IMPLEMENTATION OF CRC ON DSPTMS320VC5416 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| AMND | Amendment | ||

| E601 | Decision to refuse application | ||

| A107 | Divisional application of patent | ||

| AMND | Amendment | ||

| X701 | Decision to grant (after re-examination) | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20160427 Year of fee payment: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20170504 Year of fee payment: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20180427 Year of fee payment: 6 |

|

| FPAY | Annual fee payment |

Payment date: 20190429 Year of fee payment: 7 |