KR101470713B1 - 버퍼링된 저장을 이용하여 트랜잭션들을 가속화하기 위한 메커니즘들 - Google Patents

버퍼링된 저장을 이용하여 트랜잭션들을 가속화하기 위한 메커니즘들 Download PDFInfo

- Publication number

- KR101470713B1 KR101470713B1 KR1020127018482A KR20127018482A KR101470713B1 KR 101470713 B1 KR101470713 B1 KR 101470713B1 KR 1020127018482 A KR1020127018482 A KR 1020127018482A KR 20127018482 A KR20127018482 A KR 20127018482A KR 101470713 B1 KR101470713 B1 KR 101470713B1

- Authority

- KR

- South Korea

- Prior art keywords

- transaction

- block

- data

- write

- buffered

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0806—Multiuser, multiprocessor or multiprocessing cache systems

- G06F12/0811—Multiuser, multiprocessor or multiprocessing cache systems with multilevel cache hierarchies

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0806—Multiuser, multiprocessor or multiprocessing cache systems

- G06F12/0815—Cache consistency protocols

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0806—Multiuser, multiprocessor or multiprocessing cache systems

- G06F12/0815—Cache consistency protocols

- G06F12/0831—Cache consistency protocols using a bus scheme, e.g. with bus monitoring or watching means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0806—Multiuser, multiprocessor or multiprocessing cache systems

- G06F12/0815—Cache consistency protocols

- G06F12/0831—Cache consistency protocols using a bus scheme, e.g. with bus monitoring or watching means

- G06F12/0833—Cache consistency protocols using a bus scheme, e.g. with bus monitoring or watching means in combination with broadcast means (e.g. for invalidation or updating)

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/10—Address translation

- G06F12/1027—Address translation using associative or pseudo-associative address translation means, e.g. translation look-aside buffer [TLB]

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/3004—Arrangements for executing specific machine instructions to perform operations on memory

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30076—Arrangements for executing specific machine instructions to perform miscellaneous control operations, e.g. NOP

- G06F9/30087—Synchronisation or serialisation instructions

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/466—Transaction processing

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/466—Transaction processing

- G06F9/467—Transactional memory

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/52—Program synchronisation; Mutual exclusion, e.g. by means of semaphores

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/62—Details of cache specific to multiprocessor cache arrangements

- G06F2212/621—Coherency control relating to peripheral accessing, e.g. from DMA or I/O device

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Memory System Of A Hierarchy Structure (AREA)

- Information Retrieval, Db Structures And Fs Structures Therefor (AREA)

Abstract

일 실시예에서, 본 발명은 제1 스레드에서 트랜잭션 메모리(TM) 트랜잭션을 실행하고, 프로세서의 캐시 메모리의 제1 버퍼 내에 데이터의 블록을 버퍼링하고, 상기 제1 버퍼 내의 상기 블록의 위치에 있는 데이터가 갱신되는 만남 시에 상기 블록의 소유권을 얻기 위해 상기 블록에 대한 기록 모니터를 획득하기 위한 방법을 포함한다. 다른 실시예들이 설명되고 청구된다.

Description

소프트웨어 트랜잭션 메모리(STM) 시스템들은 트랜잭션들 내에서 변경된 데이터의 다수의 버전을 유지하는 버전 관리 메커니즘을 필요로 한다. 두 가지 버전 관리 접근법이 존재하며, 이들 각각은 소프트웨어로 구현될 때 오버헤드들을 갖는다. 제1 접근법은 이거 버저닝(eager versioning)으로 지칭되는데, 이거 버저닝에서는 새로운 데이터 값이 적소에 기록되고, 오래된 값이 롤백(rollback)의 경우에 언두 로그(undo log) 내에 저장된다. 이러한 접근법은 2개의 오버헤드를 갖는데, 즉 각각의 기록시에 언두 로그를 유지하고, 롤백 시에 언두 로그로부터 값들을 복원하는 것이다. 일부 언어-레벨 TM 메모리 모델들은 이거 버저닝을 사용하지 않는데, 그 이유는 이거 버저닝이 논-트랜잭션 액세스들(non-transactional accesses)에게 추론 값들(speculative values)이 보이게 하기 때문이다.

제2 접근법은 레이지 버저닝(lazy versioning)으로 지칭되는데, 레이지 버저닝에서는 새로운 데이터 값들이 소프트웨어 기록 버퍼 내에 기록된 후에 커미트(commit) 시에 그들의 목적 위치들에 복사된다. 이러한 접근법은 3개의 오버헤드를 갖는데, 즉 소프트웨어 기록 버퍼를 유지하고, 판독 시에 소프트웨어 기록 버퍼 내의 값들을 탐색하고, 커미트 시에 소프트웨어 기록 버퍼로부터 값들을 복사하는 것이다. 레이지 버저닝은 기록된 데이터를 만남 시에 또는 커미트 시에 록킹(locking)할 수 있는 반면, 이거 버저닝은 만남 시에만 록킹할 수 있다. 양 접근법에서 파악되듯이, STM 시스템에 대해 버전 관리의 상당한 오버헤드가 존재한다.

도 1은 본 발명의 일 실시예에 따른 프로세서의 블록도이다.

도 2는 본 발명의 일 실시예에 따른 프로세서에서의 데이터 아이템에 대한 메타데이터의 유지의 블록도이다.

도 3a는 본 발명의 일 실시예에 따른 이거 기록 록킹 및 모니터링을 수행하기 위한 방법의 흐름도이다.

도 3b는 본 발명의 일 실시예에 따른 이거 기록 모니터링 및 록킹 트랜잭션에서 트랜잭션 커미트를 수행하기 위한 방법의 흐름도이다.

도 4a는 본 발명의 일 실시예에 따른 레이지 기록 록킹 및 모니터링을 수행하기 위한 방법의 흐름도이다.

도 4b는 본 발명의 일 실시예에 따른 레이지 기록 모니터링 및 록킹 트랜잭션을 위한 커미트 방법의 흐름도이다.

도 5는 본 발명의 일 실시예에 따른 메타데이터를 이용하여 객체의 섀도 사본(shadow copy)의 위치를 효율적으로 결정하는 방법의 흐름도이다.

도 6은 본 발명의 일 실시예에 따른 시스템의 블록도이다.

도 2는 본 발명의 일 실시예에 따른 프로세서에서의 데이터 아이템에 대한 메타데이터의 유지의 블록도이다.

도 3a는 본 발명의 일 실시예에 따른 이거 기록 록킹 및 모니터링을 수행하기 위한 방법의 흐름도이다.

도 3b는 본 발명의 일 실시예에 따른 이거 기록 모니터링 및 록킹 트랜잭션에서 트랜잭션 커미트를 수행하기 위한 방법의 흐름도이다.

도 4a는 본 발명의 일 실시예에 따른 레이지 기록 록킹 및 모니터링을 수행하기 위한 방법의 흐름도이다.

도 4b는 본 발명의 일 실시예에 따른 레이지 기록 모니터링 및 록킹 트랜잭션을 위한 커미트 방법의 흐름도이다.

도 5는 본 발명의 일 실시예에 따른 메타데이터를 이용하여 객체의 섀도 사본(shadow copy)의 위치를 효율적으로 결정하는 방법의 흐름도이다.

도 6은 본 발명의 일 실시예에 따른 시스템의 블록도이다.

본 발명의 실시예들을 이용하면, 하드웨어 버퍼(예를 들어, 캐시 또는 다른 제한된 크기의 하드웨어 버퍼)에 적합한 기록 세트를 갖는 트랜잭션들에 대한 버전 관리를 가속화하도록 값들을 버퍼링하기 위해 하드웨어 지원이 제공될 수 있다. 트랜잭션 기록들을 캐시 내에 버퍼링함으로써, 레이지 버저닝이 하드웨어로 수행될 수 있으며, 따라서 소프트웨어 버전 관리의 오버헤드를 없앨 수 있고, 따라서 소프트웨어 트랜잭션 메모리 시스템들을 가속화할 수 있다.

실시예들은 이거 및 레이지 버저닝 모두를 수행하고 캐시 상주 및 무제한 판독 세트들에 대한 하드웨어 지원과 결합될 수 있는 소프트웨어 트랜잭션 메모리 시스템들을 가속화하기 위해 더 이용될 수 있다. 일 실시예에서, (명령어 세트 아키텍처(ISA)의 사용자 레벨 명령어일 수 있는) 명시적인 버퍼링된 저장 명령어가 트랜잭션 기록을 캐시에 저장하는 데 사용될 수 있다. 게다가, (ISA의 상이한 사용자 레벨 명령어일 수 있는) 명시적인 기록 모니터 명령어가 버퍼링된 저장과 동시, 예컨대 만남 시간에(만남 시간 기록 모니터링) 또는 커미트 시에(커미트 시간 기록 모니터링) 버퍼링된 캐시 라인들의 배타적인 소유권을 획득하는 데 사용될 수 있다. 일부 구현들에서는, 버퍼링된 기록 및 기록 모니터 둘 다를 수행하기 위해 단일 명령어가 사용될 수 있다. 이러한 사용자 레벨 명령어들 및 본 발명의 일 실시예에 따른 다른 기술들은 원시 코드 및 객체 기반 시스템들에 대해 모두 사용될 수 있다.

아래 더 설명되는 바와 같이, 모니터링은 더 빠른 충돌 검출, 즉 병행하여 실행하려고 시도하고 있는 2개의 트랜잭션 사이의 충돌들의 검출을 지원하기 위해 소프트웨어에 의해 사용될 수 있는 하드웨어 특징이다. 일반적으로, 모니터링은 더 낮은 비용으로 소프트웨어 록과 유사한 기능을 제공할 수 있다. 물리 메모리의 각각의 파티션(모니터 블록)은 각각의 스레드에 대한 비공개 판독 모니터 및 기록 모니터를 가질 수 있다. 대안으로서, 기록 배리어들(barriers)이 하드웨어로 암시적으로 수행될 수 있다. 액세스되는 데이터 값의 록킹 및 기록 모니터링은 상이한 구현들에서 만남 시간 또는 커미트 시간에 수행될 수 있다. (예로서, 캐시 오버플로우 또는 다른 트랜잭션에 의한 충돌하는 액세스로 인한) 임의의 버퍼링된 라인의 손실은 트랜잭션의 중단 및 재시작을 유발한다는 점에 유의한다.

무제한 TM(UTM) 시스템에서 사용될 수 있는 구현들의 배경으로서, UTM 트랜잭션들을 위해 사용될 수 있는 예시적인 하드웨어를 고찰하는 것이 도움이 된다. 일반적으로, UTM 트랜잭션은 하드웨어로 완전히 구현될 수 있는 트랜잭션들, 즉 캐시 상주 트랜잭션들, 및 하드웨어와 소프트웨어의 조합을 이용하여 실행되는 무제한 트랜잭션들과 관련하여 하드웨어의 사용을 가능하게 한다. 도 1을 참고하면, 다수의 스레드를 동시에 실행할 수 있는 프로세서의 일 실시예가 도시되어 있다. 프로세서(100)는 하드웨어 트랜잭션 실행을 위한 하드웨어 지원을 포함할 수 있다는 점에 유의한다. 하드웨어 트랜잭션 실행과 더불어 또는 개별적으로, 프로세서(100)는 STM의 하드웨어 가속화, STM의 개별 실행 또는 이들의 조합을 위한 하드웨어 지원, 예를 들어 본 발명의 일 실시예에 따른 UTM도 제공할 수 있다. 프로세서(100)는 마이크로프로세서, 내장 프로세서, 디지털 신호 프로세서(DSP), 네트워크 프로세서 또는 코드를 실행하기 위한 다른 장치와 같은 임의 타입의 프로세서일 수 있다. 프로세서(100)는 도시된 바와 같이 복수의 처리 요소를 포함한다.

물리 프로세서(100)는 도 1에 도시된 바와 같이 상위 레벨 캐시(110)에 대한 액세스를 공유하는 2개의 코어, 즉 코어(101) 및 코어(102)를 포함한다. 프로세서(100)는 비대칭 코어들, 즉 상이한 구성들, 기능 유닛들 및/또는 논리를 갖는 코어들을 포함할 수도 있지만, 대칭 코어들이 도시되어 있다. 결과적으로, 코어(101)와 동일한 것으로 도시된 코어(102)는 반복 설명을 피하기 위해 상세히 설명되지 않을 것이다. 게다가, 코어(101)는 2개의 하드웨어 스레드(101a, 101b)를 포함하고, 코어(102)는 2개의 하드웨어 스레드(102a, 102b)를 포함한다. 따라서, 운영 체제와 같은 소프트웨어 엔티티들은 잠재적으로는 프로세서(100)를 4개의 개별 프로세서, 즉 4개의 소프트웨어 스레드를 동시에 실행할 수 있는 4개의 논리 프로세서 또는 처리 요소로서 간주한다.

여기서, 제1 스레드는 아키텍처 상태 레지스터들(101a)과 관련되고, 제2 스레드는 아키텍처 상태 레지스터들(101b)과 관련되고, 제3 스레드는 아키텍처 상태 레지스터들(102a)과 관련되며, 제4 스레드는 아키텍처 상태 레지스터들(102b)과 관련된다. 도시된 바와 같이, 아키텍처 상태 레지스터들(101a)은 아키텍처 상태 레지스터들(101b)에서 복제되며, 따라서 논리 프로세서(101a) 및 논리 프로세서(101b)에 대해 개별적인 아키텍처 상태들/상황들이 저장될 수 있다. 아키텍처 상태 레지스터들은 일 실시예에서 UTM 트랜잭션의 구현에 사용하기 위한 레지스터들, 예를 들어 트랜잭션 상태 레지스터(TSR), 트랜잭션 제어 레지스터(TCR) 및 트랜잭션 동안 발생하는 (트랜잭션의 중단과 같은) 이벤트들을 처리하는 데 사용될 수 있는 이젝션 핸들러(ejection handler)의 위치를 식별하기 위한 이젝션 명령어 포인터 레지스터를 포함할 수 있다.

명령어 포인터들 및 새 이름 할당기 논리(130) 내의 개명 논리와 같은 다른 더 작은 자원들도 스레드들(101a, 101b)을 위해 복제될 수 있다. 재배열/회수 유닛(135) 내의 재배열 버퍼들, 명령어 변환 룩어사이드 버퍼(ITLB)(120), 로드/저장 버퍼들 및 큐들과 같은 일부 자원들은 파티셔닝을 통해 공유될 수 있다. 범용 내부 레지스터들, 페이지-테이블 베이스 레지스터, 저레벨 데이터-캐시 및 데이터-TLB(115), 실행 유닛(들)(140), 및 무질서 유닛(135)의 부분들과 같은 다른 자원들은 잠재적으로는 완전히 공유된다.

도시된 바와 같이, 프로세서(100)는 시스템 메모리(175), 칩셋, 노스브리지 또는 다른 집적 회로와 같은, 프로세서(100) 외부의 장치들과 통신하기 위한 버스 인터페이스 모듈(105)을 포함한다. 메모리(175)는 프로세서(100) 전용이거나, 시스템 내의 다른 장치들과 공유될 수 있다. 상위 레벨 또는 퍼더-아웃(further-out) 캐시(110)는 상위 레벨 캐시(110)로부터 최근에 페치된 요소들을 캐싱한다. 상위 레벨 또는 퍼더 아웃은 증가하거나 실행 유닛(들)로부터 더 먼 캐시 레벨들을 지칭한다는 점에 유의한다. 일 실시예에서, 상위 레벨 캐시(110)는 제2 레벨 데이터 캐시이다. 그러나, 상위 레벨 캐시(110)는 명령어 캐시와 관련되거나 포함할 수 있으므로 그에 한정되지 않는다. 최근에 디코딩된 트레이스들을 저장하기 위해 디코더(125) 뒤에 트레이스 캐시, 즉 일 타입의 명령어 캐시가 대신 결합될 수 있다. 모듈(120)은 또한 잠재적으로는 실행될/취해질 분기들을 예측하기 위한 분기 타겟 버퍼 및 명령어들에 대한 어드레스 변환 엔트리들을 저장하기 위한 ITLB를 포함한다.

디코드 모듈(125)은 페치 유닛(120)에 결합되어, 페치된 요소들을 디코딩한다. 일 실시예에서, 프로세서(100)는 프로세서(100) 상에서 실행 가능한 명령어들을 정의/지정하는 ISA와 관련된다. 여기서, ISA에 의해 인식되는 머신 코드 명령어들은 종종 실행될 명령어 또는 연산을 참조/지정하는 오피코드(opcode)로서 지칭되는 명령어의 일부를 포함한다.

일례에서, 할당기 및 개명기 블록(130)은 명령어 처리 결과들을 저장하기 위한 레지스터 파일들과 같은 자원들을 예약하기 위한 할당기를 포함한다. 그러나, 스레드들(101a, 101b)은 잠재적으로는 무질서 실행이 가능하며, 할당기 및 개명기 블록(130)은 또한 명령어 결과들을 추적하기 위한 재배열 버퍼들과 같은 다른 자원들을 예약한다. 유닛(130)은 프로그램/명령어 참조 레지스터들을 프로세서(100) 내부의 다른 레지스터들로 개명하기 위한 레지스터 개명기도 포함할 수 있다. 재배열/회수 유닛(135)은 무질서 실행 및 이후의 무질서로 실행되는 명령어들의 순차적 회수를 지원하기 위해, 전술한 재배열 버퍼들, 로드 버퍼들 및 저장 버퍼들과 같은 컴포넌트들을 포함한다.

스케줄러 및 실행 유닛(들) 블록(140)은 일 실시예에서 실행 유닛들 상의 명령어들/연산을 스케줄링하기 위한 스케줄러 유닛을 포함한다. 예를 들어, 이용 가능한 부동 소수점 실행 유닛을 갖는 실행 유닛의 포트 상에 부동 소수점 명령어가 스케줄링된다. 정보 명령어 처리 결과들을 저장하기 위해 실행 유닛들과 관련된 레지스터 파일들도 포함된다. 예시적인 실행 유닛들은 부동 소수점 실행 유닛, 정수 실행 유닛, 점프 실행 유닛, 로드 실행 유닛, 저장 실행 유닛 및 다른 공지된 실행 유닛들을 포함한다.

하위 레벨 데이터 캐시 및 데이터 변환 버퍼(D-TLB)(150)는 실행 유닛(들)(140)에 결합된다. 데이터 캐시는 잠재적으로는 메모리 일관성 상태들에 유지되는 데이터 피연산자들과 같은 최근 사용된/연산된 요소들을 저장한다. D-TLB는 최근의 가상/선형 대 물리 어드레스 변환들을 저장한다. 특정 예로서, 프로세서는 물리 메모리를 복수의 가상 페이지로 분할하기 위한 페이지 테이블 구조를 포함할 수 있다.

일 실시예에서, 프로세서(100)는 하드웨어 트랜잭션 실행, 소프트웨어 트랜잭션 실행 또는 이들의 조합 또는 혼합이 가능하다. 코드의 크리티컬 섹션(critical section) 또는 아토믹 섹션(atomic section)으로도 지칭될 수 있는 트랜잭션은 아토믹 그룹으로서 실행될 명령어들, 연산들 또는 마이크로 연산들의 그룹핑을 포함한다. 예를 들어, 명령어들 또는 연산들은 트랜잭션 또는 크리티컬 섹션을 획정하는 데 사용될 수 있다. 일 실시예에서, 이러한 명령어들은 전술한 디코더들과 같은 프로세서(100)의 하드웨어에 의해 인식될 수 있는 ISA와 같은 명령어들의 세트의 일부이다. 종종, 이러한 명령어들은 고레벨 언어로부터 하드웨어 인식 가능한 어셈블리 언어로 컴파일링되면 디코더들이 디코드 단계 동안 인식하는 명령어들의 연산 코드들(오피코드들) 또는 다른 부분들을 포함한다.

통상적으로, 트랜잭션의 실행 동안, 메모리에 대한 갱신들은 트랜잭션이 커미트될 때까지 전역적으로 보이지 않게 된다. 일례로서, 하나의 위치에 대한 트랜잭션 기록은 잠재적으로 국지 스레드에게 보이지만, 다른 스레드로부터의 판독에 응답하여, 기록 데이터는 트랜잭션 기록을 포함하는 트랜잭션이 커미트될 때까지 전달되지 않는다. 아래에 더 상세히 설명되는 바와 같이, 트랜잭션이 여전히 계속중(pending)인 동안, 메모리로부터 로딩되고 메모리 내에 기록되는 데이터 아이템들/요소들이 추적된다. 트랜잭션이 커미트 포인트에 도달하면, 트랜잭션에 대해 충돌들이 검출되지 않은 경우, 트랜잭션은 커미트되며, 트랜잭션 동안 행해진 갱신들은 전역적으로 보이게 된다.

그러나, 트랜잭션이 그의 계속중에 무효화되는 경우, 트랜잭션은 중단되며, 갱신들이 전역적으로 보이게 되지 않고 잠재적으로 재시작된다. 결과적으로, 본 명세서에서 사용될 때 트랜잭션의 계속(pendency)은 실행을 시작하였고 커미트 또는 중단되지 않은, 즉 계속중인 트랜잭션을 지칭한다.

일 실시예에서, 프로세서(100)는 하드웨어/논리를 이용하여, 즉 하드웨어 트랜잭션 메모리(HTM) 시스템 내에서 트랜잭션들을 실행할 수 있다. 다양한 특정 구현 상세들이 HTM을 구현할 때 아키텍처 및 마이크로 아키텍처 관점 양자에서 존재하며, 이들 중 대부분은 본 발명의 실시예들을 불필요하게 불명확하게 하는 것을 방지하기 위해 본 명세서에서는 설명되지 않는다. 그러나, 일부 구조들 및 구현들은 예시적인 목적으로 개시된다. 그러나, 이러한 구조들 및 구현들은 필요하지는 않으며, 상이한 구현 상세들을 갖는 다른 구조들로 증대 및/또는 대체될 수 있다.

일반적으로, 프로세서(100)는 STM 및 HTM 시스템들 양자의 이익들을 이용하려고 시도하는 UTM 시스템 내에서 트랜잭션들을 실행하는 것이 가능할 수 있다. 예를 들어, HTM은 트랜잭션들에 대한 액세스 추적, 충돌 검출, 검증 및 커미트 모두를 수행하기 위해 소프트웨어에 의존하지 않으므로, 종종 작은 트랜잭션들의 실행을 위해 빠르고 효율적이다. 그러나, HTM들은 일반적으로 더 작은 트랜잭션들만을 처리할 수 있는 반면, STM들은 무제한 크기의 트랜잭션들을 처리할 수 있다. 따라서, 일 실시예에서, UTM 시스템은 하드웨어를 이용하여 더 작은 트랜잭션들을 실행하고, 소프트웨어를 이용하여 하드웨어에 대해서는 너무 큰 트랜잭션들을 실행한다. 아래의 설명으로부터 알 수 있듯이, 소프트웨어가 트랜잭션들을 처리하고 있을 때에도, 하드웨어를 이용하여 소프트웨어를 보조하고 가속화할 수 있다. 동일 하드웨어를 이용하여, 순수 STM 시스템을 지원하고 가속화할 수도 있다.

전술한 바와 같이, 트랜잭션들은 프로세서(100) 내의 국지 처리 요소들에 의해서는 물론, 잠재적으로는 다른 처리 요소들에 의해 데이터 아이템들에 대한 트랜잭션 메모리 액세스들을 포함한다. 트랜잭션 메모리 시스템 내에 안전 메커니즘이 없는 경우, 이러한 액세스들 중 일부는 잠재적으로는 무효 데이터 및 실행, 즉 판독을 무효화하는 데이터에 대한 기록 또는 무효 데이터의 판독을 유발할 것이다. 결과적으로, 프로세서(100)는 후술하는 바와 같은 판독 모니터들 및 기록 모니터들과 같은 잠재적 충돌들의 식별을 위해 데이터 아이템들로의 그리고 그들로부터의 메모리 액세스들을 추적 또는 모니터링하기 위한 논리를 포함할 수 있다.

일 실시예에서, 프로세서(100)는 데이터 아이템들과 관련된 액세스들 및 잠재적인 후속 충돌들을 검출 또는 추적하기 위한 모니터들을 포함한다. 일례로서, 프로세서(100)의 하드웨어는 적절히 모니터링되도록 결정되는 로드들 및 저장들을 추적하기 위한 판독 모니터들 및 기록 모니터들을 포함한다. 일례로서, 하드웨어 판독 모니터들 및 기록 모니터들은 기반 저장 구조들의 입도에도 불구하고 데이터 아이템들의 입도에서 데이터 아이템들을 모니터링한다. 일 실시예에서, 데이터 아이템은 적어도 전체 데이터 아이템이 적절히 모니터링되는 것을 보증하기 위해 저장 구조들의 입도에서 관련된 추적 메커니즘들에 의해 경계가 정해진다.

특정 설명 예로서, 판독 및 기록 모니터들은 하위 레벨 데이터 캐시(150) 내의 위치들과 같은 캐시 위치들과 관련된 속성들을 포함하여, 그러한 위치들과 관련된 어드레스들로부터의 로드들 및 그들로의 저장들을 모니터링한다. 여기서, 데이터 캐시(150)의 캐시 위치에 대한 판독 속성이 판독 이벤트 시에 캐시 위치와 관련된 어드레스로 설정되어, 동일 어드레스에 대한 잠재적 충돌 기록들이 모니터링된다. 이 경우, 기록 속성들이 기록 이벤트들 동안 유사한 방식으로 동작하여, 동일 어드레스에 대한 잠재적 충돌 판독들 및 기록들이 모니터링된다. 이 예를 더 설명하면, 하드웨어는 캐시 위치들이 적절히 모니터링되고 있음을 지시하도록 설정된 판독 및/또는 기록 속성들과 함께 캐시 위치들에 대한 판독들 및 기록들에 대한 스누프들(snoops)에 기초하여 충돌들을 검출할 수 있다. 역으로, 일 실시예에서 판독 및 기록 모니터들을 설정하거나, 캐시 위치를 버퍼링된 상태로 갱신하는 것은 판독 요청들, 또는 소유권 요청들에 대한 판독과 같은 스누프들을 초래하며, 이는 다른 캐시들에서 모니터링되는 어드레스들과의 충돌들이 검출될 수 있게 한다.

따라서, 설계에 기초하여, 캐시 일관성 요청들 및 모니터링된 캐시 라인들의 일관성 상태들의 상이한 조합들은 캐시 라인이 데이터 아이템을 공유된 판독 모니터링된 상태로 유지하는 것과 스누프가 그 데이터 아이템에 대한 기록 요청을 지시하는 것과 같은 잠재적 충돌들을 유발한다. 역으로, 캐시 라인이 데이터 아이템을 버퍼링된 기록 상태로 유지하는 것과 외부 스누프가 그 데이터 아이템에 대한 판독 요청을 지시하는 것이 잠재적으로 충돌하는 것으로 간주될 수 있다. 일 실시예에서, 액세스 요청들 및 속성 상태들의 그러한 조합들을 검출하기 위해, 스누프 논리가 충돌 검출/보고를 위한 모니터들 및/또는 논리와 같은 충돌 검출/보고 논리는 물론, 충돌들을 보고하기 위한 상태 레지스터들에 결합된다.

그러나, 조건들 및 시나리오들의 어떠한 조합도 커미트 명령어와 같은 명령어에 의해 정의될 수 있는 트랜잭션에 대해 무효인 것으로 간주될 수 있다. 트랜잭션의 논-커미트(non-commit)를 위해 고려될 수 있는 팩터들의 예들은 트랜잭션에서 액세스된 메모리 위치에 대한 충돌의 검출, 모니터 정보의 손실, 버퍼링된 데이터의 손실, 트랜잭션에서 액세스된 데이터 아이템과 관련된 메타데이터의 손실, 및 인터럽트, 링 전이(ring transition) 또는 명시적인 사용자 명령(재개된 트랜잭션이 계속될 수 없음을 가정함)과 같은 다른 무효 이벤트의 검출을 포함한다.

일 실시예에서, 프로세서(100)의 하드웨어는 버퍼링된 방식으로 트랜잭션 갱신들을 유지한다. 전술한 바와 같이, 트랜잭션 기록들은 트랜잭션의 커미트까지 전역적으로 보이지 않게 된다. 그러나, 트랜잭션 기록들과 관련된 국지 소프트웨어 스레드는 후속 트랜잭션 액세스들을 위해 트랜잭션 갱신들에 액세스할 수 있다. 제1 예로서, 버퍼링된 갱신들을 유지하기 위해 프로세서(100) 내에 개별 버퍼 구조가 제공되며, 이는 다른 외부 스레드들이 아니라 국지 스레드에 갱신들을 제공할 수 있다. 그러나, 개별 버퍼 구조의 포함은 잠재적으로 비싸고 복잡하다.

이와 달리, 다른 예로서, 데이터 캐시(150)와 같은 캐시 메모리가 동일한 트랜잭션 기능을 제공하면서 갱신들을 버퍼링하는 데 사용된다. 여기서, 캐시(150)는 데이터 아이템들을 버퍼링된 일관성 상태로 유지할 수 있으며, 한 예에서는 새로운 버퍼링된 일관성 상태를 MESI(Modified Exclusive Shared Invalid) 프로토콜과 같은 캐시 일관성 프로토콜에 추가하여 MESIB 프로토콜을 형성한다. 버퍼링된 데이터 아이템, 즉 버퍼링된 일관성 상태로 유지되는 데이터 아이템에 대한 국지 요청들에 응답하여, 캐시(150)는 데이터 아이템을 국지 처리 요소에 제공하여 내부 트랜잭션 순차 배열을 보증한다. 그러나, 외부 액세스 요청들에 대해서는 미스 응답(miss response)을 제공하여, 트랜잭션에서 갱신된 데이터 아이템이 커미트까지 전역적으로 보이지 않게 되는 것을 보증한다. 더구나, 캐시(150)의 라인이 버퍼링된 일관성 상태로 유지되고, 퇴출을 위해 선택될 때, 버퍼링된 갱신은 상위 레벨 캐시 메모리들에 기록되지 않고, 버퍼링된 갱신은 메모리 시스템을 통해 확산되지 않는데, 즉 커미트 후까지 전역적으로 보이지 않게 된다. 커미트 시에, 버퍼링된 라인들은 변경된 상태로 전이되어, 데이터 아이템은 전역적으로 보이게 된다.

내부 및 외부라는 용어는 종종 트랜잭션의 실행과 관련된 스레드 또는 캐시를 공유하는 처리 요소들의 관점에 대한 것이라는 점에 유의한다. 예를 들어, 트랜잭션의 실행과 관련된 소프트웨어 스레드를 실행하기 위한 제1 처리 요소가 국지 스레드로서 참조된다. 따라서, 위의 설명에서, 제1 스레드에 의해 이전에 기록된 어드레스로의 저장 또는 그로부터의 로드 - 이는 그 어드레스에 대한 캐시 라인을 버퍼링된 일관성 상태로 유지함 -가 수신되는 경우, 캐시 라인의 버퍼링된 버전이 제1 스레드에 제공되는데, 그 이유는 이 스레드가 국지 스레드이기 때문이다. 이와 달리, 제2 스레드가 동일 프로세서 내의 다른 처리 요소 상에서 실행되고 있을 수 있지만, 캐시 라인을 버퍼링된 상태로 유지하는 것을 책임지는 트랜잭션의 실행과 관련이 없고 - 외부 스레드 -; 따라서 제2 스레드로부터 그 어드레스로의 로드 또는 저장은 캐시 라인의 버퍼링된 버전을 얻지 못하며, 상위 레벨 메모리로부터 캐시 라인의 버퍼링되지 않은 버전을 검색하기 위해 통상의 캐시 교체가 이용된다.

여기서, 내부/국지 및 외부/원격 스레드들은 동일 프로세서 상에서 실행되고 있으며, 일부 실시예들에서는 캐시에 대한 액세스를 공유하는 프로세서의 동일 코어 내의 개별 처리 요소들 상에서 실행될 수 있다. 그러나, 이러한 용어들의 사용은 그에 한정되지 않는다. 전술한 바와 같이, 국지는 트랜잭션의 실행과 관련된 단일 스레드에 특정된 것이 아니라 다수의 스레드가 캐시에 대한 액세스를 공유하는 것을 지칭할 수 있는 반면, 외부 또는 원격은 스레드들이 캐시에 대한 액세스를 공유하지 않는 것을 지칭할 수 있다.

도 1을 처음 참조하여 전술한 바와 같이, 프로세서(100)의 아키텍처는 설명을 위한 예시일 뿐이다. 예컨대, 다른 실시예들에서는, 복잡한 개명/할당기 및 재배열/회수 유닛들을 포함하지 않을 수 있는 훨씬 더 간단한 순차 실행 프로세서 설계를 갖는 프로세서를 위해 UBT 하드웨어가 구현될 수 있다. 유사하게, 메타데이터를 참조하기 위한 데이터 어드레스들의 변환의 특정 예들도 예시적인데, 그 이유는 동일 메모리의 개별 엔트리들 내에서 데이터와 메타데이터를 연관시키는 임의의 방법이 이용될 수 있기 때문이다.

도 2를 참조하면, 프로세서에서 데이터 아이템에 대한 메타데이터를 유지하는 실시예가 도시되어 있다. 도시된 바와 같이, 데이터 아이템(216)에 대한 메타데이터(217)가 메모리(215) 내에 국지적으로 유지된다. 메타데이터는 데이터 아이템(216)에 관한 트랜잭션 정보와 같은, 데이터 아이템(216)과 관련된 임의의 특성 또는 속성을 포함한다. 메타데이터의 일부 설명 예들이 아래에 포함되지만, 개시되는 메타데이터의 예들은 예시적일 뿐이다. 따라서, 메타데이터 위치(217)는 데이터 아이템(216)에 대한 정보 및 다른 속성들의 임의의 조합을 유지할 수 있다.

제1 예로서, 메타데이터(217)는 데이터 아이템(216)이 트랜잭션 내에서 이전에 액세스, 버퍼링 및/또는 백업된 경우에 트랜잭션에서 기록된 데이터 아이템(216)에 대한 백업 또는 버퍼 위치에 대한 참조를 포함한다. 여기서, 일부 구현들에서, 데이터 아이템(216)의 이전 버전의 백업 사본은 상이한 위치에 유지되며, 결과적으로 메타데이터(217)는 백업 위치에 대한 어드레스 또는 다른 참조를 포함한다. 대안으로서, 메타데이터(217) 자체는 데이터 아이템(216)에 대한 백업 또는 버퍼 위치로서 역할할 수 있다. 다른 예로서, 메타데이터(217)는 데이터 아이템(216)에 대한 반복 트랜잭션 액세스들을 가속화하기 위한 필터 값을 포함한다. 종종, 소프트웨어를 이용한 트랜잭션의 실행 동안, 트랜잭션 메모리 액세스들에서 액세스 배리어들을 수행하여, 일관성 및 데이터 유효성을 보증한다. 예를 들어, 트랜잭션 로드 동작 전에, 판독 배리어를 실행하여, 데이터 아이템(216)이 언록킹되었는지를 테스트하고, 트랜잭션의 현재 판독 세트가 여전히 유효한지를 결정하고, 필터 값을 갱신하고, 나중의 검증을 가능하게 하기 위해 트랜잭션에 대한 판독 세트 내에 버전 값들을 로깅(logging)하는 것과 같은 판독 배리어 동작들을 수행한다. 그러나, 그 위치의 판독이 트랜잭션의 실행 동안 이미 수행된 경우, 동일 판독 배리어 동작들은 잠재적으로 불필요하다.

결과적으로, 하나의 솔루션은 판독 필터를 사용하여, 데이터 아이템(216) 또는 따라서 어드레스가 트랜잭션의 실행 동안 판독되지 않았음을 지시하기 위한 제1 디폴트 값 및 데이터 아이템(216) 또는 따라서 어드레스가 트랜잭션의 계속 동안 이미 액세스되었음을 지시하기 위한 제2의 액세스된 값을 유지하는 것을 포함한다. 본질적으로, 제2의 액세스된 값은 판독 배리어가 가속화되어야 하는지를 지시한다. 이 예에서, 트랜잭션 로드 동작이 수신되고, 메타데이터 위치(217) 내의 판독 필터 값이 데이터 아이템(216)이 이미 판독되었음을 지시하는 경우, 일 실시예에서는 불필요한 중복 판독 배리어 동작들을 수행하지 않음으로써 트랜잭션 실행을 가속화하기 위해 판독 배리어를 무시하고, 실행하지 않는다. 기록 필터 값은 기록 동작들과 관련하여 동일한 방식으로 동작할 수 있다는 점에 유의한다. 그러나, 개별 필터 값들은 예시적일 뿐인데, 그 이유는 일 실시예에서 어드레스가 기록인지 또는 판독인지에 관계없이 이미 액세스되었는지를 지시하기 위해 단일 필터 값이 사용되기 때문이다. 여기서, 로드들 및 저장들 양자에 대해 216에 대한 메타데이터(217)를 검사하는 메타데이터 액세스 동작들은 단일 필터 값을 이용하며, 이는 메타데이터(217)가 개별 판독 필터 값 및 기록 필터 값을 포함하는 위의 예들과 대조적이다. 특정 설명 실시예로서, 판독 배리어가 관련 데이터 아이템과 관련하여 가속화되어야 하는지를 지시하기 위한 판독 필터, 기록 배리어가 관련 데이터 아이템과 관련하여 가속화되어야 하는지를 지시하기 위한 기록 필터, 언두 동작들이 가속화되어야 하는지를 지시하기 위한 언두 필터 및 소프트웨어에 의해 필터 값으로서 임의의 방식으로 사용될 잡동사니 필터에 메타데이터(217)의 4 비트가 할당된다.

메타데이터의 몇 가지 다른 예는 핸들러에 대한 어드레스의 지시, 표현 또는 참조를 포함하며, 이는 데이터 아이템(216)과 관련된 트랜잭션, 데이터 아이템(216)과 관련된 트랜잭션의 취소 불가한/변경하기 어려운 성질, 데이터 아이템(216)의 손실, 데이터 아이템(216)에 대한 모니터링 정보의 손실, 데이터 아이템(216)에 대해 검출되는 충돌, 데이터 아이템(216)과 관련된 판독 세트 또는 판독 세트 내의 판독 엔트리의 어드레스, 데이터 아이템(216)에 대한 이전의 로깅된 버전, 데이터 아이템(216)의 현재 버전, 데이터 아이템(216)에 대한 액세스를 허용하기 위한 록, 데이터 아이템(216)에 대한 버전 값, 데이터 아이템(216)과 관련된 트랜잭션에 대한 트랜잭션 서술자 및 다른 공지된 트랜잭션 관련 설명 정보에 일반적이거나 고유하다. 더구나, 전술한 바와 같이, 메타데이터의 사용은 트랜잭션 정보로 한정되지 않는다. 당연한 결과로서, 메타데이터(217)는 트랜잭션과 관련되지 않은 데이터 아이템(216)과 관련된 정보, 특성들, 속성들 또는 상태들도 포함할 수 있다.

전술한 바와 같이, 실시예들은 명시적인 기록 버퍼링된 명령어를 이용하여 하드웨어 버퍼에 대한 기록을 수행할 수 있다. 일 구현에서는, 기록 배리어를 이용하여, 이러한 명시적인 버퍼링된 저장 명령어를 이용하여 하드웨어 내에 갱신들을 버퍼링할 수 있다. 이제, 도 3a를 참조하면, 본 발명의 일 실시예에 따른 이거 기록 록킹 및 모니터링을 수행하기 위한 방법의 흐름도가 도시되어 있다. 더 구체적으로, 도 3a는 이거 기록 록킹 및 모니터링을 수행하는 트랜잭션을 수행하기 위한 방법을 도시한다. 이러한 이거 동작들은 캐시 상주 TM 트랜잭션과 관련되지만, 본 발명의 범위는 이와 관련하여 한정되지 않는다는 것을 이해한다. 도시된 바와 같이, 방법(300)은 트랜잭션에서 기록될 데이터가 하드웨어 버퍼에 맞는 크기를 갖는지를 결정함으로써(다이아몬드 310) 시작될 수 있다. 일례로서, 이러한 결정은 트랜잭션에서 기록될 메모리 블록의 크기 및 캐시 메모리 내에서의 이용 가능한 저장의 대응하는 양에 기초하여 이루어질 수 있다. 일 실시예에서, 캐시는 공유 캐시를 포함하는 프로세서의 캐시 계층 구조의 임의 레벨일 수 있지만, 다른 구현들은 이러한 분석을 주어진 TM 스레드가 실행되고 있는 코어의 비공개 캐시로 제한할 수 있다. 물론, 다른 실시예들은 개별 하드웨어 구조 내의 하드웨어 기록 버퍼링을 제공할 수 있다. 기록 데이터가 하드웨어 버퍼에 맞는 크기를 갖지 않는 경우, 제어는 블록 315로 전달될 수 있으며, 여기서 무제한 기록 트랜잭션이 수행될 수 있다. 이러한 UTM 트랜잭션은 모니터링 및 버퍼링을 포함하는 하드웨어 특성들로부터 도움을 받을 수 있지만, 도 3a와 관련하여 여기서 설명되는 구현은 캐시 상주 트랜잭션과 관련된다. 다른 실시예들은 기록 버퍼링을 구현하는 데 사용되는 하드웨어 버퍼에 맞는 기록 세트를 갖는 트랜잭션들에 적용될 수 있다.

데이터가 하드웨어 버퍼에 맞는 크기를 갖는 경우, 제어는 다이아몬드 310으로부터 다이아몬드 320으로 전달되며, 여기서 기록될 위치를 포함하는 블록이 이미 캐시 내에 버퍼링되었는지를 결정할 수 있다. 따라서, 이러한 결정은 기록 배리어를 수행하는 비용을 없애기 위한 필터링 기능을 수행할 수 있다. 상이한 구현들에서, 필터링을 수행하는 다양한 방법들이 실현될 수 있다. 많은 실시예에서, 하나 이상의 하드웨어 특성들을 이용하여 필터링을 수행할 수 있다. 본 명세서에서 설명되는 구현들에서, 버퍼링된 특성이 이용될 수 있다. 일 실시예에서, 사용자 레벨 테스트 명령어를 이용하여, 대응하는 기록 데이터의 어드레스가 캐시 내에 버퍼링되었는지를 결정할 수 있다. 이러한 결정은 데이터의 어드레스를 포함하는 블록과 관련된 버퍼링된 지시자에 기초하여 이루어질 수 있다. 따라서, 다이아몬드 320에서의 결정은 블록이 이미 캐시 내에 존재하는 경우에 기록 배리어를 방지 또는 필터링할 수 있다. 다른 실시예들에서는, 기록 모니터링을 이용하여, 이거 기록 모니터링 구현에서 필터링을 수행할 수 있다.

이와 달리, 기록될 블록이 아직 버퍼링되지 않은 경우, 제어는 블록 330으로 전달될 수 있으며, 여기서 기록 배리어 동작이 수행될 수 있다. 더 구체적으로, 이러한 기록 배리어 동작은 블록의 소유권을 얻기 위해 기록 록 및 기록 모니터 양자를 획득하는 이거 기록 배리어일 수 있다. 기록 록들 및 기록 모니터들의 상이한 구현들이 실현될 수 있다. 그러나, 일반성의 목적을 위해, 기록 록은 소프트웨어 기록 록, 예를 들어 메모리 내에 존재하고 기록될 특정 위치와 관련되는 기록 록일 수 있다는 것을 이해한다. 이와 달리, 기록 모니터는 일 실시예에서 캐시 라인 크기일 수 있는 모니터링된 블록 크기의 입도를 가질 수 있는 하드웨어 모니터일 수 있다. 기록 모니터링 특성의 일례로서, 캐시 라인의 상태 정보는 주어진 스레드가 캐시 라인에 대한 기록 모니터를 획득했음을 지시하도록 설정될 수 있는 기록 모니터 지시자(예로서, 모니터 비트)를 포함할 수 있다. 일부 실시예들에서, 상이한 스레드에 각각 대응하는 다수의 그러한 모니터가 주어진 캐시 라인과 관련될 수 있다. 따라서, 이 시점에서 기록 배리어가 완료되고, 제어는 블록 340으로 전달된다. 블록 340에서, 버퍼링된 블록은 기록될 데이터로 갱신될 수 있다. 이러한 갱신은 버퍼 내의 블록에 대해 기록 모니터 및 록이 획득되었으므로 그 블록에 대해 직접 이루어질 수 있다. 도 3a에는 도시되지 않았지만, 이 시점에서 트랜잭션의 과정에서의 추가적인 동작들이 이루어질 수 있다는 것을 이해한다.

이제, 도 3b를 참조하면, 이거 기록 모니터링 및 록킹 트랜잭션에서 트랜잭션 커미트를 수행하기 위한 방법의 흐름도가 도시되어 있다. 도 3b에 도시된 바와 같이, 커미트 시에, 제어가 다이아몬드 360으로 전달되고, 여기서 임의의 버퍼링된 또는 모니터링된 데이터가 버퍼로부터 퇴출되었는지를 결정할 수 있다. 이러한 결정은 트랜잭션에 기초할 수 있으며, 갱신된 블록으로 한정되지 않는다는 점에 유의한다. 라인이 퇴출되었는지에 대한 결정은 상이한 형태들을 취할 수 있다. 그러나, 하드웨어 보조 시스템에서는, 예를 들어 트랜잭션 상태 레지스터 내에 존재하는 정보를 검사하여, 예를 들어 TSR의 하나 이상의 손실 이벤트 지시자들의 분석에 의해 모니터링 또는 버퍼링의 손실이 발생하였는지를 결정할 수 있다. 그러한 손실이 발생한 경우, 트랜잭션이 중단될 수 있다(블록 370). 이어서, 제어가 예를 들어 (런타임 시스템의 이젝션 핸들러와 같은) TM 런타임 시스템으로 전달되어, 트랜잭션이 재실행되어야 하는지의 여부를 그리고 재실행되어야 하는 경우에는 재실행이 발생해야 하는 트랜잭션 실행 모드를 결정할 수 있다.

이와 달리, 버퍼링된 또는 모니터링된 데이터가 퇴출되지 않은 것으로 결정되는 경우, 제어는 대신에 다이아몬드 360으로부터 블록 380으로 전달되며, 여기서 버퍼링된 기록 데이터가 보이는 것이 가능해질 수 있다(블록 380). 즉, 트랜잭션이 커미트될 수 있고, 버퍼링된 데이터가 전역적으로 관찰되는 것으로 지시될 수 있다. 예를 들어, 버퍼링된 데이터의 캐시 일관성 상태에 관한 정보를 갱신하여, 트랜잭션을 실행하는 스레드에 의한 비밀 또는 비공개 사용으로부터 다른 에이전트들에 의해 액세스될 수 있는 공유 상태로의 그의 전이를 지시할 수 있다. 도 3b의 실시예에는 이러한 특정 구현이 도시되지만, 본 발명의 범위는 이와 관련하여 한정되지 않는다는 것을 이해한다.

아래의 테이블 1은 명시적인 버퍼링된 저장 명령어(movxb)을 이용하여 하드웨어 내에 갱신들을 버퍼링하는 일 실시예에 따른 기록 배리어(tmWrUTM)에 대한 의사 코드를 나타낸다. 이 버퍼링된 저장 명령어는 데이터를 캐시 메모리 내에 명시적으로 저장하는 전통적인 저장 명령어와 다르며, 메모리로의 데이터의 후속 기록을 제공하지 않는다. 대신에, 트랜잭션의 커미트 프로세스 동안 실행되는 명령어들이 그러한 기록을 수행할 것이다. 기록 배리어는 기록된 위치를 포함하는 버퍼링된 블록(BBLK)이 이미 버퍼링되었는지를 먼저 검사함으로써 중복 기록 배리어 동작들을 필터링하기 위해 버퍼링된 특성을 이용한다. 블록이 버퍼링되지 않은 경우, 배리어는 다른 STM 트랜잭션들과의 충돌을 피하기 위해 그 위치에 대한 STM 기록 록을 획득하고, (트랜잭션이 버퍼링된 갱신을 나중에 커미트할 수 있게 하는) 블록의 소유권을 획득하도록 기록 모니터를 설정한다. 배리어는 BBLK를 처음으로 기록하려고 하자마자(즉, 만남시에) STM 기록 록 및 기록 모니터 양자를 획득한다. 이러한 만남 시간 스킴은 이거 록킹 및 이거 기록 모니터링으로 지칭될 수 있다.

버퍼링된 또는 기록 모니터링된 캐시 라인의 손실은 트랜잭션이 그의 갱신들을 잃게 하며, 따라서 트랜잭션이 중단되게 한다는 점에 유의한다. 일 실시예에서, 트랜잭션의 커미트는 사용자 레벨 트랜잭션 커미트 명령어(TXCOMWM)에 응답하여, 기록 모니터링된 라인들이 손실되지 않는 경우에 버퍼링된 갱신들이 보이게 할 수 있다.

버퍼링된 캐시 라인의 손실은 판독들이 일관성 없는 데이터에 액세스하게 할 수 있다. (테이블 1에도 설명되는) 판독 배리어(tmRdUTM)는 그가 이전에 버퍼링된 후에 손실된 버퍼링된 블록으로부터 판독하지 않는 것을 보증할 수 있다. 즉, 판독 배리어는 버퍼링된 블록이 판독 전에 손실된 버퍼링된 기록후 판독(read-after-buffered-write)을 캐치하도록 동작할 수 있다. 이러한 데이터 비일관성은 버퍼링된 블록이 손실될 때 그리고 판독이 손실된 BBLK에 액세스하기 전에 이젝션 핸들러(이젝터로도 지칭됨)와 같은 이벤트 핸들러로 점프함으로써 방지될 수 있다. 그러나, 이젝터가 없는 경우, 판독 배리어는 트랜잭션이 이미 기록 록을 유지하고 있는 버퍼링되지 않은 위치로부터의 모든 판독시에 명시적으로 상태 레지스터(예로서, TSR의 TSR.LOSS_BF 비트)의 검사를 수행할 수 있다(기록 배리어는 록들을 열심히 획득하므로, 트랜잭션이 이미 기록 록들을 유지하고 있는 BBLK들만이 이전에 버퍼링되었을 수 있다). 일 실시예에서, 트랜잭션 개시 시에 컴파일러 또는 런타임 시스템에 의해 설정될 수 있는 CACHE_RESIDENT_WRITES 플래그는 이러한 검사가 수행되었는지를 제어한다. 다른 구현들에서, 버퍼링의 손실(예를 들어, JLOSS)을 빠르게 검사하는 명령어도 이러한 검사에 사용될 수 있다. 테이블 1의 변수들, 즉 CACHE_RESIDENT_WRITES, CACHE_RESIDENT_READS, UTM_UNDO_FILTERING, EJECTOR_ENABLED는 트랜잭션의 소정 정책들을 제어하는 플래그들로서 역할한다. CACHE_RESIDENT_WRITES가 참인 경우, 트랜잭션의 기록 세트는 버퍼링된 기록들이 사용되고 있으므로 캐시에 적합해야 한다. CACHE_RESIDENT_READS가 참인 경우, 트랜잭션의 판독 세트도 캐시에 적합해야 한다. UTM_UNDO_FILTERING이 참인 경우, 버퍼링된 기록들이 수행되지 않으며(기록들이 제한되지 않으며), 이 플래그는 하드웨어 메타데이터를 이용하여 언두 로그가 필터링되는지를 제어한다. 마지막으로, EJECTOR_ENABLED는 이젝터들이 사용되는지를 제어하며, 이것이 거짓인 경우, JLOSS 명령어(또는 테이블 1의 checkTsrLoss(LOSS_BUF))가 사용될 수 있다. 아래의 테이블 1은 판독 배리어의 실행에 더하여, 본 발명의 일 실시예에 따른 하드웨어 기록 버퍼링, 이거 록킹 및 모니터링을 이용하는 기록 배리어에 대한 일 실시예의 의사 코드를 나타낸다.

테이블 1

전술한 판독 및 기록 배리어들은 트랜잭션의 실행 동안 수행될 수 있다는 점에 유의한다. 일반적으로, 트랜잭션과 관련된 다양한 상황을 초기화하고, 트랜잭션 내의 다양한 동작들을 실행한 후에 커미트 포인트에 도달하고, 트랜잭션의 실행 동안에 실패가 발생하지 않은 경우에 트랜잭션을 커미트함으로써 트랜잭션이 이루어질 수 있다. 커미트 포인트에서, 트랜잭션이 성공적으로 커미트되고, 그의 갱신들이 시스템의 나머지에게 전역적으로 보이게 될 수 있는지 또는 트랜잭션이 충돌, 하드웨어 특성의 손실 등과 같은 다양한 이유들 중 하나로 인해 중단되어야 하는지를 결정할 수 있다.

일반적으로, 초기화는 트랜잭션의 다양한 상황에 대한 초기 상태를 설정하는 것을 포함할 수 있다. 이러한 상황은 다양한 지시자들이 다양한 이벤트들의 발생시에 이젝터와 같은 이벤트 핸들러로의 점핑을 가능하게 하도록 설정될 수 있는 TCR에 대한 초기 상태를 설정하는 것을 포함할 수 있다. 게다가, TSR은 예를 들어 초기 상태로 설정될 수 있으며, 이 상태에서 다양한 지시자들은 임의의 그러한 이벤트들의 존재의 결여를 지시하기 위해 리셋 상태로 설정될 수 있다. 이어서, 트랜잭션이 시작될 수 있고, 이 트랜잭션과 관련된 동작들에 대한 타임스탬프가 전역 타임스탬프의 값으로 설정될 수 있다. 트랜잭션의 실행 동안 이젝션이 발생하지 않는 경우, 트랜잭션은 커미트 포인트에 도달한다. 캐시 상주 트랜잭션의 경우, 트랜잭션은 커미트될 수 있으며, 사용자 레벨 트랜잭션 커미트 명령이 성공적인 경우에 캐시 내의 버퍼로부터의 갱신된 데이터를 메모리에 기록할 수 있다. 그렇지 않은 경우, 트랜잭션은 중단된다. 트랜잭션의 중단은 이젝션 핸들러의 실행을 유발할 수 있으며, 이젝션 핸들러의 다수의 코드 경로 중 하나가 트랜잭션 실패의 이유에 기초하여 동작할 수 있다. 이젝션 핸들러는 새로운 트랜잭션 모드를 선택하고, 오리지널 실행 모드와 동일하거나 상이할 수 있는 선택된 트랜잭션 실행 모드를 위한 사용자 코드로 제어를 전달할 수 있다. 이와 달리 트랜잭션이 캐시 상주 트랜잭션이 아닌 경우, 판독 세트가 검증될 수 있고, 트랜잭션은 검증 실패의 경우에 롤백 및 중단될 수 있으며, 획득된 임의의 록들이 해제될 수 있다. 이러한 롤백의 일부로서, 다양한 버퍼링된 라인들 및 모니터링이 소거될 수 있다. 이와 달리 검증이 성공적인 경우, 트랜잭션은 커미트될 수 있고, 전역 타임스탬프가 증가될 수 있다. 실시예들은 캐시 상주 트랜잭션들로 한정되지 않으며, 판독 세트가 제한되지 않지만(예를 들어, 판독 세트들이 캐시 크기에 의해 제한되지 않음), 기록 세트는 제한되는(예를 들어, 테이블 1에서 CACHE_RESIDENT_WRITES가 참이지만, CACHE_RESIDENT_READS가 거짓인 경우에 대응함) 트랜잭션들이 발생할 수 있다는 점에 유의한다.

아래의 테이블 2는 본 발명의 일 실시예에 따른 트랜잭션 개시 및 커미트에서 수행되는 동작들을 위한 예시적인 코드를 나타낸다.

테이블 2

다른 실시예에서, 기록 모니터를 설정하고 STM 기록 록을 획득하는 것은 커미터 시까지 지연될 수 있다. 이러한 커미트 시간 스킴은 레이지 록킹 및 레이지 기록 모니터링으로서 지칭될 수 있다. 전술한 이거 록킹 및 모니터링 스킴과 같이, 이 스킴은 먼저 버퍼링된 특성을 이용하여 중복 기록 배리어 동작들을 필터링한다. 이거 스킴과 달리, 값이 갱신될 때 기록 모니터를 설정하고 기록 록을 획득하는 대신, 기록될 위치의 어드레스가 기록 로그에 추가될 수 있으며, 따라서 커미트 시에 기록 모니터가 설정되고 기록 록이 획득될 수 있다. 갱신된 값은 버퍼링된 기록(예로서, movxb) 명령을 이용하여 기록될 위치의 어드레스에 저장될 수 있다는 점에 유의한다. 일 실시예에서, 예를 들어 컴파일러 또는 런타임 시스템에 의해 설정되는 LAZY_LOCKING 플래그가 이러한 모드를 가능하게 할 수 있다.

커미트 시에, 트랜잭션은 그의 기록 로그 내의 위치들을 통해 반복되어, 각각의 위치에 대해 기록 모니터를 설정하고 기록 록을 획득한다. 각각의 위치 상에 기록 모니터를 설정한 후, 트랜잭션은 (예를 들어, 상태 레지스터의 TSR.LOSS_BF 비트를 통해) 버퍼링된 라인의 손실을 검사할 수 있으며, 임의의 버퍼링된 라인이 손실된 경우에는 중단될 수 있다. 그렇지 않은 경우, 트랜잭션은 예를 들어 TXCOMWM 명령을 이용하여 커미트되어, 기록 모니터링 라인들이 손실되지 않은 경우에는 버퍼링된 갱신들이 보이게 할 수 있다.

버퍼링된 기록후 판독으로부터 손실된 BBLK로의 판독 세트 비일관성을 방지하기 위하여, 트랜잭션은 버퍼링된 라인의 손실, 예를 들어 소위 LOSS_BF 이벤트 시에 이젝트하는 이젝터를 사용할 수 있거나, (예를 들어, 상태 레지스터의 TSR.LOSS_BF 비트를 통해) 버퍼링된 라인의 손실에 대한 검사가 (트랜잭션이 이전에 기록 록킹한 버퍼링되지 않은 BBLK로부터 판독할 때만 이 비트를 명시적으로 검사하는 이거 록킹 스킴과 달리) 버퍼링되지 않은 BBLK로부터의 모든 판독시에 명시적으로 수행될 수 있다.

본 발명의 일 실시예에 따른 레이지 록킹을 구현함으로써, 다른 동시 트랜잭션들은 이들이 기록 트랜잭션의 커미트 전에 커미트되는 한은 충돌 없이 동일 트랜잭션 록에 맵핑되는 메모리 위치들을 판독할 수 있다. 이러한 방식으로, 트랜잭션의 중단 없이 다른 트랜잭션들이 갱신된 데이터를 동시에 판독할 수 있게 함으로써 동시성이 개선될 수 있다. 이러한 스킴은 2개의 트랜잭션이 동일 트랜잭션 록에 맵핑되는 상이한 위치들을 갱신하는 것으로 인한 거짓 충돌들도 줄일 수 있다.

이제, 도 4a를 참조하면, 본 발명의 일 실시예에 따른 레이지 기록 록킹 및 모니터링을 수행하기 위한 방법의 흐름도가 도시되어 있다. 도 3a의 방법(300)과 관련된 위의 설명과 유사하게, 도 4a의 방법(400)은 캐시 상주 트랜잭션과 관련하여 설명되지만, 실시예들은 그에 한정되지 않으며, 임의의 하드웨어 버퍼에 적용될 수 있다. 일반적으로, 도 4a의 흐름도는 도 3a에 관하여 전술한 것과 유사하게 진행될 수 있지만, 레이지 구현에서는 커미트까지 기록 배리어가 발생하지 않는다는 점에 유의한다. 구체적으로, 도 4a에 도시된 바와 같이, 방법(400)은 기록 데이터가 주어진 하드웨어 버퍼에 적합한 크기를 갖는지를 결정함으로써(다이아몬드 410) 시작될 수 있다. 이러한 기록이 버퍼의 오버플로우를 유발하는 경우, 제어는 무제한 기록 트랜잭션을 수행하기 위한 블록 415로 전달된다.

기록이 캐시에 맞은 크기를 갖는 경우, 제어는 다이아몬드 420으로 전달되며, 여기서 기록될 블록이 이전에 버퍼링되었는지에 기초하여 필터링 동작이 수행될 수 있다. 블록이 실제로 버퍼링된 경우, 제어는 블록 435로 전달되고, 여기서 데이터가 버퍼의 위치에 직접 기록될 수 있다. 따라서, 레이지 구현에서는, 만남 시에 록 또는 모니터링을 획득할 필요가 없다. 대신에, 단지 데이터가 갱신된다. 기록 모니터가 라인 상에 설정될 때, 하드웨어는 라인의 독점적 소유권을 획득하여, 다른 코어들 내의 다른 사본들을 무효화한다. 이어서, 이러한 레이지 예에 대해 커미트 시에 기록 모니터의 설정이 이루어진다.

이와 달리 버퍼 내의 데이터가 존재하지 않는 경우, 제어는 다이아몬드 420으로부터 블록 430으로 전달되고, 여기서 기록될 데이터의 어드레스가 기록 로그에 기록될 수 있다. 이어서, 예를 들어 movxb 명령을 이용하여 버퍼 메모리에서 데이터 자체가 갱신될 수 있다(블록 435). 따라서, 그러한 실시예에서, 갱신은 오리지널 기록 어드레스에 대한 버퍼링된 저장/기록을 수행하여, 하드웨어로 하여금 기록 모니터가 그 어드레스에 대해 설정되는 경우에 커미트 시에 전역적으로 보이게 되는 그 어드레스의 비공개 버퍼링된 사본을 생성하게 한다. 이어서, 트랜잭션의 추가적인 동작들이 수행될 수 있다.

이제, 도 4b를 참조하면, 본 발명의 일 실시예에 따른 레이지 기록 모니터링 및 록킹 트랜잭션에 대한 커미트 방법의 흐름도가 도시되어 있다. 도 4b에 도시된 바와 같이, 방법(440)은 블록 450으로 진행하여, 기록 록 및 모니터를 획득할 수 있다. 그러한 동작들은 기록 배리어 동작에 대해 도 3a를 참조하여 설명된 바와 같이 진행될 수 있다. 기록 록 및 모니터가 획득되면, 제어는 다이아몬드 460으로 전달되어, 임의의 버퍼링된 또는 모니터링된 데이터가 손실되었는지를 결정한다. 제어는 블록들 중 하나(470 또는 480)로 각각 전달되어, (손실이 발생한 경우에) 트랜잭션을 중단하거나, 트랜잭션을 커미트하고, 갱신된 데이터의 전역적 관찰을 가능하게 한다. 도 4b의 실시예에는 이러한 특정 구현이 도시되지만, 본 발명의 범위는 이와 관련하여 한정되지 않는다.

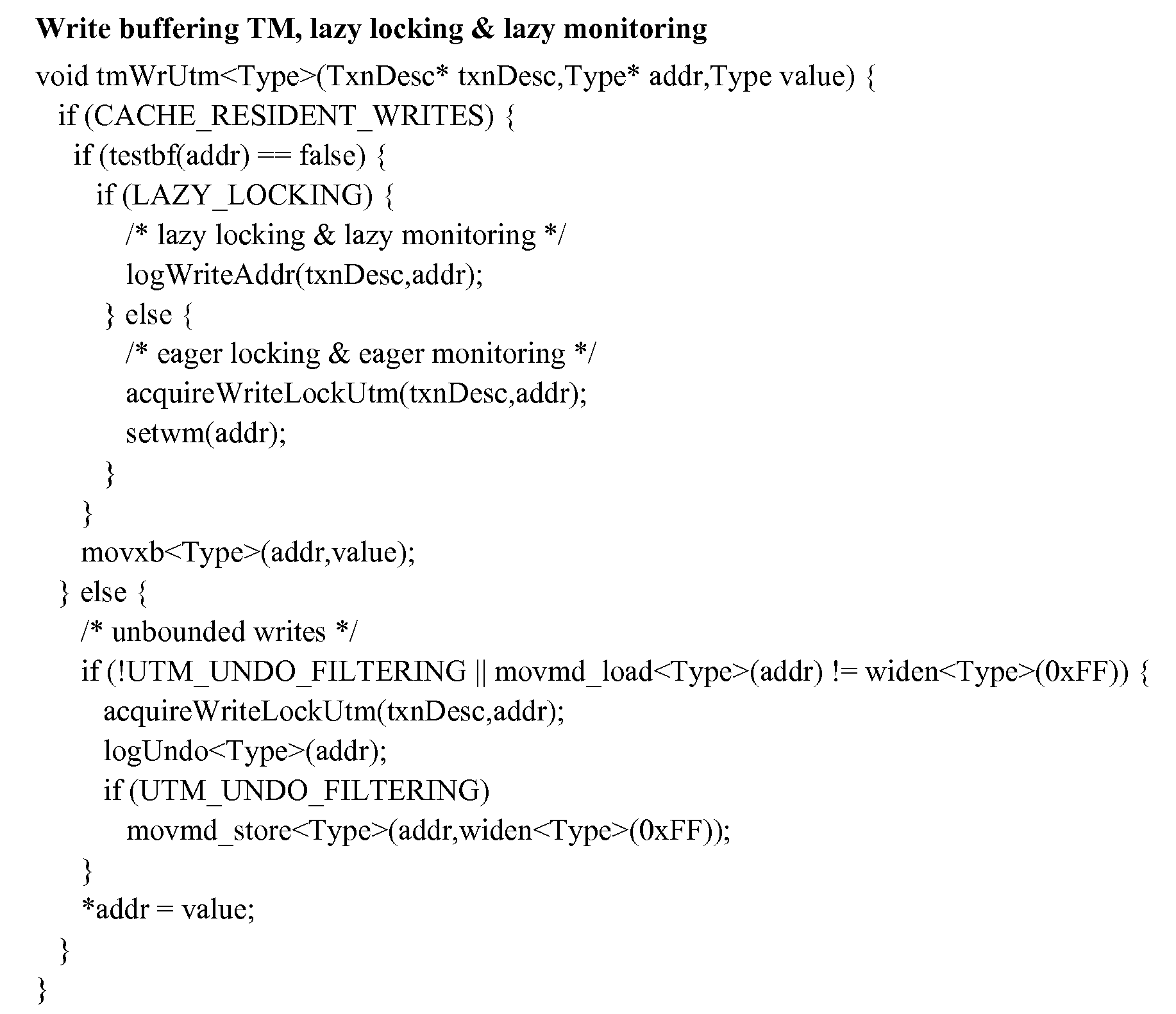

아래의 테이블 3은 본 발명의 일 실시예에 따른 하드웨어 기록 버퍼링, 레이지 록킹 및 레이지 모니터링을 이용하는 기록 배리어에 대한 일 실시예의 의사 코드를 나타낸다. 일반적으로, 테이블 3은 테이블 1에 레이지 록킹을 추가함으로써 테이블 1 내의 코드를 정밀화한다. 플래그 LAZY_LOCKING은 트랜잭션이 (테이블 1에서와 같은 이거 동작들과 대비하여) 레이지 록킹 및 기록 모니터링을 이용하고 있는지를 제어한다.

테이블 3

아래의 테이블 4는 본 발명의 일 실시예에 따른 하드웨어 기록 버퍼링, 레이지 록킹 및 레이지 모니터링을 이용하는 판독 배리어에 대한 일 실시예의 의사 코드를 나타낸다.

테이블 4

전술한 기록 및 판독 버퍼링은 트랜잭션의 실행 동안 수행될 수 있다는 점에 유의한다. 아래의 테이블 5는 레이지 록킹 및 레이지 모니터링을 구현하는 본 발명의 일 실시예에 따른 트랜잭션 커미트 시에 수행되는 동작들에 대한 예시적인 코드를 나타낸다.

테이블 5

레이지 록킹 및 기록 모니터링 스킴은 충돌 동안 기록-기록 충돌들을 늦게 검출한다는 점에 유의한다. 즉, 2개의 트랜잭션은 그들 중 하나가 커미트 단계에 도달할 때까지 그들이 동일 블록에 기입함으로써 충돌하였다는 것을 발견하지 못한다. 따라서, 레이지 충돌 검출은 기록-기록 충돌의 존재시에 일의 낭비를 유발할 수 있다. 다른 실시예에서, 이러한 단점은 기록 모니터링을 열심히 설정하면서 록들을 느리게 획득함으로써 완화될 수 있다(이는 동일 트랜잭션 록에 맵핑된 데이터를 갖는 기록기 또는 판독기 전에 동일 데이터를 판독하는 판독기들을 중단시키지 않는다). 이러한 기술은 이거 기록 모니터링을 이용하는 레이지 록킹으로 지칭될 수 있다. 이러한 기술에서, 기록 배리어는 커미트 시에 기록 록들을 느리게 획득하지만, 만남 시에 기록된 데이터에 대한 기록 모니터를 열심히 설정한다. 일반적으로, 도 3a-4b와 관련하여 전술한 방법들은 이러한 구현을 실현하도록 조합될 수 있다. 즉, 이거 모니터링을 달성하기 위해 갱신이 기록 로그에 기록되는 것과 동시에 기록 모니터가 설정될 수 있다. 그러나, 레이지 록킹은 도 4b에서와 같이 커미트 시에 발생한다.

아래의 테이블 6은 본 발명의 일 실시예에 따른 하드웨어 기록 버퍼링, 레이지 록킹 및 이거 모니터링을 이용하는 기록 배리어에 대한 일 실시예의 의사 코드를 나타낸다.

테이블 6

아래의 테이블 7은 레이지 록킹 및 이거 모니터링을 구현하는 본 발명의 일 실시예에 따른 트랜잭션 개시 및 커미트 시에 수행되는 동작들에 대한 예시적인 코드를 나타낸다.

테이블 7

소정 실시예들에서는, 기록 모니터링 상태가 트랜잭션들에 걸쳐 유지되고 재사용될 수 있다. 그러한 실시예들에서, 기록 모니터들은 다음 트랜잭션도 하드웨어 버퍼링을 사용하는 경우에 캐시 라인들에 대해 유지될 수 있다. 이러한 최적화는 필터로서 버퍼링된 특성 대신에 기록 모니터를 사용하도록 변경된 이거 기록 모니터링 및 기록 배리어들을 이용하여 구현될 수 있다. 즉, 기록 모니터가 주어진 위치에 대해 존재하는 경우, 다른 기록 배리어를 수행할 필요가 없다. 즉, 지속된 기록 모니터들 상에서는 록킹이 필요하지 않은데, 그 이유는 이러한 지속에 의해 다른 트랜잭션이 기록 모니터가 여전히 설정된 라인과 충돌(판독 또는 기록)하지 않은 것이 보증되기 때문이다. 도 3a의 흐름도를 다시 참조하면, (다이아몬드 320)에서 블록이 이미 버퍼링되었는지를 결정하는 대신에, 블록이 기록 모니터링되는지를 결정할 수 있다.

전술한 바와 같이, 실시예들은 기록 배리어 동작들을 가속화하기 위해 관리된 환경들에서 발견되는 것들과 같은 객체 기반 TM 시스템과 관련하여 사용될 수 있다. 테이블 8에서, 열 "Source"는 소스를 지시하고, 제2 열은 전통적인 STM에 의해 수행되는 동작들을 나타내며, 제3 열은 UTM 시스템에서 객체 기반 트랜잭션 시에 구현되는 바와 같은 하드웨어 특성들의 사용을 나타낸다. 테이블 8은 이거 데이터 모니터링 및 레이지 로킹 및 이거 록킹 양자에 대한 가속화된 기록 배리어를 나타낸다.

테이블 8

테이블 8에서, txnOpenForWrite 함수들은 기록되는 객체 상의 기록 록을 획득한다. 나타난 바와 같이, 이 함수의 상이한 변형들이 존재할 수 있다. 구체적으로, 2개의 변형이 나타나 있는데, 한 변형(NoLock)은 록을 획득하는 것이 아니라, 단지 객체를 로깅하며, 다른 변형(NoLog)은 객체를 록킹도 로깅도 하지 않지 않고, 버퍼링된 저장을 이용하여 객체의 트랜잭션 버전 번호를 증가시킨다.

또 다른 구현들에서는, 하드웨어 기록 버퍼링 기록 배리어가 (커미트 시에) 기록 록들을 느리게 획득하며, 액세스된 데이터에 대해 느리게 기록 모니터링을 설정한다. 이것은 데이터의 다른 판독기들이 트랜잭션을 중단하지 않고(즉, 기록 모니터링의 손실을 유발하지 않고) 진행될 수 있게 한다. 커미트 시에 기록 모니터들의 설정을 가능하게 하기 위해, 기록된 BBLK들의 로그가 제공될 수 있다. 일 실시예에서는, 함수 txnLogBblk(테이블 9의 의사 코드 내에 표시됨)가 이러한 로깅을 수행할 수 있다. 커미트 시에, 트랜잭션은 이러한 로그를 통해 반복되며, 모든 버퍼링된 라인들에 대해 기록 모니터링을 설정한다. 배리어는 다른 트랜잭션들에 의한 충돌하는 기록들을 캐치하기 위하여 기록된 MBLK 상에 판독 모니터를 설정한다. 트랜잭션이 임의의 판독 모니터링된 또는 기록 모니터링된 MBLK들을 잃은 경우에 커미트는 실패한다. 그렇지 않는 경우, 커미트가 진행될 수 있고, 사용자 레벨 커미트 명령어(예로서, TXCOMWMRM)를 이용하여 그의 버퍼링된 데이터를 커미트할 수 있다. 이러한 배리어는 다수의 프로세서가 (판독 모니터링된 그리고 버퍼링된 R-B 상태를 이용하여) 버퍼링된 상태에서 동시에 동일 라인을 갖고, 커미트 시에 기록-기록 충돌들을 느리게 검출할 수 있게 한다.

테이블 9

전술한 바와 같이, 레이지 버전 관리를 이용하는 STM 시스템들은 트랜잭션 내에서 수행된 모든 갱신들을 버퍼링한다. 레이지 버저닝 STM 시스템들은 메모리 위치 또는 객체 L에 대한 각각의 갱신을 하드웨어 버퍼가 아니라 메모리 내에 있을 수 있는 L의 섀도 사본으로 재지향시킨다. 그러한 STM들은 각각의 메모리 판독 또는 기록 시에 L의 섀도 사본에 액세스하는 것이 필요하여, 특히 낙관적인 기록들을 수행하는 STM 시스템들에서 상당한 오버헤드를 더한다.

실시예들은 하드웨어 메타데이터 편의(facility)를 이용하여, 메모리 위치 또는 객체의 섀도 사본을 찾기 위한 저렴한 방법을 구현할 수 있다. 전술한 바와 같이, 하드웨어 메타데이터는 메타데이터를 어드레스에 연관시키는 빠르지만 손실이 많은 방법을 제공할 수 있다. 본 명세서에서 사용될 때, 메타데이터는 객체 또는 어드레스의 섀도 사본에 대한 포인터를 저장하여, 섀도 사본들에 액세스하는 오버헤드를 줄일 수 있다.

이제, 도 5를 참조하면, 메타데이터를 이용하여 객체의 섀도 사본의 위치를 효율적으로 결정하는 방법의 흐름도가 도시되어 있다. 즉, 실시예들은 메타데이터 특성을 이용하여 섀도 사본에 대한 효율적인 맵핑을 수행할 수 있다. 도 5에 도시된 바와 같이, 방법(500)은 제1 스레드로부터 객체에 대한 액세스 요청(예로서, 판독 또는 기록 요청)을 수신함으로써(블록 510) 시작될 수 있다. 일례로서, 이 스레드는 임의 타입의 TM 스킴에서 트랜잭션을 수행하고 있을 수 있다. 제어가 다이아몬드 520으로 전달되고, 여기서 객체에 대한 객체 헤더의 사전 결정된 부분에 대응하는 메타데이터가 객체의 섀도 사본의 어드레스를 포함하는지를 결정할 수 있다(다이아몬드 520). 일례로서, 이러한 사전 결정된 부분은 객체 헤더의 제1 슬롯과 관련된 메타데이터 부분일 수 있다. 그렇지 않은 경우, 이것은 객체의 섀도 사본이 존재하지 않음을 지시한다. 따라서, 제어는 블록 530으로 전달되고, 여기서 메모리로부터 객체를 얻기 위해 판독 배리어 동작이 수행될 수 있다. 이어서, (기록 트랜잭션의 경우) 객체의 섀도 사본이 저장될 수 있다(블록 540). 본 발명의 범위는 이와 관련하여 제한되는 것이 아니라, 캐시 상주 트랜잭션의 경우에, 섀도 사본은 프로세서의 캐시 메모리의 버퍼에 저장될 수 있다. 이러한 액세스 요청의 저장과 관련하여, 제어는 블록 550으로 전달될 수도 있으며, 여기서 객체 헤더의 이 부분과 관련된 메타데이터가 갱신될 수 있다. 특히, 이 메타데이터는 섀도 사본 어드레스를 저장할 수 있다. 이러한 방식으로, 객체 내의 위치에 대한 미래의 액세스들은 본 발명의 일 실시예에 따른 맵핑 동작을 이용함으로써 섀도 사본에 효율적으로 액세스할 수 있다.

도 5를 계속 참조하면, 이와 달리 다이아몬드 520에서 메타데이터가 어드레스를 포함하는 것으로 결정하는 경우, 어드레스가 메타데이터로부터 획득되고(블록 560), 섀도 사본에 액세스하는 데 사용될 수 있다(블록 570). 액세스가 판독 동작이고, 객체가 이전에 결코 기록되지 않은 경우, 판독 동작은 섀도 객체가 아니라 오리지널 객체로부터 직접 판독할 것이라는 점에 유의한다. 따라서, 액세스 요청에 응답하여, 섀도 사본의 위치는 그가 존재할 때 메타데이터로부터 획득될 수 있다. 예를 들어, 기록 트랜잭션의 경우, 섀도에서 액세스되는 데이터가 동작을 수행하는 데 사용될 수 있다(블록 580). 예를 들어, 데이터는 주어진 트랜잭션의 촉진을 위해 다양한 계산들 또는 동작들을 수행하는 데 사용될 수 있다. 기록 트랜잭션의 종료시에, 섀도 사본이 보이게 될 수 있다. 즉, 커미트 시에, 트랜잭션이 성공적으로 완료되고, 어떠한 버퍼링된 정보의 손실도 없고, 경합이 발생하지 않은 경우(그리고 다른 시맨틱스가 위반되지 않은 경우), 트랜잭션은 커미트될 수 있고, 섀도 사본에 저장된 데이터는 도 3b 및 4b의 커미트 동작들과 관련하여 전술한 바와 같이 다른 스레드들에게 보이게 될 수 있다.

도 5에 도시된 것과 유사한 프로세스가, 예로서, 기록 배리어의 일부로서 기록 요청에 대해 수행될 수 있다는 점에 유의한다. 그러나, 여러 차이가 존재한다는 점에 유의한다. 첫째, 기록 배리어의 경우, 객체 헤더의 다른 사전 결정된 부분(예로서, 제2 슬롯)과 관련된 메타데이터에 대신 액세스하여 어드레스가 존재하는지를 결정할 수 있다. 어드레스가 메타데이터에 존재하지 않고, 객체가 액세스되고 섀도 사본에 저장되는 경우, 객체 헤더의 제1 및 제2 사전 결정된 부분들 양자와 관련된 메타데이터는 섀도 데이터의 어드레스로 갱신될 수 있으며, 따라서 판독 및 기록 배리어들 양자가 이 시점으로부터 필터링될 수 있다. 도 5의 실시예에는 이러한 특정 구현이 도시되지만, 본 발명의 범위는 이와 관련하여 한정되지 않는다.

아래의 테이블 10의 의사 코드는 (예를 들어, 관리되는 코드 시스템에 대해) 판독 세트 일관성을 유지하지 않지만 메타데이터를 사용하는 객체 기반 레이지 버저닝 STM 시스템에 대한 판독 및 기록 배리어들을 나타낸다. 표시된 바와 같이, "Source" 열은 판독 및 기록 동작들을 나타낸다. "Software TM" 열은 각각의 STM 판독 및 기록 배리어 의사 코드를 나타낸다. "txnOpenForWrite" 함수는 객체의 섀도 사본을 생성하여 반환한다. 이 함수는 또한 STM 시스템이 만남 시간 록킹을 수행하는 경우에 객체 상에 독점 록을 획득할 것이며, 그렇지 않은 경우에는 커미트 시까지 록의 획득을 지연시킨다. 함수 "txnOpenForRead"는 트랜잭션이 이전에 객체에 기록된 경우에 객체의 섀도 사본을 반환하며, 그렇지 않은 경우에는 공유 객체를 반환한다. 이 함수는 또한 객체를 판독 세트 내에 로깅하며, 판독들에 대해 낙관적 또는 비관적 동시성 제어를 이용할 수 있다. 의사 코드는 판독들에 대해 낙관적 동시성 제어를 이용하는 STM 시스템에서 판독 세트 일관성을 유지할 수 없는데, 그 이유는 낙관적 시스템에서의 일관성의 유지가 필드를 판독한 후에 객체의 재검증을 필요로 하기 때문이라는 점에 유의한다.

테이블 10의 "Accelerated TM" 열은 STM 동작들을 가속화하기 위해 메타데이터를 사용하는 의사 코드를 나타낸다. 판독 배리어는 먼저 객체 헤더의 사전 결정된 부분(예로서, 제1 슬롯)과 관련된 메타데이터를 검사하고, 이어서 그 메타데이터가 공백 값을 포함하는 경우에 txnOpenForRead 동작을 수행한다. 이어서, 이 함수에 의해 반환된 어드레스를 사전 결정된 부분과 관련된 객체의 메타데이터에 저장하며, 이는 동일 객체에 대한 후속 판독 배리어들이 txnOpenForRead 동작을 건너뛰게 한다(중복 판독 배리어들을 효과적으로 필터링한다). 유사하게, 기록 배리어는 먼저 객체 헤더의 다른 사전 결정된 부분(예로서, 제2 슬롯)과 관련된 메타데이터를 검사하고, 이어서 그 메타데이터가 공백 값을 포함하는 경우에 txnOpenForWrite 동작을 수행한다. 이어서, 이 함수에 의해 반환된 어드레스를 객체 헤더의 양쪽 사전 결정된 부분들(예로서, 처음 2개의 슬롯)과 관련된 메타데이터에 저장하며, 이는 동일 객체에 대한 후속 판독 및 기록 배리어들이 그들 각각의 배리어 동작을 건너뛰게 한다. 이 알고리즘은 최소 객체 크기가 2개의 포인터 값을 저장할 수 있는 것으로 가정한다는 점에 유의한다. 기록 배리어의 다른 구현은 하나의 포인터 값만을 그러나 고속 경로에서의 여분의 비교의 대가로 저장할 수 있는 최소 객체 크기를 지원할 수 있다. 전통적인 STM 판독 및 기록 배리어들에 비해, 가속화된 배리어들은 메타데이터가 "히트"할 때 메타데이터 로드 및 (1 또는 2) 조건 분기 명령어들만의 오버헤드를 유발한다.

테이블 10

테이블 10의 의사 코드는 논-트랜잭션 스레드들이 트랜잭션에 의해 액세스되고 있는 동일 객체를 갱신하는 것이 허가되는 경우에 입자성 손실 갱신들(GLU) 및 입자성 비일관성 판독들(GIR)을 유발할 수 있다는 것에 유의한다. 따라서, STM 시스템은 통상적으로 그러한 문제들을 피하거나 논-트랜잭션 스레드들에 의한 트랜잭션 객체들에 대한 갱신들을 방지하기 위해 논-트랜잭션 코드 내의 강력한 원자성 배리어들을 이용한다(분리). 본 발명의 다른 실시예는 GLU 또는 GIR 문제들을 피하기 위해 강력한 원자성 또는 분리를 필요로 하지 않는 레이지 버저닝 STM들에서 객체들의 섀도 사본 탐색을 가속화할 수 있다.

테이블 11은 (예를 들어, C/C++ STM 시스템에 대해) 판독 세트 일관성을 유지하는 하드웨어 메타데이터를 이용하는 어드레스 기반 레이지 버저닝 STM 시스템에 대한 판독 및 기록 배리어들에 대한 의사 코드를 나타낸다. 이 알고리즘은 GLU 및 GIR 문제들을 피하기 때문에 그리고 원시 코드 내의 액세스들이 블록들에 걸칠 수 있기 때문에 이전의 객체 기반 알고리즘보다 복잡하다. 원시 코드에는, 객체들 대신에 메모리의 블록들이 존재하며, 따라서 시스템은 객체들이 아니라 블록들의 섀도 사본들을 생성한다. 이어서, 메모리 판독 또는 기록이 2개의 상이한 블록에 걸치는 메모리 값에 액세스할 수 있으며, 따라서 액세스는 2개의 상이한 섀도 사본의 발견을 수반할 것이다. 테이블 11의 코드는 이 사례를 검출하고, 단순히 기반 STM txnOpenAddrForRead 및 txnOpenAddrForWrite 함수들을 호출한다.

테이블 11

따라서, 다양한 실시예들에서는, 상이한 기술들을 이용하여, UTM 시스템의 하드웨어 특성들을 이용함으로써 더 효율적인 트랜잭션들을 실현할 수 있다. 이러한 기술들은 커미트 시간(레이지) 록킹을 이용하는 커미트 시간(레이지) 기록 모니터링 또는 커미트 시간(레이지) 또는 만남 시간(이거) 록킹을 이용하는 만남 시간(이거) 기록 모니터링을 포함할 수 있다. 더구나, 실시예들은 이젝터를 이용하고 그리고/또는 버퍼링된 또는 모니터링된 라인들의 손실을 추적하는 트랜잭션 상태 레지스터의 명시적인 검사들을 이용함으로써(또는 명시적인 명령어를 이용함으로써) 일관성의 유지를 가능하게 할 수 있다. 게다가, 캐시 상주 및 무제한 판독들 양자와 함께 캐시 상주 기록들이 수행될 수 있으며, 판독들에 대한 낙관적(타임스탬프 기반) 및 비관적(판독기-기록기 록 기반) 동시성 제어 모두가 구현될 수 있다.

기록 로깅이 있거나 없이 기록 록킹의 필터링을 가능하게 하기 위해, 트랜잭션들에 걸쳐 기록 모니터들이 유지될 수 있다. 캐시 상주 기록들은 무제한 트랜잭션들에 대한 즉시(in-place) 갱신 및 기록 버퍼링 STM 양자와 더불어 발생할 수 있다. 게다가, 버퍼링된 갱신들 및 필터 검사들이 하드웨어에 의해 암시적으로 수행되는 암시 모드 핸들러 기반 시스템과 관련하여, 필터의 결여는 기록 배리어를 수행하는 핸들러를 호출한다. 따라서, 실시예들은 (캐시와 같은) 하드웨어 버퍼들에 적합한 기록 세트를 갖는 트랜잭션들에 대해 하드웨어에서 버전 관리를 수행함으로써 전통적인 STM 시스템들의 오버헤드를 줄일 수 있다.

실시예들은 객체 또는 데이터 아이템의 섀도 사본을 탐색하기 위해 레이지 버저닝 STM 시스템들에서 발생하는 소프트웨어 오버헤드들을 줄일 수도 있다. 그러한 오버헤드는 하드웨어 지원, 예를 들어 객체 또는 위치의 섀도 사본의 위치를 탐색하기 위한 하드웨어 메타데이터를 이용하여 감소될 수 있다.

실시예들은 많은 상이한 시스템 타입에서 구현될 수 있다. 이제, 도 6을 참조하면, 본 발명의 일 실시예에 따른 시스템의 블록도가 도시되어 있다. 도 6에 도시된 바와 같이, 멀티프로세서 시스템(1000)은 점대점 상호접속 시스템이며, 점대점 상호접속(1050)을 통해 결합된 제1 프로세서(1070)와 제2 프로세서(1080)를 포함한다. 도 6에 도시된 바와 같이, 프로세서들(1070, 1080) 각각은 제1 및 제2 프로세서 코어들(즉, 프로세서 코어들(1074a, 1074b) 및 프로세서 코어들(1084a, 1084b))을 포함하는 멀티코어 프로세서들일 수 있지만, 잠재적으로는 더 많은 코어가 프로세서들 내에 존재할 수 있다. 프로세서 코어들은 효율적인 무제한 트랜잭션들을 가능하게 하기 위해 하드웨어, 소프트웨어 또는 이들의 조합들을 이용하여 TM 트랜잭션들을 실행할 수 있다.

도 6을 계속 참조하면, 제1 프로세서(1070)는 메모리 제어기 허브(MCH)(1072) 및 점대점(P-P) 인터페이스들(1076, 1078)을 더 포함한다. 유사하게, 제2 프로세서(1080)는 MCH(1082) 및 P-P 인터페이스들(1086, 1088)을 포함한다. 도 6에 도시된 바와 같이, MCH들(1072, 1082)은 프로세서들을 각각의 메모리들, 즉 각각의 프로세서들에 국지적으로 부착되는 메인 메모리(예로서, 동적 랜덤 액세스 메모리(DRAM))의 부분들일 수 있는 메모리(1032) 및 메모리(1034)에 결합한다. 제1 프로세서(1070) 및 제2 프로세서(1080)는 P-P 상호접속들(1052, 1054)을 통해 각각 칩셋(1090)에 결합될 수 있다. 도 6에 도시된 바와 같이, 칩셋(1090)은 P-P 인터페이스들(1094, 1098)을 포함한다.

또한, 칩셋(1090)은 칩셋(1090)을 P-P 상호접속(1039)에 의해 고성능 그래픽 엔진(1038)과 결합하기 위한 인터페이스(1092)를 포함한다. 게다가, 칩셋(1090)은 인터페이스(1096)를 통해 제1 버스(1016)에 결합될 수 있다. 도 6에 도시된 바와 같이, 다양한 입출력(I/O) 장치들(1014)이 제1 버스(1016)를 제2 버스(1020)에 결합하는 버스 브리지(1018)와 더불어 제1 버스(1016)에 결합될 수 있다. 예를 들어 키보드/마우스(1022), 통신 장치들(1026) 및 일 실시예에서 코드(1030)를 포함할 수 있는 디스크 드라이브 또는 다른 대용량 저장 장치와 같은 데이터 저장 유닛(1028)을 포함하는 다양한 장치들이 제2 버스(1020)에 결합될 수 있다. 게다가, 오디오 I/O(1024)가 제2 버스(1020)에 결합될 수 있다.

실시예들은 코드로 구현될 수 있으며, 명령어들을 실행하도록 시스템을 프로그래밍하는 데 사용될 수 있는 명령어들을 저장한 저장 매체에 저장될 수 있다. 저장 매체는 플로피 디스크, 광 디스크, 반도체 드라이브(SSD), 콤팩트 디스크 판독 전용 메모리(CD-ROM), 콤팩트 디스크 재기록(CD-RW) 및 광자기 디스크를 포함하는 임의 타입의 디스크, 판독 전용 메모리(ROM), 동적 랜덤 액세스 메모리(DRAM), 정적 랜덤 액세스 메모리(SRAM)와 같은 랜덤 액세스 메모리(RAM), 소거 및 프로그래밍 가능한 판독 전용 메모리(EPROM), 플래시 메모리, 전기적으로 소거 및 프로그래밍 가능한 판독 전용 메모리(EEPROM)와 같은 반도체 장치, 자기 또는 광학 카드, 또는 전자 명령어들을 저장하기에 적합한 임의의 다른 타입의 매체들을 포함할 수 있지만, 이에 한정되지 않는다.

본 발명은 제한된 수의 실시예들과 관련하여 설명되었지만, 이 분야의 기술자들은 그들로부터의 다양한 변경들 및 변형들을 인식할 것이다. 첨부된 청구항들은 본 발명의 진정한 사상 및 범위 내에 속하는 바와 같은 모든 그러한 변경들 및 변형들을 커버하는 것을 의도한다.

Claims (27)

- 제1 스레드에서 트랜잭션 메모리(TM) 트랜잭션을 실행하는 단계;

상기 TM 트랜잭션 동안, 프로세서의 캐시 메모리의 제1 버퍼 내에 데이터의 블록을 버퍼링하는 단계; 및

상기 제1 버퍼 내의 상기 블록의 위치에 있는 데이터가 갱신되는 만남(encounter) 시에 상기 블록의 소유권을 얻기 위해 상기 블록에 대한 기록 모니터를 획득하는 단계

를 포함하는 방법. - 제1항에 있어서, 상기 만남 시에 상기 블록에 대한 기록 록(lock)을 획득하는 단계를 더 포함하는 방법.

- 제1항에 있어서, 상기 기록 모니터를 획득하는 단계는 상기 제1 스레드에 의한 상기 블록에 대한 상기 기록 모니터의 소유권을 지시하도록 상기 제1 스레드에 대응하는 상기 블록의 헤더의 모니터 지시자를 갱신하는 단계를 포함하는 방법.

- 제3항에 있어서, 상기 블록의 상기 모니터 지시자를 갱신하기 위해 사용자 레벨 기록 모니터 명령어를 이용하여 상기 기록 모니터를 획득하는 단계를 더 포함하는 방법.

- 제3항에 있어서, 상기 제1 스레드가 상기 블록에 대한 상기 기록 모니터를 잃지 않은 경우에 상기 TM 트랜잭션을 커미트하고, 그렇지 않은 경우에는 상기 TM 트랜잭션을 중단하는 단계를 더 포함하는 방법.

- 제5항에 있어서, 상기 TM 트랜잭션을 커미트한 후에 상기 기록 모니터를 유지하고, 제2 TM 트랜잭션에서 상기 기록 모니터를 사용하는 단계를 더 포함하는 방법.

- 제1항에 있어서, 상기 캐시 메모리의 캐시 라인에 상기 데이터를 기록하기 위해 버퍼링된 저장 명령어를 이용하여 상기 블록의 상기 위치에 있는 상기 데이터를 갱신하는 단계를 더 포함하고, 상기 버퍼링된 저장 명령어는 사용자 레벨 명령어이고, 상기 버퍼링된 저장 명령어는 상기 캐시 라인이 상기 제1 스레드에게 국지적으로 보이지만 전역적으로는 보이지 않는다는 것을 지시하기 위해 상기 캐시 라인의 캐시 일관성 상태를 버퍼링된 상태로 더 갱신하는 방법.

- 제2항에 있어서, 상기 기록 록 및 상기 기록 모니터를 획득하기 위해 제1 기록 배리어(write barrier)를 실행하는 단계를 더 포함하는 방법.

- 제8항에 있어서, 상기 블록이 버퍼링되는지를 결정하기 위해 상기 제1 버퍼에 저장된 상기 블록 내의 제2 위치에 대해 사용자 레벨 테스트 명령어를 실행하는 것을 포함하여, 상기 제2 위치를 갱신하기 위해 제2 기록 배리어를 필터링하고 제2 기록 록 또는 제2 기록 모니터를 획득하지 않는 단계를 더 포함하는 방법.

- 제2항에 있어서, 상기 TM 트랜잭션이 커미트된 후에 상기 블록에 대한 상기 기록 모니터를 모니터링하고, 상기 제1 버퍼에 저장된 상기 블록 내의 제2 위치를 갱신하기 위하여 제2 TM 트랜잭션의 기록 배리어를 필터링하고 제2 기록 록 또는 제2 기록 모니터를 획득하지 않는 단계를 더 포함하는 방법.

- 제1항에 있어서, 상기 TM 트랜잭션의 커미트 시에 상기 블록에 대한 기록 록을 획득하는 단계를 더 포함하는 방법.

- 실행시에 시스템으로 하여금,

트랜잭션 메모리(TM) 트랜잭션의 실행 동안, 블록이 프로세서의 캐시 메모리 내에 존재하는 경우에, 상기 프로세서의 상기 캐시 메모리에 저장된 상기 블록의 위치에, 데이터를 저장하기 위한 버퍼링된 저장 명령어를 이용하여, 상기 데이터를 저장하고 - 상기 버퍼링된 저장 명령어는 사용자 레벨 명령어이고, 상기 버퍼링된 저장 명령어는 상기 데이터가 시스템 메모리에 나중에 기록되는 것이 아니라 상기 캐시 메모리에 저장되는 것을 가능하게 함 -;

그렇지 않은 경우에, 제1 위치에 상기 데이터를 저장하고, 상기 저장된 데이터의 상기 제1 위치의 어드레스를 기록 로그에 저장하며;

상기 TM 트랜잭션의 커미트 시에 상기 블록에 대한 기록 모니터를 획득하고, 상기 기록 모니터링된 블록 내의 데이터가 손실되지 않은 경우에 상기 TM 트랜잭션을 커미트하게 하는

명령어들을 포함하는 컴퓨터 판독가능한 기록 매체. - 제12항에 있어서, 실행시에 상기 시스템으로 하여금, 상기 커미트 시가 아니라 만남 시에 상기 기록 모니터를 획득할 수 있게 하는 명령어들을 더 포함하고, 상기 TM 트랜잭션의 이거 모드(eager mode)가 활성인 컴퓨터 판독가능한 기록 매체.

- 제12항에 있어서, 실행시에 상기 시스템으로 하여금, 상기 기록 모니터가 획득되었는지를 결정하기 위하여 상기 제1 위치에 대해 사용자 레벨 테스트 명령어를 수행할 수 있게 하는 명령어들을 더 포함하는 컴퓨터 판독가능한 기록 매체.

- 제12항에 있어서, 실행시에 상기 시스템으로 하여금, 트랜잭션 상태 레지스터(TSR) 내의 지시자에 기초하여 임의의 버퍼링된 블록이 손실되었는지를 커미트 시에 결정하고, 임의의 버퍼링된 블록이 손실된 경우에 상기 TM 트랜잭션을 중단하고, 상기 TM 트랜잭션의 재실행을 위해 트랜잭션 실행 모드를 선택할 수 있게 하는 명령어들을 더 포함하는 컴퓨터 판독가능한 기록 매체.

- 명령어들을 실행하기 위한 적어도 하나의 코어를 포함하는 제1 프로세서;

상기 제1 프로세서에 결합된 시스템 메모리 - 상기 시스템 메모리는 상기 제1 프로세서로 하여금, 트랜잭션 메모리(TM) 트랜잭션 동안, 상기 시스템 메모리에 저장된 객체의 제1의 사전 결정된 부분과 관련된 메타데이터에 액세스하고, 상기 메타데이터가 상기 객체의 섀도 사본의 어드레스를 포함하는지를 결정하고, 그렇지 않은 경우에 상기 객체에 대해 제1 배리어 동작을 수행하고, 상기 메타데이터가 상기 어드레스를 포함하는 경우에 상기 제1 배리어 동작을 수행하지 않고, 상기 제1 배리어 동작이 수행된 경우에 상기 객체의 상기 제1의 사전 결정된 부분과 관련된 상기 메타데이터 내에 상기 객체의 상기 섀도 사본의 상기 어드레스를 저장할 수 있게 하는 명령어들을 포함함 -

를 포함하는 시스템. - 제16항에 있어서, 상기 객체의 상기 제1의 사전 결정된 부분은 상기 객체의 객체 헤더의 제1 슬롯에 대응하는 시스템.

- 제16항에 있어서, 상기 명령어들은 또한 상기 제1 프로세서로 하여금, 상기 객체의 상기 제1의 사전 결정된 부분과 관련된 상기 메타데이터 내에 포함된 상기 어드레스를 이용하여 상기 객체의 상기 섀도 사본에 액세스할 수 있게 하는 시스템.

- 제16항에 있어서, 상기 명령어들은 또한 상기 제1 프로세서로 하여금, 상기 객체로부터 데이터를 판독하기 전에 상기 액세스 및 결정을 수행할 수 있게 하는 시스템.

- 제16항에 있어서, 상기 명령어들은 또한 상기 제1 프로세서로 하여금,

상기 객체의 제2의 사전 결정된 부분과 관련된 메타데이터에 액세스하고;

상기 제2의 사전 결정된 부분과 관련된 상기 메타데이터가 상기 섀도 사본 어드레스를 포함하는지를 결정할 수 있게 하는 시스템. - 제20항에 있어서, 상기 메타데이터가 상기 섀도 사본 어드레스를 포함하지 않는 경우, 상기 명령어들은 또한 상기 제1 프로세서로 하여금, 상기 객체에 대해 제2 배리어 동작을 수행하고, 상기 객체의 상기 제1 및 제2의 사전 결정된 부분들과 관련된 상기 메타데이터 내에 상기 섀도 사본 어드레스를 저장할 수 있게 하는 시스템.

- 제16항에 있어서, 상기 명령어들은 원시 코드 애플리케이션으로 하여금, 상기 시스템 메모리에 저장된 블록의 제1의 사전 결정된 부분과 관련된 메타데이터에 액세스하고, 상기 메타데이터가 상기 블록의 섀도 사본의 어드레스를 포함하는지를 결정하고, 그렇지 않은 경우에 상기 블록에 대해 배리어 동작을 수행하고, 상기 메타데이터가 상기 어드레스를 포함하는 경우에 상기 배리어 동작을 수행하지 않고, 상기 배리어 동작이 수행된 경우에 상기 블록의 상기 제1의 사전 결정된 부분과 관련된 상기 메타데이터 내에 상기 블록의 상기 섀도 사본의 상기 어드레스를 저장할 수 있게 하는 시스템.

- 제1 스레드에서 트랜잭션 메모리(TM) 트랜잭션을 실행하는 단계;

상기 TM 트랜잭션에서 수행될 기록 데이터가 하드웨어 버퍼에 저장될 수 있는 지를 결정하는 단계;

상기 기록 데이터가 상기 하드웨어 버퍼에 저장될 수 있는 경우, 상기 데이터의 사본이 상기 하드웨어 버퍼 내에 존재하는지를 결정하고, 상기 데이터의 상기 사본이 상기 하드웨어 버퍼 내에 존재하는 경우에 상기 데이터를 기록하기 위한 버퍼링된 저장 명령어를 이용하여 상기 하드웨어 버퍼 내의 상기 데이터를 갱신하는 단계 - 상기 버퍼링된 저장 명령어는 사용자 레벨 명령어이고, 상기 버퍼링된 저장 명령어는 상기 데이터가 상기 제1 스레드에게 국지적으로 보이지만 전역적으로는 보이지 않는다는 것을 더 지시함 -; 및

상기 사본이 상기 하드웨어 버퍼 내에 존재하지 않는 경우, 상기 버퍼링된 저장 명령어를 이용하여 상기 하드웨어 버퍼의 위치에 상기 데이터의 버퍼링된 사본을 생성하고, 상기 버퍼링된 저장 명령어를 이용하여 상기 버퍼링된 사본 내의 상기 데이터를 갱신하는 단계

를 포함하는 방법. - 제23항에 있어서, 상기 TM 트랜잭션이 커미트 시간 록킹 스킴에 따르는 경우에 상기 위치의 어드레스를 기록 로그에 저장하고, 상기 TM 트랜잭션이 만남 시간 록킹 스킴에 따르는 경우에 상기 위치에 상기 데이터를 저장하고, 상기 데이터가 상기 위치에 저장되는 만남 시에 상기 위치의 소유권을 얻기 위해 상기 위치에 대한 기록 모니터를 획득하는 단계를 더 포함하는 방법.

- 제24항에 있어서, 상기 TM 트랜잭션이 상기 커미트 시간 록킹 스킴에 따를 때 상기 위치 내의 데이터가 손실되지 않은 경우에, 커미트 시에 상기 위치에 대한 기록 모니터를 획득하고 상기 TM 트랜잭션을 커미트하는 단계를 더 포함하는 방법.

- 제25항에 있어서, 상기 사본이 상기 하드웨어 버퍼 내에 존재하는 경우에, 상기 데이터가 버퍼링되는지를 결정하기 위하여 상기 하드웨어 버퍼 내의 제2 위치에 대해 사용자 레벨 테스트 명령어를 수행하는 것을 포함하여, 상기 제2 위치를 갱신하기 위해 배리어 동작을 필터링하고 제2 기록 모니터를 획득하지 않는 방법.

- 제23항에 있어서, 상기 TM 트랜잭션이 상기 하드웨어 버퍼를 오버플로우하는 경우, 상기 TM 트랜잭션을 중단하고, 제어를 이젝션 핸들러에 제공하여, 상기 TM 트랜잭션을 재실행하기 위한 트랜잭션 실행 모드를 선택하는 단계를 더 포함하는 방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/638,054 | 2009-12-15 | ||

| US12/638,054 US8316194B2 (en) | 2009-12-15 | 2009-12-15 | Mechanisms to accelerate transactions using buffered stores |

| PCT/US2010/056142 WO2011081718A2 (en) | 2009-12-15 | 2010-11-10 | Mechanisms to accelerate transactions using buffered stores |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20120103715A KR20120103715A (ko) | 2012-09-19 |

| KR101470713B1 true KR101470713B1 (ko) | 2014-12-08 |

Family

ID=44144191

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020127018482A KR101470713B1 (ko) | 2009-12-15 | 2010-11-10 | 버퍼링된 저장을 이용하여 트랜잭션들을 가속화하기 위한 메커니즘들 |

Country Status (7)

| Country | Link |

|---|---|

| US (5) | US8316194B2 (ko) |

| EP (1) | EP2513779A4 (ko) |

| JP (1) | JP5507706B2 (ko) |

| KR (1) | KR101470713B1 (ko) |

| CN (2) | CN102741806B (ko) |

| AU (1) | AU2010337318B2 (ko) |

| WO (1) | WO2011081718A2 (ko) |

Families Citing this family (129)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8607241B2 (en) | 2004-06-30 | 2013-12-10 | Intel Corporation | Compare and exchange operation using sleep-wakeup mechanism |

| US8316194B2 (en) | 2009-12-15 | 2012-11-20 | Intel Corporation | Mechanisms to accelerate transactions using buffered stores |

| US20110238490A1 (en) * | 2010-03-25 | 2011-09-29 | Microsoft Corporation | Auction flighting |

| US8922559B2 (en) * | 2010-03-26 | 2014-12-30 | Microsoft Corporation | Graph clustering |

| EP2444903A1 (en) | 2010-09-29 | 2012-04-25 | STMicroelectronics (Grenoble 2) SAS | A transaction reordering arrangement |

| EP2442231A1 (en) * | 2010-09-29 | 2012-04-18 | STMicroelectronics (Grenoble 2) SAS | Reordering arrangement |

| US8745134B1 (en) | 2011-03-04 | 2014-06-03 | Zynga Inc. | Cross social network data aggregation |

| US8332488B1 (en) * | 2011-03-04 | 2012-12-11 | Zynga Inc. | Multi-level cache with synch |

| US8347322B1 (en) | 2011-03-31 | 2013-01-01 | Zynga Inc. | Social network application programming interface |

| US10135776B1 (en) | 2011-03-31 | 2018-11-20 | Zynga Inc. | Cross platform social networking messaging system |

| US8607247B2 (en) * | 2011-11-03 | 2013-12-10 | Advanced Micro Devices, Inc. | Method and system for workitem synchronization |

| US9009318B2 (en) | 2011-11-03 | 2015-04-14 | Microsoft Corporation | Offline resource allocation algorithms |

| US20130117062A1 (en) * | 2011-11-03 | 2013-05-09 | Microsoft Corporation | Online resource allocation algorithms |

| US9092272B2 (en) * | 2011-12-08 | 2015-07-28 | International Business Machines Corporation | Preparing parallel tasks to use a synchronization register |

| US20140059333A1 (en) * | 2012-02-02 | 2014-02-27 | Martin G. Dixon | Method, apparatus, and system for speculative abort control mechanisms |

| US9430238B2 (en) | 2012-03-16 | 2016-08-30 | International Business Machines Corporation | Run-time-instrumentation controls emit instruction |

| US9465716B2 (en) | 2012-03-16 | 2016-10-11 | International Business Machines Corporation | Run-time instrumentation directed sampling |

| US9280447B2 (en) | 2012-03-16 | 2016-03-08 | International Business Machines Corporation | Modifying run-time-instrumentation controls from a lesser-privileged state |

| US9411591B2 (en) * | 2012-03-16 | 2016-08-09 | International Business Machines Corporation | Run-time instrumentation sampling in transactional-execution mode |

| US9158660B2 (en) | 2012-03-16 | 2015-10-13 | International Business Machines Corporation | Controlling operation of a run-time instrumentation facility |

| US9454462B2 (en) | 2012-03-16 | 2016-09-27 | International Business Machines Corporation | Run-time instrumentation monitoring for processor characteristic changes |

| US9367316B2 (en) | 2012-03-16 | 2016-06-14 | International Business Machines Corporation | Run-time instrumentation indirect sampling by instruction operation code |

| US9483268B2 (en) | 2012-03-16 | 2016-11-01 | International Business Machines Corporation | Hardware based run-time instrumentation facility for managed run-times |

| US9250902B2 (en) | 2012-03-16 | 2016-02-02 | International Business Machines Corporation | Determining the status of run-time-instrumentation controls |

| US9405541B2 (en) | 2012-03-16 | 2016-08-02 | International Business Machines Corporation | Run-time instrumentation indirect sampling by address |

| US9442824B2 (en) | 2012-03-16 | 2016-09-13 | International Business Machines Corporation | Transformation of a program-event-recording event into a run-time instrumentation event |

| US9471315B2 (en) | 2012-03-16 | 2016-10-18 | International Business Machines Corporation | Run-time instrumentation reporting |

| US9146741B2 (en) | 2012-04-26 | 2015-09-29 | Qualcomm Incorporated | Eliminating redundant masking operations instruction processing circuits, and related processor systems, methods, and computer-readable media |

| ITTO20120470A1 (it) | 2012-05-30 | 2013-12-01 | St Microelectronics Srl | Procedimento per gestire transazioni di accesso e relativo sistema |

| US9448796B2 (en) | 2012-06-15 | 2016-09-20 | International Business Machines Corporation | Restricted instructions in transactional execution |

| US20130339680A1 (en) | 2012-06-15 | 2013-12-19 | International Business Machines Corporation | Nontransactional store instruction |

| US9384004B2 (en) | 2012-06-15 | 2016-07-05 | International Business Machines Corporation | Randomized testing within transactional execution |

| US10437602B2 (en) | 2012-06-15 | 2019-10-08 | International Business Machines Corporation | Program interruption filtering in transactional execution |

| US9740549B2 (en) | 2012-06-15 | 2017-08-22 | International Business Machines Corporation | Facilitating transaction completion subsequent to repeated aborts of the transaction |

| US9436477B2 (en) | 2012-06-15 | 2016-09-06 | International Business Machines Corporation | Transaction abort instruction |

| US9442737B2 (en) | 2012-06-15 | 2016-09-13 | International Business Machines Corporation | Restricting processing within a processor to facilitate transaction completion |

| US9367323B2 (en) | 2012-06-15 | 2016-06-14 | International Business Machines Corporation | Processor assist facility |

| US9361115B2 (en) | 2012-06-15 | 2016-06-07 | International Business Machines Corporation | Saving/restoring selected registers in transactional processing |

| US8966324B2 (en) | 2012-06-15 | 2015-02-24 | International Business Machines Corporation | Transactional execution branch indications |

| US8682877B2 (en) * | 2012-06-15 | 2014-03-25 | International Business Machines Corporation | Constrained transaction execution |

| US8688661B2 (en) | 2012-06-15 | 2014-04-01 | International Business Machines Corporation | Transactional processing |

| US9317460B2 (en) | 2012-06-15 | 2016-04-19 | International Business Machines Corporation | Program event recording within a transactional environment |

| US8880959B2 (en) | 2012-06-15 | 2014-11-04 | International Business Machines Corporation | Transaction diagnostic block |

| US9772854B2 (en) | 2012-06-15 | 2017-09-26 | International Business Machines Corporation | Selectively controlling instruction execution in transactional processing |

| US9348642B2 (en) | 2012-06-15 | 2016-05-24 | International Business Machines Corporation | Transaction begin/end instructions |

| US9336046B2 (en) | 2012-06-15 | 2016-05-10 | International Business Machines Corporation | Transaction abort processing |

| US20140075124A1 (en) * | 2012-09-07 | 2014-03-13 | International Business Machines Corporation | Selective Delaying of Write Requests in Hardware Transactional Memory Systems |

| US9361116B2 (en) * | 2012-12-28 | 2016-06-07 | Intel Corporation | Apparatus and method for low-latency invocation of accelerators |

| US9417873B2 (en) | 2012-12-28 | 2016-08-16 | Intel Corporation | Apparatus and method for a hybrid latency-throughput processor |

| US10140129B2 (en) | 2012-12-28 | 2018-11-27 | Intel Corporation | Processing core having shared front end unit |

| US10346195B2 (en) | 2012-12-29 | 2019-07-09 | Intel Corporation | Apparatus and method for invocation of a multi threaded accelerator |

| US20140281429A1 (en) * | 2013-03-14 | 2014-09-18 | Qualcomm Incorporated | Eliminating redundant synchronization barriers in instruction processing circuits, and related processor systems, methods, and computer-readable media |

| US9547594B2 (en) | 2013-03-15 | 2017-01-17 | Intel Corporation | Instructions to mark beginning and end of non transactional code region requiring write back to persistent storage |

| KR102094475B1 (ko) | 2013-04-29 | 2020-03-27 | 삼성전자주식회사 | 멀티-트랜잭션의 아토믹 라이트 방법 |

| EP3011465A4 (en) * | 2013-06-18 | 2017-01-25 | Intel Corporation | Software polling elision with restricted transactional memory |

| US9766926B2 (en) * | 2013-09-13 | 2017-09-19 | Oracle International Corporation | Method and system for optimizing parallel program execution based on speculation that an object written to is not shared |

| US9524195B2 (en) | 2014-02-27 | 2016-12-20 | International Business Machines Corporation | Adaptive process for data sharing with selection of lock elision and locking |

| JP6244916B2 (ja) * | 2014-01-06 | 2017-12-13 | 富士通株式会社 | 演算処理装置,演算処理装置の制御方法及び情報処理装置 |

| US20150205721A1 (en) * | 2014-01-22 | 2015-07-23 | Advanced Micro Devices, Inc. | Handling Reads Following Transactional Writes during Transactions in a Computing Device |

| US9311178B2 (en) | 2014-02-27 | 2016-04-12 | International Business Machines Corporation | Salvaging hardware transactions with instructions |

| US9442775B2 (en) | 2014-02-27 | 2016-09-13 | International Business Machines Corporation | Salvaging hardware transactions with instructions to transfer transaction execution control |

| US9411729B2 (en) | 2014-02-27 | 2016-08-09 | International Business Machines Corporation | Salvaging lock elision transactions |

| US9645879B2 (en) | 2014-02-27 | 2017-05-09 | International Business Machines Corporation | Salvaging hardware transactions with instructions |

| US9336097B2 (en) | 2014-02-27 | 2016-05-10 | International Business Machines Corporation | Salvaging hardware transactions |

| US9465673B2 (en) | 2014-02-27 | 2016-10-11 | International Business Machines Corporation | Deferral instruction for managing transactional aborts in transactional memory computing environments to complete transaction by deferring disruptive events handling |

| US9329946B2 (en) | 2014-02-27 | 2016-05-03 | International Business Machines Corporation | Salvaging hardware transactions |

| US9471371B2 (en) | 2014-02-27 | 2016-10-18 | International Business Machines Corporation | Dynamic prediction of concurrent hardware transactions resource requirements and allocation |

| US9442853B2 (en) | 2014-02-27 | 2016-09-13 | International Business Machines Corporation | Salvaging lock elision transactions with instructions to change execution type |

| US20150242216A1 (en) | 2014-02-27 | 2015-08-27 | International Business Machines Corporation | Committing hardware transactions that are about to run out of resource |

| US9361041B2 (en) | 2014-02-27 | 2016-06-07 | International Business Machines Corporation | Hint instruction for managing transactional aborts in transactional memory computing environments |

| US9262206B2 (en) | 2014-02-27 | 2016-02-16 | International Business Machines Corporation | Using the transaction-begin instruction to manage transactional aborts in transactional memory computing environments |

| US9430273B2 (en) | 2014-02-27 | 2016-08-30 | International Business Machines Corporation | Suppressing aborting a transaction beyond a threshold execution duration based on the predicted duration |

| US9575890B2 (en) | 2014-02-27 | 2017-02-21 | International Business Machines Corporation | Supporting atomic accumulation with an addressable accumulator |

| US9424072B2 (en) | 2014-02-27 | 2016-08-23 | International Business Machines Corporation | Alerting hardware transactions that are about to run out of space |

| US9524187B2 (en) | 2014-03-02 | 2016-12-20 | International Business Machines Corporation | Executing instruction with threshold indicating nearing of completion of transaction |

| US9971627B2 (en) | 2014-03-26 | 2018-05-15 | Intel Corporation | Enabling maximum concurrency in a hybrid transactional memory system |

| US9569212B2 (en) * | 2014-03-28 | 2017-02-14 | Intel Corporation | Instruction and logic for a memory ordering buffer |

| US9870209B2 (en) * | 2014-03-28 | 2018-01-16 | Intel Corporation | Instruction and logic for reducing data cache evictions in an out-of-order processor |

| US9916356B2 (en) | 2014-03-31 | 2018-03-13 | Sandisk Technologies Llc | Methods and systems for insert optimization of tiered data structures |

| US10956050B2 (en) * | 2014-03-31 | 2021-03-23 | Sandisk Enterprise Ip Llc | Methods and systems for efficient non-isolated transactions |

| US20150324135A1 (en) * | 2014-05-06 | 2015-11-12 | Netapp, Inc. | Automatic storage system configuration based on workload monitoring |

| US9477481B2 (en) | 2014-06-27 | 2016-10-25 | International Business Machines Corporation | Accurate tracking of transactional read and write sets with speculation |

| US10114752B2 (en) | 2014-06-27 | 2018-10-30 | International Business Machines Corporation | Detecting cache conflicts by utilizing logical address comparisons in a transactional memory |

| US10025715B2 (en) | 2014-06-27 | 2018-07-17 | International Business Machines Corporation | Conditional inclusion of data in a transactional memory read set |

| US9703718B2 (en) | 2014-06-27 | 2017-07-11 | International Business Machines Corporation | Managing read tags in a transactional memory |

| US9524257B2 (en) * | 2014-06-27 | 2016-12-20 | International Business Machines Corporation | Transactional execution enabled supervisor call interruption while in TX mode |

| US9740614B2 (en) | 2014-06-27 | 2017-08-22 | International Business Machines Corporation | Processor directly storing address range of co-processor memory accesses in a transactional memory where co-processor supplements functions of the processor |

| US10073784B2 (en) | 2014-06-27 | 2018-09-11 | International Business Machines Corporation | Memory performance when speculation control is enabled, and instruction therefor |

| US9658961B2 (en) | 2014-06-27 | 2017-05-23 | International Business Machines Corporation | Speculation control for improving transaction success rate, and instruction therefor |

| US20150378939A1 (en) * | 2014-06-27 | 2015-12-31 | Analog Devices, Inc. | Memory mechanism for providing semaphore functionality in multi-master processing environment |

| US10013351B2 (en) | 2014-06-27 | 2018-07-03 | International Business Machines Corporation | Transactional execution processor having a co-processor accelerator, both sharing a higher level cache |

| US9772944B2 (en) | 2014-06-27 | 2017-09-26 | International Business Machines Corporation | Transactional execution in a multi-processor environment that monitors memory conflicts in a shared cache |

| US9720837B2 (en) | 2014-06-27 | 2017-08-01 | International Business Machines Corporation | Allowing non-cacheable loads within a transaction |

| US9471397B2 (en) * | 2014-10-03 | 2016-10-18 | International Business Machines Corporation | Global lock contention predictor |

| US9767024B2 (en) * | 2014-12-18 | 2017-09-19 | Intel Corporation | Cache closure and persistent snapshot in dynamic code generating system software |

| US10929353B2 (en) | 2015-04-29 | 2021-02-23 | Box, Inc. | File tree streaming in a virtual file system for cloud-based shared content |

| US10318430B2 (en) | 2015-06-26 | 2019-06-11 | International Business Machines Corporation | System operation queue for transaction |

| US10133764B2 (en) | 2015-09-30 | 2018-11-20 | Sandisk Technologies Llc | Reduction of write amplification in object store |

| US9563467B1 (en) | 2015-10-29 | 2017-02-07 | International Business Machines Corporation | Interprocessor memory status communication |

| US9916179B2 (en) | 2015-10-29 | 2018-03-13 | International Business Machines Corporation | Interprocessor memory status communication |

| US10261827B2 (en) | 2015-10-29 | 2019-04-16 | International Business Machines Corporation | Interprocessor memory status communication |

| US9760397B2 (en) | 2015-10-29 | 2017-09-12 | International Business Machines Corporation | Interprocessor memory status communication |

| US9619165B1 (en) | 2015-10-30 | 2017-04-11 | Sandisk Technologies Llc | Convertible leaf memory mapping |

| US9471313B1 (en) * | 2015-11-25 | 2016-10-18 | International Business Machines Corporation | Flushing speculative instruction processing |

| US10289340B2 (en) | 2016-02-23 | 2019-05-14 | Sandisk Technologies Llc | Coalescing metadata and data writes via write serialization with device-level address remapping |

| US10747676B2 (en) | 2016-02-23 | 2020-08-18 | Sandisk Technologies Llc | Memory-efficient object address mapping in a tiered data structure |

| US10185658B2 (en) | 2016-02-23 | 2019-01-22 | Sandisk Technologies Llc | Efficient implementation of optimized host-based garbage collection strategies using xcopy and multiple logical stripes |

| US9996471B2 (en) * | 2016-06-28 | 2018-06-12 | Arm Limited | Cache with compressed data and tag |

| CN107562648B (zh) * | 2016-07-01 | 2021-04-06 | 北京忆恒创源科技有限公司 | 无锁ftl访问方法与装置 |

| US10664306B2 (en) | 2017-01-13 | 2020-05-26 | Arm Limited | Memory partitioning |

| US20180203807A1 (en) | 2017-01-13 | 2018-07-19 | Arm Limited | Partitioning tlb or cache allocation |

| US10268379B2 (en) | 2017-01-13 | 2019-04-23 | Arm Limited | Partitioning of memory system resources or performance monitoring |

| US10649678B2 (en) | 2017-01-13 | 2020-05-12 | Arm Limited | Partitioning of memory system resources or performance monitoring |

| US10394454B2 (en) * | 2017-01-13 | 2019-08-27 | Arm Limited | Partitioning of memory system resources or performance monitoring |

| US10795836B2 (en) * | 2017-04-17 | 2020-10-06 | Microsoft Technology Licensing, Llc | Data processing performance enhancement for neural networks using a virtualized data iterator |

| US10929210B2 (en) | 2017-07-07 | 2021-02-23 | Box, Inc. | Collaboration system protocol processing |

| US11470131B2 (en) | 2017-07-07 | 2022-10-11 | Box, Inc. | User device processing of information from a network-accessible collaboration system |

| US10664400B2 (en) | 2017-07-11 | 2020-05-26 | Arm Limited | Address translation cache partitioning |

| US10430187B2 (en) * | 2017-08-15 | 2019-10-01 | Oracle International Corporation | Persistent transactional memory metadata-based buffer caches |

| US10552042B2 (en) * | 2017-09-06 | 2020-02-04 | Samsung Electronics Co., Ltd. | Effective transaction table with page bitmap |

| GB2567433B (en) * | 2017-10-10 | 2020-02-26 | Advanced Risc Mach Ltd | Checking lock variables for transactions in a system with transactional memory support |

| GB2570474B (en) * | 2018-01-26 | 2020-04-15 | Advanced Risc Mach Ltd | Region fusing |

| EP3863259A4 (en) | 2018-10-24 | 2021-12-08 | Samsung Electronics Co., Ltd. | PROCESS, DEVICE, COMPUTER READABLE MEDIA, AND TRANSACTION MANAGEMENT SYSTEM |

| CN110109759B (zh) * | 2019-05-07 | 2021-11-26 | Oppo广东移动通信有限公司 | 卡顿优化方法、服务器、电子装置及计算机可读存储介质 |

| US11256625B2 (en) | 2019-09-10 | 2022-02-22 | Arm Limited | Partition identifiers for page table walk memory transactions |

| US11226764B2 (en) | 2020-01-16 | 2022-01-18 | International Business Machines Corporation | Consistent reads in a distributed transaction protocol |

| US11928497B2 (en) * | 2020-01-27 | 2024-03-12 | International Business Machines Corporation | Implementing erasure coding with persistent memory |

| CN111984379B (zh) * | 2020-07-14 | 2023-04-07 | 上海金仕达软件科技股份有限公司 | 读写事务控制方法、系统、终端设备及存储介质 |

| CN113722052B (zh) * | 2021-08-23 | 2024-02-20 | 华中科技大学 | 一种基于数据双版本的非易失内存更新方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6571332B1 (en) * | 2000-04-11 | 2003-05-27 | Advanced Micro Devices, Inc. | Method and apparatus for combined transaction reordering and buffer management |

| US7313764B1 (en) * | 2003-03-06 | 2007-12-25 | Apple Inc. | Method and apparatus to accelerate scrolling for buffered windows |

| US20080256073A1 (en) * | 2007-04-11 | 2008-10-16 | Microsoft Corporation | Transactional memory using buffered writes and enforced serialization order |

| US20090144524A1 (en) * | 2007-11-29 | 2009-06-04 | International Business Machines Corporation | Method and System for Handling Transaction Buffer Overflow In A Multiprocessor System |

Family Cites Families (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0588954A (ja) * | 1991-09-27 | 1993-04-09 | Nippon Telegr & Teleph Corp <Ntt> | データベースの更新方法 |

| US6212574B1 (en) | 1997-04-04 | 2001-04-03 | Microsoft Corporation | User mode proxy of kernel mode operations in a computer operating system |

| JPH11338834A (ja) * | 1998-05-26 | 1999-12-10 | Ai System Kk | 同期型並列処理システムおよび同期型並列処理方法 |

| US6243778B1 (en) | 1998-10-13 | 2001-06-05 | Stmicroelectronics, Inc. | Transaction interface for a data communication system |

| US20020108025A1 (en) | 1998-10-21 | 2002-08-08 | Nicholas Shaylor | Memory management unit for java environment computers |

| US6640285B1 (en) | 2000-10-26 | 2003-10-28 | Emc Corporation | Method and apparatus for improving the efficiency of cache memories using stored activity measures |

| JP2002373082A (ja) * | 2001-06-15 | 2002-12-26 | Nec Corp | マルチタスク構成のトランザクション処理方法及びトランザクション処理プログラム |

| US7127561B2 (en) | 2001-12-31 | 2006-10-24 | Intel Corporation | Coherency techniques for suspending execution of a thread until a specified memory access occurs |

| US6978396B2 (en) | 2002-05-30 | 2005-12-20 | Solid Information Technology Oy | Method and system for processing replicated transactions parallel in secondary server |

| US7120825B2 (en) | 2003-06-06 | 2006-10-10 | Hewlett-Packard Development Company, L.P. | Adaptive batch sizing for asynchronous data redundancy |

| US7836450B2 (en) | 2003-08-28 | 2010-11-16 | Mips Technologies, Inc. | Symmetric multiprocessor operating system for execution on non-independent lightweight thread contexts |

| US20050086446A1 (en) | 2003-10-04 | 2005-04-21 | Mckenney Paul E. | Utilizing software locking approach to execute code upon failure of hardware transactional approach |

| US7395382B1 (en) | 2004-08-10 | 2008-07-01 | Sun Microsystems, Inc. | Hybrid software/hardware transactional memory |

| US7523265B2 (en) * | 2005-03-18 | 2009-04-21 | International Business Machines Corporation | Systems and arrangements for promoting a line to exclusive in a fill buffer of a cache |

| US7882339B2 (en) * | 2005-06-23 | 2011-02-01 | Intel Corporation | Primitives to enhance thread-level speculation |

| US7590806B2 (en) | 2005-12-07 | 2009-09-15 | Microsoft Corporation | Filtering of transactional memory operations using associative tables |

| US7809903B2 (en) | 2005-12-15 | 2010-10-05 | Intel Corporation | Coordinating access to memory locations for hardware transactional memory transactions and software transactional memory transactions |

| US7870545B2 (en) | 2005-12-16 | 2011-01-11 | Intel Corporation | Protecting shared variables in a software transactional memory system |

| US8683143B2 (en) | 2005-12-30 | 2014-03-25 | Intel Corporation | Unbounded transactional memory systems |

| US7730286B2 (en) | 2005-12-30 | 2010-06-01 | Intel Corporation | Software assisted nested hardware transactions |

| US20070186056A1 (en) * | 2006-02-07 | 2007-08-09 | Bratin Saha | Hardware acceleration for a software transactional memory system |

| US8028133B2 (en) | 2006-02-22 | 2011-09-27 | Oracle America, Inc. | Globally incremented variable or clock based methods and apparatus to implement parallel transactions |

| US7620850B2 (en) | 2006-06-09 | 2009-11-17 | Sun Microsystems, Inc. | Breakpoints in a transactional memory-based representation of code |

| US7502897B2 (en) | 2006-06-28 | 2009-03-10 | Intel Corporation | Object based conflict detection in a software transactional memory |

| US7542977B2 (en) | 2006-06-29 | 2009-06-02 | Intel Corporation | Transactional memory with automatic object versioning |

| US7802136B2 (en) | 2006-12-28 | 2010-09-21 | Intel Corporation | Compiler technique for efficient register checkpointing to support transaction roll-back |

| US8086827B2 (en) | 2006-12-28 | 2011-12-27 | Intel Corporation | Mechanism for irrevocable transactions |

| US8132158B2 (en) | 2006-12-28 | 2012-03-06 | Cheng Wang | Mechanism for software transactional memory commit/abort in unmanaged runtime environment |

| US8719807B2 (en) | 2006-12-28 | 2014-05-06 | Intel Corporation | Handling precompiled binaries in a hardware accelerated software transactional memory system |

| US8185698B2 (en) | 2007-04-09 | 2012-05-22 | Bratin Saha | Hardware acceleration of a write-buffering software transactional memory |

| US8140773B2 (en) | 2007-06-27 | 2012-03-20 | Bratin Saha | Using ephemeral stores for fine-grained conflict detection in a hardware accelerated STM |

| US8065490B2 (en) * | 2007-09-28 | 2011-11-22 | Intel Corporation | Hardware acceleration of strongly atomic software transactional memory |

| US7966459B2 (en) | 2007-12-31 | 2011-06-21 | Oracle America, Inc. | System and method for supporting phased transactional memory modes |

| JP2009245252A (ja) * | 2008-03-31 | 2009-10-22 | Fuji Xerox Co Ltd | 画像処理装置及び電子ペン及びプログラム |

| US8191046B2 (en) | 2008-10-06 | 2012-05-29 | Microsoft Corporation | Checking transactional memory implementations |

| DE112009005006T5 (de) | 2009-06-26 | 2013-01-10 | Intel Corporation | Optimierungen für ein ungebundenes transaktionales Speichersystem (UTM) |

| US8316194B2 (en) | 2009-12-15 | 2012-11-20 | Intel Corporation | Mechanisms to accelerate transactions using buffered stores |

-

2009

- 2009-12-15 US US12/638,054 patent/US8316194B2/en active Active

-

2010

- 2010-11-10 CN CN201080063965.5A patent/CN102741806B/zh active Active

- 2010-11-10 CN CN201510063088.6A patent/CN104598397B/zh active Active

- 2010-11-10 EP EP10841433.5A patent/EP2513779A4/en active Pending

- 2010-11-10 WO PCT/US2010/056142 patent/WO2011081718A2/en active Application Filing

- 2010-11-10 JP JP2012544519A patent/JP5507706B2/ja not_active Expired - Fee Related

- 2010-11-10 AU AU2010337318A patent/AU2010337318B2/en active Active

- 2010-11-10 KR KR1020127018482A patent/KR101470713B1/ko active IP Right Grant

-

2012

- 2012-10-23 US US13/658,212 patent/US9069670B2/en active Active

- 2012-10-23 US US13/658,264 patent/US8886894B2/en active Active

- 2012-10-23 US US13/658,360 patent/US8856466B2/en active Active

-

2014

- 2014-11-10 US US14/536,805 patent/US9195600B2/en not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6571332B1 (en) * | 2000-04-11 | 2003-05-27 | Advanced Micro Devices, Inc. | Method and apparatus for combined transaction reordering and buffer management |

| US7313764B1 (en) * | 2003-03-06 | 2007-12-25 | Apple Inc. | Method and apparatus to accelerate scrolling for buffered windows |

| US20080256073A1 (en) * | 2007-04-11 | 2008-10-16 | Microsoft Corporation | Transactional memory using buffered writes and enforced serialization order |

| US20090144524A1 (en) * | 2007-11-29 | 2009-06-04 | International Business Machines Corporation | Method and System for Handling Transaction Buffer Overflow In A Multiprocessor System |

Also Published As

| Publication number | Publication date |

|---|---|

| US9069670B2 (en) | 2015-06-30 |

| EP2513779A4 (en) | 2014-01-29 |

| AU2010337318B2 (en) | 2016-02-18 |

| CN104598397A (zh) | 2015-05-06 |

| KR20120103715A (ko) | 2012-09-19 |

| CN104598397B (zh) | 2017-11-17 |

| US20130046924A1 (en) | 2013-02-21 |

| US20130046925A1 (en) | 2013-02-21 |