JP7623398B2 - メモリ要件が低減されたデュアルモーメンタム勾配最適化 - Google Patents

メモリ要件が低減されたデュアルモーメンタム勾配最適化 Download PDFInfo

- Publication number

- JP7623398B2 JP7623398B2 JP2022561510A JP2022561510A JP7623398B2 JP 7623398 B2 JP7623398 B2 JP 7623398B2 JP 2022561510 A JP2022561510 A JP 2022561510A JP 2022561510 A JP2022561510 A JP 2022561510A JP 7623398 B2 JP7623398 B2 JP 7623398B2

- Authority

- JP

- Japan

- Prior art keywords

- momentum values

- momentum

- format

- gradient

- values

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N20/00—Machine learning

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/044—Recurrent networks, e.g. Hopfield networks

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/044—Recurrent networks, e.g. Hopfield networks

- G06N3/0442—Recurrent networks, e.g. Hopfield networks characterised by memory or gating, e.g. long short-term memory [LSTM] or gated recurrent units [GRU]

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/045—Combinations of networks

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/0464—Convolutional networks [CNN, ConvNet]

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/0495—Quantised networks; Sparse networks; Compressed networks

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/06—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons

- G06N3/063—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons using electronic means

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/08—Learning methods

- G06N3/084—Backpropagation, e.g. using gradient descent

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/08—Learning methods

- G06N3/09—Supervised learning

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/08—Learning methods

- G06N3/098—Distributed learning, e.g. federated learning

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N5/00—Computing arrangements using knowledge-based models

- G06N5/04—Inference or reasoning models

- G06N5/046—Forward inferencing; Production systems

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- Software Systems (AREA)

- Computing Systems (AREA)

- Artificial Intelligence (AREA)

- Mathematical Physics (AREA)

- General Physics & Mathematics (AREA)

- Data Mining & Analysis (AREA)

- Evolutionary Computation (AREA)

- General Engineering & Computer Science (AREA)

- Biophysics (AREA)

- Biomedical Technology (AREA)

- Life Sciences & Earth Sciences (AREA)

- Health & Medical Sciences (AREA)

- Computational Linguistics (AREA)

- General Health & Medical Sciences (AREA)

- Molecular Biology (AREA)

- Neurology (AREA)

- Computer Vision & Pattern Recognition (AREA)

- Medical Informatics (AREA)

- Complex Calculations (AREA)

- Management, Administration, Business Operations System, And Electronic Commerce (AREA)

- Feedback Control In General (AREA)

- Advance Control (AREA)

Description

ft=ρ(Wxfxt+Whfht-1+Wcfct-1+bf)

ct=ftct-1ittanh(Wxcxt+Whcht-1+bc)

ot=ρ(Wxoxt+Whoht-1+Wcoct+bo)

ht=ottanh(ct)

[00021]この例では、各LSTM層の内部で、入力と隠れ状態は、ベクトル演算(例えば、ドット積、内積、またはベクトル加算)と非線形関数(例えば、シグモイド、双曲線、および接線)の組み合わせを使用して処理され得る。ある場合には、最も計算集約的な演算は、密な行列-ベクトルおよび行列-行列の乗算ルーチンを使用して実装され得る、ドット積から生じる可能性がある。一実施例では、ベクトル演算および非線形関数の処理は、並列に実行されてもよい。

st:=β2・st+(1-β2)・dw2

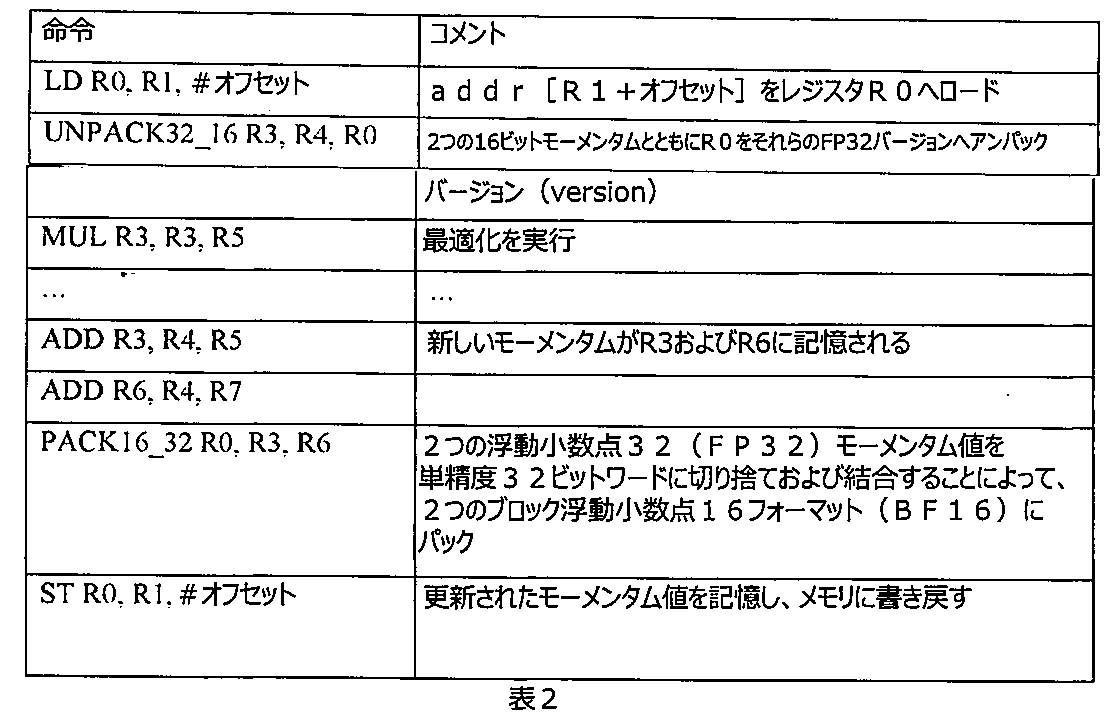

[00023]有利には、デュアルモーメンタムオプティマイザの使用は、SGD(確率的勾配降下法)のようなゼロ/シングルモーメンタムオプティマイザよりも速く収束するニューラルネットワークモデルを得ることができる。しかし、デュアルモーメンタムオプティマイザを使用すると、モデル重み以外のモーメンタムをバッファリングするために、ゼロ/シングルモーメンタムオプティマイザが必要とするメモリの少なくとも2倍のメモリが必要になる場合がある。この傾向は、特に数百万から数十億のパラメータを含む大規模なモデルで深刻化する可能性がある。オプティマイザがメモリ制限のあるGPU/ASIC上で実行される場合、オプティマイザが要求するメモリ領域は、逆に最大バッチサイズを低減させる。一方、オプティマイザをホストCPUに移すことで、メモリサイズのボトルネックは解消され得る。しかし、メモリ帯域幅のボトルネックは、プロセッサが重み/勾配ペアごとにメモリから2つのFP32モーメンタムを余分にフェッチし、それらを記憶する必要があるので、オプティマイザの速度を低下させる可能性がある。

st:=β2・st+(1-β2)・dw2

st_new:=β2・st_fp32+(1-β2)・dw2

st:=β2・st+(1-β2)・dw2

Claims (20)

- 勾配(gradient)オプティマイザと、L層を含むニューラルネットワークモデルに関連するモーメンタム値を記憶するように構成されたメモリと、を含むシステムにおける方法であって、Lは1より大きい整数であり、

選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応する、モーメンタム値の第1のセットを前記メモリから取り出すステップと、

前記選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応する、モーメンタム値の第2のセットを前記メモリから取り出すステップと、

前記選択された記憶フォーマットを有するモーメンタム値の前記第1のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第3のセットに変換するステップと、

前記選択された記憶フォーマットを有するモーメンタム値の前記第2のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第4のセットに変換するステップと、

前記勾配オプティマイザを用いて、モーメンタム値の前記第3のセットおよびモーメンタム値の前記第4のセットを使用して勾配最適化を実行するステップと、

を含み、前記勾配オプティマイザは、連続するバーストサイクルが前記勾配オプティマイザを通る勾配のストリーミングをもたらすように、バーストモードで動作するように構成される、

方法。 - 前記選択された記憶フォーマットは、縮小単精度(reduced single precision)フォーマットを含む、

請求項1に記載の方法。 - 前記訓練フォーマットは、単精度フォーマットまたは倍精度(double precision)フォーマットを含む、

請求項1記載の方法。 - 勾配(gradient)オプティマイザと、L層を含むニューラルネットワークモデルに関連するモーメンタム値を記憶するように構成されたメモリと、を含むシステムにおける方法であって、Lは1より大きい整数であり、

選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応する、モーメンタム値の第1のセットを前記メモリから取り出すステップと、

前記選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応する、モーメンタム値の第2のセットを前記メモリから取り出すステップと、

前記選択された記憶フォーマットを有するモーメンタム値の前記第1のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第3のセットに変換するステップと、

前記選択された記憶フォーマットを有するモーメンタム値の前記第2のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第4のセットに変換するステップと、

前記勾配オプティマイザを用いて、モーメンタム値の前記第3のセットおよびモーメンタム値の前記第4のセットを使用して勾配最適化を実行するステップと、

を含み、前記選択された記憶フォーマットを有するモーメンタム値の前記第1のセットを、前記訓練フォーマットを有するモーメンタム値の前記第3のセットに変換するステップは、単精度フォーマットのモーメンタム値を形成するために余分なゼロビットをパディング(padding)するステップを含む、

方法。 - 勾配(gradient)オプティマイザと、L層を含むニューラルネットワークモデルに関連するモーメンタム値を記憶するように構成されたメモリと、を含むシステムにおける方法であって、Lは1より大きい整数であり、

選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応する、モーメンタム値の第1のセットを前記メモリから取り出すステップと、

前記選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応する、モーメンタム値の第2のセットを前記メモリから取り出すステップと、

前記選択された記憶フォーマットを有するモーメンタム値の前記第1のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第3のセットに変換するステップと、

前記選択された記憶フォーマットを有するモーメンタム値の前記第2のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第4のセットに変換するステップと、

前記勾配オプティマイザを用いて、モーメンタム値の前記第3のセットおよびモーメンタム値の前記第4のセットを使用して勾配最適化を実行するステップと、

を含み、

勾配最適化の次の反復のためのモーメンタム値の第5のセットおよびモーメンタム値の第6のセットを生成するステップと、モーメンタム値の前記第5のセットおよびモーメンタム値の前記第6のセットのそれぞれを記憶する前に、それぞれのモーメンタム値のそれぞれに関連する符号ビットおよび7つの最上位ビットのみを記憶することによってモーメンタム値の前記第5のセットおよびモーメンタム値の前記第6のセットのそれぞれを前記記憶フォーマットへ変換するステップと、

をさらに含む、方法。 - 勾配最適化を実行するステップは、アダプティブモーメンタム推定アルゴリズムを実装するステップを含む、

請求項1に記載の方法。 - 前記勾配オプティマイザは、フィールドプログラマブルゲートアレイ(FPGA)を使用して実装される、

請求項6に記載の方法。 - 勾配オプティマイザを含むシステムであって、

L層を含むニューラルネットワークモデルに関連するモーメンタム値を記憶するように構成されたメモリを含み、Lは1より大きい整数であり、

選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応する、モーメンタム値の第1のセットを前記メモリから取り出し、

前記選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応する、モーメンタム値の第2のセットを前記メモリから取り出し、

前記選択された記憶フォーマットを有するモーメンタム値の前記第1のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第3のセットに変換し、

前記選択された記憶フォーマットを有するモーメンタム値の前記第2のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第4のセットに変換し、

前記勾配オプティマイザを使用して、モーメンタム値の前記第3のセットとモーメンタム値の前記第4のセットを用いて勾配最適化を実行する、

ように構成され、前記勾配オプティマイザは、連続するバーストサイクルが前記勾配オプティマイザを通る勾配のストリーミングをもたらすように、バーストモードで動作するように構成される、

記載のシステム。 - 前記選択された記憶フォーマットは、縮小単精度フォーマットを含む、

請求項8に記載のシステム。 - 勾配オプティマイザを含むシステムであって、

L層を含むニューラルネットワークモデルに関連するモーメンタム値を記憶するように構成されたメモリを含み、Lは1より大きい整数であり、

選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応する、モーメンタム値の第1のセットを前記メモリから取り出し、

前記選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応する、モーメンタム値の第2のセットを前記メモリから取り出し、

前記選択された記憶フォーマットを有するモーメンタム値の前記第1のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第3のセットに変換し、

前記選択された記憶フォーマットを有するモーメンタム値の前記第2のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第4のセットに変換し、

前記勾配オプティマイザを使用して、モーメンタム値の前記第3のセットとモーメンタム値の前記第4のセットを用いて勾配最適化を実行する、

ように構成され、

前記訓練フォーマットは、単精度フォーマットまたは倍精度フォーマットを含み、

単精度フォーマットのモーメンタム値または倍精度フォーマットのモーメンタム値を形成するために、余分なゼロビットをパディングするようにさらに構成される、

システム。 - 勾配オプティマイザを含むシステムであって、

L層を含むニューラルネットワークモデルに関連するモーメンタム値を記憶するように構成されたメモリを含み、Lは1より大きい整数であり、

選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応する、モーメンタム値の第1のセットを前記メモリから取り出し、

前記選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応する、モーメンタム値の第2のセットを前記メモリから取り出し、

前記選択された記憶フォーマットを有するモーメンタム値の前記第1のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第3のセットに変換し、

前記選択された記憶フォーマットを有するモーメンタム値の前記第2のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第4のセットに変換し、

前記勾配オプティマイザを使用して、モーメンタム値の前記第3のセットとモーメンタム値の前記第4のセットを用いて勾配最適化を実行する、

ように構成され、

勾配最適化の次の反復のためのモーメンタム値の第5のセットおよびモーメンタム値の第6のセットを生成し、モーメンタム値の前記第5のセットおよびモーメンタム値の前記第6のセットのそれぞれを記憶する前に、それぞれのモーメンタム値のそれぞれに関連する符号ビットおよび7つの最上位ビットのみを記憶することによってモーメンタム値の前記第5のセットおよびモーメンタム値の前記第6のセットのそれぞれを前記記憶フォーマットへ変換する、ようにさらに構成される、

システム。 - アダプティブモーメンタム推定アルゴリズムを実装するように構成される、

請求項8に記載のシステム。 - 前記勾配オプティマイザは、フィールドプログラマブルゲートアレイ(FPGA)を使用して実装される、

請求項8に記載のシステム。 - 勾配オプティマイザと、L層を含むニューラルネットワークモデルに関連する重みおよびモーメンタム値を記憶するように構成されたメモリと、を含むシステムにおける方法であって、Lは1より大きい整数であり、

選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応するモーメンタム値の第1のセットを前記メモリから取り出すステップと、

前記選択された記憶フォーマットを有する、前記ニューラルネットワークモデルの層に対応するモーメンタム値の第2のセットを前記メモリから取り出すステップと、

前記選択された記憶フォーマットを有するモーメンタム値の前記第1のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第3のセットに変換するステップと、

前記選択された記憶フォーマットを有するモーメンタム値の前記第2のセットを、前記勾配オプティマイザに関連付けられた訓練フォーマットを有するモーメンタム値の第4のセットに変換するステップと、

前記勾配オプティマイザを用いて、モーメンタム値の前記第3のセットおよびモーメンタム値の前記第4のセットを使用して勾配最適化を実行するステップと、

勾配最適化の次の反復のためのモーメンタム値の第5のセットおよびモーメンタム値の第6のセットを生成するステップと、

符号ビットのみを記憶し、モーメンタム値の前記第5のセットの仮数に関連する所定の数のビットを切り捨てることによって、モーメンタム値の前記第5のセットを、前記記憶フォーマットを有するモーメンタム値の第7のセットに変換するステップと、

符号ビットのみを記憶し、モーメンタム値の前記第6のセットの仮数に関連する所定の数のビットを切り捨てることによって、モーメンタム値の前記第6のセットを、前記記憶フォーマットを有するモーメンタム値の第8のセットに変換するステップと、

を含む、方法。 - 前記勾配オプティマイザは、連続するバーストサイクルが前記勾配オプティマイザを通る勾配のストリーミングをもたらすように、バーストモードで動作するように構成される、

請求項14に記載の方法。 - 前記選択された記憶フォーマットは、縮小単精度(reduced single precision)フォーマットを含む、

請求項14または15に記載の方法。 - 前記訓練フォーマットは、単精度フォーマットまたは倍精度(double precision)フォーマットを含む、

請求項14または15記載の方法。 - 勾配最適化を実行するステップは、アダプティブモーメンタム推定アルゴリズムを実装するステップを含む、

請求項14または15に記載の方法。 - 前記訓練フォーマットは、32ビット浮動小数点フォーマットを含み、前記記憶フォーマットは、8ビット浮動小数点フォーマットを含む、

請求項14または15に記載の方法。 - 前記勾配オプティマイザは、フィールドプログラマブルゲートアレイ(FPGA)を使用して実装される、

請求項14または15に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US16/851,847 US11651228B2 (en) | 2020-04-17 | 2020-04-17 | Dual-momentum gradient optimization with reduced memory requirements |

| US16/851,847 | 2020-04-17 | ||

| PCT/US2021/017215 WO2021211193A1 (en) | 2020-04-17 | 2021-02-09 | Dual-momentum gradient optimization with reduced memory requirements |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2023521975A JP2023521975A (ja) | 2023-05-26 |

| JP7623398B2 true JP7623398B2 (ja) | 2025-01-28 |

Family

ID=74856929

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022561510A Active JP7623398B2 (ja) | 2020-04-17 | 2021-02-09 | メモリ要件が低減されたデュアルモーメンタム勾配最適化 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US11651228B2 (ja) |

| EP (1) | EP4136587A1 (ja) |

| JP (1) | JP7623398B2 (ja) |

| KR (1) | KR102856047B1 (ja) |

| CN (1) | CN115398449A (ja) |

| WO (1) | WO2021211193A1 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2023110297A (ja) * | 2022-01-28 | 2023-08-09 | 国立大学法人北海道大学 | 最適化装置及び最適化方法並びに最適化用プログラム |

| CN116007597B (zh) * | 2022-12-19 | 2024-06-11 | 北京工业大学 | 基于动量梯度下降法对框架柱的垂直度测量方法及装置 |

| KR102842262B1 (ko) * | 2024-04-03 | 2025-08-04 | 울산과학기술원 | 정방행렬화 알고리즘을 이용한 메모리 효율적인 심층신경망 최적화 장치 및 방법 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20190034784A1 (en) | 2017-07-28 | 2019-01-31 | Beijing Deephi Intelligence Technology Co., Ltd. | Fixed-point training method for deep neural networks based on dynamic fixed-point conversion scheme |

| JP2019512126A (ja) | 2016-02-29 | 2019-05-09 | アリババ グループ ホウルディング リミテッド | 機械学習システムをトレーニングする方法及びシステム |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10572800B2 (en) | 2016-02-05 | 2020-02-25 | Nec Corporation | Accelerating deep neural network training with inconsistent stochastic gradient descent |

| US12299577B2 (en) * | 2016-06-15 | 2025-05-13 | Nvidia Corporation | Tensor processing using low precision format |

| US11276002B2 (en) | 2017-12-20 | 2022-03-15 | Salesforce.Com, Inc. | Hybrid training of deep networks |

| US10372991B1 (en) * | 2018-04-03 | 2019-08-06 | Google Llc | Systems and methods that leverage deep learning to selectively store audiovisual content |

| US11645493B2 (en) * | 2018-05-04 | 2023-05-09 | Microsoft Technology Licensing, Llc | Flow for quantized neural networks |

| KR102732517B1 (ko) * | 2018-07-04 | 2024-11-20 | 삼성전자주식회사 | 뉴럴 네트워크에서 파라미터를 처리하는 방법 및 장치 |

| US11586904B2 (en) * | 2018-09-13 | 2023-02-21 | Google Llc | Adaptive optimization with improved convergence |

| US20200380369A1 (en) * | 2019-05-31 | 2020-12-03 | Nvidia Corporation | Training a neural network using selective weight updates |

| US10769528B1 (en) * | 2019-06-07 | 2020-09-08 | Sas Institute Inc. | Deep learning model training system |

| KR20190098107A (ko) * | 2019-08-02 | 2019-08-21 | 엘지전자 주식회사 | 딥 러닝을 위한 신경망 학습 장치 및 그 방법 |

-

2020

- 2020-04-17 US US16/851,847 patent/US11651228B2/en active Active

-

2021

- 2021-02-09 CN CN202180028394.XA patent/CN115398449A/zh active Pending

- 2021-02-09 WO PCT/US2021/017215 patent/WO2021211193A1/en not_active Ceased

- 2021-02-09 KR KR1020227035854A patent/KR102856047B1/ko active Active

- 2021-02-09 JP JP2022561510A patent/JP7623398B2/ja active Active

- 2021-02-09 EP EP21709831.8A patent/EP4136587A1/en active Pending

-

2023

- 2023-04-11 US US18/298,791 patent/US20230244945A1/en active Pending

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019512126A (ja) | 2016-02-29 | 2019-05-09 | アリババ グループ ホウルディング リミテッド | 機械学習システムをトレーニングする方法及びシステム |

| US20190034784A1 (en) | 2017-07-28 | 2019-01-31 | Beijing Deephi Intelligence Technology Co., Ltd. | Fixed-point training method for deep neural networks based on dynamic fixed-point conversion scheme |

Non-Patent Citations (1)

| Title |

|---|

| Sebastian Ruder,An overview of gradient descent optimization algorithms,arxiv.org, [online],2017年06月15日,[検索日 2024.09.09], Retrieved from the Internet: <URL: https://arxiv.org/pdf/1609.04747> |

Also Published As

| Publication number | Publication date |

|---|---|

| US20210326711A1 (en) | 2021-10-21 |

| EP4136587A1 (en) | 2023-02-22 |

| KR102856047B1 (ko) | 2025-09-04 |

| US11651228B2 (en) | 2023-05-16 |

| JP2023521975A (ja) | 2023-05-26 |

| KR20230006815A (ko) | 2023-01-11 |

| WO2021211193A1 (en) | 2021-10-21 |

| US20230244945A1 (en) | 2023-08-03 |

| CN115398449A (zh) | 2022-11-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20230244945A1 (en) | Dual-momentum gradient optimization with reduced memory requirements | |

| US11663444B2 (en) | Pipelined neural network processing with continuous and asynchronous updates | |

| US20200082269A1 (en) | Memory efficient neural networks | |

| CN112836787B (zh) | 通过高效混合并行化减少深度神经网络训练次数 | |

| WO2020167480A1 (en) | Adjusting activation compression for neural network training | |

| WO2020142192A1 (en) | Neural network activation compression with narrow block floating-point | |

| US20170061279A1 (en) | Updating an artificial neural network using flexible fixed point representation | |

| CN113273082A (zh) | 具有异常块浮点的神经网络激活压缩 | |

| CN114626516A (zh) | 一种基于对数块浮点量化的神经网络加速系统 | |

| CN113508402A (zh) | 从量化的固件神经网络层得出一致的软件神经网络层 | |

| WO2020176250A1 (en) | Neural network layer processing with normalization and transformation of data | |

| WO2020176248A1 (en) | Neural network layer processing with scaled quantization | |

| CN119884332B (zh) | 一种应答信息生成方法、设备、介质及计算机程序产品 | |

| US20240220572A1 (en) | Pipeline-parallel-dataflow artificial intelligence system for accelerating self-attention computations | |

| US12353984B2 (en) | Hardware-assisted gradient optimization using streamed gradients | |

| CN119005265A (zh) | 面向高性能数据并行dnn训练的稀疏化压缩方法及装置 | |

| JP2024529835A (ja) | 二重指数バウンディングボックス浮動小数点プロセッサ | |

| EP4196919A1 (en) | Method and system for quantizing a neural network | |

| CN117808079A (zh) | 一种基于少学习参数的神经网络训练方法及装置 | |

| US20250377940A1 (en) | Hardware acceleration for generative models | |

| He et al. | Research on Efficient CNN Acceleration Through Mixed Precision Quantization: A Comprehensive Methodology. | |

| Huang et al. | A Data-Efficient Deep Reinforcement Learning Algorithm and FPGA Accelerator for Real-Time Robot Motion Control Applications | |

| Xu et al. | MERINDA: Model Recovery in FPGA-Based Dynamic Architecture for Edge and Physical AI | |

| JPWO2023003639A5 (ja) | ||

| CN121523860A (zh) | 一种基于多gpu编码的共现矩阵构建方法、设备及介质 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20240125 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240917 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20241206 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20241217 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20250116 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7623398 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D02 |