JP7586895B2 - メモリー・アパーチャのフラッシュ・オーダーを使用したデーター保存 - Google Patents

メモリー・アパーチャのフラッシュ・オーダーを使用したデーター保存 Download PDFInfo

- Publication number

- JP7586895B2 JP7586895B2 JP2022511208A JP2022511208A JP7586895B2 JP 7586895 B2 JP7586895 B2 JP 7586895B2 JP 2022511208 A JP2022511208 A JP 2022511208A JP 2022511208 A JP2022511208 A JP 2022511208A JP 7586895 B2 JP7586895 B2 JP 7586895B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- aperture

- memory

- physical address

- storage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/023—Free address space management

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0866—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches for peripheral storage systems, e.g. disk cache

- G06F12/0868—Data transfer between cache memory and other subsystems, e.g. storage devices or host systems

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/0614—Improving the reliability of storage systems

- G06F3/0619—Improving the reliability of storage systems in relation to data integrity, e.g. data losses, bit errors

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/062—Securing storage systems

- G06F3/0622—Securing storage systems in relation to access

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0638—Organizing or formatting or addressing of data

- G06F3/064—Management of blocks

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0638—Organizing or formatting or addressing of data

- G06F3/0644—Management of space entities, e.g. partitions, extents, pools

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0673—Single storage device

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/455—Emulation; Interpretation; Software simulation, e.g. virtualisation or emulation of application or operating system execution engines

- G06F9/45533—Hypervisors; Virtual machine monitors

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/50—Allocation of resources, e.g. of the central processing unit [CPU]

- G06F9/5005—Allocation of resources, e.g. of the central processing unit [CPU] to service a request

- G06F9/5011—Allocation of resources, e.g. of the central processing unit [CPU] to service a request the resources being hardware resources other than CPUs, Servers and Terminals

- G06F9/5016—Allocation of resources, e.g. of the central processing unit [CPU] to service a request the resources being hardware resources other than CPUs, Servers and Terminals the resource being the memory

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/10—Providing a specific technical effect

- G06F2212/1032—Reliability improvement, data loss prevention, degraded operation etc

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/15—Use in a specific computing environment

- G06F2212/152—Virtualized environment, e.g. logically partitioned system

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/20—Employing a main memory using a specific memory technology

- G06F2212/202—Non-volatile memory

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/22—Employing cache memory using specific memory technology

- G06F2212/222—Non-volatile memory

- G06F2212/2228—Battery-backed RAM

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/26—Using a specific storage system architecture

- G06F2212/263—Network storage, e.g. SAN or NAS

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/31—Providing disk cache in a specific location of a storage system

- G06F2212/314—In storage network, e.g. network attached cache

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Software Systems (AREA)

- Human Computer Interaction (AREA)

- Computer Security & Cryptography (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

Description

(a)データー集合A-データーをアパーチャに格納する要求を受けるステップ。A-データーはクリティカル・データーと指定されたデーターを含む。(b)アパーチャの未割り当てメモリーの一部分A-メモリーを識別するステップ。A-メモリーはA-データーを保持できるだけ十分に大きく、A-メモリーは、アパーチャの他のいずれの未割り当てメモリーの他のいずれのアドレスよりもアパーチャのフラッシュ先端に近いアドレスを有する。(c)A-メモリーに割り当て済みの印を付け、A-データーのコピーをA-メモリーに入力するステップ。これらのステップ(a)~(c)は、クリティカル・データーを収容するそれぞれの異なるデーター集合の分だけ、複数回繰り返すことができる。

(d)データー集合Z-データーをアパーチャに格納する要求を受けるステップ。Z-データーは、クリティカル・データーに指定されたデーターを全く含まない。(e)アパーチャの未割り当てメモリーの一部分Z-メモリーを識別するステップ。Z-メモリーはZ-データーを保持できるだけ十分に大きく、Z-メモリーは、アパーチャの他のいずれの未割り当てメモリーの他いずれのアドレスよりもアパーチャのフラッシュ後端に近いアドレスを有する。(f)Z-メモリーに割り当て済みの印を付け、Z-データーのコピーをZ-メモリーに入力するステップ。これらのステップ(d)~(f)は、クリティカル・データーを収容しないそれぞれの異なるデーター集合の分だけ繰り返すことができ、クリティカル・データーだけが格納されているときは省略してもよい。

[0025] 技術革新はそれらの原点を超えて拡大することができるが、技術革新の 原点を理解すると、一層深くその技術革新の真意を認めるのに役立つことができる。本願の場合、本明細書において説明する教示は、機械学習用のビッグ・データーを格納するという技術的課題が動機となった。もののインターネット・デバイスは、データーを大量にそして高速(rapid rate)で産出し(pump out)、機械学習ツールおよび技法は、このデーターの洪水を有益な方法で処理できる場合もある。ある機械学習データーベースは、何百万ものレコードを実際のデーターベース内に含み、したがって高い読み取り速度が重要となる。大量のデーターが関与するにも拘わらず、個々のデーターに対する不正な意図的変更は望ましくないという意味、そしてリブートまたは予期されない停電によって起こるデーター変化は望ましくないという意味の双方で、データーの完全性も重要である。

[0032] 本明細書において説明する実施形態の技術的特長は、当業者には明白であろう。そして、広い範囲の注意深い読者にも幾通りもの方法で明白になるであろう。ある実施形態は、メモリー割り当て、揮発性ストレージから不揮発性ストレージへのデーターのフラッシュ、バッテリー特性に基づくメモリー・アパーチャのサイズ決定またはサイズ決定し直し、およびメモリーのディフラッギングというような、各々、コンピューティング技術に深く根付いた技術的活動に取り組む。論ずる技術的メカニズムの一部には、例えば、NVDIMMまたは他のバッテリー・バックアップ・メモリー、統一拡張可能ファームウェア・インターフェース(Unified Extensible Firmware Interface)、計算ノード、ストレージ・ノード、メモリー・マップ、フラッシュ・オーダー、および仮想機械が含まれる。論ずる技術的効果の一部には、例えば、クリティカル・データーが完全性の脅威に対抗して保存される可能性を高めること、データー保存を行うためのデーター冗長性依拠を減らすこと、バッテリー特性および非クリティカル・データーのために確保するメモリー量というような判断基準を考慮してバッテリー・バックアップ・メモリーのアパーチャのサイズを効率的に決定することが含まれる。つまり、純粋に心理的なプロセスは、明確に除外される。ある実施形態は、NVDIMMコスト、カスタマー・サービス品質保証要件、およびデーター冗長性のためのノード・ストレージの可用性というような判断基準の均衡を取りながら、完全性の脅威に対抗してデーターを保存することによって、コンピューティング・システムおよびサービスの機能(functioning)を改善する。本教示の技術特性に基づく他の利点も、提示する説明から、当業者には明白になるであろう。

[0034] 一部の頭字語、省略、名称、および記号について、以下に定義する。他のものは、本明細書の他の場所で定義されるか、または当業者が理解するために本明細書における定義が必要ないものである。

[0036] ALU:算術演算および論理ユニット

[0037] API:アプリケーション・プログラム・インターフェース

[0038] BIOS:基本入力/出力システム

[0039] BMC:ベースボード管理コントローラ

[0040] CD:コンパクト・ディスク

[0041] CPU:中央処理ユニット

[0042] EFI:拡張可能ファームウェア・インターフェース

[0043] DRAM:ダイナミック・ランダム・アクセス・メモリー

[0044] DVD:ディジタル・バーサタイル・ディスクまたはディジタル・ビデオ・ディスク

[0045] FPGA:フィールド・プログラマブル・ゲート・アレイ

[0046] FPU:浮動小数点処理ユニット

[0047] GPU:グラフィカル処理ユニット

[0048] GUI:グラフィカル・ユーザー・インターフェース

[0049] HDD:ハード・ディスク・ドライブ(例えば、ソリッド・ステート、電気機械、光学)

[0050] IaaSまたはIAAS:サービスとしてのインフラストラクチャ

[0051] ID:識別または識別情報(identity)

[0052] IoT:もののインターネット

[0053] LA N:ローカル・エリア・ネットワーク

[0054] N V D I M M:不揮発性デュアル・インライン・メモリー・モジュール

[0055] N V M e:不揮発性メモリー・エクスプレス

[0056] O S:オペレーティング・システム

[0057] P a a SまたはP A A S:サービスとしてのプラットフォーム

[0058] R A M:ランダム・アクセス・メモリー

[0059] R O M:リード・オンリー・メモリー

[0060] S A T A:シリアルA T A(コンピューター・バス・インターフェース)

[0061] S L A:サービス品質保証

[0062] S M M:システム管理モード

[0063] T C P/I P:送信制御プロトコル/インターネット・プロトコル

[0064] U E F I:統一拡張可能ファームウェア・インターフェース

[0065] V M:仮想機械

[0066] W A N:ワイド・エリア・ネットワーク

[0067] いくつかの追加の用語

[00100] 以下のリストは、便利であるように、そして図面の支援のために提示され、複数の項目を参照して技術革新を説明する明細書の本文の一部として提示されるものである。ここのリストに掲示されない項目も、しかしながら、所与の実施形態の一部であってもよい。本文を読みやすくするために、所与の参照番号は、本文において参照される項目の、全てではないが一部の記載の近くに記載される。同じ参照番号が、所与の項目の異なる例または異なる実例を参照するために使用される場合もある。参照番号のリストは次の通りである。

[00102] 102 計算システムまたはコンピューティング・システムとも呼ばれるコンピューター・システム

[00103] 104 ユーザー

[00104] 106 周辺機器

[00105] 108 例えば、LAN、WAN、ソフトウェア定義ネットワーク、クラウド、および他の有線またはワイヤレス・ネットワークを含むネットワーク全体

[00106] 110 プロセッサー

[00107] 112 コンピューター読み取り

可能記憶媒体、例えば、RAM、ハード・ディスク。

[00109] 116 プロセッサーによって実行可能な命令であって、リムーバブル記憶媒体上または他のメモリー(揮発性または不揮発性または双方)内に常駐することができる。

[00111] 120 カーネル(1つまたは複数)、例えば、オペレーティング・システム(1つまたは複数)、BIOS、UEFI、デバイス・ドライバー

[00112] 122 ツール、例えば、ウィルス予防ソフトウェア、ファイアウォール、パケット・スニファー・ソフトウェア、侵入検出システム、侵入防止システム、デバッガー、プロファイラー、コンパイラー、インタプリター、デコンパイラー、アセンブラー、ディスアセンブラー、ソース・コード・エディター、自動完了ソフトウェア、シミュレーター、ファザー(fuzzer)、レポジトリー・アクセス・ツール、バージョン制御ツール、オプティマイザー、協働ツール、ソフトウェア開発ツールおよびツール・スイート、ハードウェア開発ツールおよびツール・スイート、診断等。

[00114] 126 表示画面 。「ディスプレイ」とも呼ぶ。

[00117] 202 計算ノード。

[00118] 204 データー・ソース、例えば、データーを出力するまたそうでなければ生成するプログラム。

[00121] 210 例えば、ストレージ・ノードにおける格納機能。

[00123] 214 不揮発性ストレージ、例えば、NVDIMM、ディスク、フラッシュ・メモリー。

[00125] 218 バッテリー・バックアップ・メモリー

[00126] 220 メモリー・アパーチャ。物理デバイスにおけるディジタル・データー格納位置と関連付けられた物理アドレス空間の一部分を指すことができ、またはディジタル・データー格納位置自体を指すこともできる。

[00128] 224 データー格納要求に対する応答

[00129] 226 データーの複製

[00130] 300 コンピューティング環境の態様

[00131] 302 クラウド。「クラウド・コンピューティング環境」と呼んでもよい。

[00134] 308 ハイパーバイザー。

[00137] 314 データー完全性の脅威

[00138] 316 2つ以上のノード間におけるストレージ関係

[00139] 318 データー・クリティカル性。データーがクリティカルに指定されているか否かに言及することができ、またはデーターが未だそのように指定されていなくても、クリティカルに指定される判断基準を満たすか否かに言及することができる。これは、ブーリアンまたは他の指示、例えば、データーのフラッシングにどのように優先順位を付けるかを示す2つ以上の値の範囲内にある値であってもよい。

[00141] 404 NVDIMM

[00142] 406 バッテリー特性

[00143] 408 ディフラッガー(defragger)(メモリー・ディフラグメンテーション)コード。

[00145] 412 クリティカル・データーを含むデーター集合(いくらかの非クリティカル・データーも有してもよい)。

[00147] 416 クリティカル・データーを全く含まないデーター集合。

[00149] 420 ファームウェア。

[00153] 504 信頼性値、例えば、平均故障間隔、または残存予測寿命、または列挙値(例えば、10が最良で0が最悪である目盛の中の2)、または信頼性等級(例えば、中度の信頼性)。

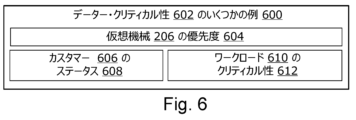

[00155] 600 データー・クリティカル性判断基準の例。

[00157] 604 データーを生成した仮想機械に割り当てられる優先度。

[00158] 606 カスタマー、例えば、クラウドのテナント。

[00160] 610 ワークロード、たとえば、特定の計算ノードに割り当てられる処理タスク。

[00162] 702 物理機械、例えば、プロセッサー、回路、チップ、バッテリー、ディスプレイ、電源、筐体等。あらゆる埋め込みファームウェア、または物理機械の不揮発性メモリーに格納されたソフトウェアを含む。コンピューティング・システム102は、1つ以上の物理機械702を含む。

[00164] 706 コンテナ。例えば、ユーザー空間仮想化を行う(provide)コンピューティング構造(construct)であり、それ自体はオペレーティング・システムを含まないが、それにもかかわらず、オペレーティング・システムに依存して実行する。

[00168] 806 アパーチャのフラッシュ先端。

[00169] 808 アパーチャのフラッシュ後端。

[00171] 812 同じメモリー・デバイス内であるがアパーチャの外側にあるメモリーの部分。

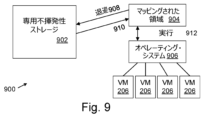

[00173] 900 仮想機械を実行するオペレーティング・システムまたはコンテナを有するシステムを含み、本明細書において教示するようなデーター保存機能が装備されコンピューティング・システム。

[00175] 904 専用ストレージ902にマッピングされるメモリー領域。バッテリー・バックアップ・メモリー・アパーチャ220は、領域904の一例である。

[00177] 908 揮発性メモリーから、この揮発性メモリーをバックアップする専用不揮発性ストレージにデーターをコピーする退避動作。退避は、退避されるデーターの完全性に対する差し迫った脅威を全く伴わずに、意図的に行うことができ、または差し迫った脅威または発生している(current)脅威に応答して行われるフラッシュであってもよい。

[00179] 912 プログラムの実行。プログラムを実行するアクト、またはプログラム動作のインスタンスを指すこともできる。

[00184] 1008 例えば、memcpy()によって使用される機能、ブロック・コピー等を実行することによって、データーのコピーをメモリー内に入力する。

[00189] 1104 データー格納要求を受ける。

[00191] 1108 例えば、バイトまたはブロックを単位としたアパーチャ220のサイズ。

[00193] 1112 データー格納要求を送る。

[00195] 1115 アパーチャを移動させる。

[00196] 1116 非クリティカル・データーのみを保持するために、アパーチャの少なくとも指定された部分を予約する。

[00198] 1120 データーをコピーする、またはデーターを移動させる、または以前には割り当てられていなかったメモリーにデーターを挿入することによって、アパーチャの少なくとも一部分をディフラグすることによって、未割り当てであるメモリーの量を削減する、またはアパーチャのフラッシュ先端からの未割り当てメモリーの距離を延長する、または双方を行う。例えば、これを、同じユーザーまたは同じプロセスまたは同じファイルに属するメモリーの部分を統合することを伴う、別の「ディフラグ」の使用から区別するために、これを「フラッシュ・ディフラグ」と呼んでもよい。

[00201] 1126 アパーチャ外部、そしてアパーチャがフラッシュされる不揮発性ストレージ外部のどこかに、データーのコピーを保持する。

[00203] 1130 空間を作る、即ち、メモリーの所与の部分を割り当て済みから空きに変更する。

[00206] 1136 割り当て部分間にある未割り当て空間を消滅させる。

[00207] 1138 脅威に対抗してクリティカル・データーを保存する可能性を高める。

[00209] 1142 ファームウェアを実行する。実行912の一例。

[00211] 動作環境

[00212] 図1を参照すると、実施形態の動作環境100は、少なくとも1つのコンピューター・システム102を含む。コンピューター・システム102は、マルチプロセッサー・コンピューター・システムであっても、またはなくてもよい。動作環境は、所与のコンピューター・システム内に1つ以上の機械を含むことができ、これらはクラスター化されても、クライアント-サーバー関係でネットワーク接続されても、および/またはクラウド内においてピア・ツー・ピアの形態でネットワーク接続されてもよい。個々の機械はコンピューター・システムであり、協働する機械のグループもコンピューター・システムである。所与のコンピューター・システム102が、例えば、アプリケーションを用いて、エンド・ユーザーのために構成されても、アドミニストレーターのためにサーバーとして構成されても、分散型処理ノードとして構成されても、および/または他の方法で構成されてもよい。

[00223] 図1から図11までを参照すると、ある実施形態は機能増強システム800または900を使用もしくは提供する。機能増強は、動作ステップとデバイス特性との組み合わせを実装して完全性の脅威314に対抗してデーターを保存することによって、データー保存を促進する(promote)のに役立つ。データー118は、クリティカル・データー412および非クリティカル・データー416に分割され、クリティカル・データーは1つ以上のバッテリー・バックアップ・メモリー218のアパーチャ220内の物理アドレス424に格納され、脅威が検出されたとき(1010)に非クリティカル・データーよりも先に、クリティカル・データーがフラッシュされる(1012)。バッテリー・バックアップ・メモリー・アパーチャ220は、バッテリーの特性406にしたがってサイズが決定され、条件が変化するに連れてサイズを変更することができる。ディフラガー(defragger)408は、クリティカル・データー412を格納するためのアパーチャの使用を最適化する。

[00231] 図4は、革新的なデーター保存機能をコンピューティング・システム102に付加することができるデーター保存サブシステムの一例306を示す。サブシステム306のメモリーは、バッテリー・バックアップ・メモリー218、例えば、NVDIMM404においてアパーチャ220を含む。図4および図5において気付かれるように、バッテリーは、容量502、信頼性504、および経年数506の内1つ以上というような、追跡または指示対象となる特性406を有することができる。これらのバッテリー特性406は、互いに重複する、即ち、互いに影響を及ぼし合うこともある。例えば、信頼性は経年数と共に低下するとして差し支えない。また、サブシステム306は、バッテリー216によってバックアップされない揮発性メモリー402も含むことができる。

[00235] ある実施形態は、コンピューティング・システム102においてデーター保存サブシステム306を提供または使用する。データー保存サブシステム306は、アパーチャ220を有するバッテリー・バックアップ・メモリー218を含むことができる。アパーチャ220は、フラッシュ・オーダー312を有する。フラッシュ・オーダー312は、データー完全性の脅威314に応答して、データーをアパーチャからアパーチャ関連不揮発性ストレージ902にコピーする順序(order)である。フラッシュ・オーダーは、アパーチャのフラッシュ先端806と、アパーチャのフラッシュ後端808とを定める。

(d)データー集合Z-データー416をアパーチャに格納する要求222を受ける。Z-データーは、クリティカル・データーに指定されるデーターを全く含まない。

ここで、ラベル(a)から(f)までは、単に識別子として役割を果たすに過ぎず、したがって必ずしもこれら自体が動作の順序を指定する訳ではない。このデーター保存サブシステム306は、フラッシュ-オーダーにおいてクリティカル・データーを非クリティカル・データーよりも前にバッテリー・バックアップ・メモリーに入力することによって、クリティカル・データーをフラッシュするのに成功し(1012)、それによってクリティカル・データーを保存する可能性を高める。クリティカル・データー保存の可能性は、データーのクリティカル性を考慮せずに、即ち、クリティカル性を欠いて、バッテリー・バックアップ・メモリーにデーターを格納するアーキテクチャにおけるよりも高い。

[00246] 図10は、本明細書において教示するデーター保存機能を有し、図1から図9までの1つ以上によって示される増強システムによって実行または補佐することができる方法の一例である、方法1000を示す。図10に示す受けるステップ1002、特定するステップ1004、印を付けるステップ1006、入力するステップ1008、検出するステップ1010、およびフラッシュするステップ1012について、本開示全体を通じて、これらの参照番号で明示的に引用しながら、そして引用せずに説明する。具体的には、図2、図8、および図9の論述は、図10に示すステップ1002から1012までに関係がある。

[00262] ある実施形態は、構成コンピューター読み取り可能記憶媒体112を含む。記憶媒体112は、ディスク(磁気、光、またはこれら以外)、RAM、EEPROMS、または他のROM、および/または具体的にはコンピューター読み取り可能記憶媒体(単なる伝搬信号ではない)を含む、他の構成可能なメモリーを含むことができる。構成された記憶媒体とは、具体的に、CD、DVD、またはフラッシュ・メモリーのような、リムーバブル記憶媒体114としてもよい。リムーバブルであってもなくてもよく、揮発性であってもなくてもよい汎用メモリーは、アロケーター422、ディフラガー408、およびマッピング814というような品目を使用して、データー118および命令116の形態で構成して、実施形態にすることができる。データー118および命令116は、構成記憶媒体を形成するために、リムーバブル記憶媒体114および/またはネットワーク接続のような他のソースから読み取られる。構成記憶媒体112は、コンピューター・システム102に、本明細書において開示した通りに、データー保存のための技術的プロセス・ステップを実行させることができる。このため、図は、構成記憶媒体の実施形態およびプロセス(別名、方法)の実施形態、ならびにシステムおよびプロセスの実施形態を例示するのに役立つ。具体的には、図9、図10、または図11において示したプロセス・ステップ、もしくは本明細書において教示したプロセス・ステップはいずれも、記憶媒体を構成し、構成記憶媒体の実施形態を形成するために使用することができる。

[00272] 尚、本開示のあらゆる部分、またはその中のあらゆる特定の詳細が、実施可能性、書面による説明、または最良の態様というような、法的判断基準を必ずしも満たす必要はないことは、当業者には認められよう。また、実施形態は、特定のネットワーク、プロトコル、ツール、識別子、フィールド、データー構造、関数、秘密または他の証明(secrets or other proofs)、あるいは本明細書において説明した他の実施態様の選択肢には限定されない。他のいずれの特許開示との明らかな矛盾は、本技術革新の所有者からであっても、本特許開示において提示される請求項を解釈するには全く役には立たない。これは本開示の全ての部分に関係することを理解した上で、いくつかの追加の例および観察事項を提供する。

[00285] コード、データー構造、ロジック、コンポーネント、通信、および/またはそれらの機能的同等物のこれらの組み合わせの内任意のものを、以上で説明したシステムおよびそれらの変形(variation)の内任意のものと組み合わせることもできる。プロセスは、本明細書において説明した任意のステップを、動作可能な任意の部分集合または組み合わせまたはシーケンスに含めることもできる。各異形(variant)は、単独で、または他の異形の任意の1つ以上との組み合わせで行われてもよい。各異形は、前述のプロセスの内任意のものとともに行われてもよく、各プロセスは、他のプロセスの任意の1つ以上と組み合わせることもできる。各プロセスまたはプロセスの組み合わせは、異形を含んで、以上で説明した構成記憶媒体の組み合わせおよび異形の内任意のものと組み合わせることもできる。

[00287] 端的に言うと、本明細書において提示した教示は、コンピューティング・システムにおいてデーター保存機能を強化する(enhance)ために適用することができる。ある実施形態では、動作ステップとデバイス特性とを組み合わせることによって、完全性の脅威314に対抗してデーター118を保存し易くする。データー118は、カスタマー606の要求608、ワークロード610のクリティカル性612、または仮想機械206のクリティカル性604というような判断基準602に基づいて、クリティカル・データー412および非クリティカル・データー416に分割される。データー118は、計算ノード202において生成し、例えば、ストレージ・ノード212における格納のために送る(222)ことができる。クリティカル・データー412は、バッテリー・バックアップ・メモリー218のアパーチャ220において、物理アドレス424に格納され、ここから、フラッシュ・オーダー312にしたがって非クリティカル・データー416よりも前にフラッシュされる(1012)。フラッシュ・オーダー312は、バッテリー・バックアップ・メモリーの回路によって課せられ(impose)、または外部の力、例えば、システム・ファームウェア420によってバッテリー・バックアップ・メモリーに課せられる。フラッシュ・オーダー312は、例えば、ボトムアップNVDIMM404のフラッシュ・オーダーでもよい。複製されたコピーを保存する(1102)ためにそれをフラッシュする(1012)のに間に合わなかった場合、データー118の冗長コピー226(特に、非クリティカル・データー416)も保持する(1126)ことがでいる。バッテリー・バックアップ・メモリーのアパーチャ220は、バッテリーの特性406にしたがって、大きさが決められ(1106)そして配置され(1106)、条件が変化するに連れて、配置換え(1115)または大きさの決め直し(1114)を行うこともできる。フラッシュ・ディフラッギング1120は、特に、クリティカル・データー412を保持するアパーチャの部分414内において、アパーチャ220の使用を最適化するために行われる。

[00297] 提出された全ての請求項および要約書は、明細書の一部である。

Claims (20)

- コンピューティング・システムにおけるデーター保存サブシステムであって、

アパーチャを有するバッテリー・バックアップ・メモリーであって、前記メモリーは物理アドレス空間においてアドレスされるデジタル・データー格納位置を含み、前記アパーチャは前記デジタル・データー格納位置の少なくとも一部分を含み、前記アパーチャは物理アドレスのフラッシュ・オーダーを有し、前記物理アドレスのフラッシュ・オーダーは、データー完全性の脅威に応答して、前記アパーチャからアパーチャ関連不揮発性ストレージにデーターをコピーする順序であり、前記フラッシュ・オーダーは、前記アパーチャのフラッシュ先端物理アドレス(first-to-flush physical address end)および前記アパーチャのフラッシュ後端物理アドレス(last-to-flush physical address end)を定める、バッテリー・バックアップ・メモリーと、

前記バッテリー・バックアップ・メモリーと動作可能に通信するデーター保存回路であって、データー保存ステップを実行するように構成され、前記データー保存ステップは、

(a)データー集合A-データーを前記アパーチャに格納する要求を受けるステップであって、前記A-データーはクリティカル・データーと指定されたデーターを含む、ステップと、

(b)前記アパーチャの未割り当てメモリーの一部分A-メモリーを識別するステップであって、前記A-メモリーは前記A-データーを保持できるだけ十分に大きく、前記A-メモリーは、前記アパーチャの他のいずれの未割り当てメモリーの他のいずれの物理アドレスよりも前記アパーチャのフラッシュ先端物理アドレスに近い物理アドレスを有する、ステップと、

(c)前記A-メモリーに割り当て済みの印を付け、前記A-データーのコピーを前記A-メモリーに入力するステップと、

(d)データー集合Z-データーを前記アパーチャに格納する要求を受けるステップであって、前記Z-データーは、クリティカル・データーに指定されたデーターを全く含まない、ステップと、

(e)前記アパーチャの未割り当てメモリーの一部分Z-メモリーを識別するステップであって、前記Z-メモリーは前記Z-データーを保持できるだけ十分に大きく、前記Z-メモリーは前記アパーチャの他のいずれの未割り当てメモリーの他いずれの物理アドレスよりも前記アパーチャのフラッシュ後端物理アドレスに近い物理アドレスを有する、ステップと、

(f)前記Z-メモリーに割り当て済みの印を付け、前記Z-データーのコピーを前記Z-メモリーに入力するステップと

を含む、データー保存回路と

を備え、

データー・クリティカル性を考慮せずにデーターを前記バッテリー・バックアップ・メモリーに格納することによるよりも、クリティカル・データーをフラッシュするのに成功し、これによってそれを保存する可能性を高める、

データー保存サブシステム。 - 請求項1記載のデーター保存サブシステムにおいて、前記バッテリー・バックアップ・メモリー・アパーチャは、ネットワーク・ノードX内に常駐するか、または、前記ネットワーク・ノードXによって制御され、前記アパーチャにA-データーを格納する前記要求は、異なるネットワーク・ノードYから送られた、データー保存サブシステム。

- 請求項2記載のデーター保存サブシステムにおいて、前記ネットワーク・ノードXは、クラウドにおいてストレージ・ノードを含み、前記ネットワーク・ノードYは前記クラウドにおいて計算ノードを含む、データー保存サブシステム。

- 請求項2記載のデーター保存サブシステムにおいて、前記ネットワーク・ノードXおよび前記ネットワーク・ノードYは、ストレージ関係Rによって関係付けられ、MがNの代わりにデーターを格納するとき、2つのノードMおよびNがRによって関係付けられるように、Rが定められ、Rは、前記ネットワーク・ノードXおよび前記ネットワーク・ノードYの1対1の関係ではない、データー保存サブシステム。

- 請求項1記載のデーター保存サブシステムにおいて、前記バッテリー・バックアップ・メモリーはNVDIMMメモリーを含む、データー保存サブシステム。

- 請求項1記載のデーター保存サブシステムにおいて、前記コンピューティング・システムは仮想機械を備え、前記データー集合A-データーは前記データー保存サブシステムに仮想機械VM-Aから送られ、前記データー集合Z-データーは前記データー保存サブシステムに仮想機械VM-Zから送られる、データー保存サブシステム。

- コンピューティング・システムにおけるデーター保存方法であって、

データー集合A-データーをバッテリー・バックアップ・メモリーのアパーチャに格納する要求を受けるステップであって、前記メモリーは物理アドレス空間においてアドレスされるデジタル・データー格納位置を含み、前記アパーチャは前記デジタル・データー格納位置の少なくとも一部分を含み、前記アパーチャは物理アドレスのフラッシュ・オーダーを有し、前記物理アドレスのフラッシュ・オーダーは、データー完全性の脅威に応答して、前記アパーチャからアパーチャ関連不揮発性ストレージにデーターをコピーする順序であり、前記フラッシュ・オーダーは、前記アパーチャのフラッシュ先端物理アドレス(first-to-flush physical address end)および前記アパーチャのフラッシュ後端物理アドレス(last-to-flush physical address end)を定め、前記A-データーはクリティカル・データーと指定されたデーターを含む、ステップと、

前記アパーチャの未割り当てメモリーの一部分A-メモリーを識別するステップであって、前記A-メモリーは前記A-データーを保持できるだけ十分に大きく、前記A-メモリーは、前記アパーチャの他のいずれの未割り当てメモリーの他のいずれの物理アドレスよりも前記アパーチャのフラッシュ先端物理アドレスに近い物理アドレスを有する、ステップと、

前記A-メモリーに割り当て済みの印を付け、前記A-データーのコピーを前記A-メモリーに入力するステップと、

データー集合Z-データーを前記アパーチャに格納する要求を受けるステップであって、前記Z-データーは、クリティカル・データーに指定されたデーターを全く含まない、ステップと、

前記アパーチャの未割り当てメモリーの一部分Z-メモリーを識別するステップであって、前記Z-メモリーは前記Z-データーを保持できるだけ十分に大きく、前記Z-メモリーは前記アパーチャの他のいずれの未割り当てメモリーの他いずれの物理アドレスよりも前記アパーチャのフラッシュ後端物理アドレスに近い物理アドレスを有する、ステップと、

前記Z-メモリーに割り当て済みの印を付け、前記Z-データーのコピーを前記Z-メモリーに入力するステップと

を含み、

前記フラッシュ・オーダーにおいて前記クリティカル・データーを非クリティカル・データーよりも前に前記バッテリー・バックアップ・メモリーに入力することによって、クリティカル・データーをフラッシュするのに成功し、これによってそれを保存する可能性を高める、方法。 - 請求項7記載の方法であって、

少なくとも部分的に前記バッテリー・バックアップ・メモリーのバッテリー特性に基づいて前記アパーチャのサイズを決定するステップと、

少なくとも部分的に前記バッテリー・バックアップ・メモリーのバッテリー特性に基づいて、前記アパーチャの位置を決定するステップと、

少なくとも部分的に前記バッテリー・バックアップ・メモリーのバッテリー特性における変化に基づいて、前記アパーチャの大きさを決定し直すステップと、

少なくとも部分的に前記バッテリー・バックアップ・メモリーのバッテリー特性における変化に基づいて、前記アパーチャを移動させるステップと

のうちの少なくとも1つを更に含む方法。 - 請求項7記載の方法であって、前記アパーチャの少なくともディフラグ部分をフラッシュ・ディフラグするステップを更に含み、前記ディフラグ部分はクリティカル・データーを含む、方法。

- 請求項7記載の方法であって、ワークロードのクリティカル性、仮想機械優先度、または、カスタマー・ステータスという判断基準のうちの少なくとも1つに基づいて、前記A-データーの少なくとも一部分をクリティカル・データーに指定するステップを更に含む方法。

- 請求項7記載の方法であって、

前記データー完全性の脅威を検出するステップと、

前記クリティカル・データーの全てを前記アパーチャから前記アパーチャ関連不揮発性ストレージにフラッシュするステップと、

少なくとも一部の非クリティカル・データーを前記アパーチャから前記アパーチャ関連不揮発性ストレージにフラッシュし損なうステップと

を更に含む方法。 - 請求項7記載の方法であって、

前記データー完全性の脅威を検出するステップと、

前記クリティカル・データーの少なくとも全てを前記アパーチャから前記アパーチャ関連不揮発性ストレージにフラッシュするステップと、

その後、フラッシュした前記データーの全てを、前記アパーチャ関連不揮発性ストレージから、揮発性メモリーと、前記データーがフラッシュされた元である前記バッテリー・バックアップ・メモリーと、前記データーがフラッシュされた元である前記バッテリー・バックアップ・メモリーとは異なるバッテリー・バックアップ・メモリーとのうちの少なくとも1つに復元するステップと

を更に含む方法。 - 請求項7記載の方法であって、前記Z-データーの少なくとも1つのコピーを、前記アパーチャの外部および前記アパーチャ関連不揮発性ストレージの外部に保持するステップを更に含む方法。

- 請求項7記載の方法において、前記バッテリー・バックアップ・メモリーのアパーチャは、ここではMで示す物理機械内に常駐し、前記アパーチャに前記A-データーを格納する要求は、ここではNで示す異なる物理機械から送られた、方法。

- 請求項7記載の方法であって、前記A-データーを1つのストレージ・ノードのみに格納し、前記Z-データーのコピーを複数のストレージ・ノードに格納するステップを含む方法。

- データーおよび命令を含むよう構成されたコンピューター読み取り可能記憶媒体であって、前記命令は、実行されると、データー保存サブシステムに、コンピューティング・システムにおけるデーター保存のための方法を実行させ、前記方法は、

複数の要求を受けるステップであって、各要求は、それぞれのデーター集合のバッテリー・バックアップ・メモリーのアパーチャにおける格納を求め、前記メモリーは物理アドレス空間においてアドレスされるデジタル・データー格納位置を含み、前記アパーチャは前記デジタル・データー格納位置の少なくとも一部分を含み、前記アパーチャは物理アドレスのフラッシュ・オーダーを有し、前記物理アドレスのフラッシュ・オーダーは、データー完全性の脅威に応答して、前記アパーチャからアパーチャ関連不揮発性ストレージにデーターをコピーする順序であり、前記物理アドレスのフラッシュ・オーダーは、前記アパーチャのフラッシュ先端物理アドレス(first-to-flush physical address end)および前記アパーチャのフラッシュ後端物理アドレス(last-to-flush physical address end)を定め、それぞれのデーター集合の各々は、クリティカル・データーと指定されたデーターを含む、ステップと、

前記要求のうちの少なくとも2つについて、前記アパーチャの未割り当てメモリーのそれぞれの部分を識別するステップであって、未割り当てメモリーの各部分は、前記それぞれのデーター集合を保持できるだけ十分に大きく、未割り当てメモリーの識別された前記それぞれの部分は、前記アパーチャの他のいずれの未割り当てメモリーの他のいずれの物理アドレスよりも前記アパーチャのフラッシュ先端物理アドレスに近い物理アドレスを有する、ステップと、

前記要求のうちの少なくとも1つについて、未割り当てメモリーの識別された前記それぞれの部分に割り当て済みの印を付け、それに前記それぞれのデーター集合のコピーを入力するステップと、

前記データー完全性の脅威を検出するステップと、

前記アパーチャにコピーされた前記クリティカル・データーの全てを前記アパーチャから前記アパーチャ関連不揮発性ストレージにフラッシュするステップと

を含み、これによって、前記方法は、前記データー完全性の脅威にもかかわらず、前記アパーチャにコピーされた前記クリティカル・データーの全てを保存する、コンピューター読み取り可能記憶媒体。 - 請求項16に記載のコンピューター読み取り可能記憶媒体において、前記方法は、アパーチャ・サイズとアパーチャ・アドレスとのうちの少なくとも一方を特定するステップを更に含み、特定する前記ステップは、バッテリー容量と、バッテリーの経年数と、バッテリーの信頼性値とのうちの少なくとも1つに基づく、コンピューター読み取り可能記憶媒体。

- 請求項16に記載のコンピューター読み取り可能記憶媒体において、フラッシュする前記ステップは、統一拡張可能ファームウェア・インターフェースを有するファームウェアを実行するステップを含む、コンピューター読み取り可能記憶媒体。

- 請求項16に記載のコンピューター読み取り可能記憶媒体において、前記方法は、クリティカル・データーに指定されていないデーターを保持するために、前記アパーチャの少なくとも10パーセントを予約するステップを更に含む、コンピューター読み取り可能記憶媒体。

- 請求項16に記載のコンピューター読み取り可能記憶媒体において、前記方法は、

クリティカル・データーと指定されたデーターのための空間を作るために、クリティカル・データーと指定されていないデーターを、前記アパーチャ―の外部の格納位置に移動するステップと、

前記アパーチャの少なくとも一部分をディフラグし、これによって、前記アパーチャの2つの割り当て部分の間に位置していた未割り当て部分を削減するか又は消滅させるステップと

のうちの少なくとも1つを更に含む、コンピューター読み取り可能記憶媒体。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US16/546,337 US11113188B2 (en) | 2019-08-21 | 2019-08-21 | Data preservation using memory aperture flush order |

| US16/546,337 | 2019-08-21 | ||

| PCT/US2020/037681 WO2021034391A1 (en) | 2019-08-21 | 2020-06-15 | Data preservation using memory aperture flush order |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2022545012A JP2022545012A (ja) | 2022-10-24 |

| JPWO2021034391A5 JPWO2021034391A5 (ja) | 2023-06-21 |

| JP7586895B2 true JP7586895B2 (ja) | 2024-11-19 |

Family

ID=71409548

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022511208A Active JP7586895B2 (ja) | 2019-08-21 | 2020-06-15 | メモリー・アパーチャのフラッシュ・オーダーを使用したデーター保存 |

Country Status (13)

| Country | Link |

|---|---|

| US (1) | US11113188B2 (ja) |

| EP (1) | EP4018319B1 (ja) |

| JP (1) | JP7586895B2 (ja) |

| KR (1) | KR102879385B1 (ja) |

| CN (1) | CN114222975B (ja) |

| AU (1) | AU2020334772A1 (ja) |

| BR (1) | BR112022000200A2 (ja) |

| CA (1) | CA3147608A1 (ja) |

| IL (1) | IL290568A (ja) |

| MX (1) | MX2022002112A (ja) |

| PH (1) | PH12022550425A1 (ja) |

| WO (1) | WO2021034391A1 (ja) |

| ZA (1) | ZA202200837B (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI737189B (zh) * | 2019-02-23 | 2021-08-21 | 國立清華大學 | 易於從固態儲存裝置之故障中還原的方法、電腦系統,及固態儲存裝置 |

| US11720401B2 (en) * | 2020-03-27 | 2023-08-08 | Intel Corporation | Reclaiming and reusing pre-boot reserved memory post-boot |

| US11435920B2 (en) | 2021-01-20 | 2022-09-06 | Western Digital Technologies, Inc. | Storage system and method for using read and write buffers in a memory |

| US11983111B2 (en) | 2021-08-19 | 2024-05-14 | Microsoft Technology Licensing, Llc | Systems and methods to flush data in persistent memory region to non-volatile memory using auxiliary processor |

| US11842069B2 (en) | 2022-01-14 | 2023-12-12 | Western Digital Technologies, Inc. | Storage system and method for delaying flushing of a write buffer based on a host-provided threshold |

| US12298897B2 (en) * | 2022-02-04 | 2025-05-13 | National Technology & Engineering Solutions Of Sandia, Llc | Architectural support for persistent applications |

| US11940913B2 (en) * | 2022-03-31 | 2024-03-26 | Microsoft Technology Licensing, Llc | Overflow signal caching and aggregation |

| US12450126B2 (en) | 2023-02-13 | 2025-10-21 | Pure Storage, Inc. | Automated backups in a distributed storage system |

| KR102639244B1 (ko) | 2023-08-04 | 2024-02-21 | (주)그리드텍 | Sso에 기반한 통합 인증 솔루션을 제공하는 방법, 서버및 시스템 |

| US20250306771A1 (en) * | 2024-04-02 | 2025-10-02 | Samsung Electronics Co., Ltd. | Systems and methods for selective data flushing |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2000050997A1 (en) | 1999-02-22 | 2000-08-31 | Hitachi, Ltd. | Memory card, method for allotting logical address, and method for writing data |

| JP2004080405A (ja) | 2002-08-19 | 2004-03-11 | Fuji Photo Film Co Ltd | デジタルカメラ |

| JP2006277411A (ja) | 2005-03-29 | 2006-10-12 | Toshiba Corp | プロセッサ、メモリ、コンピュータシステムおよびデータ転送方法 |

| JP2008262451A (ja) | 2007-04-13 | 2008-10-30 | Matsushita Electric Ind Co Ltd | メモリ電源管理装置及びメモリ電源管理方法 |

| JP2011005683A (ja) | 2009-06-24 | 2011-01-13 | Fuji Xerox Co Ltd | 画像処理装置及びプログラム |

| WO2011007599A1 (ja) | 2009-07-17 | 2011-01-20 | 株式会社 東芝 | メモリ管理装置 |

| JP2013047979A (ja) | 2004-05-03 | 2013-03-07 | Microsoft Corp | 不揮発性メモリ・キャッシュの性能改善 |

| US20150106410A1 (en) | 2013-10-10 | 2015-04-16 | Apple Inc. | Memory System with Shared File System |

Family Cites Families (91)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6633964B2 (en) | 2001-03-30 | 2003-10-14 | Intel Corporation | Method and system using a virtual lock for boot block flash |

| US7073006B2 (en) | 2001-08-02 | 2006-07-04 | Intel Corporation | Implementing hardware interrupt event driven mechanism to offer soft real-time universal serial bus |

| US20030070115A1 (en) | 2001-10-05 | 2003-04-10 | Nguyen Tom L. | Logging and retrieving pre-boot error information |

| US7434068B2 (en) | 2001-10-19 | 2008-10-07 | Intel Corporation | Content protection in non-volatile storage devices |

| US7127579B2 (en) | 2002-03-26 | 2006-10-24 | Intel Corporation | Hardened extended firmware interface framework |

| US7143277B2 (en) | 2002-08-19 | 2006-11-28 | Intel Corporation | Methods and apparatus for event based console variable coherence maintenance in a pre-boot environment |

| US7337309B2 (en) | 2003-03-24 | 2008-02-26 | Intel Corporation | Secure online BIOS update schemes |

| US7174451B2 (en) | 2003-03-31 | 2007-02-06 | Intel Corporation | System and method for saving and/or restoring system state information over a network |

| US20040249992A1 (en) | 2003-04-30 | 2004-12-09 | Komarla Eshwari P. | Methods and apparatus to provide environment-based instruction selection |

| US7188238B2 (en) | 2003-05-21 | 2007-03-06 | Intel Corporation | Methods and apparatus to update a basic input/output system (BIOS) |

| US7440998B2 (en) | 2003-06-18 | 2008-10-21 | Intel Corporation | Provisioning for a modular server |

| US7587750B2 (en) | 2003-06-26 | 2009-09-08 | Intel Corporation | Method and system to support network port authentication from out-of-band firmware |

| US7444667B2 (en) | 2003-07-28 | 2008-10-28 | Intel Corporation | Method and apparatus for trusted blade device computing |

| US7370324B2 (en) | 2003-09-30 | 2008-05-06 | Intel Corporation | Switching between a service virtual machine and a guest virtual machine in a virtual machine monitor environment |

| US7562230B2 (en) | 2003-10-14 | 2009-07-14 | Intel Corporation | Data security |

| US20050240669A1 (en) | 2004-03-29 | 2005-10-27 | Rahul Khanna | BIOS framework for accommodating multiple service processors on a single server to facilitate distributed/scalable server management |

| US7496706B2 (en) | 2004-06-30 | 2009-02-24 | Intel Corporation | Message signaled interrupt redirection table |

| US7305544B2 (en) | 2004-12-10 | 2007-12-04 | Intel Corporation | Interleaved boot block to support multiple processor architectures and method of use |

| US7278006B2 (en) | 2004-12-30 | 2007-10-02 | Intel Corporation | Reducing memory fragmentation |

| US7366891B2 (en) | 2004-12-30 | 2008-04-29 | Intel Corporation | Methods and apparatus to provide dual-mode drivers in processor systems |

| US7673128B2 (en) | 2005-04-22 | 2010-03-02 | Intel Corporation | Methods and apparatus to facilitate fast restarts in processor systems |

| US20060288197A1 (en) | 2005-06-16 | 2006-12-21 | Swanson Robert C | Identifying an operating system associated with a boot path |

| US20070006048A1 (en) | 2005-06-29 | 2007-01-04 | Intel Corporation | Method and apparatus for predicting memory failure in a memory system |

| US7647474B2 (en) | 2005-09-27 | 2010-01-12 | Intel Corporation | Saving system context in the event of power loss |

| US20070157015A1 (en) | 2005-12-29 | 2007-07-05 | Swanson Robert C | Methods and apparatus to optimize boot speed |

| US20070234029A1 (en) | 2006-03-28 | 2007-10-04 | Rothman Michael A | Methods and apparatus for context sensitive component dispatch management |

| US20070234077A1 (en) | 2006-03-31 | 2007-10-04 | Rothman Michael A | Reducing power consumption by load imbalancing |

| US7406560B2 (en) | 2006-06-21 | 2008-07-29 | Intel Corporation | Using multiple non-volatile memory devices to store data in a computer system |

| US20080126650A1 (en) | 2006-09-21 | 2008-05-29 | Swanson Robert C | Methods and apparatus for parallel processing in system management mode |

| US7596714B2 (en) | 2006-11-20 | 2009-09-29 | Intel Corporation | Methods and apparatus to manage throttling in computing environments |

| US7945841B2 (en) | 2006-12-06 | 2011-05-17 | Intel Corporation | System and method for continuous logging of correctable errors without rebooting |

| US20080155277A1 (en) | 2006-12-26 | 2008-06-26 | Mallik Bulusu | Hardware partitioned trust |

| US7596643B2 (en) | 2007-02-07 | 2009-09-29 | Siliconsystems, Inc. | Storage subsystem with configurable buffer |

| US7987348B2 (en) | 2007-03-30 | 2011-07-26 | Intel Corporation | Instant on video |

| US7890811B2 (en) | 2007-06-29 | 2011-02-15 | Intel Corporation | Method and apparatus for improved memory reliability, availability and serviceability |

| US8391913B2 (en) | 2007-07-18 | 2013-03-05 | Intel Corporation | Software-defined radio support in sequestered partitions |

| US7793090B2 (en) | 2007-08-30 | 2010-09-07 | Intel Corporation | Dual non-volatile memories for a trusted hypervisor |

| US7831858B2 (en) | 2007-08-31 | 2010-11-09 | Intel Corporation | Extended fault resilience for a platform |

| US7900084B2 (en) | 2007-12-21 | 2011-03-01 | Intel Corporation | Reliable memory for memory controller with multiple channels |

| US8583908B2 (en) | 2007-12-31 | 2013-11-12 | Intel Corporation | Enhanced network and local boot of Unified Extensible Firmware Interface images |

| KR101497074B1 (ko) * | 2008-06-17 | 2015-03-05 | 삼성전자주식회사 | 불휘발성 메모리 시스템 및 그것의 데이터 관리 방법 |

| US8090977B2 (en) | 2009-12-21 | 2012-01-03 | Intel Corporation | Performing redundant memory hopping |

| US8219851B2 (en) | 2009-12-29 | 2012-07-10 | Intel Corporation | System RAS protection for UMA style memory |

| US9015268B2 (en) | 2010-04-02 | 2015-04-21 | Intel Corporation | Remote direct storage access |

| US8566613B2 (en) | 2010-06-11 | 2013-10-22 | Intel Corporation | Multi-owner deployment of firmware images |

| US8479017B2 (en) | 2010-06-21 | 2013-07-02 | Intel Corporation | System and method for N-ary locality in a security co-processor |

| US9063836B2 (en) | 2010-07-26 | 2015-06-23 | Intel Corporation | Methods and apparatus to protect segments of memory |

| US8499141B2 (en) | 2010-08-02 | 2013-07-30 | Intel Corporation | Multi-socket server management with RFID |

| US20120036308A1 (en) | 2010-08-06 | 2012-02-09 | Swanson Robert C | Supporting a secure readable memory region for pre-boot and secure mode operations |

| US8539245B2 (en) | 2010-08-06 | 2013-09-17 | Intel Corporation | Apparatus and method for accessing a secure partition in non-volatile storage by a host system enabled after the system exits a first instance of a secure mode |

| US8688812B2 (en) | 2010-09-23 | 2014-04-01 | Intel Corporation | Cluster computing—NIC based OS provision |

| US8428929B2 (en) | 2010-09-30 | 2013-04-23 | Intel Corporation | Demand based USB proxy for data stores in service processor complex |

| US20120159136A1 (en) | 2010-12-16 | 2012-06-21 | Rothman Michael A | Computer system boot enhancements with user override |

| US8370667B2 (en) | 2010-12-22 | 2013-02-05 | Intel Corporation | System context saving based on compression/decompression time |

| US20130325738A1 (en) | 2011-12-15 | 2013-12-05 | Robert C. Swanson | Location service for physical delivery |

| CN104012166B (zh) | 2011-12-21 | 2018-06-22 | 英特尔公司 | 位置感知资源定位符 |

| EP2795561A4 (en) | 2011-12-22 | 2015-06-10 | Intel Corp | OBTAINING PROVIDER INFORMATION BY USING INTER-NETWORKING MOBILE DEVICES |

| EP3404947A1 (en) | 2011-12-30 | 2018-11-21 | INTEL Corporation | Trusted application migration across computer nodes |

| CN110083494B (zh) | 2011-12-30 | 2023-07-25 | 英特尔公司 | 在多核心环境中管理硬件错误的方法和装置 |

| WO2013147825A1 (en) | 2012-03-30 | 2013-10-03 | Intel Corporation | Providing an immutable antivirus payload for internet ready compute nodes |

| US9678863B2 (en) * | 2012-06-12 | 2017-06-13 | Sandisk Technologies, Llc | Hybrid checkpointed memory |

| US9098302B2 (en) | 2012-06-28 | 2015-08-04 | Intel Corporation | System and apparatus to improve boot speed in serial peripheral interface system using a baseboard management controller |

| US9384367B2 (en) | 2012-09-04 | 2016-07-05 | Intel Corporation | Measuring platform components with a single trusted platform module |

| US9454214B2 (en) | 2013-03-12 | 2016-09-27 | Intel Corporation | Memory state management for electronic device |

| US20150006962A1 (en) | 2013-06-27 | 2015-01-01 | Robert C. Swanson | Memory dump without error containment loss |

| EP3033676A1 (en) | 2013-08-14 | 2016-06-22 | Intel Corporation | Manageability redundancy for micro server and clustered system-on-a-chip deployments |

| US9996142B2 (en) | 2013-10-31 | 2018-06-12 | Intel Corporation | Selective power management for pre-boot firmware updates |

| US9413765B2 (en) | 2014-03-25 | 2016-08-09 | Intel Corporation | Multinode hubs for trusted computing |

| US9880859B2 (en) | 2014-03-26 | 2018-01-30 | Intel Corporation | Boot image discovery and delivery |

| US10146657B2 (en) | 2014-03-26 | 2018-12-04 | Intel Corporation | Initialization trace of a computing device |

| KR102303008B1 (ko) * | 2014-08-15 | 2021-09-15 | 마이크로소프트 테크놀로지 라이센싱, 엘엘씨 | 파일 시스템에서의 플러싱 기법 |

| US10437742B2 (en) | 2014-10-10 | 2019-10-08 | Microsoft Technology Licensing, Llc | Vendor-specific peripheral device class identifiers |

| US10126950B2 (en) | 2014-12-22 | 2018-11-13 | Intel Corporation | Allocating and configuring persistent memory |

| EP3311286A4 (en) | 2015-06-17 | 2019-01-16 | Intel Corporation | DATA PROCESSING DEVICE AND METHOD WITH PERSISTENT MEMORY |

| US9886194B2 (en) | 2015-07-13 | 2018-02-06 | Samsung Electronics Co., Ltd. | NVDIMM adaptive access mode and smart partition mechanism |

| US10031674B2 (en) | 2015-10-07 | 2018-07-24 | Samsung Electronics Co., Ltd. | DIMM SSD addressing performance techniques |

| KR20170048114A (ko) | 2015-10-26 | 2017-05-08 | 삼성전자주식회사 | 저장 장치 및 저장 장치에 의해 기록 명령이 수행되는 방법 |

| US10115442B2 (en) | 2016-01-22 | 2018-10-30 | Microsoft Technology Licensing, Llc | Demand-based provisioning of volatile memory for use as non-volatile memory |

| US10133617B2 (en) * | 2016-07-01 | 2018-11-20 | Hewlett Packard Enterprise Development Lp | Failure notifications in multi-node clusters |

| US10452404B2 (en) | 2016-07-28 | 2019-10-22 | Microsoft Technology Licensing, Llc. | Optimized UEFI reboot process |

| US10025649B2 (en) | 2016-08-25 | 2018-07-17 | Microsoft Technology Licensing, Llc | Data error detection in computing systems |

| US10152393B2 (en) | 2016-08-28 | 2018-12-11 | Microsoft Technology Licensing, Llc | Out-of-band data recovery in computing systems |

| US20180107596A1 (en) | 2016-10-13 | 2018-04-19 | Microsoft Technology Licensing, Llc | Battery-based data persistence management in computing systems |

| US10402394B2 (en) | 2016-11-03 | 2019-09-03 | Veritas Technologies Llc | Systems and methods for flushing data in a virtual computing environment |

| US11243782B2 (en) | 2016-12-14 | 2022-02-08 | Microsoft Technology Licensing, Llc | Kernel soft reset using non-volatile RAM |

| US10839080B2 (en) | 2017-09-01 | 2020-11-17 | Microsoft Technology Licensing, Llc | Hardware-enforced firmware security |

| US10635553B2 (en) | 2017-10-20 | 2020-04-28 | Microsoft Technology Licensing, Llc | Error recovery in non-volatile storage partitions |

| US10713128B2 (en) | 2017-11-30 | 2020-07-14 | Microsoft Technology Licensing, Llc | Error recovery in volatile memory regions |

| US11157265B2 (en) | 2017-12-11 | 2021-10-26 | Microsoft Technology Licensing, Llc | Firmware update |

| US10552280B2 (en) | 2017-12-14 | 2020-02-04 | Microsoft Technology Licensing, Llc | In-band monitor in system management mode context for improved cloud platform availability |

| US10657052B2 (en) * | 2018-04-25 | 2020-05-19 | Dell Products, L.P. | Information handling system with priority based cache flushing of flash dual in-line memory module pool |

-

2019

- 2019-08-21 US US16/546,337 patent/US11113188B2/en active Active

-

2020

- 2020-06-15 KR KR1020227005323A patent/KR102879385B1/ko active Active

- 2020-06-15 CA CA3147608A patent/CA3147608A1/en active Pending

- 2020-06-15 BR BR112022000200A patent/BR112022000200A2/pt unknown

- 2020-06-15 WO PCT/US2020/037681 patent/WO2021034391A1/en not_active Ceased

- 2020-06-15 EP EP20735781.5A patent/EP4018319B1/en active Active

- 2020-06-15 AU AU2020334772A patent/AU2020334772A1/en not_active Abandoned

- 2020-06-15 PH PH1/2022/550425A patent/PH12022550425A1/en unknown

- 2020-06-15 JP JP2022511208A patent/JP7586895B2/ja active Active

- 2020-06-15 CN CN202080056937.4A patent/CN114222975B/zh active Active

- 2020-06-15 MX MX2022002112A patent/MX2022002112A/es unknown

-

2022

- 2022-01-18 ZA ZA2022/00837A patent/ZA202200837B/en unknown

- 2022-02-13 IL IL290568A patent/IL290568A/en unknown

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2000050997A1 (en) | 1999-02-22 | 2000-08-31 | Hitachi, Ltd. | Memory card, method for allotting logical address, and method for writing data |

| JP2004080405A (ja) | 2002-08-19 | 2004-03-11 | Fuji Photo Film Co Ltd | デジタルカメラ |

| JP2013047979A (ja) | 2004-05-03 | 2013-03-07 | Microsoft Corp | 不揮発性メモリ・キャッシュの性能改善 |

| JP2006277411A (ja) | 2005-03-29 | 2006-10-12 | Toshiba Corp | プロセッサ、メモリ、コンピュータシステムおよびデータ転送方法 |

| JP2008262451A (ja) | 2007-04-13 | 2008-10-30 | Matsushita Electric Ind Co Ltd | メモリ電源管理装置及びメモリ電源管理方法 |

| JP2011005683A (ja) | 2009-06-24 | 2011-01-13 | Fuji Xerox Co Ltd | 画像処理装置及びプログラム |

| WO2011007599A1 (ja) | 2009-07-17 | 2011-01-20 | 株式会社 東芝 | メモリ管理装置 |

| US20150106410A1 (en) | 2013-10-10 | 2015-04-16 | Apple Inc. | Memory System with Shared File System |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20220050895A (ko) | 2022-04-25 |

| MX2022002112A (es) | 2022-03-17 |

| US11113188B2 (en) | 2021-09-07 |

| AU2020334772A1 (en) | 2022-03-10 |

| CN114222975A (zh) | 2022-03-22 |

| US20210056016A1 (en) | 2021-02-25 |

| CA3147608A1 (en) | 2021-02-25 |

| WO2021034391A1 (en) | 2021-02-25 |

| BR112022000200A2 (pt) | 2022-03-03 |

| JP2022545012A (ja) | 2022-10-24 |

| IL290568A (en) | 2022-04-01 |

| KR102879385B1 (ko) | 2025-10-31 |

| PH12022550425A1 (en) | 2023-03-27 |

| EP4018319A1 (en) | 2022-06-29 |

| CN114222975B (zh) | 2025-05-20 |

| ZA202200837B (en) | 2023-04-26 |

| EP4018319B1 (en) | 2023-05-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7586895B2 (ja) | メモリー・アパーチャのフラッシュ・オーダーを使用したデーター保存 | |

| JP7489988B2 (ja) | ガベージコレクションのマーキングにおける同期依存の軽減 | |

| US8370835B2 (en) | Method for dynamically generating a configuration for a virtual machine with a virtual hard disk in an external storage device | |

| US8881144B1 (en) | Systems and methods for reclaiming storage space from virtual machine disk images | |

| CN104252319A (zh) | 针对多个逻辑分区的备份管理 | |

| WO2012131507A1 (en) | Running a plurality of instances of an application | |

| CN105683985A (zh) | 虚拟机内省 | |

| JPWO2013088818A1 (ja) | 仮想計算機システム、仮想化機構、及びデータ管理方法 | |

| US11656888B2 (en) | Performing an application snapshot using process virtual machine resources | |

| US11422932B2 (en) | Integrated reference and secondary marking | |

| US20120179650A1 (en) | Asynchronous assertions | |

| US10838737B1 (en) | Restoration of memory content to restore machine state | |

| WO2024041351A1 (en) | Disabling processor facility on new processor generation without breaking binary compatibility | |

| US20240111857A1 (en) | Secure execution of a file on a copy device in a virtualized computing environment | |

| US11467889B2 (en) | System and method of utilizing legacy applications with secure memory medium portions | |

| RU2805768C2 (ru) | Уменьшение зависимости от синхронизации в пометке сбора мусора | |

| Bem | Virtual machine for computer forensics–the open source perspective | |

| Nanavati | Operator, number please: mediating access to shared resources for efficiency and isolation | |

| CN102073529B (zh) | 超级内核组件的升级方法和计算机系统 | |

| JP2016076152A (ja) | エラー検出システム、エラー検出方法およびエラー検出プログラム | |

| Rogers | Lightweight local cloning of kvm/qemu virtual machines | |

| Ng | An application for normal and critical operations in a tactical MLS system | |

| HK40056571A (en) | Reducing synchronization reliance in garbage collection marking | |

| Bai | A Checkpointing Methodology for Android Smartphone | |

| CN102073529A (zh) | 超级内核组件的升级方法和计算机系统 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230612 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230612 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240522 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240806 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20241022 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20241107 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7586895 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D02 |