以下、実施の形態について図面を参照しながら説明する。ただし、実施の形態は多くの異なる態様で実施することが可能であり、趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

また、図面において、大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお、図面は、理想的な例を模式的に示したものであり、図面に示す形状または値などに限定されない。例えば、実際の製造工程において、エッチングなどの処理により層やレジストマスクなどが意図せずに目減りすることがあるが、理解を容易とするため、図に反映しないことがある。また、図面において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する場合がある。また、同様の機能を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

また、特に上面図(「平面図」ともいう。)や斜視図などにおいて、発明の理解を容易とするため、一部の構成要素の記載を省略する場合がある。また、一部の隠れ線などの記載を省略する場合がある。

また、本明細書等において、第1、第2等として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。また、本明細書等に記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

また、本明細書等において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。したがって、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。

例えば、本明細書等において、XとYとが接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接的に接続されている場合とが、本明細書等に開示されているものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に開示されているものとする。ここで、X、Yは、対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など)であるとする。

また、本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。そして、ドレイン(ドレイン端子、ドレイン領域またはドレイン電極)とソース(ソース端子、ソース領域またはソース電極)の間にチャネルが形成される領域(以下、チャネル形成領域ともいう。)を有しており、チャネル形成領域を介して、ソースとドレインとの間に電流を流すことができるものである。なお、本明細書等において、チャネル形成領域とは、電流が主として流れる領域をいう。

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができる場合がある。

なお、チャネル長とは、例えば、トランジスタの上面図において、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲート電極とが互いに重なる領域、またはチャネル形成領域における、ソース(ソース領域またはソース電極)とドレイン(ドレイン領域またはドレイン電極)との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。すなわち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネル形成領域における、いずれか一の値、最大値、最小値または平均値とする。

チャネル幅とは、例えば、トランジスタの上面図において、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲート電極とが互いに重なる領域、またはチャネル形成領域における、チャネル長方向を基準として垂直方向のチャネル形成領域の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。すなわち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネル形成領域における、いずれか一の値、最大値、最小値または平均値とする。

なお、本明細書等において、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅(以下、「実効的なチャネル幅」ともいう。)と、トランジスタの上面図において示されるチャネル幅(以下、「見かけ上のチャネル幅」ともいう。)と、が異なる場合がある。例えば、ゲート電極が半導体の側面を覆う場合、実効的なチャネル幅が、見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつゲート電極が半導体の側面を覆うトランジスタでは、半導体の側面に形成されるチャネル形成領域の割合が大きくなる場合がある。その場合は、見かけ上のチャネル幅よりも、実効的なチャネル幅の方が大きくなる。

このような場合、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

本明細書では、単にチャネル幅と記載した場合には、見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅などは、断面TEM像などを解析することなどによって、値を決定することができる。

なお、半導体の不純物とは、例えば、半導体を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物と言える。不純物が含まれることにより、例えば、半導体の欠陥準位密度が高くなることや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第13族元素、第14族元素、第15族元素、酸化物半導体の主成分以外の遷移金属などがあり、例えば、水素、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。なお、水も不純物として機能する場合がある。また、例えば不純物の混入によって、酸化物半導体に酸素欠損(VOと表記する場合がある)が形成される場合がある。

なお、本明細書等において、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものである。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものである。

また、本明細書等において、「絶縁体」という用語を、絶縁膜または絶縁層と言い換えることができる。また、「導電体」という用語を、導電膜または導電層と言い換えることができる。また、「半導体」という用語を、半導体膜または半導体層と言い換えることができる。

また、本明細書等において、「平行」とは、二つの直線が-10度以上10度以下の角度で配置されている状態をいう。したがって、-5度以上5度以下の場合も含まれる。また、「概略平行」とは、二つの直線が-30度以上30度以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が80度以上100度以下の角度で配置されている状態をいう。したがって、85度以上95度以下の場合も含まれる。また、「概略垂直」とは、二つの直線が60度以上120度以下の角度で配置されている状態をいう。

本明細書等において、金属酸化物(metal oxide)とは、広い意味での金属の酸化物である。金属酸化物は、酸化物絶縁体、酸化物導電体(透明酸化物導電体を含む。)、酸化物半導体(Oxide Semiconductorまたは単にOSともいう。)などに分類される。例えば、トランジスタの半導体層に金属酸化物を用いた場合、当該金属酸化物を酸化物半導体と呼称する場合がある。つまり、OSトランジスタと記載する場合においては、金属酸化物または酸化物半導体を有するトランジスタと換言することができる。

また、本明細書等において、ノーマリーオフとは、ゲートに電位を印加しない、またはゲートに接地電位を与えたときに、トランジスタに流れるチャネル幅1μmあたりのドレイン電流が、室温において1×10-20A以下、85℃において1×10-18A以下、または125℃において1×10-16A以下であることをいう。

(実施の形態1)

本実施の形態では、図1A乃至図16Dを用いて、本発明の一態様に係るトランジスタ200を有する半導体装置の一例、およびその作製方法について説明する。

<半導体装置の構成例>

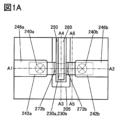

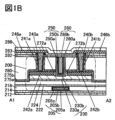

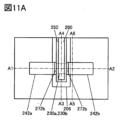

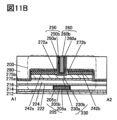

図1A乃至図1Dを用いて、トランジスタ200を有する半導体装置の構成を説明する。図1A乃至図1Dは、トランジスタ200を有する半導体装置の上面図および断面図である。図1Aは、当該半導体装置の上面図である。また、図1B乃至図1Dは、当該半導体装置の断面図である。ここで、図1Bは、図1AにA1-A2の一点鎖線で示す部位の断面図であり、トランジスタ200のチャネル長方向の断面図でもある。また、図1Cは、図1AにA3-A4の一点鎖線で示す部位の断面図であり、トランジスタ200のチャネル幅方向の断面図でもある。また、図1Dは、図1AにA5-A6の一点鎖線で示す部位の断面図である。なお、図1Aの上面図では、図の明瞭化のために一部の要素を省いている。

本発明の一態様の半導体装置は、基板(図示せず)上の絶縁体212と、絶縁体212上の絶縁体214と、絶縁体214上のトランジスタ200と、トランジスタ200上の絶縁体280と、絶縁体280上の絶縁体282と、絶縁体282上の絶縁体283と、を有する。絶縁体212、絶縁体214、絶縁体280、絶縁体282、および絶縁体283は層間膜として機能する。また、トランジスタ200と電気的に接続し、プラグとして機能する導電体240a、および導電体240bを有する。なお、導電体240aの側面に接して絶縁体241aが設けられ、導電体240bの側面に接して絶縁体241bが設けられる。また、絶縁体283上、導電体240a上、および導電体240b上には、導電体240a、および導電体240bとそれぞれ電気的に接続し、配線として機能する導電体246a、および導電体246bが設けられる。また、導電体246a上、導電体246b上、および絶縁体283上には、絶縁体286が設けられる。

絶縁体280、絶縁体282、絶縁体283などの開口の側壁に接して絶縁体241aが設けられ、絶縁体241aの側面に接して導電体240aの第1の導電体が設けられ、さらに内側に導電体240aの第2の導電体が設けられている。また、絶縁体280、絶縁体282、絶縁体283などの開口の側壁に接して絶縁体241bが設けられ、絶縁体241bの側面に接して導電体240bの第1の導電体が設けられ、さらに内側に導電体240bの第2の導電体が設けられている。ここで、導電体240aおよび導電体240bの上面の高さと、導電体246aまたは導電体246bと重なる領域の、絶縁体283の上面の高さと、は同程度にできる。なお、トランジスタ200では、導電体240aの第1の導電体および導電体240aの第2の導電体を積層し、導電体240bの第1の導電体および導電体240bの第2の導電体を積層する構成について示しているが、本発明はこれに限られるものではない。例えば、導電体240aおよび導電体240bのそれぞれを単層、または3層以上の積層構造として設ける構成にしてもよい。構造体が積層構造を有する場合、形成順に序数を付与し、区別する場合がある。

[トランジスタ200]

図1A乃至図1Dに示すように、トランジスタ200は、絶縁体214上の絶縁体216と、絶縁体214および/または絶縁体216に埋め込まれるように配置された導電体205(導電体205a、導電体205b、および導電体205c)と、絶縁体216上、および導電体205上の絶縁体222と、絶縁体222上の絶縁体224と、絶縁体224上の酸化物230aと、酸化物230a上の酸化物230bと、酸化物230b上の導電体242a、および導電体242bと、酸化物230b上の絶縁体250(絶縁体250a、および絶縁体250b)と、絶縁体250上に位置し、酸化物230bの一部と重なる導電体260(導電体260a、および導電体260b)と、酸化物230b上、かつ、導電体242aと絶縁体250aとの間に位置する酸化物272aと、酸化物230b上、かつ、導電体242bと絶縁体250aとの間に位置する酸化物272bと、絶縁体224、酸化物230a、酸化物230b、導電体242a、導電体242b、酸化物272a、および酸化物272bの上に配置される絶縁体275(絶縁体275a、および絶縁体275b)と、を有する。ここで、図1Bおよび図1Cに示すように、導電体260の上面は、絶縁体250の上面、および絶縁体280の上面と略一致して配置される。また、絶縁体282は、導電体260、絶縁体250、および絶縁体280のそれぞれの上面と接する。

なお、以下において、酸化物230aと酸化物230bをまとめて酸化物230と呼ぶ場合がある。

絶縁体280および絶縁体275には、酸化物230bに達する開口が設けられる。当該開口内に、絶縁体250、および導電体260が配置されている。また、トランジスタ200のチャネル長方向において、導電体242aと、導電体242bとの間に導電体260、絶縁体250、酸化物272a、および酸化物272bが設けられている。絶縁体250は、導電体260の側面と接する領域と、導電体260の底面と接する領域と、を有する。酸化物272aは、導電体242aの側面と接する領域と、絶縁体250aの側面と接する領域と、酸化物230bの上面と接する領域と、を有する。酸化物272bは、導電体242bの側面と接する領域と、絶縁体250aの側面と接する領域と、酸化物230bの上面と接する領域と、を有する。

酸化物230は、絶縁体224の上に配置された酸化物230aと、酸化物230aの上に配置された酸化物230bと、を有することが好ましい。酸化物230b下に酸化物230aを有することで、酸化物230aよりも下方に形成された構造物から、酸化物230bへの不純物の拡散を抑制することができる。

なお、トランジスタ200では、酸化物230が、酸化物230a、および酸化物230bの2層を積層する構成について示しているが、本発明はこれに限られるものではない。例えば、酸化物230bの単層、または3層以上の積層構造を設ける構成にしてもよいし、酸化物230a、および酸化物230bのそれぞれが積層構造を有していてもよい。

導電体260は、第1のゲート(トップゲートともいう。)電極として機能し、導電体205は、第2のゲート(バックゲートともいう。)電極として機能する。また、絶縁体222、絶縁体224、および絶縁体250は、ゲート絶縁体として機能する。また、導電体242aは、ソースまたはドレインの一方として機能し、導電体242bは、ソースまたはドレインの他方として機能する。また、酸化物230の導電体260と重畳する領域の少なくとも一部はチャネル形成領域として機能する。

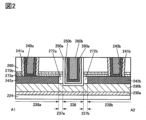

ここで、図1Bにおけるチャネル形成領域近傍の拡大図を図2に示す。図2に示すように、酸化物230bは、トランジスタ200のチャネル形成領域として機能する領域236と、ソース領域またはドレイン領域として機能する領域238aおよび領域238bと、を有する。領域236は、少なくとも一部が導電体260と重畳している。言い換えると、領域236は、導電体242aと導電体242bの間の領域に設けられている。領域238aは、導電体242aと重畳し、領域238bは、導電体242bと重畳している。

トランジスタ200は、チャネル形成領域を含む酸化物230(酸化物230a、および酸化物230b)に、半導体として機能する金属酸化物(以下、酸化物半導体ともいう。)を用いることが好ましい。

また、半導体として機能する金属酸化物は、バンドギャップが2eV以上のものを用いることが好ましく、2.5eV以上のものを用いることがより好ましい。このように、バンドギャップの大きい金属酸化物を用いることで、トランジスタのオフ電流を低減することができる。

酸化物230として、例えば、インジウム、元素Mおよび亜鉛を有するIn-M-Zn酸化物(元素Mは、アルミニウム、ガリウム、イットリウム、錫、銅、バナジウム、ベリリウム、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種)等の金属酸化物を用いるとよい。また、酸化物230として、In-Ga酸化物、In-Zn酸化物、インジウム酸化物などを用いてもよい。

ここで、酸化物230bに用いる金属酸化物における、元素Mに対するInの原子数比が、酸化物230aに用いる金属酸化物における、元素Mに対するInの原子数比より大きいことが好ましい。元素Mに対するInの原子数比が小さいほど、不純物および酸素の拡散を抑制する傾向がある。よって、酸化物230bの下に酸化物230aを配置することで、酸化物230aよりも下方に形成された構造物からの、酸化物230bに対する、不純物および酸素の拡散を抑制することができる。

酸化物230bは、結晶性を有することが好ましい。特に、酸化物230bとして、CAAC-OS(c-axis aligned crystalline oxide semiconductor)を用いることが好ましい。

CAAC-OSは、結晶性の高い、緻密な構造を有しており、不純物や欠陥(例えば、酸素欠損など)が少ない金属酸化物である。特に、金属酸化物の形成後に、金属酸化物が多結晶化しない程度の温度(例えば、400℃以上600℃以下)で加熱処理することで、CAAC-OSをより結晶性の高い、緻密な構造にすることができる。このようにして、CAAC-OSの密度をより高めることで、当該CAAC-OS中の不純物または酸素の拡散をより低減することができる。

また、CAAC-OSは、明確な結晶粒界を確認することが難しいため、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。したがって、CAAC-OSを有する金属酸化物は、物理的性質が安定する。そのため、CAAC-OSを有する金属酸化物は熱に強く、信頼性が高い。

酸化物半導体を用いたトランジスタは、酸化物半導体中のチャネル形成領域に不純物および酸素欠損が存在すると、電気特性が変動しやすく、信頼性が悪くなる場合がある。また、酸素欠損近傍の水素が、酸素欠損に水素が入った欠陥(以下、VOHと呼ぶ場合がある。)を形成し、キャリアとなる電子を生成する場合がある。このため、酸化物半導体中のチャネル形成領域に酸素欠損が含まれていると、トランジスタはノーマリーオン特性(ゲート電極に電圧を印加しなくてもチャネルが存在し、トランジスタに電流が流れる特性)となりやすい。したがって、酸化物半導体中のチャネル形成領域では、不純物、酸素欠損、およびVOHはできる限り低減されていることが好ましい。言い換えると、酸化物半導体中のチャネルが形成される領域は、キャリア濃度が低減され、i型(真性化)または実質的にi型であることが好ましい。

しかしながら、i型または実質的にi型である領域が、酸化物半導体中のソース領域またはドレイン領域にまで広がると、トランジスタ200のオン電流の低下、電界効果移動度の低下などを引き起こす恐れがある。

よって、酸化物半導体中において、チャネル形成領域として機能する領域236は、キャリア濃度が低減され、i型または実質的にi型であることが好ましいが、ソース領域またはドレイン領域として機能する領域238aおよび領域238bは、キャリア濃度が高く、n型であることが好ましい。

また、トランジスタを微細化することで、ソース領域とドレイン領域との間の距離が短くなり、トランジスタのソース-ドレイン耐圧が低下する恐れがある。また、領域236と領域238aまたは領域238bとの境界での電流密度が集中し、チャネルとソースまたはドレインとの境界における発熱が生じる恐れがある。

そこで、本発明の一態様では、酸化物230bの、領域236と領域238aとの間に領域237aが設けられ、領域236と領域238bとの間に領域237bが設けられることが好ましい。

さらに、領域237aのキャリア濃度は、領域238aのキャリア濃度と同等、またはそれよりも低く、領域236のキャリア濃度と同等、またはそれよりも高いことが好ましい。また、領域237bのキャリア濃度は、領域238bのキャリア濃度と同等、またはそれよりも低く、領域236のキャリア濃度と同等、またはそれよりも高いことが好ましい。つまり、領域237aは、領域236と領域238aとのオフセット領域として機能し、領域237bは、領域236と領域238bとのオフセット領域として機能する。

ここで、トランジスタのゲート長について説明する。ゲート長とは、トランジスタ動作時にキャリアがチャネル形成領域内部を移動する方向における、ゲート電極の長さであり、トランジスタの上面図における、ゲート電極の底面の幅をいう。つまり、トランジスタ200のチャネル長方向の断面視において、ゲート長は、酸化物230と重なる領域の、導電体260の底面の幅である。言い換えると、ゲート長は、領域236の幅に相当する。なお、ゲート電極の底面が緩やかな曲面を有する場合や、ゲート電極が底面に向かってテーパーがついた形状を有する場合がある。このときのゲート長は、トランジスタの上面図における、ゲート電極の底面の幅よりも大きくなる場合がある。

ここで、トランジスタの実効的なチャネル長について説明する。実効的なチャネル長とは、トランジスタの上面図において、ソース電極とドレイン電極との間の距離をいう。つまり、トランジスタ200のチャネル長方向の断面視において、実効的なチャネル長は、導電体242aと導電体242bとの間の距離である。言い換えると、実効的なチャネル長は、領域237aの幅と、領域236の幅と、領域237bの幅との和に相当する。なお、ソース電極の側面が、ソース電極の被形成面に対して傾斜し、ドレイン電極の側面が、ドレイン電極の被形成面に対して傾斜している場合、実効的なチャネル長とは、トランジスタの上面図において、ソース電極の側面の底部と、ドレイン電極の側面の底部との間の距離をいう。

酸化物230bに領域237aおよび領域237bを設けることで、実効的なチャネル長を伸長することができる。よって、トランジスタのソース-ドレイン耐圧を向上させることができ、信頼性の高いトランジスタを実現できる。また、領域236と領域238aまたは領域238bとの境界での電流密度を緩和でき、チャネルとソースまたはドレインとの境界における発熱が抑制され、信頼性の高いトランジスタ、および半導体装置とすることができる。したがって、トランジスタが微細化されても、良好な電気特性を得ることができる。

トランジスタ200のチャネル長方向の断面視において、領域237aおよび領域237bの幅のそれぞれは、代表的には、1nm以上10nm未満、好ましくは3nm以上8nm未満である。なお、トランジスタ200のチャネル長方向の断面視における、領域237aの幅は、領域237aの、領域236と領域238aとの間の長さと言い換えることができる。また、トランジスタ200のチャネル長方向の断面視における、領域237bの幅は、領域237bの、領域236と領域238bとの間の長さと言い換えることができる。このとき、トランジスタ200のチャネル長方向の断面視において、チャネル形成領域として機能する領域236の幅が5nm以上40nm以下であっても、良好な電気特性を得ることができる。なお、トランジスタ200のチャネル長方向の断面視における、領域236の幅は、領域236の、領域237aと領域237bとの間の長さと言い換えることができる。

チャネル形成領域として機能する領域236のキャリア濃度は、1×1017cm-3未満であることが好ましく、1×1016cm-3未満であることがより好ましく、1×1013cm-3未満であることがさらに好ましく、1×1012cm-3未満であることがさらに好ましい。なお、領域236のキャリア濃度の下限値については、特に限定は無いが、例えば、1×10-9cm-3とすることができる。

また、ソース領域またはドレイン領域として機能する領域238aおよび領域238bのキャリア濃度は、1×1017cm-3以上1×1021cm-3未満であることが好ましく、1×1018cm-3以上1×1020cm-3未満であることがより好ましい。

また、領域237a、および領域237bのキャリア濃度は、領域236、領域238a、および領域238bのキャリア濃度にもよるが、代表的には、1×1015cm-3以上1×1017cm-3以下、好ましくは5×1015cm-3以上1×1016cm-3以下である。

なお、酸化物230bに領域237aを設けるには、導電体242aと絶縁体250aとの間に酸化物272aが配置されることが好ましい。このとき、領域237aは、酸化物272aと接する領域を有する。酸化物272aを設けることで、絶縁体280、絶縁体250aなどが有する酸素を、酸化物272aを介して、領域237aに供給することができる。よって、領域237a中の酸素欠損を低減し、領域237aのキャリア濃度を低くすることができる。また、トランジスタのチャネル長方向の断面視において、酸化物272aの幅は、1nm以上10nm未満であることが好ましく、3nm以上8nm未満であることがより好ましい。なお、トランジスタのチャネル長方向の断面視における、酸化物272aの幅は、導電体242aと絶縁体250aとの間の、酸化物272aの膜厚と言い換えることができる。

同様に、酸化物230bに領域237bを設けるには、導電体242bと絶縁体250aとの間に酸化物272bが配置されることが好ましい。このとき、領域237bは、酸化物272bと接する領域を有する。酸化物272bを設けることで、絶縁体280、絶縁体250aなどが有する酸素を、酸化物272bを介して、領域237bに供給することができる。よって、領域237b中の酸素欠損を低減し、領域237bのキャリア濃度を低くすることができる。また、トランジスタのチャネル長方向の断面視において、酸化物272bの幅は、1nm以上10nm未満であることが好ましく、3nm以上8nm未満であることがより好ましい。なお、トランジスタのチャネル長方向の断面視における、酸化物272bの幅は、導電体242bと絶縁体250aとの間の、酸化物272bの膜厚と言い換えることができる。

トランジスタ200のチャネル長方向の断面視における、酸化物272aおよび酸化物272bの幅を上記にすることで、ゲート長または領域236の幅が5nm以上40nm以下であっても、良好な電気特性を得ることができる。

酸化物272a、および酸化物272bは、それぞれ導電体242a、および導電体242bの側端部が酸化されることで、形成される場合がある。よって、酸化物272a、および酸化物272bは、それぞれ導電体242a、および導電体242bが有する金属を含む場合がある。例えば、導電体242a、および導電体242bとして、タンタルを含む窒化物を用いる場合、酸化物272a、および酸化物272bのそれぞれは、タンタルと、酸素と、を有する。

また、酸化物272a、および酸化物272bは、絶縁体250aとも接する。よって、酸化物272a、および酸化物272bは、導電体242a、および導電体242bが有する金属に加えて、絶縁体250aが有する元素を含む場合がある。例えば、絶縁体250aとして、酸化シリコン、または酸化窒化シリコンなどを用いる場合、酸化物272a、および酸化物272bのそれぞれは、タンタルと、シリコンと、酸素と、を有する場合がある。

酸化物272aおよび酸化物272bは、それぞれ、導電体242aおよび導電体242bよりも酸素を多く含むため、絶縁性を有すると推定される。よって、酸化物272aおよび酸化物272bを、semi-insulator(SI)と呼ぶことができる場合がある。領域237aおよび領域237bのキャリア濃度は、領域238aおよび領域238bのキャリア濃度と同等、またはそれよりも低く、領域236のキャリア濃度と同等、またはそれよりも高いため、領域237aおよび領域237bをSIまたはSI領域と呼ぶことができる場合がある。領域236を、I型または実質的にI型であるとみなし、領域238aおよび領域238bを、N型またはN+型であるとみなすと、トランジスタ200は、(N+-SI-I-SI-N+)構造を有するといえる。

また、酸化物230b上に導電体242aおよび導電体242bを設けた状態で、酸素を含む雰囲気でマイクロ波処理を行うことが好ましい。ここで、マイクロ波処理とは、例えばマイクロ波を用いて高密度プラズマを発生させる電源を有する装置を用いた処理のことを指す。

酸素を含む雰囲気でマイクロ波処理を行うことで、マイクロ波、またはRF等の高周波を用いて酸素ガスをプラズマ化し、当該酸素プラズマを作用させることができる。このとき、マイクロ波、またはRF等の高周波を領域236、領域237a、および領域237bに照射することもできる。プラズマ、マイクロ波などの作用により、領域236、領域237a、および領域237bのVOHを分断し、水素を領域236、領域237a、および領域237bから除去し、酸素欠損を酸素で補填することができる。つまり、領域236、領域237a、および領域237bにおいて、「VOH→H+VO」という反応が起きて、領域236、領域237a、および領域237bの水素濃度を低減することができる。よって、領域236中、領域237a中、および領域237b中の酸素欠損、およびVOHを低減し、キャリア濃度を低下させることができる。

また、酸素を含む雰囲気でマイクロ波処理を行う際、マイクロ波、またはRF等の高周波、酸素プラズマなどの作用は、導電体242aおよび導電体242bに遮蔽され、領域238aおよび領域238bには及ばない。さらに、酸素プラズマの作用は、酸化物230b、導電体242a、および導電体242bを覆って設けられている、絶縁体275および絶縁体280によって低減することができる。これにより、マイクロ波処理の際に、領域238aおよび領域238bで、VOHの低減、および過剰な量の酸素供給が発生しないので、キャリア濃度の低下を防ぐことができる。

また、酸素を含む雰囲気でマイクロ波処理を行う際、マイクロ波、またはRF等の高周波、酸素プラズマなどの作用は、酸化物272a、酸化物272b、絶縁体275、および絶縁体280によって低減することができる。よって、領域237a、および領域237bへの当該作用は、領域236よりも弱く、領域238aおよび領域238bよりも強い。したがって、マイクロ波処理による、領域237aおよび領域237bのキャリア濃度は、領域238aおよび領域238bよりも低下し、領域236ほど低下しない。

このようにして、酸化物半導体の領域236で選択的に酸素欠損、およびVOHを除去して、領域236をi型または実質的にi型とすることができる。さらに、ソース領域またはドレイン領域として機能する領域238aおよび領域238bに過剰な酸素が供給されるのを抑制し、n型を維持することができる。さらに、領域237aおよび領域237bのキャリア濃度は、領域238aおよび領域238bのキャリア濃度と同等、またはそれよりも低く、領域236のキャリア濃度と同等、またはそれよりも高くすることができる。これにより、トランジスタ200の電気特性の変動が抑制され、基板面内でトランジスタ200の電気特性がばらつくのを抑制することができる。

このように、開示する発明の一態様では、微細化に伴う問題点を解消することができるため、結果として、トランジスタサイズを十分に小さくすることが可能になる。トランジスタサイズを十分に小さくすることで、トランジスタを用いた半導体装置の占める面積が小さくなるため、基板あたりの半導体装置の取り数が増大する。これにより、半導体装置あたりの製造コストは抑制される。また、半導体装置が小型化されるため、同程度の大きさでさらに機能が高められた半導体装置を実現することができる。つまり、開示する発明の一態様により酸化物半導体を用いたトランジスタの微細化が達成されることで、これに付随する様々な効果を得ることが可能である。

なお、図2では、領域236、領域237a、領域237b、領域238a、および領域238bが酸化物230bに形成される例について示しているが、本発明はこれに限られるものではない。例えば、上記の各領域が酸化物230bだけでなく、酸化物230aまで形成されてもよい。

また、図2では、領域236の幅が絶縁体250aの幅と一致しているが、本実施の形態は、これに限られるものではない。領域236の幅が絶縁体250aの幅より狭くなる場合、または領域236の幅が絶縁体250aの幅より広くなる場合もある。例えば、図3に示すように、領域236の幅が導電体260の底面の幅と一致する場合がある。

また、図2では、領域237aの幅は、酸化物272aの幅と一致している。なお、本実施の形態は、これに限られるものではない。例えば、領域237aの幅は、酸化物272aの幅より狭くなる場合、または酸化物272aの幅より広くなる場合もある。また、領域237aが、導電体242aと重なる領域を有する場合、導電体260と重なる領域を有する場合もある。例えば、図3に示すように、領域237aの幅は、導電体260に対向する導電体242aの側面と導電体260との間の距離と一致する場合がある。なお、領域237bの幅についても、領域237aの幅と同様のことがいえる。

また、酸化物230において、各領域の境界を明確に検出することが困難な場合がある。各領域内で検出される金属元素、ならびに水素、および窒素などの不純物元素の濃度は、領域ごとの段階的な変化に限らず、各領域内でも連続的に変化していてもよい。つまり、チャネル形成領域に近い領域であるほど、金属元素、ならびに水素、および窒素などの不純物元素の濃度が減少していればよい。

以上のような構成にすることで、トランジスタ特性のばらつきが少ない半導体装置を提供することができる。また、信頼性が良好な半導体装置を提供することができる。また、良好な電気特性を有する半導体装置を提供することができる。また、微細化または高集積化が可能な半導体装置を提供することができる。

なお、図1Bなどにおいて、導電体260等を埋め込む開口の側面が、酸化物230bの溝部も含めて、酸化物230bの被形成面に対して概略垂直となっているが、本実施の形態はこれに限られるものではない。例えば、図3に示すように、当該開口の底部が緩やかな曲面を有する、U字型の形状となってもよい。また、例えば、当該開口の側面が酸化物230bの被形成面に対して傾斜していてもよい。

また、図1Cに示すように、トランジスタ200のチャネル幅方向の断面視において、酸化物230bの側面と酸化物230bの上面との間に、湾曲面を有してもよい。つまり、当該側面の端部と当該上面の端部は、湾曲してもよい(以下、ラウンド状ともいう。)。

上記湾曲面での曲率半径は、0nmより大きく、導電体242aまたは導電体242bと重なる領域の酸化物230bの膜厚より小さい、または、上記湾曲面を有さない領域の長さの半分より小さいことが好ましい。上記湾曲面での曲率半径は、具体的には、0nmより大きく20nm以下、好ましくは1nm以上15nm以下、さらに好ましくは2nm以上10nm以下とする。このような形状にすることで、絶縁体250および導電体260の、酸化物230bへの被覆性を高めることができる。

酸化物230は、化学組成が異なる複数の酸化物層の積層構造を有することが好ましい。具体的には、酸化物230aに用いる金属酸化物において、主成分である金属元素に対する元素Mの原子数比が、酸化物230bに用いる金属酸化物における、主成分である金属元素に対する元素Mの原子数比より、大きいことが好ましい。また、酸化物230aに用いる金属酸化物において、Inに対する元素Mの原子数比が、酸化物230bに用いる金属酸化物における、Inに対する元素Mの原子数比より大きいことが好ましい。また、酸化物230bに用いる金属酸化物において、元素Mに対するInの原子数比が、酸化物230aに用いる金属酸化物における、元素Mに対するInの原子数比より大きいことが好ましい。

また、酸化物230bは、CAAC-OSなどの結晶性を有する酸化物であることが好ましい。CAAC-OSなどの結晶性を有する酸化物は、不純物や欠陥(酸素欠損など)が少なく、結晶性の高い、緻密な構造を有している。よって、ソース電極またはドレイン電極による、酸化物230bからの酸素の引き抜きを抑制することができる。これにより、熱処理を行っても、酸化物230bから酸素が引き抜かれることを低減できるので、トランジスタ200は、製造工程における高い温度(所謂サーマルバジェット)に対して安定である。

ここで、酸化物230aと酸化物230bの接合部において、伝導帯下端はなだらかに変化する。換言すると、酸化物230aと酸化物230bの接合部における伝導帯下端は、連続的に変化または連続接合するともいうことができる。このようにするためには、酸化物230aと酸化物230bとの界面に形成される混合層の欠陥準位密度を低くするとよい。

具体的には、酸化物230aと酸化物230bが、酸素以外に共通の元素を主成分として有することで、欠陥準位密度が低い混合層を形成することができる。例えば、酸化物230bがIn-M-Zn酸化物の場合、酸化物230aとして、In-M-Zn酸化物、M-Zn酸化物、元素Mの酸化物、In-Zn酸化物、インジウム酸化物などを用いてもよい。

具体的には、酸化物230aとして、In:M:Zn=1:3:4[原子数比]もしくはその近傍の組成、またはIn:M:Zn=1:1:0.5[原子数比]もしくはその近傍の組成の金属酸化物を用いればよい。また、酸化物230bとして、In:M:Zn=1:1:1[原子数比]もしくはその近傍の組成、またはIn:M:Zn=4:2:3[原子数比]もしくはその近傍の組成の金属酸化物を用いればよい。なお、近傍の組成とは、所望の原子数比の±30%の範囲を含む。また、元素Mとして、ガリウムを用いることが好ましい。

なお、金属酸化物をスパッタリング法により成膜する場合、上記の原子数比は、成膜された金属酸化物の原子数比に限られず、金属酸化物の成膜に用いるスパッタリングターゲットの原子数比であってもよい。

酸化物230aおよび酸化物230bを上述の構成とすることで、酸化物230aと酸化物230bとの界面における欠陥準位密度を低くすることができる。そのため、界面散乱によるキャリア伝導への影響が小さくなり、トランジスタ200は大きいオン電流、および高い周波数特性を得ることができる。

トランジスタ200において、絶縁体224上の酸化物230は、少なくとも一部がチャネル形成領域として機能する。なお、SOI(Silicon On Insulator)構造において、絶縁膜上のシリコン膜は、少なくとも一部がチャネル形成領域として機能する。よって、SOI構造は、広義にとらえると、Semiconductor On Insulator構造とみなすことができる。よって、トランジスタ200は、SOI構造を有するといえる。

また、絶縁体224上の酸化物230は、島状に形成されている。よって、同一基板上に、複数のトランジスタ200を設けることができる。よって、本発明の一態様により、集積化構造を形成することができる。

絶縁体212、絶縁体214、絶縁体275、絶縁体282、絶縁体283、および絶縁体286の少なくとも一は、水、水素などの不純物が、基板側から、または、トランジスタ200の上方からトランジスタ200に拡散するのを抑制するバリア絶縁膜として機能することが好ましい。したがって、絶縁体212、絶縁体214、絶縁体275、絶縁体282、絶縁体283、および絶縁体286の少なくとも一は、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子(N2O、NO、NO2など)、銅原子などの不純物の拡散を抑制する機能を有する(上記不純物が透過しにくい)絶縁性材料を用いることが好ましい。または、酸素(例えば、酸素原子、酸素分子などの少なくとも一)の拡散を抑制する機能を有する(上記酸素が透過しにくい)絶縁性材料を用いることが好ましい。

なお、本明細書において、バリア絶縁膜とは、バリア性を有する絶縁膜のことを指す。本明細書において、バリア性とは、対応する物質の拡散を抑制する機能(透過性が低いともいう)とする。または、対応する物質を、捕獲、および固着する(ゲッタリングともいう)機能とする。

絶縁体212、絶縁体214、絶縁体275、絶縁体282、絶縁体283、および絶縁体286としては、水、水素などの不純物、および酸素の拡散を抑制する機能を有する絶縁体を用いることが好ましく、例えば、酸化アルミニウム、酸化マグネシウム、酸化ハフニウム、酸化ガリウム、インジウムガリウム亜鉛酸化物、窒化シリコン、または窒化酸化シリコンなどを用いることができる。例えば、絶縁体212、絶縁体283、および絶縁体286として、より水素バリア性が高い、窒化シリコンなどを用いることが好ましい。また、例えば、絶縁体214、絶縁体275、および絶縁体282として、水素を捕獲および水素を固着する機能が高い、酸化アルミニウムまたは酸化マグネシウムなどを用いることが好ましい。これにより、水、水素などの不純物が絶縁体212、および絶縁体214を介して、基板側からトランジスタ200側に拡散するのを抑制することができる。または、水、水素などの不純物が絶縁体286よりも外側に配置されている層間絶縁膜などから、トランジスタ200側に拡散するのを抑制することができる。または、絶縁体224などに含まれる酸素が、絶縁体212、および絶縁体214を介して基板側に拡散するのを抑制することができる。または、絶縁体280などに含まれる酸素が、絶縁体282などを介してトランジスタ200より上方に拡散するのを抑制することができる。この様に、トランジスタ200を、水、水素などの不純物、および酸素の拡散を抑制する機能を有する絶縁体212、絶縁体214、絶縁体275、絶縁体282、絶縁体283、および絶縁体286で取り囲む構造とすることが好ましい。

ここで、絶縁体212、絶縁体214、絶縁体275、絶縁体282、絶縁体283、および絶縁体286として、アモルファス構造を有する酸化物を用いることが好ましい。例えば、AlOx(xは0より大きい任意数)、またはMgOy(yは0より大きい任意数)などの金属酸化物を用いることが好ましい。このようなアモルファス構造を有する金属酸化物では、酸素原子がダングリングボンドを有しており、当該ダングリングボンドで水素を捕獲または固着する性質を有する場合がある。このようなアモルファス構造を有する金属酸化物をトランジスタ200の構成要素として用いる、またはトランジスタ200の周囲に設けることで、トランジスタ200に含まれる水素、またはトランジスタ200の周囲に存在する水素を捕獲または固着することができる。特にトランジスタ200のチャネル形成領域に含まれる水素を捕獲または固着することが好ましい。アモルファス構造を有する金属酸化物をトランジスタ200の構成要素として用いる、またはトランジスタ200の周囲に設けることで、良好な特性を有し、信頼性の高いトランジスタ200、および半導体装置を作製することができる。

また、絶縁体212、絶縁体214、絶縁体275、絶縁体282、絶縁体283、および絶縁体286は、アモルファス構造であることが好ましいが、一部に多結晶構造の領域が形成されていてもよい。また、絶縁体212、絶縁体214、絶縁体275、絶縁体282、絶縁体283、および絶縁体286は、アモルファス構造の層と、多結晶構造の層と、が積層された多層構造であってもよい。例えば、アモルファス構造の層の上に多結晶構造の層が形成された積層構造でもよい。

絶縁体212、絶縁体214、絶縁体275、絶縁体282、絶縁体283、および絶縁体286の成膜は、例えば、スパッタリング法を用いて行えばよい。スパッタリング法は、成膜ガスに水素を用いなくてよいので、絶縁体212、絶縁体214、絶縁体275、絶縁体282、絶縁体283、および絶縁体286の水素濃度を低減することができる。なお、成膜方法は、スパッタリング法に限られるものではなく、化学気相成長(CVD:Chemical Vapor Deposition)法、分子線エピタキシー(MBE:Molecular Beam Epitaxy)法、パルスレーザ堆積(PLD:Pulsed Laser Deposition)法、原子層堆積(ALD:Atomic Layer Deposition)法などを適宜用いてもよい。

また、絶縁体212、絶縁体283、および絶縁体286の抵抗率を低くすることが好ましい場合がある。例えば、絶縁体212、絶縁体283、および絶縁体286の抵抗率を概略1×1013Ωcmとすることで、半導体装置作製工程のプラズマ等を用いる処理において、絶縁体212、絶縁体283、および絶縁体286が、導電体205、導電体242a、導電体242b、導電体260、導電体246a、または導電体246bのチャージアップを緩和することができる場合がある。絶縁体212、絶縁体283、および絶縁体286の抵抗率は、好ましくは、1×1010Ωcm以上1×1015Ωcm以下とする。

また、絶縁体216、および絶縁体280は、絶縁体214よりも誘電率が低いことが好ましい。誘電率が低い材料を層間膜とすることで、配線間に生じる寄生容量を低減することができる。例えば、絶縁体216、および絶縁体280として、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコンなどを適宜用いればよい。特に、酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため好ましい。特に、酸化シリコン、酸化窒化シリコン、空孔を有する酸化シリコンなどの材料は、加熱により脱離する酸素を含む領域を容易に形成することができるため好ましい。

導電体205は、酸化物230、および導電体260と、重なるように配置する。ここで、導電体205は、絶縁体214および/または絶縁体216に形成された開口に埋め込まれて設けることが好ましい。

導電体205は、導電体205a、導電体205b、および導電体205cを有する。導電体205aは、当該開口の底面および側壁に接して設けられる。導電体205bは、導電体205aに形成された凹部に埋め込まれるように設けられる。ここで、導電体205bの上面は、導電体205aの上面および絶縁体216の上面より低くなる。導電体205cは、導電体205bの上面、および導電体205aの側面に接して設けられる。ここで、導電体205cの上面の高さは、導電体205aの上面の高さおよび絶縁体216の上面の高さと略一致する。つまり、導電体205bは、導電体205aおよび導電体205cに包み込まれる構成になる。

ここで、導電体205aおよび導電体205cは、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子(N2O、NO、NO2など)、銅原子などの不純物の拡散を抑制する機能を有する導電性材料を用いることが好ましい。または、酸素(例えば、酸素原子、酸素分子などの少なくとも一)の拡散を抑制する機能を有する導電性材料を用いることが好ましい。

導電体205aおよび導電体205cに、水素の拡散を低減する機能を有する導電性材料を用いることにより、導電体205bに含まれる水素などの不純物が、絶縁体224等を介して、酸化物230に拡散するのを防ぐことができる。また、導電体205aおよび導電体205cに、酸素の拡散を抑制する機能を有する導電性材料を用いることにより、導電体205bが酸化して導電率が低下することを抑制することができる。酸素の拡散を抑制する機能を有する導電性材料としては、例えば、チタン、窒化チタン、タンタル、窒化タンタル、ルテニウム、酸化ルテニウムなどを用いることが好ましい。したがって、導電体205aおよび導電体205cとしては、上記導電性材料を単層または積層とすればよい。例えば、導電体205aおよび導電体205cは、窒化チタンを用いればよい。

また、導電体205bは、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。例えば、導電体205bは、タングステンを用いればよい。

導電体205は、第2のゲート電極として機能する場合がある。その場合、導電体205に印加する電位を、導電体260に印加する電位と、連動させず、独立して変化させることで、トランジスタ200のしきい値電圧(Vth)を制御することができる。特に、導電体205に負の電位を印加することにより、トランジスタ200のVthをより大きくし、オフ電流を低減することが可能となる。したがって、導電体205に負の電位を印加したほうが、印加しない場合よりも、導電体260に印加する電位が0Vのときのドレイン電流を小さくすることができる。

また、導電体205の電気抵抗率は、上記の導電体205に印加する電位を考慮して設計され、導電体205の膜厚は当該電気抵抗率に合わせて設定される。また、絶縁体216の膜厚は、導電体205とほぼ同じになる。ここで、導電体205の設計が許す範囲で導電体205および絶縁体216の膜厚を薄くすることが好ましい。絶縁体216の膜厚を薄くすることで、絶縁体216中に含まれる水素などの不純物の絶対量を低減することができるので、当該不純物が酸化物230に拡散するのを低減することができる。

なお、導電体205は、図1Aに示すように、酸化物230の導電体242aおよび導電体242bと重ならない領域の大きさよりも、大きく設けるとよい。特に、図1Cに示すように、導電体205は、酸化物230aおよび酸化物230bのチャネル幅方向と交わる端部よりも外側の領域においても、延伸していることが好ましい。つまり、酸化物230のチャネル幅方向における側面の外側において、導電体205と、導電体260とは、絶縁体を介して重畳していることが好ましい。当該構成を有することで、第1のゲート電極として機能する導電体260の電界と、第2のゲート電極として機能する導電体205の電界によって、酸化物230のチャネル形成領域を電気的に取り囲むことができる。本明細書において、第1のゲート、および第2のゲートの電界によって、チャネル形成領域を電気的に取り囲むトランジスタの構造を、surrounded channel(S-channel)構造とよぶ。

なお、本明細書等において、S-channel構造のトランジスタとは、一対のゲート電極の一方および他方の電界によって、チャネル形成領域を電気的に取り囲むトランジスタの構造を表す。また、本明細書等で開示するS-channel構造は、Fin型構造およびプレーナ型構造とは異なる。S-channel構造を採用することで、短チャネル効果に対する耐性を高める、別言すると短チャネル効果が発生し難いトランジスタとすることができる。

また、図1Cに示すように、導電体205は延伸させて、配線としても機能させている。ただし、これに限られることなく、導電体205の下に、配線として機能する導電体を設ける構成にしてもよい。また、導電体205は、必ずしも各トランジスタに一個ずつ設ける必要はない。例えば、導電体205を複数のトランジスタで共有する構成にしてもよい。

なお、トランジスタ200では、導電体205は、導電体205a、導電体205b、および導電体205cを積層する構成について示しているが、本発明はこれに限られるものではない。例えば、導電体205は、単層、2層または4層以上の積層構造として設ける構成にしてもよい。

絶縁体222、および絶縁体224は、ゲート絶縁体として機能する。

絶縁体222は、水素(例えば、水素原子、水素分子などの少なくとも一)の拡散を抑制する機能を有することが好ましい。また、絶縁体222は、酸素(例えば、酸素原子、酸素分子などの少なくとも一)の拡散を抑制する機能を有することが好ましい。例えば、絶縁体222は、絶縁体224よりも水素および酸素の一方または双方の拡散を抑制する機能を有することが好ましい。

絶縁体222は、絶縁性材料であるアルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体を用いるとよい。当該絶縁体として、酸化アルミニウム、酸化ハフニウム、アルミニウムおよびハフニウムを含む酸化物(ハフニウムアルミネート)などを用いることが好ましい。このような材料を用いて絶縁体222を形成した場合、絶縁体222は、酸化物230から基板側への酸素の放出や、トランジスタ200の周辺部から酸化物230への水素等の不純物の拡散を抑制する層として機能する。よって、絶縁体222を設けることで、水素等の不純物が、トランジスタ200の内側へ拡散することを抑制し、酸化物230中の酸素欠損の生成を抑制することができる。また、導電体205が、絶縁体224や、酸化物230が有する酸素と反応することを抑制することができる。

または、上記絶縁体に、例えば、酸化アルミニウム、酸化ビスマス、酸化ゲルマニウム、酸化ニオブ、酸化シリコン、酸化チタン、酸化タングステン、酸化イットリウム、酸化ジルコニウムを添加してもよい。または、これらの絶縁体を窒化処理してもよい。また、絶縁体222は、これらの絶縁体に酸化シリコン、酸化窒化シリコンまたは窒化シリコンを積層して用いてもよい。

また、絶縁体222は、例えば、酸化アルミニウム、酸化ハフニウム、酸化タンタル、酸化ジルコニウム、チタン酸ジルコン酸鉛(PZT)、チタン酸ストロンチウム(SrTiO3)、(Ba,Sr)TiO3(BST)などのいわゆるhigh-k材料を含む絶縁体を単層または積層で用いてもよい。トランジスタの微細化、および高集積化が進むと、ゲート絶縁体の薄膜化により、リーク電流などの問題が生じる場合がある。ゲート絶縁体として機能する絶縁体にhigh-k材料を用いることで、物理膜厚を保ちながら、トランジスタ動作時のゲート電位の低減が可能となる。

酸化物230と接する絶縁体224は、過剰酸素を含む(加熱により酸素を脱離する)ことが好ましい。例えば、絶縁体224は、酸化シリコン、酸化窒化シリコンなどを適宜用いればよい。酸素を含む絶縁体を酸化物230に接して設けることにより、酸化物230中の酸素欠損を低減し、トランジスタ200の信頼性を向上させることができる。

絶縁体224として、具体的には、加熱により一部の酸素が脱離する酸化物材料、別言すると、過剰酸素領域を有する絶縁体材料を用いることが好ましい。加熱により酸素を脱離する酸化膜とは、TDS(Thermal Desorption Spectroscopy)分析にて、酸素分子の脱離量が1.0×1018molecules/cm3以上、好ましくは1.0×1019molecules/cm3以上、さらに好ましくは2.0×1019molecules/cm3以上、または3.0×1020molecules/cm3以上である酸化膜である。なお、上記TDS分析時における膜の表面温度としては100℃以上700℃以下、または100℃以上400℃以下の範囲が好ましい。

また、トランジスタ200の作製工程中において、酸化物230の表面が露出した状態で、加熱処理を行うと好適である。当該加熱処理は、例えば、100℃以上600℃以下、より好ましくは350℃以上550℃以下で行えばよい。なお、加熱処理は、窒素ガスもしくは不活性ガスの雰囲気、または酸化性ガスを10ppm以上、1%以上、もしくは10%以上含む雰囲気で行う。例えば、加熱処理は酸素雰囲気で行うことが好ましい。これにより、酸化物230に酸素を供給して、酸素欠損の低減を図ることができる。また、加熱処理は減圧状態で行ってもよい。または、加熱処理は、窒素ガスもしくは不活性ガスの雰囲気で加熱処理した後に、脱離した酸素を補うために、酸化性ガスを10ppm以上、1%以上、または10%以上含む雰囲気で行ってもよい。または、酸化性ガスを10ppm以上、1%以上、または10%以上含む雰囲気で加熱処理した後に、連続して窒素ガスもしくは不活性ガスの雰囲気で加熱処理を行っても良い。

なお、酸化物230に加酸素化処理を行うことで、酸化物230中の酸素欠損を、供給された酸素により修復させる、別言すると「VO+O→null」という反応を促進させることができる。さらに、酸化物230中に残存した水素に供給された酸素が反応することで、当該水素をH2Oとして除去する(脱水化する)ことができる。これにより、酸化物230中に残存していた水素が酸素欠損に再結合してVOHが形成されるのを抑制することができる。

なお、絶縁体222、および絶縁体224が、2層以上の積層構造を有していてもよい。その場合、同じ材料からなる積層構造に限定されず、異なる材料からなる積層構造でもよい。また、絶縁体224は、酸化物230aと重畳して島状に形成してもよい。この場合、絶縁体275が、絶縁体224の側面および絶縁体222の上面に接する構成になる。

導電体242a、および導電体242bは酸化物230bの上面に接して設けられることが好ましい。導電体242aおよび導電体242bは、それぞれトランジスタ200のソース電極またはドレイン電極として機能する。

導電体242aおよび導電体242bとしては、例えば、タンタルを含む窒化物、チタンを含む窒化物、モリブデンを含む窒化物、タングステンを含む窒化物、タンタルおよびアルミニウムを含む窒化物、チタンおよびアルミニウムを含む窒化物などを用いることが好ましい。本発明の一態様においては、タンタルを含む窒化物が特に好ましい。また、例えば、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物などを用いてもよい。これらの材料は、酸化しにくい導電性材料、または、酸素を吸収しても導電性を維持する材料であるため、好ましい。

なお、酸化物230bなどに含まれる水素が、導電体242aまたは導電体242bに拡散する場合がある。特に、導電体242aおよび導電体242bに、タンタルを含む窒化物を用いることで、酸化物230bなどに含まれる水素は、導電体242aまたは導電体242bに拡散しやすく、拡散した水素は、導電体242aまたは導電体242bが有する窒素と結合することがある。つまり、酸化物230bなどに含まれる水素は、導電体242aまたは導電体242bに吸い取られる場合がある。

また、導電体242aの側面と導電体242aの上面との間、および導電体242bの側面と導電体242bの上面との間に、湾曲面が形成されないことが好ましい。当該湾曲面が形成されない導電体242aおよび導電体242bとすることで、図1Dに示すような、チャネル幅方向の断面における、導電体242aおよび導電体242bの断面積を大きくすることができる。これにより、導電体242aおよび導電体242bの導電率を大きくし、トランジスタ200のオン電流を大きくすることができる。

絶縁体275は、絶縁体224、酸化物230a、酸化物230b、導電体242a、および導電体242bを覆って設けられており、絶縁体250、および導電体260が設けられる領域に開口が形成されている。絶縁体275は、絶縁体224の上面、酸化物230aの側面、酸化物230bの側面、導電体242aの側面および上面、ならびに導電体242bの側面および上面に接して絶縁体275aが設けられ、絶縁体275a上に絶縁体275bが設けられることが好ましい。

なお、トランジスタ200では、絶縁体275が、絶縁体275a、および絶縁体275bの2層を積層する構成について示しているが、本発明はこれに限られるものではない。例えば、単層、または3層以上の積層構造を設ける構成にしてもよいし、絶縁体275a、および絶縁体275bのそれぞれが積層構造を有していてもよい。

絶縁体275は、酸素の透過を抑制するバリア絶縁膜として機能することが好ましい。また、絶縁体275は、水、水素などの不純物が、上方から絶縁体224に拡散するのを抑制するバリア絶縁膜として機能することが好ましく、水素などの不純物を捕獲する機能を有することが好ましい。その場合、絶縁体275としては、アモルファス構造を有する金属酸化物、例えば、酸化アルミニウムまたは酸化マグネシウムなどの絶縁体を含むことが好ましい。絶縁体275としては、例えば、酸化アルミニウム、および窒化シリコンなどの絶縁体を単層で、または積層して用いればよい。絶縁体275として、酸化アルミニウム、および窒化シリコンを積層して用いる場合、絶縁体275aとして酸化アルミニウムを設け、絶縁体275bとして窒化シリコンを設けることが好ましい。

また、絶縁体275の少なくとも一部に酸化アルミニウムを用いる場合、該酸化アルミニウムは、アモルファス構造を有する酸化アルミニウム、またはアモルファス構造の酸化アルミニウムであることが好ましい。アモルファス構造を有する金属酸化物、特に、アモルファス構造を有する酸化アルミニウム、およびアモルファス構造の酸化アルミニウムは、周囲に存在する水素を捕獲または固着することができる場合があるため、良好な特性を有し、信頼性の高いトランジスタ200、および半導体装置を作製することができる。

絶縁体212と絶縁体283に挟まれた領域内で、絶縁体280、または絶縁体224に接して、水素などの不純物を捕獲する機能を有する、絶縁体275を設けることで、絶縁体280、または絶縁体224に含まれる水素などの不純物を捕獲し、当該領域内における、水素の量を一定値にすることができる。この場合は、絶縁体275として、酸化アルミニウムなどを用いることが好ましい。

絶縁体250(絶縁体250a、および絶縁体250b)は、ゲート絶縁体として機能する。酸化物230bの上面に接して絶縁体250aが配置され、絶縁体250a上に絶縁体250bが配置される。絶縁体250は、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコンなどを用いることができる。特に、酸化シリコン、および酸化窒化シリコンは熱に対し安定であるため好ましい。

絶縁体250は、絶縁体224と同様に、絶縁体250中の水、水素などの不純物濃度が低減されていることが好ましい。絶縁体250の膜厚は、1nm以上20nm以下とするのが好ましい。

絶縁体250aは、加熱により酸素が放出される絶縁体を用いて形成し、絶縁体250bは、酸素の拡散を抑制する機能を有する絶縁体を用いて形成することが好ましい。このような構成にすることで、絶縁体250aに含まれる酸素が、導電体260へ拡散するのを抑制することができる。つまり、酸化物230へ供給する酸素量の減少を抑制することができる。また、絶縁体250aに含まれる酸素による導電体260の酸化を抑制することができる。例えば、絶縁体250aは、上述した絶縁体250に用いることができる材料を用いて設け、絶縁体250bは、絶縁体222と同様の材料を用いて設けることができる。

なお、絶縁体250aに酸化シリコンや酸化窒化シリコンなどを用いる場合、絶縁体250bは、比誘電率が高いhigh-k材料である絶縁性材料を用いてもよい。ゲート絶縁体を、絶縁体250aと絶縁体250bとの積層構造とすることで、熱に対して安定、かつ比誘電率の高い積層構造とすることができる。したがって、ゲート絶縁体の物理膜厚を保持したまま、トランジスタ動作時に印加するゲート電位の低電位化が可能となる。また、ゲート絶縁体として機能する絶縁体の等価酸化膜厚(EOT)の薄膜化が可能となる。

絶縁体250bとして、具体的には、ハフニウム、アルミニウム、ガリウム、イットリウム、ジルコニウム、タングステン、チタン、タンタル、ニッケル、ゲルマニウム、マグネシウムなどから選ばれた一種、もしくは二種以上が含まれた金属酸化物、または酸化物230として用いることができる金属酸化物を用いることができる。特に、アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体を用いることが好ましい。例えば、絶縁体250として、酸化シリコンと、該酸化シリコン上の酸化ハフニウムを含む積層構造を用いればよい。

絶縁体250を2層の積層構造にすることで、絶縁体250の物理的な厚みにより、導電体260と、酸化物230との間の距離を保つことで、導電体260と酸化物230との間のリーク電流を抑制することができる。また、導電体260と酸化物230との間の物理的な距離、および導電体260から酸化物230へかかる電界強度を、容易に適宜調整することができる。

なお、図1Bおよび図1Cでは、絶縁体250を2層の積層構造で図示したが、単層、または3層以上の積層構造としてもよい。

また、絶縁体250と導電体260との間に金属酸化物を設けてもよい。当該金属酸化物は、絶縁体250から導電体260への酸素の拡散を抑制することが好ましい。酸素の拡散を抑制する金属酸化物を設けることで、絶縁体250から導電体260への酸素の拡散が抑制される。つまり、酸化物230へ供給する酸素量の減少を抑制することができる。また、絶縁体250の酸素による導電体260の酸化を抑制することができる。

なお、上記金属酸化物は、第1のゲート電極の一部としての機能を有する構成にしてもよい。例えば、酸化物230として用いることができる金属酸化物を、上記金属酸化物として用いることができる。その場合、導電体260aをスパッタリング法で成膜することで、上記金属酸化物の電気抵抗値を低下させて導電体とすることができる。これをOC(Oxide Conductor)電極と呼ぶことができる。上記金属酸化物を有することで、導電体260からの電界の影響を弱めることなく、トランジスタ200のオン電流の向上を図ることができる。

導電体260は、トランジスタ200の第1のゲート電極として機能する。導電体260は、導電体260aと、導電体260aの上に配置された導電体260bと、を有することが好ましい。例えば、導電体260aは、導電体260bの底面および側面を包むように配置されることが好ましい。また、図1Bおよび図1Cに示すように、導電体260の上面は、絶縁体250の上面と略一致している。なお、図1Bおよび図1Cでは、導電体260は、導電体260aと導電体260bの2層構造として示しているが、単層構造でもよいし、3層以上の積層構造であってもよい。

導電体260aは、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子、銅原子などの不純物の拡散を抑制する機能を有する導電性材料を用いることが好ましい。または、酸素(例えば、酸素原子、酸素分子などの少なくとも一)の拡散を抑制する機能を有する導電性材料を用いることが好ましい。

また、導電体260aが酸素の拡散を抑制する機能を持つことにより、絶縁体250に含まれる酸素により、導電体260bが酸化して導電率が低下することを抑制することができる。酸素の拡散を抑制する機能を有する導電性材料としては、例えば、チタン、窒化チタン、タンタル、窒化タンタル、ルテニウム、酸化ルテニウムなどを用いることが好ましい。

また、導電体260は、配線としても機能するため、導電性が高い導電体を用いることが好ましい。例えば、導電体260bは、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることができる。また、導電体260bは積層構造としてもよく、例えば、チタンまたは窒化チタンと上記導電性材料との積層構造としてもよい。

また、トランジスタ200では、導電体260は、絶縁体280などに形成されている開口を埋めるように自己整合的に形成される。導電体260をこのように形成することにより、導電体242aと導電体242bとの間の領域に、導電体260を位置合わせすることなく確実に配置することができる。

また、図1Cに示すように、トランジスタ200のチャネル幅方向において、導電体260の、導電体260と酸化物230bとが重ならない領域の底面は、酸化物230bの底面より低いことが好ましい。ゲート電極として機能する導電体260が、絶縁体250などを介して、酸化物230bのチャネル形成領域の側面および上面を覆う構成とすることで、導電体260の電界を酸化物230bのチャネル形成領域全体に作用させやすくなる。よって、トランジスタ200のオン電流を増大させ、周波数特性を向上させることができる。絶縁体222の底面を基準としたとき、酸化物230aおよび酸化物230bと、導電体260とが、重ならない領域における導電体260の底面の高さと、酸化物230bの底面の高さと、の差は、0nm以上100nm以下、好ましくは3nm以上50nm以下、より好ましくは5nm以上20nm以下とする。

絶縁体280は、絶縁体275上に設けられ、絶縁体250、および導電体260が設けられる領域に開口が形成されている。また、絶縁体280の上面は、平坦化されていてもよい。

絶縁体280は、絶縁体224と同様に、過剰酸素領域または過剰酸素を有することが好ましい。また、絶縁体280中の水、水素などの不純物濃度は低減されていることが好ましい。例えば、絶縁体280は、酸化シリコン、酸化窒化シリコンなどのシリコンを含む酸化物を適宜用いればよい。過剰酸素を有する絶縁体を酸化物230に接して設けることにより、酸化物230中の酸素欠損を低減し、トランジスタ200の信頼性を向上させることができる。また、絶縁体280は、上記の材料が積層された構造でもよく、例えば、スパッタリング法で成膜した酸化シリコンと、その上に積層されたCVD法で成膜された酸化窒化シリコンの積層構造とすればよい。また、さらに上に窒化シリコンを積層してもよい。

絶縁体282は、水、水素などの不純物が、上方から絶縁体280に拡散するのを抑制するバリア絶縁膜として機能することが好ましく、水素などの不純物を捕獲する機能を有することが好ましい。また、絶縁体282は、酸素の透過を抑制するバリア絶縁膜として機能することが好ましい。絶縁体282としては、アモルファス構造を有する金属酸化物、例えば、酸化アルミニウムなどの絶縁体を用いればよい。絶縁体212と絶縁体283に挟まれた領域内で、絶縁体280に接して、水素などの不純物を捕獲する機能を有する、絶縁体282を設けることで、絶縁体280などに含まれる水素などの不純物を捕獲し、当該領域内における、水素の量を一定値にすることができる。特に、絶縁体282として、アモルファス構造を有する酸化アルミニウム、またはアモルファス構造の酸化アルミニウムを用いることで、より効果的に水素を捕獲または固着できる場合があるため好ましい。これにより、良好な特性を有し、信頼性の高いトランジスタ200、および半導体装置を作製することができる。

絶縁体283は、水、水素などの不純物が、上方から絶縁体280に拡散するのを抑制するバリア絶縁膜として機能する。絶縁体283は、絶縁体282の上に配置される。絶縁体283としては、窒化シリコンまたは窒化酸化シリコンなどの、シリコンを含む窒化物を用いることが好ましい。例えば、絶縁体283としてスパッタリング法で成膜された窒化シリコンを用いればよい。絶縁体283をスパッタリング法で成膜することで、密度が高く、鬆などが形成されにくい窒化シリコン膜を形成することができる。また、絶縁体283として、スパッタリング法で成膜された窒化シリコンの上に、さらに、CVD法で成膜された窒化シリコンを積層してもよい。

導電体240aおよび導電体240bは、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。また、導電体240aおよび導電体240bは積層構造としてもよい。

また、導電体240aおよび導電体240bのそれぞれを積層構造とする場合、絶縁体283、絶縁体282、絶縁体280、および絶縁体275と接する導電体には、水、水素などの不純物の透過を抑制する機能を有する導電性材料を用いることが好ましい。例えば、タンタル、窒化タンタル、チタン、窒化チタン、ルテニウム、酸化ルテニウムなどを用いることが好ましい。また、水、水素などの不純物の透過を抑制する機能を有する導電性材料は、単層または積層で用いてもよい。また、絶縁体283より上層に含まれる水、水素などの不純物が、導電体240aおよび導電体240bを通じて酸化物230に混入するのを抑制することができる。

絶縁体241aおよび絶縁体241bとしては、例えば、窒化シリコン、酸化アルミニウム、窒化酸化シリコンなどの絶縁体を用いればよい。絶縁体241aおよび絶縁体241bは、絶縁体283、絶縁体282、および絶縁体275に接して設けられるので、絶縁体280などに含まれる水、水素などの不純物が、導電体240aおよび導電体240bを通じて酸化物230に混入するのを抑制することができる。特に、窒化シリコンは水素に対するブロッキング性が高いので好適である。また、絶縁体280に含まれる酸素が導電体240aおよび導電体240bに吸収されるのを防ぐことができる。

また、導電体240aの上面、および導電体240bの上面に接して、配線として機能する導電体246a、および導電体246bを配置してもよい。導電体246a、および導電体246bは、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。また、当該導電体は、積層構造としてもよく、例えば、チタンまたは窒化チタンと上記導電性材料との積層としてもよい。なお、当該導電体は、絶縁体に設けられた開口に埋め込むように形成してもよい。

絶縁体286は、導電体246a上、導電体246b上、および絶縁体283上に設けられる。これにより、導電体246aの上面、導電体246aの側面、導電体246bの上面、および導電体246bの側面は、絶縁体286と接し、導電体246aの下面、および導電体246bの下面は、絶縁体283と接する。つまり、導電体246aおよび導電体246bは、絶縁体283、および絶縁体286で包まれる構成とすることができる。この様な構成とすることで、外方からの酸素の透過を抑制し、導電体246aおよび導電体246bの酸化を防止することができる。また、導電体246aおよび導電体246bから、水、水素などの不純物が外部に拡散することを防ぐことができるので好ましい。

<半導体装置の構成材料>

以下では、半導体装置に用いることができる構成材料について説明する。

<<基板>>

トランジスタ200を形成する基板としては、例えば、絶縁体基板、半導体基板、または導電体基板を用いればよい。絶縁体基板としては、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板(イットリア安定化ジルコニア基板など)、樹脂基板などがある。また、半導体基板としては、例えば、シリコン、ゲルマニウムを材料とした半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムからなる化合物半導体基板などがある。さらには、前述の半導体基板内部に絶縁体領域を有する半導体基板、例えば、SOI(Silicon On Insulator)基板などがある。導電体基板としては、黒鉛基板、金属基板、合金基板、導電性樹脂基板などがある。または、金属の窒化物を有する基板、金属の酸化物を有する基板などがある。さらには、絶縁体基板に導電体または半導体が設けられた基板、半導体基板に導電体または絶縁体が設けられた基板、導電体基板に半導体または絶縁体が設けられた基板などがある。または、これらの基板に素子が設けられたものを用いてもよい。基板に設けられる素子としては、容量素子、抵抗素子、スイッチ素子、発光素子、記憶素子などがある。

<<絶縁体>>

絶縁体としては、絶縁性を有する酸化物、窒化物、酸化窒化物、窒化酸化物、金属酸化物、金属酸化窒化物、金属窒化酸化物などがある。

例えば、トランジスタの微細化、および高集積化が進むと、ゲート絶縁体の薄膜化により、リーク電流などの問題が生じる場合がある。ゲート絶縁体として機能する絶縁体に、high-k材料を用いることで物理膜厚を保ちながら、トランジスタ動作時の低電圧化が可能となる。一方、層間膜として機能する絶縁体には、比誘電率が低い材料を用いることで、配線間に生じる寄生容量を低減することができる。したがって、絶縁体の機能に応じて、材料を選択するとよい。

また、比誘電率の高い絶縁体としては、酸化ガリウム、酸化ハフニウム、酸化ジルコニウム、アルミニウムおよびハフニウムを有する酸化物、アルミニウムおよびハフニウムを有する酸化窒化物、シリコンおよびハフニウムを有する酸化物、シリコンおよびハフニウムを有する酸化窒化物、またはシリコンおよびハフニウムを有する窒化物などがある。

また、比誘電率が低い絶縁体としては、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコン、または樹脂などがある。

また、金属酸化物を用いたトランジスタは、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体で囲うことによって、トランジスタの電気特性を安定にすることができる。水素などの不純物および酸素の透過を抑制する機能を有する絶縁体としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウム、またはタンタルを含む絶縁体を、単層で、または積層で用いればよい。具体的には、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体として、酸化アルミニウム、酸化マグネシウム、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタルなどの金属酸化物、窒化アルミニウム、窒化酸化シリコン、窒化シリコンなどの金属窒化物を用いることができる。

また、ゲート絶縁体として機能する絶縁体は、加熱により脱離する酸素を含む領域を有する絶縁体であることが好ましい。例えば、加熱により脱離する酸素を含む領域を有する酸化シリコンまたは酸化窒化シリコンを酸化物230と接する構造とすることで、酸化物230が有する酸素欠損を補償することができる。

<<導電体>>

導電体としては、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タングステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニウム、ベリリウム、インジウム、ルテニウム、イリジウム、ストロンチウム、ランタンなどから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いることが好ましい。例えば、窒化タンタル、窒化チタン、タングステン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物などを用いることが好ましい。また、窒化タンタル、窒化チタン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物は、酸化しにくい導電性材料、または、酸素を吸収しても導電性を維持する材料であるため、好ましい。また、リン等の不純物元素を含有させた多結晶シリコンに代表される、電気伝導度が高い半導体、ニッケルシリサイドなどのシリサイドを用いてもよい。

また、上記の材料で形成される導電層を複数積層して用いてもよい。例えば、前述した金属元素を含む材料と、酸素を含む導電性材料と、を組み合わせた積層構造としてもよい。また、前述した金属元素を含む材料と、窒素を含む導電性材料と、を組み合わせた積層構造としてもよい。また、前述した金属元素を含む材料と、酸素を含む導電性材料と、窒素を含む導電性材料と、を組み合わせた積層構造としてもよい。

なお、トランジスタのチャネル形成領域に酸化物を用いる場合において、ゲート電極として機能する導電体には、前述した金属元素を含む材料と、酸素を含む導電性材料と、を組み合わせた積層構造を用いることが好ましい。この場合は、酸素を含む導電性材料をチャネル形成領域側に設けるとよい。酸素を含む導電性材料をチャネル形成領域側に設けることで、当該導電性材料から離脱した酸素がチャネル形成領域に供給されやすくなる。

特に、ゲート電極として機能する導電体として、チャネルが形成される金属酸化物に含まれる金属元素および酸素を含む導電性材料を用いることが好ましい。また、前述した金属元素および窒素を含む導電性材料を用いてもよい。例えば、窒化チタン、窒化タンタルなどの窒素を含む導電性材料を用いてもよい。また、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、シリコンを添加したインジウム錫酸化物を用いてもよい。また、窒素を含むインジウムガリウム亜鉛酸化物を用いてもよい。このような材料を用いることで、チャネルが形成される金属酸化物に含まれる水素を捕獲することができる場合がある。または、外方の絶縁体などから混入する水素を捕獲することができる場合がある。

<<金属酸化物>>

酸化物230として、半導体として機能する金属酸化物(酸化物半導体)を用いることが好ましい。以下では、本発明に係る酸化物230に適用可能な金属酸化物について説明する。

金属酸化物は、少なくともインジウムまたは亜鉛を含むことが好ましい。特に、インジウムおよび亜鉛を含むことが好ましい。また、それらに加えて、アルミニウム、ガリウム、イットリウム、錫などが含まれていることが好ましい。また、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、マグネシウム、コバルトなどから選ばれた一種、または複数種が含まれていてもよい。

ここでは、金属酸化物が、インジウム、元素Mおよび亜鉛を有するIn-M-Zn酸化物である場合を考える。なお、元素Mは、アルミニウム、ガリウム、イットリウム、または錫とする。そのほかの元素Mに適用可能な元素としては、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、マグネシウム、コバルトなどがある。ただし、元素Mとして、前述の元素を複数組み合わせても構わない場合がある。

なお、本明細書等において、窒素を有する金属酸化物も金属酸化物(metal oxide)と総称する場合がある。また、窒素を有する金属酸化物を、金属酸窒化物(metal oxynitride)と呼称してもよい。

<結晶構造の分類>

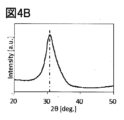

まず、酸化物半導体における、結晶構造の分類について、図4Aを用いて説明を行う。図4Aは、酸化物半導体、代表的にはIGZO(Inと、Gaと、Znと、を含む金属酸化物)の結晶構造の分類を説明する図である。

図4Aに示すように、酸化物半導体は、大きく分けて「Amorphous(無定形)」と、「Crystalline(結晶性)」と、「Crystal(結晶)」と、に分類される。また、「Amorphous」の中には、completely amorphousが含まれる。また、「Crystalline」の中には、CAAC(c-axis-aligned crystalline)、nc(nanocrystalline)、及びCAC(cloud-aligned composite)が含まれる(excluding single crystal and poly crystal)。なお、「Crystalline」の分類には、single crystal、poly crystal、及びcompletely amorphousは除かれる。また、「Crystal」の中には、single crystal、及びpoly crystalが含まれる。

なお、図4Aに示す太枠内の構造は、「Amorphous(無定形)」と、「Crystal(結晶)」との間の中間状態であり、新しい境界領域(New crystalline phase)に属する構造である。すなわち、当該構造は、エネルギー的に不安定な「Amorphous(無定形)」や、「Crystal(結晶)」とは全く異なる構造と言い換えることができる。

なお、膜または基板の結晶構造は、X線回折(XRD:X-Ray Diffraction)スペクトルを用いて評価することができる。ここで、「Crystalline」に分類されるCAAC-IGZO膜のGIXD(Grazing-Incidence XRD)測定で得られるXRDスペクトルを図4Bに示す。なお、GIXD法は、薄膜法またはSeemann-Bohlin法ともいう。以降、図4Bに示すGIXD測定で得られるXRDスペクトルを、単にXRDスペクトルと記す。なお、図4Bに示すCAAC-IGZO膜の組成は、In:Ga:Zn=4:2:3[原子数比]近傍である。また、図4Bに示すCAAC-IGZO膜の厚さは、500nmである。

図4Bでは、横軸は2θ[deg.]であり、縦軸は強度(Intensity)[a.u.]である。図4Bに示すように、CAAC-IGZO膜のXRDスペクトルでは、明確な結晶性を示すピークが検出される。具体的には、CAAC-IGZO膜のXRDスペクトルでは、2θ=31°近傍に、c軸配向を示すピークが検出される。なお、図4Bに示すように、2θ=31°近傍のピークは、ピーク強度が検出された角度を軸に左右非対称である。

また、膜または基板の結晶構造は、極微電子線回折法(NBED:Nano Beam Electron Diffraction)によって観察される回折パターン(極微電子線回折パターンともいう。)にて評価することができる。CAAC-IGZO膜の回折パターンを、図4Cに示す。図4Cは、電子線を基板に対して平行に入射するNBEDによって観察される回折パターンである。なお、図4Cに示すCAAC-IGZO膜の組成は、In:Ga:Zn=4:2:3[原子数比]近傍である。また、極微電子線回折法では、プローブ径を1nmとして電子線回折が行われる。

図4Cに示すように、CAAC-IGZO膜の回折パターンでは、c軸配向を示す複数のスポットが観察される。

<<酸化物半導体の構造>>

なお、酸化物半導体は、結晶構造に着目した場合、図4Aとは異なる分類となる場合がある。例えば、酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体と、に分けられる。非単結晶酸化物半導体としては、例えば、上述のCAAC-OS、及びnc-OSがある。また、非単結晶酸化物半導体には、多結晶酸化物半導体、擬似非晶質酸化物半導体(a-like OS:amorphous-like oxide semiconductor)、非晶質酸化物半導体、などが含まれる。

ここで、上述のCAAC-OS、nc-OS、及びa-like OSの詳細について、説明を行う。

[CAAC-OS]

CAAC-OSは、複数の結晶領域を有し、当該複数の結晶領域はc軸が特定の方向に配向している酸化物半導体である。なお、特定の方向とは、CAAC-OS膜の厚さ方向、CAAC-OS膜の被形成面の法線方向、またはCAAC-OS膜の表面の法線方向である。また、結晶領域とは、原子配列に周期性を有する領域である。なお、原子配列を格子配列とみなすと、結晶領域とは、格子配列の揃った領域でもある。さらに、CAAC-OSは、a-b面方向において複数の結晶領域が連結する領域を有し、当該領域は歪みを有する場合がある。なお、歪みとは、複数の結晶領域が連結する領域において、格子配列の揃った領域と、別の格子配列の揃った領域と、の間で格子配列の向きが変化している箇所を指す。つまり、CAAC-OSは、c軸配向し、a-b面方向には明らかな配向をしていない酸化物半導体である。

なお、上記複数の結晶領域のそれぞれは、1つまたは複数の微小な結晶(最大径が10nm未満である結晶)で構成される。結晶領域が1つの微小な結晶で構成されている場合、当該結晶領域の最大径は10nm未満となる。また、結晶領域が多数の微小な結晶で構成されている場合、当該結晶領域の大きさは、数十nm程度となる場合がある。

また、In-M-Zn酸化物(元素Mは、アルミニウム、ガリウム、イットリウム、スズ、チタンなどから選ばれた一種、または複数種)において、CAAC-OSは、インジウム(In)、及び酸素を有する層(以下、In層)と、元素M、亜鉛(Zn)、及び酸素を有する層(以下、(M,Zn)層)とが積層した、層状の結晶構造(層状構造ともいう)を有する傾向がある。なお、インジウムと元素Mは、互いに置換可能である。よって、(M,Zn)層にはインジウムが含まれる場合がある。また、In層には元素Mが含まれる場合がある。なお、In層にはZnが含まれる場合もある。当該層状構造は、例えば、高分解能TEM像において、格子像として観察される。

CAAC-OS膜に対し、例えば、XRD装置を用いて構造解析を行うと、θ/2θスキャンを用いたOut-of-plane XRD測定では、c軸配向を示すピークが2θ=31°またはその近傍に検出される。なお、c軸配向を示すピークの位置(2θの値)は、CAAC-OSを構成する金属元素の種類、組成などにより変動する場合がある。

また、例えば、CAAC-OS膜の電子線回折パターンにおいて、複数の輝点(スポット)が観測される。なお、あるスポットと別のスポットとは、試料を透過した入射電子線のスポット(ダイレクトスポットともいう。)を対称中心として、点対称の位置に観測される。

上記特定の方向から結晶領域を観察した場合、当該結晶領域内の格子配列は、六方格子を基本とするが、単位格子は正六角形とは限らず、非正六角形である場合がある。また、上記歪みにおいて、五角形、七角形などの格子配列を有する場合がある。なお、CAAC-OSにおいて、歪み近傍においても、明確な結晶粒界(グレインバウンダリー)を確認することはできない。即ち、格子配列の歪みによって、結晶粒界の形成が抑制されていることがわかる。これは、CAAC-OSが、a-b面方向において酸素原子の配列が稠密でないことや、金属原子が置換することで原子間の結合距離が変化することなどによって、歪みを許容することができるためと考えられる。

なお、明確な結晶粒界が確認される結晶構造は、いわゆる多結晶(polycrystal)と呼ばれる。結晶粒界は、再結合中心となり、キャリアが捕獲されトランジスタのオン電流の低下、電界効果移動度の低下などを引き起こす可能性が高い。よって、明確な結晶粒界が確認されないCAAC-OSは、トランジスタの半導体層に好適な結晶構造を有する結晶性の酸化物の一つである。なお、CAAC-OSを構成するには、Znを有する構成が好ましい。例えば、In-Zn酸化物、及びIn-Ga-Zn酸化物は、In酸化物よりも結晶粒界の発生を抑制できるため好適である。

CAAC-OSは、結晶性が高く、明確な結晶粒界が確認されない酸化物半導体である。よって、CAAC-OSは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。また、酸化物半導体の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、CAAC-OSは不純物や欠陥(酸素欠損など)の少ない酸化物半導体ともいえる。従って、CAAC-OSを有する酸化物半導体は、物理的性質が安定する。そのため、CAAC-OSを有する酸化物半導体は熱に強く、信頼性が高い。また、CAAC-OSは、製造工程における高い温度(所謂サーマルバジェット)に対しても安定である。したがって、OSトランジスタにCAAC-OSを用いると、製造工程の自由度を広げることが可能となる。

[nc-OS]

nc-OSは、微小な領域(例えば、1nm以上10nm以下の領域、特に1nm以上3nm以下の領域)において原子配列に周期性を有する。別言すると、nc-OSは、微小な結晶を有する。なお、当該微小な結晶の大きさは、例えば、1nm以上10nm以下、特に1nm以上3nm以下であることから、当該微小な結晶をナノ結晶ともいう。また、nc-OSは、異なるナノ結晶間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、nc-OSは、分析方法によっては、a-like OSや非晶質酸化物半導体と区別が付かない場合がある。例えば、nc-OS膜に対し、XRD装置を用いて構造解析を行うと、θ/2θスキャンを用いたOut-of-plane XRD測定では、結晶性を示すピークが検出されない。また、nc-OS膜に対し、ナノ結晶よりも大きいプローブ径(例えば50nm以上)の電子線を用いる電子線回折(制限視野電子線回折ともいう。)を行うと、ハローパターンのような回折パターンが観測される。一方、nc-OS膜に対し、ナノ結晶の大きさと近いかナノ結晶より小さいプローブ径(例えば1nm以上30nm以下)の電子線を用いる電子線回折(ナノビーム電子線回折ともいう。)を行うと、ダイレクトスポットを中心とするリング状の領域内に複数のスポットが観測される電子線回折パターンが取得される場合がある。

[a-like OS]

a-like OSは、nc-OSと非晶質酸化物半導体との間の構造を有する酸化物半導体である。a-like OSは、鬆又は低密度領域を有する。即ち、a-like OSは、nc-OS及びCAAC-OSと比べて、結晶性が低い。また、a-like OSは、nc-OS及びCAAC-OSと比べて、膜中の水素濃度が高い。

<<酸化物半導体の構成>>

次に、上述のCAC-OSの詳細について、説明を行う。なお、CAC-OSは材料構成に関する。

[CAC-OS]

CAC-OSとは、例えば、金属酸化物を構成する元素が、0.5nm以上10nm以下、好ましくは、1nm以上3nm以下、またはその近傍のサイズで偏在した材料の一構成である。なお、以下では、金属酸化物において、一つまたは複数の金属元素が偏在し、該金属元素を有する領域が、0.5nm以上10nm以下、好ましくは、1nm以上3nm以下、またはその近傍のサイズで混合した状態をモザイク状、またはパッチ状ともいう。

さらに、CAC-OSとは、第1の領域と、第2の領域と、に材料が分離することでモザイク状となり、当該第1の領域が、膜中に分布した構成(以下、クラウド状ともいう。)である。つまり、CAC-OSは、当該第1の領域と、当該第2の領域とが、混合している構成を有する複合金属酸化物である。

ここで、In-Ga-Zn酸化物におけるCAC-OSを構成する金属元素に対するIn、Ga、およびZnの原子数比のそれぞれを、[In]、[Ga]、および[Zn]と表記する。例えば、In-Ga-Zn酸化物におけるCAC-OSにおいて、第1の領域は、[In]が、CAC-OS膜の組成における[In]よりも大きい領域である。また、第2の領域は、[Ga]が、CAC-OS膜の組成における[Ga]よりも大きい領域である。または、例えば、第1の領域は、[In]が、第2の領域における[In]よりも大きく、且つ、[Ga]が、第2の領域における[Ga]よりも小さい領域である。また、第2の領域は、[Ga]が、第1の領域における[Ga]よりも大きく、且つ、[In]が、第1の領域における[In]よりも小さい領域である。

具体的には、上記第1の領域は、インジウム酸化物、インジウム亜鉛酸化物などが主成分である領域である。また、上記第2の領域は、ガリウム酸化物、ガリウム亜鉛酸化物などが主成分である領域である。つまり、上記第1の領域を、Inを主成分とする領域と言い換えることができる。また、上記第2の領域を、Gaを主成分とする領域と言い換えることができる。

なお、上記第1の領域と、上記第2の領域とは、明確な境界が観察できない場合がある。

例えば、In-Ga-Zn酸化物におけるCAC-OSでは、エネルギー分散型X線分光法(EDX:Energy Dispersive X-ray spectroscopy)を用いて取得したEDXマッピングにより、Inを主成分とする領域(第1の領域)と、Gaを主成分とする領域(第2の領域)とが、偏在し、混合している構造を有することが確認できる。

CAC-OSをトランジスタに用いる場合、第1の領域に起因する導電性と、第2の領域に起因する絶縁性とが、相補的に作用することにより、スイッチングさせる機能(On/Offさせる機能)をCAC-OSに付与することができる。つまり、CAC-OSとは、材料の一部では導電性の機能と、材料の一部では絶縁性の機能とを有し、材料の全体では半導体としての機能を有する。導電性の機能と絶縁性の機能とを分離させることで、双方の機能を最大限に高めることができる。よって、CAC-OSをトランジスタに用いることで、高いオン電流(Ion)、高い電界効果移動度(μ)、および良好なスイッチング動作を実現することができる。

酸化物半導体は、多様な構造をとり、それぞれが異なる特性を有する。本発明の一態様の酸化物半導体は、非晶質酸化物半導体、多結晶酸化物半導体、a-like OS、CAC-OS、nc-OS、CAAC-OSのうち、二種以上を有していてもよい。

<酸化物半導体を有するトランジスタ>

続いて、上記酸化物半導体をトランジスタに用いる場合について説明する。

上記酸化物半導体をトランジスタに用いることで、高い電界効果移動度のトランジスタを実現することができる。また、信頼性の高いトランジスタを実現することができる。

トランジスタのチャネル形成領域には、キャリア濃度の低い酸化物半導体を用いることが好ましい。例えば、酸化物半導体のチャネル形成領域のキャリア濃度は1×1017cm-3以下、好ましくは1×1015cm-3以下、さらに好ましくは1×1013cm-3以下、より好ましくは1×1011cm-3以下、さらに好ましくは1×1010cm-3未満であり、1×10-9cm-3以上である。なお、酸化物半導体膜のキャリア濃度を低くする場合においては、酸化物半導体膜中の不純物濃度を低くし、欠陥準位密度を低くすればよい。本明細書等において、不純物濃度が低く、欠陥準位密度の低いことを高純度真性又は実質的に高純度真性と言う。なお、キャリア濃度の低い酸化物半導体を、高純度真性又は実質的に高純度真性な酸化物半導体と呼ぶ場合がある。

また、高純度真性又は実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。

また、酸化物半導体のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体にチャネル形成領域が形成されるトランジスタは、電気特性が不安定となる場合がある。

従って、トランジスタの電気特性を安定にするためには、酸化物半導体中の不純物濃度を低減することが有効である。また、酸化物半導体中の不純物濃度を低減するためには、近接する膜中の不純物濃度も低減することが好ましい。不純物としては、水素、窒素、アルカリ金属、アルカリ土類金属、鉄、ニッケル、シリコン等がある。

<不純物>

ここで、酸化物半導体中における各不純物の影響について説明する。

酸化物半導体において、第14族元素の一つであるシリコンや炭素が含まれると、酸化物半導体において欠陥準位が形成される。このため、酸化物半導体のチャネル形成領域におけるシリコンや炭素の濃度と、酸化物半導体のチャネル形成領域との界面近傍のシリコンや炭素の濃度(二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)により得られる濃度)を、2×1018atoms/cm3以下、好ましくは2×1017atoms/cm3以下とする。

また、酸化物半導体にアルカリ金属又はアルカリ土類金属が含まれると、欠陥準位を形成し、キャリアを生成する場合がある。従って、アルカリ金属又はアルカリ土類金属が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため、SIMSにより得られる酸化物半導体のチャネル形成領域中のアルカリ金属又はアルカリ土類金属の濃度を、1×1018atoms/cm3以下、好ましくは2×1016atoms/cm3以下にする。

また、酸化物半導体において、窒素が含まれると、キャリアである電子が生じ、キャリア濃度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を半導体に用いたトランジスタはノーマリーオン特性となりやすい。または、酸化物半導体において、窒素が含まれると、トラップ準位が形成される場合がある。この結果、トランジスタの電気特性が不安定となる場合がある。このため、SIMSにより得られる酸化物半導体のチャネル形成領域中の窒素濃度を、5×1019atoms/cm3未満、好ましくは5×1018atoms/cm3以下、より好ましくは1×1018atoms/cm3以下、さらに好ましくは5×1017atoms/cm3以下にする。

また、酸化物半導体に含まれる水素は、金属原子と結合する酸素と反応して水になるため、酸素欠損を形成する場合がある。該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することがある。従って、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体のチャネル形成領域における中の水素はできる限り低減されていることが好ましい。具体的には、酸化物半導体のチャネル形成領域において、SIMSにより得られる水素濃度を、1×1020atoms/cm3未満、好ましくは5×1019atoms/cm3未満、より好ましくは1×1019atoms/cm3未満、さらに好ましくは5×1018atoms/cm3未満、さらに好ましくは1×1018atoms/cm3未満にする。

不純物が十分に低減された酸化物半導体をトランジスタのチャネル形成領域に用いることで、安定した電気特性を付与することができる。

<<その他の半導体材料>>

酸化物230に用いることができる半導体材料は、上述の金属酸化物に限られない。酸化物230として、バンドギャップを有する半導体材料(ゼロギャップ半導体ではない半導体材料)を用いてもよい。例えば、シリコンなどの単体元素の半導体、ヒ化ガリウムなどの化合物半導体、半導体として機能する層状物質(原子層物質、2次元材料などともいう。)などを半導体材料に用いることが好ましい。特に、半導体として機能する層状物質を半導体材料に用いると好適である。

ここで、本明細書等において、層状物質とは、層状の結晶構造を有する材料群の総称である。層状の結晶構造は、共有結合やイオン結合によって形成される層が、ファンデルワールス力のような、共有結合やイオン結合よりも弱い結合を介して積層している構造である。層状物質は、単位層内における電気伝導性が高く、つまり、2次元電気伝導性が高い。半導体として機能し、かつ、2次元電気伝導性の高い材料をチャネル形成領域に用いることで、オン電流の大きいトランジスタを提供することができる。

層状物質として、グラフェン、シリセン、カルコゲン化物などがある。カルコゲン化物は、カルコゲンを含む化合物である。また、カルコゲンは、第16族に属する元素の総称であり、酸素、硫黄、セレン、テルル、ポロニウム、リバモリウムが含まれる。また、カルコゲン化物として、遷移金属カルコゲナイド、13族カルコゲナイドなどが挙げられる。

酸化物230として、例えば、半導体として機能する遷移金属カルコゲナイドを用いることが好ましい。酸化物230として適用可能な遷移金属カルコゲナイドとして、具体的には、硫化モリブデン(代表的にはMoS2)、セレン化モリブデン(代表的にはMoSe2)、モリブデンテルル(代表的にはMoTe2)、硫化タングステン(代表的にはWS2)、セレン化タングステン(代表的にはWSe2)、タングステンテルル(代表的にはWTe2)、硫化ハフニウム(代表的にはHfS2)、セレン化ハフニウム(代表的にはHfSe2)、硫化ジルコニウム(代表的にはZrS2)、セレン化ジルコニウム(代表的にはZrSe2)などが挙げられる。

<半導体装置の作製方法>

次に、図1A乃至図1Dに示す、本発明の一態様である半導体装置の作製方法を、図5A乃至図13Dを用いて説明する。

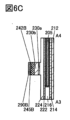

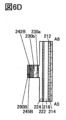

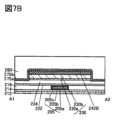

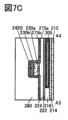

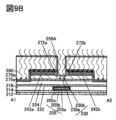

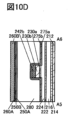

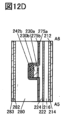

図5A、図6A、図7A、図8A、図9A、図10A、図11A、図12A、および図13Aは上面図を示す。また、図5B、図6B、図7B、図8B、図9B、図10B、図11B、図12B、および図13Bはそれぞれ、図5A、図6A、図7A、図8A、図9A、図10A、図11A、図12A、および図13AにA1-A2の一点鎖線で示す部位に対応する断面図であり、トランジスタ200のチャネル長方向の断面図でもある。また、図5C、図6C、図7C、図8C、図9C、図10C、図11C、図12C、および図13Cはそれぞれ、図5A、図6A、図7A、図8A、図9A、図10A、図11A、図12A、および図13AにA3-A4の一点鎖線で示す部位に対応する断面図であり、トランジスタ200のチャネル幅方向の断面図でもある。また、図5D、図6D、図7D、図8D、図9D、図10D、図11D、図12D、および図13Dはそれぞれ、図5A、図6A、図7A、図8A、図9A、図10A、図11A、図12A、および図13AにA5-A6の一点鎖線で示す部位に対応する断面図である。なお、図5A、図6A、図7A、図8A、図9A、図10A、図11A、図12A、および図13Aの上面図では、図の明瞭化のために一部の要素を省いている。

以下において、絶縁体を形成するための絶縁性材料、導電体を形成するための導電性材料、または半導体を形成するための半導体材料は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを適宜用いて成膜することができる。

なお、スパッタリング法にはスパッタリング用電源に高周波電源を用いるRFスパッタリング法、直流電源を用いるDCスパッタリング法、さらにパルス的に電極に印加する電圧を変化させるパルスDCスパッタリング法がある。RFスパッタリング法は主に絶縁膜を成膜する場合に用いられ、DCスパッタリング法は主に金属導電膜を成膜する場合に用いられる。また、パルスDCスパッタリング法は、主に、酸化物、窒化物、炭化物などの化合物をリアクティブスパッタリング法で成膜する際に用いられる。

なお、CVD法は、プラズマを利用するプラズマCVD(PECVD:Plasma Enhanced CVD)法、熱を利用する熱CVD(TCVD:Thermal CVD)法、光を利用する光CVD(Photo CVD)法などに分類できる。さらに用いる原料ガスによって金属CVD(MCVD:Metal CVD)法、有機金属CVD(MOCVD:Metal Organic CVD)法に分けることができる。

プラズマCVD法は、比較的低温で高品質の膜が得られる。また、熱CVD法は、プラズマを用いないため、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。例えば、半導体装置に含まれる配線、電極、素子(トランジスタ、容量素子など)などは、プラズマから電荷を受け取ることでチャージアップする場合がある。このとき、蓄積した電荷によって、半導体装置に含まれる配線、電極、素子などが破壊される場合がある。一方、プラズマを用いない熱CVD法の場合、こういったプラズマダメージが生じないため、半導体装置の歩留まりを高くすることができる。また、熱CVD法では、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。

また、ALD法としては、プリカーサ及びリアクタントの反応を熱エネルギーのみで行う熱ALD(Thermal ALD)法、プラズマ励起されたリアクタントを用いるPEALD(Plasma Enhanced ALD)法などを用いることができる。

また、ALD法は、原子の性質である自己制御性を利用し、一層ずつ原子を堆積することができるので、極薄の成膜が可能、アスペクト比の高い構造への成膜が可能、ピンホールなどの欠陥の少ない成膜が可能、被覆性に優れた成膜が可能、低温での成膜が可能、などの効果がある。PEALD(Plasma Enhanced ALD)法では、プラズマを利用することで、より低温での成膜が可能となり好ましい場合がある。なお、ALD法で用いるプリカーサには炭素などの不純物を含むものがある。このため、ALD法により設けられた膜は、他の成膜法により設けられた膜と比較して、炭素などの不純物を多く含む場合がある。なお、不純物の定量は、X線光電子分光法(XPS:X-ray Photoelectron Spectroscopy)を用いて行うことができる。

CVD法およびALD法は、ターゲットなどから放出される粒子が堆積する成膜方法とは異なり、被処理物の表面における反応により膜が形成される成膜方法である。したがって、被処理物の形状の影響を受けにくく、良好な段差被覆性を有する成膜方法である。特に、ALD法は、優れた段差被覆性と、優れた厚さの均一性を有するため、アスペクト比の高い開口部の表面を被覆する場合などに好適である。ただし、ALD法は、比較的成膜速度が遅いため、成膜速度の速いCVD法などの他の成膜方法と組み合わせて用いることが好ましい場合もある。

CVD法およびALD法は、原料ガスの流量比によって、得られる膜の組成を制御することができる。例えば、CVD法およびALD法では、原料ガスの流量比によって、任意の組成の膜を成膜することができる。また、例えば、CVD法およびALD法では、成膜しながら原料ガスの流量比を変化させることによって、組成が連続的に変化した膜を成膜することができる。原料ガスの流量比を変化させながら成膜する場合、複数の成膜室を用いて成膜する場合と比べて、搬送や圧力調整に掛かる時間を要さない分、成膜に掛かる時間を短くすることができる。したがって、半導体装置の生産性を高めることができる場合がある。

まず、基板(図示しない。)を準備し、当該基板上に絶縁体212を成膜する(図5B乃至図5D参照。)。絶縁体212の成膜は、スパッタリング法を用いて行うことが好ましい。成膜ガスに水素を用いなくてもよいスパッタリング法を用いることで、絶縁体212中の水素濃度を低減することができる。ただし、絶縁体212の成膜は、スパッタリング法に限られるものではなく、CVD法、MBE法、PLD法、ALD法などを適宜用いてもよい。

本実施の形態では、絶縁体212として、窒素ガスを含む雰囲気でシリコンターゲットを用いて、パルスDCスパッタリング法で窒化シリコンを成膜する。パルスDCスパッタリング法を用いることで、ターゲット表面のアーキングによるパーティクルの発生を抑制することができるので、膜厚分布をより均一にすることができる。また、パルス電圧を用いることで、高周波電圧より、放電の立ち上がり、立ち下がりを急峻にすることができる。これにより、電極に、電力をより効率的に供給しスパッタレート、および膜質を向上することができる。

窒化シリコンのように水、水素などの不純物が透過しにくい絶縁体を用いることにより、絶縁体212より下層に含まれる水、水素などの不純物の拡散を抑制することができる。また、絶縁体212として、窒化シリコンなどの銅が透過しにくい絶縁体を用いることにより、絶縁体212より下層(図示しない。)の導電体に銅など拡散しやすい金属を用いても、当該金属が絶縁体212を介して上方に拡散するのを抑制することができる。

次に、絶縁体212上に絶縁体214を成膜する(図5B乃至図5D参照。)。絶縁体214の成膜は、スパッタリング法を用いて行うことが好ましい。成膜ガスに水素を用いなくてもよいスパッタリング法を用いることで、絶縁体214中の水素濃度を低減することができる。ただし、絶縁体214の成膜は、スパッタリング法に限られるものではなく、CVD法、MBE法、PLD法、ALD法などを適宜用いてもよい。

本実施の形態では、絶縁体214として、酸素ガスを含む雰囲気でアルミニウムターゲットを用いて、パルスDCスパッタリング法で酸化アルミニウムを成膜する。パルスDCスパッタリング法を用いることで、膜厚分布をより均一にし、スパッタレート、および膜質を向上することができる。

絶縁体214として、水素を捕獲および水素を固着する機能が高い、アモルファス構造を有する金属酸化物、例えば酸化アルミニウムを用いること好ましい。これにより、絶縁体216などに含まれる水素を捕獲または固着し、当該水素が酸化物230に拡散するのを防ぐことができる。特に、絶縁体214として、アモルファス構造を有する酸化アルミニウム、またはアモルファス構造の酸化アルミニウムを用いることで、より効果的に水素を捕獲または固着できる場合があるため好ましい。これにより、良好な特性を有し、信頼性の高いトランジスタ200、および半導体装置を作製することができる。

次に、絶縁体214上に絶縁体216を成膜する。絶縁体216の成膜は、スパッタリング法を用いて行うことが好ましい。成膜ガスに水素を用いなくてもよいスパッタリング法を用いることで、絶縁体216中の水素濃度を低減することができる。ただし、絶縁体216の成膜は、スパッタリング法に限られるものではなく、CVD法、MBE法、PLD法、ALD法などを適宜用いてもよい。

本実施の形態では、絶縁体216として、酸素ガスを含む雰囲気でシリコンターゲットを用いて、パルスDCスパッタリング法で酸化シリコンを成膜する。パルスDCスパッタリング法を用いることで、膜厚分布をより均一にし、スパッタレート、および膜質を向上することができる。

絶縁体212、絶縁体214、および絶縁体216は、大気に暴露することなく連続して成膜することが好ましい。例えば、マルチチャンバー方式の成膜装置を用いればよい。これにより、絶縁体212、絶縁体214、および絶縁体216を、膜中の水素を低減して成膜し、さらに、各成膜工程の合間に膜中に水素が混入するのを低減することができる。

次に、絶縁体216に絶縁体214に達する開口を形成する。開口とは、例えば、溝やスリットなども含まれる。また、開口が形成された領域を指して開口部とする場合がある。開口の形成はウェットエッチングを用いてもよいが、ドライエッチングを用いるほうが微細加工には好ましい。また、絶縁体214は、絶縁体216をエッチングして溝を形成する際のエッチングストッパ膜として機能する絶縁体を選択することが好ましい。例えば、溝を形成する絶縁体216に酸化シリコンまたは酸化窒化シリコンを用いた場合は、絶縁体214は窒化シリコン、酸化アルミニウム、または酸化ハフニウムを用いるとよい。

ドライエッチング装置としては、平行平板型電極を有する容量結合型プラズマ(CCP:Capacitively Coupled Plasma)エッチング装置を用いることができる。平行平板型電極を有する容量結合型プラズマエッチング装置は、平行平板型電極の一方の電極に高周波電圧を印加する構成でもよい。または平行平板型電極の一方の電極に複数の異なった高周波電圧を印加する構成でもよい。または平行平板型電極それぞれに同じ周波数の高周波電圧を印加する構成でもよい。または平行平板型電極それぞれに周波数の異なる高周波電圧を印加する構成でもよい。または高密度プラズマ源を有するドライエッチング装置を用いることができる。高密度プラズマ源を有するドライエッチング装置は、例えば、誘導結合型プラズマ(ICP:Inductively Coupled Plasma)エッチング装置などを用いることができる。

開口の形成後に、導電体205aとなる導電膜を成膜する。当該導電膜は、酸素の透過を抑制する機能を有する導電体を含むことが望ましい。例えば、窒化タンタル、窒化タングステン、窒化チタンなどを用いることができる。または、酸素の透過を抑制する機能を有する導電体と、タンタル、タングステン、チタン、モリブデン、アルミニウム、銅、またはモリブデンタングステン合金との積層膜とすることができる。当該導電膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。

本実施の形態では、導電体205aとなる導電膜として窒化チタン膜を成膜する。このような金属窒化物を導電体205bの下層に用いることにより、絶縁体216などによって、導電体205bが酸化されるのを抑制することができる。また、導電体205bとして銅などの拡散しやすい金属を用いても、当該金属が導電体205aから外に拡散するのを防ぐことができる。

次に、導電体205bとなる導電膜を成膜する。当該導電膜としては、タンタル、タングステン、チタン、モリブデン、アルミニウム、銅、モリブデンタングステン合金などを用いることができる。当該導電膜の成膜は、メッキ法、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。本実施の形態では、当該導電膜として、タングステン膜を成膜する。

次に、CMP処理を行うことで、導電体205aとなる導電膜および導電体205bとなる導電膜の一部を除去し、絶縁体216を露出する。その結果、開口部のみに、導電体205aおよび導電体205bが残存する。なお、当該CMP処理により、絶縁体216の一部が除去される場合がある。

次に、エッチングを行って、導電体205bの上部を除去する。これにより、導電体205bの上面は、導電体205aの上面および絶縁体216の上面より低くなる。導電体205bのエッチングには、ドライエッチングまたはウェットエッチングを用いればよいが、ドライエッチングを用いるほうが微細加工には好ましい。

次に、絶縁体216、導電体205a、および導電体205bの上に、導電体205cとなる導電膜を成膜する。当該導電膜は、導電体205aと同様に、酸素の透過を抑制する機能を有する導電体を含むことが望ましい。

本実施の形態では、導電体205cとなる導電膜として窒化チタン膜を成膜する。このような金属窒化物を導電体205bの上層に用いることにより、絶縁体222などによって、導電体205bが酸化されるのを抑制することができる。また、導電体205bとして銅などの拡散しやすい金属を用いても、当該金属が導電体205cから外に拡散するのを防ぐことができる。

次に、CMP処理を行うことで、導電体205cとなる導電膜の一部を除去し、絶縁体216を露出する。その結果、開口部のみに、導電体205a、導電体205b、および導電体205cが残存する。これにより、上面が平坦な、導電体205を形成することができる(図5A乃至図5D参照。)。さらに、導電体205bが、導電体205aおよび導電体205cに包みこまれる構成になる。よって、導電体205bから水素などの不純物が導電体205aおよび導電体205cの外に拡散するのを防ぎ、かつ導電体205aおよび導電体205cの外から酸素が混入し、導電体205bが酸化するのを防ぐことができる。なお、当該CMP処理により、絶縁体216の一部が除去される場合がある。

次に、絶縁体216、および導電体205上に絶縁体222を成膜する。絶縁体222として、アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体を成膜するとよい。アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体は、酸素、水素、および水に対するバリア性を有する。絶縁体222が、水素および水に対するバリア性を有することで、トランジスタ200の周辺に設けられた構造体に含まれる水素、および水が、絶縁体222を通じてトランジスタ200の内側へ拡散することが抑制され、酸化物230中の酸素欠損の生成を抑制することができる。

絶縁体222の成膜は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。本実施の形態では、絶縁体222として、ALD法を用いて、酸化ハフニウムを成膜する。

続いて、加熱処理を行うと好ましい。加熱処理は、250℃以上650℃以下、好ましくは300℃以上500℃以下、さらに好ましくは320℃以上450℃以下で行えばよい。なお、加熱処理は、窒素ガスもしくは不活性ガスの雰囲気、または酸化性ガスを10ppm以上、1%以上、もしくは10%以上含む雰囲気で行う。例えば、窒素ガスと酸素ガスの混合雰囲気で加熱処理をする場合、酸素ガスを20%程度にすればよい。また、加熱処理は減圧状態で行ってもよい。または、加熱処理は、窒素ガスもしくは不活性ガスの雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上、1%以上、または10%以上含む雰囲気で加熱処理を行ってもよい。

また、上記加熱処理で用いるガスは、高純度化されていることが好ましい。例えば、上記加熱処理で用いるガスに含まれる水分量が1ppb以下、好ましくは0.1ppb以下、より好ましくは0.05ppb以下にすればよい。高純度化されたガスを用いて加熱処理を行うことで、絶縁体222などに水分等が取り込まれることを可能な限り防ぐことができる。

本実施の形態では、加熱処理として、絶縁体222の成膜後に、窒素ガスと酸素ガスの流量比を4slm:1slmとして、400℃の温度で1時間の処理を行う。当該加熱処理によって、絶縁体222に含まれる水、水素などの不純物を除去することなどができる。また、絶縁体222として、ハフニウムを含む酸化物を用いる場合、当該加熱処理によって、絶縁体222の一部が結晶化する場合がある。また、加熱処理は、絶縁体224の成膜後などのタイミングで行うこともできる。

次に、絶縁体222上に絶縁体224を成膜する。絶縁体224の成膜は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。本実施の形態では、絶縁体224として、PECVD法を用いて、酸化シリコンを成膜する。

ここで、絶縁体224に過剰酸素領域を形成するために、減圧状態で酸素を含むプラズマ処理を行ってもよい。酸素を含むプラズマ処理は、例えばマイクロ波を用いた高密度プラズマを発生させる電源を有する装置を用いることが好ましい。または、基板側にRF(Radio Frequency)を印加する電源を有してもよい。高密度プラズマを用いることにより、高密度の酸素ラジカルを生成することができ、基板側にRFを印加することで、高密度プラズマによって生成された酸素ラジカルを効率よく絶縁体224内に導くことができる。または、この装置を用いて不活性ガスを含むプラズマ処理を行った後に、脱離した酸素を補うために酸素を含むプラズマ処理を行ってもよい。なお、当該プラズマ処理の条件を適宜選択することにより、絶縁体224に含まれる水、水素などの不純物を除去することができる。その場合、加熱処理は行わなくてもよい。

ここで、絶縁体224にCMP処理を行ってもよい。当該CMP処理を行うことで、絶縁体224表面の平坦化および平滑化を行うことができる。絶縁体224表面の平坦化および平滑化を行うことで、後に成膜する酸化物の被覆率の悪化を防止し、半導体装置の歩留りの低下を防ぐことができる場合がある。なお、CMP処理によって、絶縁体224の膜厚が薄くなるが、絶縁体224の成膜時に膜厚を調整すればよい。

また、絶縁体224上に、例えば、スパッタリング法によって、酸化アルミニウムを成膜した後、絶縁体224に達するまで、CMP処理を行ってもよい。当該酸化アルミニウムを絶縁体224上に配置してCMP処理を行うことで、CMP処理の終点検出が容易となる。また、CMP処理によって、絶縁体224の一部が研磨されて、絶縁体224の膜厚が薄くなることがあるが、絶縁体224の成膜時に膜厚を調整すればよい。また、絶縁体224上に、スパッタリング法によって、酸化アルミニウムを成膜することにより、絶縁体224に酸素を添加することができるので好ましい。

次に、絶縁体224上に、酸化膜230A、酸化膜230Bを順に成膜する(図5A乃至図5D参照。)。なお、酸化膜230Aおよび酸化膜230Bは、大気環境にさらさずに連続して成膜することが好ましい。例えば、マルチチャンバー方式の成膜装置を用いればよい。大気開放せずに成膜することで、酸化膜230A上、および酸化膜230B上に大気環境からの不純物または水分が付着することを防ぐことができ、酸化膜230Aと酸化膜230Bとの界面近傍を清浄に保つことができる。

酸化膜230A、および酸化膜230Bの成膜はスパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。

例えば、酸化膜230A、および酸化膜230Bをスパッタリング法によって成膜する場合は、スパッタリングガスとして酸素、または、酸素と希ガスの混合ガスを用いる。スパッタリングガスに含まれる酸素の割合を高めることで、成膜される酸化膜中の過剰酸素を増やすことができる。また、上記の酸化膜をスパッタリング法によって成膜する場合は、上記のIn-M-Zn酸化物ターゲットなどを用いることができる。

特に、酸化膜230Aの成膜時に、スパッタリングガスに含まれる酸素の一部が絶縁体224に供給される場合がある。したがって、当該スパッタリングガスに含まれる酸素の割合は70%以上、好ましくは80%以上、より好ましくは100%とすればよい。

また、酸化膜230Bをスパッタリング法で形成する場合、スパッタリングガスに含まれる酸素の割合を、30%を超えて100%以下、好ましくは70%以上100%以下として成膜すると、酸素過剰型の酸化物半導体が形成される。酸素過剰型の酸化物半導体をチャネル形成領域に用いたトランジスタは、比較的高い信頼性が得られる。ただし、本発明の一態様はこれに限定されない。酸化膜230Bをスパッタリング法で形成する場合、スパッタリングガスに含まれる酸素の割合を1%以上30%以下、好ましくは5%以上20%以下として成膜すると、酸素欠乏型の酸化物半導体が形成される。酸素欠乏型の酸化物半導体をチャネル形成領域に用いたトランジスタは、比較的高い電界効果移動度が得られる。また、基板を加熱しながら成膜を行うことによって、当該酸化膜の結晶性を向上させることができる。

本実施の形態では、酸化膜230Aとして、スパッタリング法によって、In:Ga:Zn=1:3:4[原子数比]の酸化物ターゲットを用いて成膜する。また、酸化膜230Bとして、スパッタリング法によって、In:Ga:Zn=4:2:4.1[原子数比]の酸化物ターゲットを用いて成膜する。なお、各酸化膜は、成膜条件、および原子数比を適宜選択することで、酸化物230a、および酸化物230bに求める特性に合わせて形成するとよい。

次に、加熱処理を行うことが好ましい。加熱処理は、酸化膜230A、および酸化膜230Bが多結晶化しない温度範囲で行えばよく、250℃以上650℃以下、好ましくは400℃以上600℃以下で行えばよい。なお、加熱処理は、窒素ガスもしくは不活性ガスの雰囲気、または酸化性ガスを10ppm以上、1%以上、もしくは10%以上含む雰囲気で行う。例えば、窒素ガスと酸素ガスの混合雰囲気で加熱処理をする場合、酸素ガスを20%程度にすればよい。また、加熱処理は減圧状態で行ってもよい。または、加熱処理は、窒素ガスもしくは不活性ガスの雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上、1%以上、または10%以上含む雰囲気で加熱処理を行ってもよい。

また、上記加熱処理で用いるガスは、高純度化されていることが好ましい。例えば、上記加熱処理で用いるガスに含まれる水分量が1ppb以下、好ましくは0.1ppb以下、より好ましくは0.05ppb以下にすればよい。高純度化されたガスを用いて加熱処理を行うことで、酸化膜230A、および酸化膜230Bなどに水分等が取り込まれることを可能な限り防ぐことができる。

本実施の形態では、加熱処理として、窒素雰囲気にて400℃の温度で1時間の処理を行った後に、連続して酸素雰囲気にて400℃の温度で1時間の処理を行う。当該加熱処理によって、酸化膜230A中、および酸化膜230B中の水、水素などの不純物を除去することなどができる。

次に、酸化膜230B上に導電膜242Aを成膜する(図5A乃至図5D参照。)。導電膜242Aの成膜はスパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。例えば、導電膜242Aとして、スパッタリング法を用いて窒化タンタル膜を成膜すればよい。なお、導電膜242Aの成膜前に、加熱処理を行ってもよい。当該加熱処理は、減圧下で行い、大気に暴露することなく、連続して導電膜242Aを成膜してもよい。このような処理を行うことによって、酸化膜230Bの表面などに吸着している水分および水素を除去し、さらに酸化膜230A中、および酸化膜230B中の水分濃度および水素濃度を低減させることができる。加熱処理の温度は、100℃以上400℃以下が好ましい。本実施の形態では、加熱処理の温度を200℃とする。

次に、導電膜242A上に絶縁膜245Aを成膜する(図5A乃至図5D参照。)。絶縁膜245Aの成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。絶縁膜245Aは、酸素の透過を抑制する機能を有する絶縁膜を用いることが好ましい。例えば、絶縁膜245Aとして、酸化アルミニウム膜、または窒化シリコン膜を成膜すればよい。

次に、絶縁膜245A上に、導電膜290Aを成膜する(図5A乃至図5D参照。)。導電膜290Aの成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。例えば、導電膜290Aとして、タングステン膜を成膜すればよい。

次に、導電膜290A、および絶縁膜245Aを島状に加工して、導電層290B、および絶縁層245Bを形成する(図6(A)乃至図6(D)参照。)。導電層290B、および絶縁層245Bは、ハードマスクとして機能する。

次に、リソグラフィー法を用いて、酸化膜230A、酸化膜230B、および導電膜242Aを島状に加工して、酸化物230a、酸化物230b、および導電層242Bを形成する(図6A乃至図6D参照。)。当該加工はドライエッチング法やウェットエッチング法を用いることができる。ドライエッチング法による加工は微細加工に適している。また、酸化膜230A、酸化膜230B、および導電膜242Aの加工は、それぞれ異なる条件で行ってもよい。なお、当該工程において、絶縁体224の酸化物230aと重ならない領域の膜厚が薄くなることがある。また、当該工程において、絶縁体224を、酸化物230aと重畳して、島状に加工する構成にしてもよい。

なお、リソグラフィー法では、まず、マスクを介してレジストを露光する。次に、露光された領域を、現像液を用いて除去または残存させてレジストマスクを形成する。次に、当該レジストマスクを介してエッチング処理することで導電体、半導体、または絶縁体などを所望の形状に加工することができる。例えば、KrFエキシマレーザ光、ArFエキシマレーザ光、EUV(Extreme Ultraviolet)光などを用いて、レジストを露光することでレジストマスクを形成すればよい。また、基板と投影レンズとの間に液体(例えば水)を満たして露光する、液浸技術を用いてもよい。また、前述した光に代えて、電子ビームやイオンビームを用いてもよい。なお、電子ビームやイオンビームを用いる場合には、マスクは不要となる。なお、レジストマスクは、アッシングなどのドライエッチング処理を行う、ウェットエッチング処理を行う、ドライエッチング処理後にウェットエッチング処理を行う、またはウェットエッチング処理後にドライエッチング処理を行うことで、除去することができる。

さらに、レジストマスクの下に絶縁体や導電体からなるハードマスクを用いてもよい。ハードマスクを用いる場合、導電膜242A上にハードマスク材料となる絶縁膜や導電膜を形成し、その上にレジストマスクを形成し、ハードマスク材料をエッチングすることで所望の形状のハードマスクを形成することができる。導電膜242Aなどのエッチングは、レジストマスクを除去してから行っても良いし、レジストマスクを残したまま行っても良い。後者の場合、エッチング中にレジストマスクが消失することがある。導電膜242Aなどのエッチング後にハードマスクをエッチングにより除去しても良い。一方、ハードマスクの材料が後工程に影響が無い、あるいは後工程で利用できる場合、必ずしもハードマスクを除去する必要は無い。本実施の形態では、絶縁層245B、および導電層290Bをハードマスクとして用いている。一方、絶縁層245Bがハードマスクとして十分機能する場合、導電層290Bは、必ずしも設ける必要は無い。その場合、導電膜290Aの形成は不要となる。また、導電層290Bを設けず、絶縁層245Bをハードマスクとする場合、絶縁層245Bの膜厚を適宜調整し、導電膜242Aなどのエッチング中に絶縁層245Bの消失を抑制することが好ましい。

ここで、絶縁層245B、および導電層290Bが導電層242Bのマスクとして機能するので、図6B乃至図6Dに示すように、導電層242Bは側面と上面の間に湾曲面を有しない。これにより、図1Bおよび図1Dに示す導電体242aおよび導電体242bは、側面と上面が交わる端部が角状になる。導電体242aの側面と上面が交わる端部、および導電体242bの側面と上面が交わる端部が角状になることで、当該端部が曲面を有する場合に比べて、導電体242aおよび導電体242bの断面積が大きくなる。これにより、導電体242aおよび導電体242bの抵抗が低減されるので、トランジスタ200のオン電流を大きくすることができる。

また、酸化物230a、酸化物230b、および導電層242Bは、少なくとも一部が導電体205と重なるように形成する。また、酸化物230a、酸化物230b、および導電層242Bの側面は、絶縁体222の上面に対し、概略垂直であることが好ましい。酸化物230a、酸化物230b、および導電層242Bの側面が、絶縁体222の上面に対し、概略垂直であることで、複数のトランジスタ200を設ける際に、小面積化、高密度化が可能となる。または、酸化物230a、酸化物230b、および導電層242Bの側面と、絶縁体222の上面とのなす角が低い角度になる構成にしてもよい。その場合、酸化物230a、酸化物230b、および導電層242Bの側面と、絶縁体222の上面とのなす角は60度以上70度未満が好ましい。この様な形状とすることで、これより後の工程において、絶縁体275などの被覆性が向上し、鬆などの欠陥を低減することができる。

また、上記エッチング工程で発生した副生成物が、絶縁体224の上面、ならびに酸化物230a、酸化物230b、および導電層242Bの側面に、層状に形成される場合がある。当該層状の副生成物が絶縁体224上に形成された状態で、絶縁体275を成膜しても、当該層状の副生成物によって、絶縁体224への酸素の添加が妨害されるおそれがある。よって、絶縁体224の上面に接して形成された当該層状の副生成物は、除去することが好ましい。

なお、上記エッチング工程で、絶縁層245B、または導電層290Bが残存する場合、残存した絶縁層245B、または導電層290Bを除去する。なお、絶縁層245Bは、残存させてもよい。

次に、絶縁体224、および導電層242B上に、絶縁体275a、絶縁体275bを順に成膜する。(図7B乃至図7D参照。)。絶縁体275a、および絶縁体275bの成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。なお、絶縁体275a、および絶縁体275bの成膜は、同じ方法を用いてもよいし、異なる方法を用いてもよい。例えば、絶縁体275として、酸素を含む雰囲気でスパッタリング法を用いて絶縁体275aを成膜し、次にALD法を用いて絶縁体275bを成膜してもよい。ALD法は、被覆性の良好な成膜法なので、1層目の凹凸による段切れが生じるのを防ぐことができる。

また、絶縁体275a、および絶縁体275bには上記材料を用いることができ、絶縁体275a、および絶縁体275bは同じ材料としてもよいし、異なる材料としてもよい。例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコンまたは窒化シリコンと、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体と、の積層構造としてもよい。また、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体として、例えば、アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体を用いることができる。

本実施の形態では、絶縁体275aとして、スパッタリング法によって、酸化アルミニウムを成膜し、絶縁体275bとして、ALD法によって、酸化アルミニウムを成膜する。スパッタリング法で絶縁体275aを成膜することで、絶縁体224に酸素を添加することができる。

次に、絶縁体275上に、絶縁体280となる絶縁膜を成膜する。当該絶縁膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。例えば、当該絶縁膜として、スパッタリング法を用いて酸化シリコン膜を成膜すればよい。当該絶縁膜を、酸素を含む雰囲気で、スパッタリング法で成膜することで、過剰酸素を含む絶縁体280を形成することができる。また、成膜ガスに水素を用いなくてもよいスパッタリング法を用いることで、絶縁体280中の水素濃度を低減することができる。なお、当該絶縁膜の成膜前に、加熱処理を行ってもよい。加熱処理は、減圧下で行い、大気に暴露することなく、連続して当該絶縁膜を成膜してもよい。このような処理を行うことによって、絶縁体275の表面などに吸着している水分および水素を除去し、さらに酸化物230a中、酸化物230b中、および絶縁体224中の水分濃度および水素濃度を低減させることができる。当該加熱処理には、上述した加熱処理条件を用いることができる。

次に、絶縁体280となる絶縁膜にCMP処理を行い、上面が平坦な絶縁体280を形成する(図7B乃至図7D参照。)。なお、絶縁体280上に、例えば、スパッタリング法によって窒化シリコンを成膜し、該窒化シリコンを絶縁体280に達するまで、CMP処理を行ってもよい。

次に、絶縁体280の一部、絶縁体275の一部、および導電層242Bの一部を加工して、酸化物230bに達する開口を形成する。当該開口は、導電体205と重なるように形成することが好ましい。当該開口の形成によって、導電体242a、および導電体242bを形成する(図8A乃至図8D参照。)。

また、絶縁体280の一部、絶縁体275の一部、および導電層242Bの一部の加工は、ドライエッチング法、またはウェットエッチング法を用いることができる。ドライエッチング法による加工は微細加工に適している。また、当該加工は、それぞれ異なる条件で行ってもよい。例えば、絶縁体280の一部をドライエッチング法で加工し、絶縁体275の一部をウェットエッチング法で加工し、導電層242Bの一部をドライエッチング法で加工してもよい。

上記開口を形成する際、導電体242aの側端部が酸化されることで、酸化物272aが形成され、導電体242bの側端部が酸化されることで、酸化物272bが形成される場合がある(図8A乃至図8D参照。)。酸化物272a、および酸化物272bのチャネル長方向の幅は、上記開口を形成する際の加工条件によって、変化する。

導電体242aおよび導電体242bの形成に用いるドライエッチング装置は、エッチング中に基板に蓄積した静電気を除電する機能を有する。即ち、導電体242aおよび導電体242bを形成するエッチング処理が完了した後に、導電体242aおよび導電体242bの形成よりも低い電力によるプラズマ処理を行うことで、基板に蓄積した静電気を除去するものである。このプラズマ処理を除電プラズマ処理と呼ぶ。例えば、除電プラズマ処理に窒素を用いた場合の、酸化物272a、および酸化物272bのチャネル長方向の幅は、除電プラズマ処理に酸素を用いる場合と比較して狭くなる傾向がある。

上記開口を形成する際に、酸化物230bの上部が除去される場合がある。酸化物230bの一部が除去されることで、酸化物230bに溝部が形成される場合がある。

ドライエッチング法とウェットエッチング法とでは異方性が異なる。上記加工をそれぞれ異なる条件で行うことで、図3に示すように、上記開口部において、絶縁体280、導電体242aまたは導電体242b、および酸化物230bの側面と、絶縁体224の底面とのなす角の角度、および、絶縁体275の側面と、絶縁体224の底面とのなす角の角度が異なる場合がある。

ここで、酸化物230a、酸化物230bなどの表面に付着または内部に拡散した不純物を除去することが好ましい。また、上記ドライエッチングで酸化物230b表面に形成される、損傷領域を除去することが好ましい。当該不純物としては、絶縁体280、絶縁体275、および導電層242Bに含まれる成分、上記開口を形成する際に用いられる装置に使われている部材に含まれる成分、エッチングに使用するガスまたは液体に含まれる成分などに起因したものが挙げられる。当該不純物としては、例えば、アルミニウム、シリコン、タンタル、フッ素、塩素などがある。

特に、アルミニウム、またはシリコンなどの不純物は、酸化物230bのCAAC-OS化を阻害する。よって、アルミニウム、またはシリコンなどの、CAAC-OS化を阻害する不純物元素が、低減または除去されていることが好ましい。例えば、酸化物230b、およびその近傍における、アルミニウム原子の濃度が、5.0原子%以下とすればよく、2.0原子%以下が好ましく、1.5原子%以下がより好ましく、1.0原子%以下がさらに好ましく、0.3原子%未満がさらに好ましい。

なお、アルミニウム、またはシリコンなどの不純物によりCAAC-OS化が阻害され、a-like OSとなった金属酸化物の領域を、非CAAC領域と呼ぶ場合がある。非CAAC領域では、結晶構造の緻密さが低下しているため、VOHが多量に形成され、トランジスタがノーマリーオン化しやすくなる。よって、酸化物230bの非CAAC領域は、低減または除去されていることが好ましい。

これに対して、酸化物230bに層状のCAAC構造を有していることが好ましい。特に、酸化物230bのドレイン下端部までCAAC構造を有することが好ましい。ここで、トランジスタ200において、導電体242aまたは導電体242b、およびその近傍がドレインとして機能する。つまり、導電体242a(導電体242b)の下端部近傍の、酸化物230bが、CAAC構造を有することが好ましい。このように、ドレイン耐圧に顕著に影響するドレイン端部においても、酸化物230bの損傷領域が除去され、CAAC構造を有することで、トランジスタ200の電気特性の変動をさらに抑制することができる。また、トランジスタ200の信頼性を向上させることができる。

上記の不純物などを除去するために、洗浄処理を行う。洗浄方法としては、洗浄液など用いたウェット洗浄、プラズマを用いたプラズマ処理、熱処理による洗浄などがあり、上記洗浄を適宜組み合わせて行ってもよい。なお、当該洗浄処理によって、上記溝部が深くなる場合がある。

ウェット洗浄としては、アンモニア水、シュウ酸、リン酸、フッ化水素酸などを炭酸水または純水で希釈した水溶液、純水、炭酸水などを用いて洗浄処理を行ってもよい。または、これらの水溶液、純水、または炭酸水を用いた超音波洗浄を行ってもよい。または、これらの洗浄を適宜組み合わせて行ってもよい。

なお、本明細書等では、市販のフッ化水素酸を純水で希釈した水溶液を希釈フッ化水素酸と呼び、市販のアンモニア水を純水で希釈した水溶液を希釈アンモニア水と呼ぶ場合がある。また、当該水溶液の濃度、温度などは、除去したい不純物、洗浄される半導体装置の構成などによって、適宜調整すればよい。希釈アンモニア水のアンモニア濃度は0.01%以上5%以下、好ましくは0.1%以上0.5%以下とすればよい。また、希釈フッ化水素酸のフッ化水素濃度は0.01ppm以上100ppm以下、好ましくは0.1ppm以上10ppm以下とすればよい。

なお、超音波洗浄には、200kHz以上、好ましくは900kHz以上の周波数を用いることが好ましい。当該周波数を用いることで、酸化物230bなどへのダメージを低減することができる。

また、上記洗浄処理を複数回行ってもよく、洗浄処理毎に洗浄液を変更してもよい。例えば、第1の洗浄処理として希釈フッ化水素酸、または希釈アンモニア水を用いた処理を行い、第2の洗浄処理として純水、または炭酸水を用いた処理を行ってもよい。

上記洗浄処理として、本実施の形態では、希釈フッ化水素酸を用いてウェット洗浄を行う。当該洗浄処理を行うことで、酸化物230a、酸化物230bなどの表面に付着または内部に拡散した不純物を除去することができる。さらに、酸化物230bの結晶性を高めることができる。

これまでドライエッチングなどの加工、または上記洗浄処理によって、上記開口と重なり、かつ酸化物230bと重ならない領域の、絶縁体224の膜厚が、酸化物230bと重なる領域の、絶縁体224の膜厚より薄くなる場合がある。

上記エッチング後、または上記洗浄後に加熱処理を行ってもよい。加熱処理は、100℃以上450℃以下、好ましくは350℃以上400℃以下で行えばよい。なお、加熱処理は、窒素ガスもしくは不活性ガスの雰囲気、または酸化性ガスを10ppm以上、1%以上、もしくは10%以上含む雰囲気で行う。例えば、加熱処理は酸素雰囲気で行うことが好ましい。これにより、酸化物230aおよび酸化物230bに酸素を供給して、酸素欠損の低減を図ることができる。また、このような熱処理を行うことで、酸化物230bの結晶性を向上させることができる。また、加熱処理は減圧状態で行ってもよい。または、酸素雰囲気で加熱処理した後に、大気に露出せずに連続して窒素雰囲気で加熱処理を行ってもよい。

次に絶縁膜250Aを成膜する(図9A乃至図9D参照)。絶縁膜250Aの成膜前に加熱処理を行ってもよく、当該加熱処理は、減圧下で行い、大気に暴露することなく、連続して絶縁膜250Aを成膜してもよい。また、当該加熱処理は、酸素を含む雰囲気で行ってもよい。このような処理を行うことによって、酸化物230bの表面などに吸着している水分および水素を除去し、さらに酸化物230a中、および酸化物230b中の水分濃度および水素濃度を低減させることができる。加熱処理の温度は、100℃以上400℃以下が好ましい。

絶縁膜250Aは、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて成膜することができる。また、絶縁膜250Aは、水素原子が低減または除去されたガスを用いた成膜方法で成膜することが好ましい。これにより、絶縁膜250Aの水素濃度を低減することができる。絶縁膜250Aは、後の工程で酸化物230bと接する絶縁体250となるので、このように水素濃度が低減されていることが好適である。

なお、絶縁膜250Aを成膜することで、酸化物272a、および酸化物272bのチャネル長方向の幅が広くなる場合がある。なお、絶縁膜250Aの成膜前に、酸化物272a、および酸化物272bが形成されていない場合、絶縁膜250Aの成膜時に、導電体242aの側端部が酸化されることで酸化物272aが形成され、導電体242bの側端部が酸化されることで酸化物272bが形成される場合がある。

次に、酸素を含む雰囲気でマイクロ波処理を行う(図9A乃至図9D参照)。ここで、図9B乃至図9Dに点線で示す矢印は、マイクロ波、RFなどの高周波、酸素プラズマ、または酸素ラジカルなどを示す。マイクロ波処理は、例えばマイクロ波を用いた高密度プラズマを発生させる電源を有する、マイクロ波処理装置を用いることが好ましい。また、マイクロ波処理装置は基板側にRFを印加する電源を有してもよい。高密度プラズマを用いることより、高密度の酸素ラジカルを生成することができる。また、基板側にRFを印加することで、高密度プラズマによって生成された酸素イオンを、効率よく酸化物230b中に導くことができる。また、上記マイクロ波処理は、減圧下で行うことが好ましく、圧力を60Pa以上、好ましくは133Pa以上、より好ましくは200Pa以上、さらに好ましくは400Pa以上とすればよい。また、酸素流量比(O2/(O2+Ar))が50%以下、好ましくは10%以上30%以下で行うとよい。また、処理温度は、750℃以下、好ましくは500℃以下、例えば400℃程度で行えばよい。また、酸素プラズマ処理を行った後に、外気に曝すことなく、連続して熱処理を行ってもよい。

図9B乃至図9Dに示すように、酸素を含む雰囲気でマイクロ波処理を行うことで、マイクロ波、またはRF等の高周波を用いて酸素ガスをプラズマ化し、当該酸素プラズマを酸化物230bの導電体242aと導電体242bの間の領域に作用させることができる。このとき、マイクロ波、またはRF等の高周波を領域236、領域237a、および領域237bに照射することもできる。つまり、図2に示す領域236、領域237a、および領域237bに、マイクロ波、またはRF等の高周波、酸素プラズマなどを作用させることができる。プラズマ、マイクロ波などの作用により、領域236、領域237a、および領域237bのVOHを分断し、水素を領域236、領域237a、および領域237bから除去することができる。つまり、領域236、領域237a、および領域237bにおいて、「VOH→H+VO」という反応が起きて、領域236、領域237a、および領域237bの水素濃度を低減することができる。よって、領域236中、領域237a中、および領域237b中の酸素欠損、およびVOHを低減し、キャリア濃度を低下させることができる。また、領域236、領域237a、および領域237bで形成された酸素欠損に、上記酸素プラズマで発生した酸素ラジカル、または絶縁体250に含まれる酸素を供給することで、さらに、領域236中、領域237a中、および領域237b中の酸素欠損を低減し、キャリア濃度を低下させることができる。

一方、図2に示す領域238aおよび領域238b上には、導電体242aおよび導電体242bが設けられている。図9B乃至図9Dに示すように、導電体242aおよび導電体242bは、マイクロ波、またはRF等の高周波、酸素プラズマなどの作用を遮蔽するので、これらの作用は領域238aおよび領域238bには及ばない。これにより、マイクロ波処理によって、領域238aおよび領域238bで、VOHの低減、および過剰な量の酸素供給が発生しないので、キャリア濃度の低下を防ぐことができる。

なお、酸素を含む雰囲気でマイクロ波処理を行う際、マイクロ波、またはRF等の高周波、酸素プラズマなどの作用は、酸化物272a、酸化物272b、絶縁体275、および絶縁体280によって低減することができる。よって、領域237aおよび領域237bへの当該作用は、領域236よりも弱く、領域238aおよび領域238bよりも強い。したがって、マイクロ波処理による、領域237aおよび領域237bのキャリア濃度は、領域238aおよび領域238bよりも低下し、領域236ほど低下しない。

このようにして、酸化物半導体の領域236で選択的に酸素欠損、およびVOHを除去して、領域236をi型または実質的にi型とすることができる。さらに、ソース領域またはドレイン領域として機能する領域238aおよび領域238bに過剰な酸素が供給されるのを抑制し、n型化を維持することができる。さらに、領域237aおよび領域237bのキャリア濃度は、領域238aおよび領域238bのキャリア濃度と同等、またはそれよりも低く、領域236のキャリア濃度と同等、またはそれよりも高くすることができる。これにより、トランジスタ200の電気特性の変動が抑制され、基板面内でトランジスタ200の電気特性がばらつくのを抑制することができる。

また、マイクロ波処理後に減圧状態を保ったままで、加熱処理を行ってもよい。このような処理を行うことで、絶縁膜250A中、酸化物230b中、および酸化物230a中の水素を効率よく除去することができる。また、水素の一部は、導電体242a、および導電体242bにゲッタリングされる場合がある。または、マイクロ波処理後に減圧状態を保ったままで、加熱処理を行うステップを複数回繰り返して行ってもよい。加熱処理を繰り返し行うことで、絶縁膜250A中、酸化物230b中、および酸化物230a中の水素をさらに効率よく除去することができる。なお、加熱処理温度は、300℃以上500℃以下とすることが好ましい。

また、マイクロ波処理を行って絶縁膜250Aの膜質を改質することで、水素、水、不純物等の拡散を抑制することができる。従って、導電体260となる導電膜の成膜などの後工程、または熱処理などの後処理により、絶縁体250を介して、水素、水、不純物等が、酸化物230b、酸化物230aなどへ拡散することを抑制することができる。

なお、上記マイクロ波処理を行うことで、酸化物272a、および酸化物272bのチャネル長方向の幅が広くなる場合がある。なお、上記マイクロ波処理を行う前までに、酸化物272a、および酸化物272bが形成されていない場合、上記マイクロ波処理を行う際、導電体242aの側端部が酸化されることで酸化物272aが形成され、導電体242bの側端部が酸化されることで酸化物272bが形成される場合がある。

図9A乃至図9Dに示す工程においては、絶縁膜250Aの成膜後にマイクロ波処理を行ったが、本発明はこれに限られるものではない。例えば、絶縁膜250Aの成膜前にマイクロ波処理を行ってもよいし、絶縁膜250Aの成膜前と成膜後の両方でマイクロ波処理を行ってもよい。

次に絶縁膜250Bを成膜する(図10B乃至図10D参照)。絶縁膜250Bの成膜前に加熱処理を行ってもよく、当該加熱処理は、減圧下で行い、大気に暴露することなく、連続して絶縁膜250Bを成膜してもよい。また、当該加熱処理は、酸素を含む雰囲気で行ってもよい。このような処理を行うことによって、絶縁膜250Aの表面などに吸着している水分および水素を除去し、さらに酸化物230a中、酸化物230b中、および絶縁膜250A中の水分濃度および水素濃度を低減させることができる。加熱処理の温度は、100℃以上400℃以下が好ましい。

絶縁膜250Bは、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて成膜することができる。また、絶縁膜250Bは、酸素の拡散を抑制する機能を有する絶縁体を用いて形成することが好ましい。このような構成にすることで、絶縁体250aに含まれる酸素が、導電体260へ拡散するのを抑制することができる。つまり、酸化物230へ供給する酸素量の減少を抑制することができる。また、絶縁体250aに含まれる酸素による導電体260の酸化を抑制することができる。例えば、絶縁膜250Bは、絶縁体222と同様の材料を用いて設けることができる。

絶縁膜250Bとして、具体的には、ハフニウム、アルミニウム、ガリウム、イットリウム、ジルコニウム、タングステン、チタン、タンタル、ニッケル、ゲルマニウム、マグネシウムなどから選ばれた一種、もしくは二種以上が含まれた金属酸化物、または酸化物230として用いることができる金属酸化物を用いることができる。特に、アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体を用いることが好ましい。

本実施の形態では、絶縁膜250Bとして、熱ALD法によって、酸化ハフニウム膜を成膜する。なお、マイクロ波処理を行って、絶縁膜250Aの酸化シリコンをPEALD法で成膜し、絶縁膜250Bの酸化ハフニウムを熱ALD法で成膜してもよい。ここで、上記マイクロ波処理、PEALD法での酸化シリコンの成膜、および熱ALD法での酸化ハフニウムの成膜は、大気に暴露することなく、連続処理することが好ましい。例えば、マルチチャンバー方式の処理装置を用いればよい。また、上記マイクロ波処理を、PEALD装置の、プラズマ励起されたリアクタント(酸化剤)の処理で代替してもよい。ここで、リアクタント(酸化剤)としては、酸素ガスを用いればよい。

次に、上記の加熱処理と同様の条件で加熱処理を行ってもよい。本実施の形態では、窒素ガスと酸素ガスの流量比を4slm:1slmとして、400℃の温度で1時間の処理を行う。該加熱処理によって、絶縁体250中、および絶縁体280中の水分濃度および水素濃度を低減させることができる。

なお、ここまでの工程で、導電体242aの側面に酸化物272aが形成され、導電体242bの側面に酸化物272bが形成される。

次に、導電膜260A、導電膜260Bを順に成膜する(図10A乃至図10D参照。)。導電膜260Aおよび導電膜260Bの成膜は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。本実施の形態では、CVD法を用いて、導電膜260Aおよび導電膜260Bを成膜する。

次に、CMP処理によって、絶縁膜250A、絶縁膜250B、導電膜260A、および導電膜260Bを絶縁体280が露出するまで研磨することによって、絶縁体250(絶縁体250a、および絶縁体250b)、および導電体260(導電体260a、および導電体260b)を形成する(図11A乃至図11D参照。)。これにより、絶縁体250は、酸化物230bに達する開口および酸化物230bの溝部の内壁(側壁、および底面)を覆うように配置される。また、導電体260は、絶縁体250を介して、上記開口および上記溝部を埋め込むように配置される。

次に、上記の加熱処理と同様の条件で加熱処理を行ってもよい。本実施の形態では、窒素雰囲気にて400℃の温度で1時間の処理を行う。該加熱処理によって、絶縁体250中および絶縁体280中の水分濃度および水素濃度を低減させることができる。なお、上記加熱処理後、大気に曝すことなく連続して、絶縁体282の成膜を行ってもよい。

次に、絶縁体250上、導電体260上、および絶縁体280上に、絶縁体282を形成する(図12A乃至図12D参照。)。絶縁体282の成膜は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。絶縁体282の成膜は、スパッタリング法を用いて行うことが好ましい。成膜ガスに水素を用いなくてもよいスパッタリング法を用いることで、絶縁体282中の水素濃度を低減することができる。また、スパッタリング法を用いて、酸素を含む雰囲気で絶縁体282の成膜を行うことで、成膜しながら、絶縁体280に酸素を添加することができる。これにより、絶縁体280に過剰酸素を含ませることができる。このとき、基板加熱を行いながら、絶縁体282を成膜することが好ましい。

本実施の形態では、絶縁体282として、酸素ガスを含む雰囲気でアルミニウムターゲットを用いて、パルスDCスパッタリング法で酸化アルミニウムを成膜する。パルスDCスパッタリング法を用いることで、膜厚分布をより均一にし、スパッタレート、および膜質を向上することができる。

次に、絶縁体282上に、絶縁体283を形成する(図12A乃至図12D参照。)。絶縁体283の成膜は、スパッタリング法、CVD法、MBE法、PLD法、またはALD法などを用いて行うことができる。絶縁体283の成膜は、スパッタリング法を用いて行うことが好ましい。成膜ガスに水素を用いなくてもよいスパッタリング法を用いることで、絶縁体283中の水素濃度を低減することができる。また、絶縁体283は、多層としてもよい。例えば、スパッタリング法を用いて、窒化シリコンを成膜し、当該窒化シリコン上に、CVD法を用いて窒化シリコンを成膜してもよい。バリア性の高い絶縁体283および絶縁体212でトランジスタ200を包み込むことで、外部から水分、および水素が侵入するのを防止することができる。

次に、加熱処理を行ってもよい。本実施の形態では、窒素雰囲気にて400℃の温度で1時間の処理を行う。当該加熱処理によって、絶縁体282の成膜によって添加された酸素を絶縁体280、および絶縁体250へ拡散させ、酸化物230のチャネル形成領域へ選択的に供給することができる。なお、当該加熱処理は、絶縁体283の形成後に限らず、絶縁体282の成膜後などに行ってもよい。

次に、絶縁体275、絶縁体280、絶縁体282、および絶縁体283に、導電体242aに達する開口、および導電体242bに達する開口を形成する(図13A乃至図13D参照。)。当該開口の形成は、リソグラフィー法を用いて行えばよい。なお、図13Aで当該開口の形状は、上面視において円形状にしているが、これに限られるものではない。例えば、当該開口が、上面視において、楕円などの略円形状、四角形などの多角形状、四角形等の多角形の角部を丸めた形状になっていてもよい。

次に、絶縁体241aおよび絶縁体241bとなる絶縁膜を成膜し、当該絶縁膜を異方性エッチングして絶縁体241aおよび絶縁体241bを形成する。(図13A乃至図13D参照。)。当該絶縁膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法、またはALD法などを用いて行うことができる。当該絶縁膜として、酸素の透過を抑制する機能を有する絶縁膜を用いることが好ましい。例えば、ALD法を用いて、酸化アルミニウム膜を成膜することが好ましい。または、PEALD法を用いて、窒化シリコン膜を成膜することが好ましい。窒化シリコンは水素に対するブロッキング性が高いので好ましい。

また、絶縁体241aおよび絶縁体241bとなる絶縁膜の異方性エッチングとしては、例えばドライエッチング法などを用いればよい。開口の側壁部に絶縁体241aおよび絶縁体241bを設けることで、外方からの酸素の透過を抑制し、次に形成する導電体240aおよび導電体240bの酸化を防止することができる。また、導電体240aおよび導電体240bから、水、水素などの不純物が外部に拡散することを防ぐことができる。

次に、導電体240aおよび導電体240bとなる導電膜を成膜する。当該導電膜は、水、水素など不純物の透過を抑制する機能を有する導電体を含む積層構造とすることが望ましい。たとえば、窒化タンタル、窒化チタンなどと、タングステン、モリブデン、銅など、と、の積層とすることができる。当該導電膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。

次に、CMP処理を行うことで、導電体240aおよび導電体240bとなる導電膜の一部を除去し、絶縁体283の上面を露出する。その結果、開口のみに、当該導電膜が残存することで上面が平坦な導電体240aおよび導電体240bを形成することができる(図13A乃至図13D参照。参照)。なお、当該CMP処理により、絶縁体283の上面の一部が除去される場合がある。

次に、導電体246aおよび導電体246bとなる導電膜を成膜する。当該導電膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。

次に、導電体246aおよび導電体246bとなる導電膜をリソグラフィー法によって加工し、導電体240aの上面と接する導電体246a、および導電体240bの上面と接する導電体246bを形成する。この時、導電体246aおよび導電体246bと、絶縁体283とが重ならない領域の絶縁体283の一部が除去されることがある。

次に、導電体246a上、導電体246b上、および絶縁体283上に、絶縁体286を成膜する。絶縁体286の成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。また、絶縁体286は、多層としてもよい。例えば、スパッタリング法を用いて、窒化シリコンを成膜し、当該窒化シリコン上に、CVD法を用いて窒化シリコンを成膜してもよい。

以上により、図1A乃至図1Dに示すトランジスタ200を有する半導体装置を作製することができる。図5A乃至図13Dに示すように、本実施の形態に示す半導体装置の作製方法を用いることで、トランジスタ200を作製することができる。

<半導体装置の変形例>

以下では、図14A乃至図16Dを用いて、本発明の一態様である半導体装置の一例について説明する。

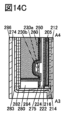

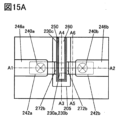

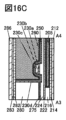

図14A、図15A、および図16Aは半導体装置の上面図を示す。また、図14B、図15B、および図16Bはそれぞれ、図14A、図15A、および図16AにA1-A2の一点鎖線で示す部位に対応する断面図である。また、図14C、図15C、および図16Cはそれぞれ、図14A、図15A、および図16AにA3-A4の一点鎖線で示す部位に対応する断面図である。また、図14D、図15D、図16Dはそれぞれ、図14A、図15A、および図16AにA5-A6の一点鎖線で示す部位に対応する断面図である。図14A、図15A、および図16Aの上面図では、図の明瞭化のために一部の要素を省いている。

なお、図14A乃至図16Dに示す半導体装置において、<半導体装置の構成例>に示した半導体装置を構成する構造と同機能を有する構造には、同符号を付記する。なお、本項目においても、半導体装置の構成材料については<半導体装置の構成例>などで詳細に説明した材料を用いることができる。

<<半導体装置の変形例1>>

図14A乃至図14Dに示す半導体装置は、図1A乃至図1Dに示した半導体装置の変形例である。図14A乃至図14Dに示す半導体装置は、図1A乃至図1Dに示した半導体装置とは、絶縁体283の形状が異なる。また、絶縁体284および絶縁体274を有することが異なる。

図14A乃至図14Dに示す半導体装置では、絶縁体214、絶縁体216、絶縁体222、絶縁体224、絶縁体275、絶縁体280、および絶縁体282がパターニングされている。また、絶縁体284は、絶縁体214、絶縁体216、絶縁体222、絶縁体224、絶縁体275、絶縁体280、および絶縁体282を覆う構造になっている。つまり、絶縁体284は、絶縁体282の上面と、絶縁体214、絶縁体216、絶縁体222、絶縁体224、絶縁体275、絶縁体280、および絶縁体282の側面と、絶縁体212の上面と、に接する。さらに、絶縁体284を覆って絶縁体283が配置されている。これにより、酸化物230、絶縁体214、絶縁体216、絶縁体222、絶縁体224、絶縁体275、絶縁体280、および絶縁体282は、絶縁体283および絶縁体284と、絶縁体212とによって、外部から隔離される。別言すると、トランジスタ200は、絶縁体283および絶縁体284と、絶縁体212とで封止された領域内に配置される。

例えば、絶縁体214、絶縁体275、絶縁体282、および絶縁体284を、水素を捕獲および水素を固着する機能を有する材料を用いて形成すればよい。なお、絶縁体284は、絶縁体282と同様の絶縁体を用いることができる。また、絶縁体212、および絶縁体283を水素および酸素の拡散を抑制する機能を有する材料を用いて形成すればよい。絶縁体214、絶縁体275、絶縁体282、および絶縁体284としては、アモルファス構造を有する金属酸化物、例えば酸化アルミニウムを用いることができる。また、代表的には、絶縁体212、および絶縁体283としては、窒化シリコンを用いることができる。特に、絶縁体284として、アモルファス構造を有する酸化アルミニウム、またはアモルファス構造の酸化アルミニウムを用いることで、より効果的に水素を捕獲または固着できる場合があるため好ましい。これにより、良好な特性を有し、信頼性の高いトランジスタ200、および半導体装置を作製することができる。

上記構成にすることで、上記封止された領域外に含まれる水素が、上記封止された領域内に混入することを抑制することができる。

また、図14A乃至図14Dに示すトランジスタ200では、絶縁体212、および絶縁体283を、単層として設ける構成について示しているが、本発明はこれに限られるものではない。例えば、絶縁体212、および絶縁体283のそれぞれを2層以上の積層構造として設ける構成にしてもよい。

絶縁体274は、絶縁体283を覆って設けられており、層間膜として機能する。絶縁体274は、絶縁体214よりも誘電率が低いことが好ましい。誘電率が低い材料を層間膜とすることで、配線間に生じる寄生容量を低減することができる。絶縁体274は、例えば、絶縁体280と同様の材料を用いて設けることができる。

<<半導体装置の変形例2>>

図15A乃至図15Dに示す半導体装置は、図1A乃至図1Dに示した半導体装置の変形例である。図15A乃至図15Dに示す半導体装置は、図1A乃至図1Dに示した半導体装置とは、酸化物230c、絶縁体271a、絶縁体271b、酸化物243a、および酸化物243bを有することが異なる。

酸化物243a、および酸化物243bは、酸化物230b上に設けられる。酸化物243aと酸化物243bは、導電体260を挟んで離隔して設けられる。

酸化物243a、および酸化物243bは、酸素の透過を抑制する機能を有することが好ましい。ソース電極やドレイン電極として機能する導電体242a(導電体242b)と酸化物230bとの間に酸素の透過を抑制する機能を有する酸化物243a(酸化物243b)を配置することで、導電体242a(導電体242b)と、酸化物230bとの間の電気抵抗が低減されるので好ましい。このような構成とすることで、トランジスタ200の電気特性およびトランジスタ200の信頼性を向上させることができる。なお、導電体242aまたは導電体242bと酸化物230bの間の電気抵抗を十分低減できる場合、酸化物243aおよび酸化物243bを設けない構成にしてもよい。

酸化物243aおよび酸化物243bとして、元素Mを有する金属酸化物を用いてもよい。特に、元素Mは、アルミニウム、ガリウム、イットリウム、または錫を用いるとよい。酸化物243aおよび酸化物243bは、酸化物230bよりも元素Mの濃度が高いことが好ましい。また、酸化物243aおよび酸化物243bとして、酸化ガリウムを用いてもよい。また、酸化物243aおよび酸化物243bとして、In-M-Zn酸化物等の金属酸化物を用いてもよい。具体的には、酸化物243aおよび酸化物243bに用いる金属酸化物において、Inに対する元素Mの原子数比が、酸化物230bに用いる金属酸化物における、Inに対する元素Mの原子数比より大きいことが好ましい。また、酸化物243aおよび酸化物243bの膜厚は、0.5nm以上5nm以下が好ましく、より好ましくは1nm以上3nm以下、さらに好ましくは1nm以上2nm以下である。また、酸化物243aおよび酸化物243bは、結晶性を有すると好ましい。酸化物243aおよび酸化物243bが結晶性を有する場合、酸化物230中の酸素の放出を好適に抑制することが出来る。例えば、酸化物243aおよび酸化物243bの結晶構造が六方晶などであれば、酸化物230中の酸素の放出を抑制できる場合がある。

絶縁体271aは、導電体242aの上面に接して設けられており、絶縁体271bは、導電体242bの上面に接して設けられている。絶縁体271a、および絶縁体271bは、少なくとも酸素に対するバリア絶縁膜として機能することが好ましい。したがって、絶縁体271aおよび絶縁体271bは、酸素の拡散を抑制する機能を有することが好ましい。例えば、絶縁体271aおよび絶縁体271bは、絶縁体280よりも酸素の拡散を抑制する機能を有することが好ましい。絶縁体271aおよび絶縁体271bとしては、例えば、窒化シリコンなどのシリコンを含む窒化物を用いればよい。また、絶縁体271aおよび絶縁体271bは、水素などの不純物を捕獲する機能を有することが好ましい。その場合、絶縁体271aおよび絶縁体271bとしては、アモルファス構造を有する金属酸化物、例えば、酸化アルミニウムまたは酸化マグネシウムなどの絶縁体を用いればよい。特に、絶縁体271aおよび絶縁体271bとして、アモルファス構造を有する酸化アルミニウム、またはアモルファス構造の酸化アルミニウムを用いることで、より効果的に水素を捕獲または固着できる場合があるため好ましい。これにより、良好な特性を有し、信頼性の高いトランジスタ200、および半導体装置を作製することができる。

上記のような絶縁体271aおよび絶縁体271bを設けることで、酸素に対するバリア性を有する絶縁体で導電体242aおよび導電体242bを包み込むことができる。つまり、絶縁体275成膜時に添加される酸素が、導電体242aおよび導電体242bに拡散するのを防ぐことができる。これにより、絶縁体275成膜時に添加される酸素によって、導電体242aおよび導電体242bが酸化されて抵抗率が増大するのを防ぎ、オン電流が低減するのを抑制することができる。

なお、絶縁体275が酸素などに対して十分なバリア性を有する場合、絶縁体271aおよび絶縁体271bを設けない構成にしてもよい。

酸化物230cは、絶縁体280および絶縁体275に形成された開口の中に設けられる。また、酸化物230cは、酸化物243aの側面、酸化物243bの側面、酸化物272aの側面、酸化物272bの側面、絶縁体271aの側面、絶縁体271bの側面、および絶縁体275の側面とそれぞれ接する。また、酸化物230cの上面は、絶縁体282に接する。また、酸化物230cは、酸化物230bと重なる領域を有する。

また、トランジスタのチャネル長方向の断面視において、酸化物230bに溝部を設け、当該溝部に、酸化物230cを埋め込むことが好ましい。このとき、酸化物230cは、当該溝部の内壁(側壁、および底面)を覆うように配置される。また、酸化物230cの膜厚は、当該溝部の深さと同程度であることが好ましい。このような構成にすることで、導電体260などを埋め込むための開口を形成する際に、開口の底部にあたる酸化物230bの表面に損傷領域が形成されても、当該損傷領域を除去することができる。これにより、損傷領域に起因するトランジスタ200の電気特性の不良を抑制することができる。

なお、酸化物230cをキャリアの主たる経路とする場合には、酸化物230cにおいて、主成分である金属元素に対するインジウムの原子数比が、酸化物230bにおける、主成分である金属元素に対するインジウムの原子数比より大きいことが好ましい。また、酸化物230cにおいて、元素Mに対するInの原子数比が、酸化物230bにおける、元素Mに対するInの原子数比より大きいことが好ましい。インジウムの含有量が多い金属酸化物をチャネル形成領域に用いることで、トランジスタのオン電流を増大することができる。よって、酸化物230cにおいて、主成分である金属元素に対するインジウムの原子数比を、酸化物230bにおける、主成分である金属元素に対するインジウムの原子数比よりも大きくすることで、酸化物230cをキャリアの主たる経路とすることができる。また、酸化物230cの伝導帯下端は、酸化物230aおよび酸化物230bの伝導帯下端より真空準位から離れていることが好ましい。言い換えると、酸化物230cの電子親和力は、酸化物230aおよび酸化物230bの電子親和力より大きいことが好ましい。このとき、キャリアの主たる経路は酸化物230cとなる。

酸化物230cとして、具体的には、In:M:Zn=4:2:3[原子数比]もしくはその近傍の組成、In:M:Zn=5:1:3[原子数比]もしくはその近傍の組成、またはIn:M:Zn=10:1:3[原子数比]もしくはその近傍の組成の金属酸化物、インジウム酸化物などを用いるとよい。なお、近傍の組成とは、所望の原子数比の±30%の範囲を含む。また、元素Mとして、ガリウムを用いることが好ましい。

また、酸化物230cとして、CAAC-OSを用いることが好ましく、酸化物230cが有する結晶のc軸が、酸化物230cの被形成面または上面に概略垂直な方向を向いていることが好ましい。CAAC-OSは、c軸と垂直方向に酸素を移動させやすい性質を有する。したがって、酸化物230cが有する酸素を、酸化物230bに効率的に供給することができる。

なお、酸化物230cは、トランジスタ200毎に設けてもよい。つまり、トランジスタ200の酸化物230cと、当該トランジスタ200に隣接するトランジスタ200の酸化物230cと、は、接しなくてもよい。また、トランジスタ200の酸化物230cと、当該トランジスタ200に隣接するトランジスタ200の酸化物230cと、を、離隔してもよい。別言すると、酸化物230cが、トランジスタ200と、当該トランジスタ200に隣接するトランジスタ200との間に配置されない構成としてもよい。

複数のトランジスタ200がチャネル幅方向に配置されている半導体装置において、上記構成にすることで、トランジスタ200に酸化物230cがそれぞれ独立して設けられる。よって、トランジスタ200と、当該トランジスタ200に隣接するトランジスタ200との間に、寄生トランジスタが生じるのを抑制し、リークパスが生じるのを抑制することができる。したがって、良好な電気特性を有し、かつ、微細化または高集積化が可能な半導体装置を提供することができる。

<<半導体装置の変形例3>>

図16A乃至図16Dに示す半導体装置は、図15A乃至図15Dに示した半導体装置の変形例である。図16A乃至図16Dに示す半導体装置は、図15A乃至図15Dに示した半導体装置とは、酸化物230cの形状が異なる。また、酸化物230dを有することが異なる。

酸化物230dは、絶縁体280および絶縁体275に形成された開口の側壁に接して設けられる。また、酸化物230dは、酸化物243aの側面、酸化物243bの側面、酸化物272aの側面、酸化物272bの側面、絶縁体271aの側面、絶縁体271bの側面、および絶縁体275の側面とそれぞれ接する。また、酸化物230dの上面は、絶縁体282に接する。

酸化物230cは、絶縁体280および絶縁体275に形成された開口の底面に接して設けられる。また、酸化物230cは、酸化物230bの上面、および酸化物230dの側面とそれぞれ接する。

酸化物230dは、酸化物230cより、酸素の拡散または透過を抑制する金属酸化物であることが好ましい。絶縁体250と導電体242aとの間、および絶縁体250と導電体242bとの間に酸化物230dを設けることで、絶縁体280に含まれる酸素が、導電体242aおよび導電体242bに吸収されるのを防ぐことができる。よって、酸化物230cを介して、酸化物230bに効率的に酸素を供給することができる。

酸化物230dは、酸化物230cに用いられる金属酸化物を構成する金属元素の少なくとも一つを含むことが好ましく、当該金属元素を全て含むことがより好ましい。例えば、酸化物230cとして、In-M-Zn酸化物、In-Zn酸化物、またはインジウム酸化物を用い、酸化物230dとして、In-M-Zn酸化物、M-Zn酸化物、または元素Mの酸化物を用いるとよい。

具体的には、酸化物230cとして、In:M:Zn=4:2:3[原子数比]もしくはその近傍の組成、In:M:Zn=5:1:3[原子数比]もしくはその近傍の組成、またはIn:M:Zn=10:1:3[原子数比]もしくはその近傍の組成の金属酸化物、または、インジウム酸化物を用いればよい。また、酸化物230dとして、In:M:Zn=1:3:4[原子数比]もしくはその近傍の組成、M:Zn=2:1[原子数比]もしくはその近傍の組成、またはM:Zn=2:5[原子数比]もしくはその近傍の組成の金属酸化物、または、元素Mの酸化物を用いればよい。なお、近傍の組成とは、所望の原子数比の±30%の範囲を含む。また、元素Mとして、ガリウムを用いることが好ましい。

上記構成において、酸化物230dは、酸化物230bおよび酸化物230cよりも、導電性が低いと推定される。よって、酸化物272aおよび酸化物230dをまとめて、semi-insulator(SI)と呼ぶことができる場合がある。また、酸化物272bおよび酸化物230dをまとめて、semi-insulator(SI)と呼ぶことができる場合がある。別言すると、領域237a上に位置し、導電体242aの側端部に位置する膜は、酸化物272aと酸化物230dの複合膜または多層膜と呼ぶことができる場合がある。また、領域237b上に位置し、導電体242bの側端部に位置する膜は、酸化物272bと酸化物230dの複合膜または多層膜と呼ぶことができる場合がある。

<半導体装置の応用例>