JP7583000B2 - 計算機及びデータ処理方法 - Google Patents

計算機及びデータ処理方法 Download PDFInfo

- Publication number

- JP7583000B2 JP7583000B2 JP2022141346A JP2022141346A JP7583000B2 JP 7583000 B2 JP7583000 B2 JP 7583000B2 JP 2022141346 A JP2022141346 A JP 2022141346A JP 2022141346 A JP2022141346 A JP 2022141346A JP 7583000 B2 JP7583000 B2 JP 7583000B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- register

- encrypted

- processor

- user data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/60—Protecting data

- G06F21/602—Providing cryptographic facilities or services

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/60—Protecting data

- G06F21/64—Protecting data integrity, e.g. using checksums, certificates or signatures

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/70—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer

- G06F21/78—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer to assure secure storage of data

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Computer Security & Cryptography (AREA)

- Computer Hardware Design (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- General Health & Medical Sciences (AREA)

- Health & Medical Sciences (AREA)

- Bioethics (AREA)

- Signal Processing For Digital Recording And Reproducing (AREA)

- Storage Device Security (AREA)

Description

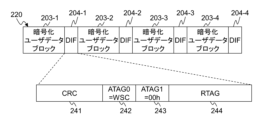

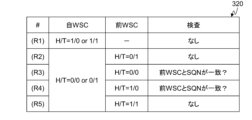

(R1)自ブロックのWSCのHEAD/TAILが1/0又は1/1の場合、検査は行われない。

(R2)自ブロックのWSCのHEAD/TAILが0/0又は0/1、かつ、前のブロックのWSCのHEAD/TAILが0/1である場合、検査は行われない。

(R3)自ブロックのWSCのHEAD/TAILが0/0又は0/1、かつ、前のブロックのWSCのHEAD/TAILが0/0の場合、ストレージシステム120は、自ブロックのWSCのSQNが前ブロックのWSCのSQNと一致するか否かを検査する。

(R4)自ブロックのWSCのHEAD/TAILが0/0又は0/1、かつ、その前のブロックのWSCのHEAD/TAILが1/0の場合、ストレージシステム120は、自ブロックのWSCのSQNが前ブロックのWSCのSQNと一致するか否かを検査する。

(R5)自ブロックのWSCのHEAD/TAILが0/0又は0/1、かつ、前のブロックのWSCのHEAD/TAILが1/1の場合、検査は行われない。

120 ストレージシステム

130 ストレージコントローラ

131 FE I/F

132 BE I/F

133 CPU

134 DRAM

140 ストレージデバイス

Claims (21)

- 複数のデータブロックを含むユーザデータの書き込み及び読み出しを行う計算機であって、

プロセッサ、前記プロセッサに接続されるメモリ、前記プロセッサに接続される記憶媒体、及び前記プロセッサに接続される接続インタフェースを備え、

前記プロセッサは、

複数のレジスタを有し、

前記ユーザデータの書き込みリクエストを受信し、

前記書き込みリクエストに従って書き込まれる前記ユーザデータを前記メモリに格納し、

前記複数のレジスタを用いて、複数の暗号化データブロックを含む暗号化ユーザデータを生成する暗号化処理を実行し、

2以上の第1データ保全性フィールドを第1レジスタに格納し、

前記第1レジスタに格納された前記2以上の前記第1データ保全性フィールドの各々に、前記暗号化データブロックの格納位置を示す第1アドレスを設定する設定処理を並列に実行し、

前記暗号化ユーザデータに含まれる前記複数の暗号化データブロックの各々に、前記第1アドレスが設定された第1データ保全性フィールドを付加し、

前記暗号化ユーザデータを前記記憶媒体に格納する、

ことを特徴とする計算機。 - 請求項1に記載の計算機であって、

前記第1データ保全性フィールドには、前記データブロックの書き込みの世代を表す第1世代番号を設定することができ、

前記プロセッサは、前記第1レジスタに格納された前記2以上の前記第1データ保全性フィールドの各々に、前記暗号化データブロックの前記第1世代番号を設定する設定処理を並列に実行することを特徴とする計算機。 - 請求項1に記載の計算機であって、

前記第1データ保全性フィールドは第1誤り符号を含むことを特徴とする計算機。 - 請求項2に記載の計算機であって、

前記プロセッサは、

前記暗号化ユーザデータの読み出しリクエストを受信し、

前記記憶媒体から、前記読み出しリクエストによって指定された前記暗号化ユーザデータを読み出し、前記メモリに格納し、

前記複数のレジスタを用いて、前記暗号化ユーザデータを復号する復号処理を実行し、

第2レジスタに2以上の第2データ保全性フィールドを格納し、

前記第2レジスタに格納された前記2以上の前記第2データ保全性フィールドの各々に、前記暗号化データブロックの格納位置を示す第2アドレスを設定する設定処理を並列に実行し、

復号された前記ユーザデータに含まれる前記複数のデータブロックの各々に、前記第2アドレスが設定された第2データ保全性フィールドを付加し、前記メモリに格納する、

ことを特徴とする計算機。 - 請求項4に記載の計算機であって、

前記第2データ保全性フィールドには、前記データブロックの書き込みの世代を表す第2世代番号を設定することができ、

前記プロセッサは、前記第2レジスタに格納された前記2以上の前記第2データ保全性フィールドの各々に、前記データブロックの前記第2世代番号を設定する設定処理を並列に実行することを特徴とする計算機。 - 請求項5に記載の計算機であって、

前記プロセッサは、

SIMD命令を用いて、前記第1レジスタに格納された前記2以上の前記第1データ保全性フィールドの各々に前記第1アドレスを設定する設定処理を並列で実行し、

前記SIMD命令を用いて、前記第1レジスタに格納された前記2以上の前記第1データ保全性フィールドの各々に前記第1世代番号を設定する設定処理を並列で実行し、

前記SIMD命令を用いて、前記第2レジスタに格納された前記2以上の前記第2データ保全性フィールドの各々に前記第2アドレスを設定する設定処理を並列で実行し、

前記SIMD命令を用いて、前記第2レジスタに格納された前記2以上の前記第2データ保全性フィールドの各々に前記第2世代番号を設定する設定処理を並列で実行することを特徴とする計算機。 - 請求項4に記載の計算機であって、

前記第2データ保全性フィールドは第1誤り符号を含むことを特徴とする計算機。 - 複数のデータブロックを含むユーザデータの書き込み及び読み出しを行う計算機であって、

プロセッサ、前記プロセッサに接続されるメモリ、前記プロセッサに接続される記憶媒体、及び前記プロセッサに接続される接続インタフェースを備え、

前記プロセッサは、

複数のレジスタを有し、

前記ユーザデータの書き込みリクエストを受信し、

前記書き込みリクエストに従って書き込まれる前記ユーザデータを前記メモリに格納し、

前記複数のレジスタを用いて、複数の暗号化データブロックを含む暗号化ユーザデータを生成する暗号化処理を実行し、

前記複数のレジスタを用いて、前記ユーザデータの破損を検出するための第1検査処理を実行し、

前記暗号化ユーザデータを前記記憶媒体に格納し、

前記ユーザデータに含まれる前記複数のデータブロックの各々には、第1誤り符号を含む第1データ保全性フィールドが付加され、

前記暗号化処理では、

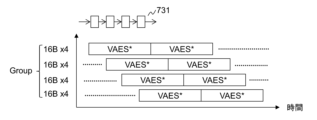

所定の数の前記データブロックから、前記データブロックの一部である部分データを読み出し、第1レジスタに格納する第1処理と、

前記第1レジスタに格納される前記部分データを暗号化した暗号化部分データを第2レジスタに格納する第2処理と、

前記第1レジスタに格納される前記部分データを用いて、前記第1誤り符号を生成するための第1演算を実行し、前記第1演算の結果を第3レジスタに格納する第3処理と、

が繰り返し実行され、

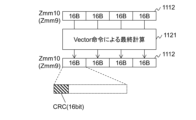

前記第1検査処理は、

第4レジスタに、所定の数の前記データブロックの前記第1データ保全性フィールドを読み出す処理と、

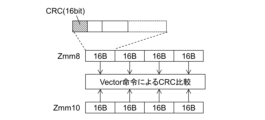

前記第3レジスタに格納される前記第1誤り符号と、前記第4レジスタに格納される前記第1データ保全性フィールドに含まれる前記第1誤り符号とを比較することによって、前記メモリから読み出された前記ユーザデータが破損しているか否かを判定する処理と、

を含むことを特徴とする計算機。 - 請求項8に記載の計算機であって、

前記第1データ保全性フィールドは、前記データブロックの格納位置を示す第1アドレスを含み、

前記第1検査処理は、

第5レジスタに、所定の数の前記データブロックの前記第1アドレスを読み出す処理と、

前記第5レジスタに格納される前記第1アドレスと、前記第4レジスタに格納される前記第1データ保全性フィールドに含まれる前記第1アドレスとを比較することによって、前記メモリから読み出された前記ユーザデータが破損しているか否かを判定する処理と、

を含むことを特徴とする計算機。 - 請求項9に記載の計算機であって、

前記プロセッサは、

前記暗号化ユーザデータの読み出しリクエストを受信し、

前記記憶媒体から、前記読み出しリクエストによって指定された前記暗号化ユーザデータを読み出し、前記メモリに格納し、

前記複数のレジスタを用いて、前記暗号化ユーザデータを復号する復号処理を実行し、

前記複数のレジスタを用いて、前記暗号化ユーザデータの破損を検出するための第2検査処理を実行し、

前記ユーザデータを前記メモリに格納し、

前記暗号化ユーザデータに含まれる前記複数の暗号化データブロックの各々には、第2誤り符号を含む第2データ保全性フィールドが付加され、

前記復号処理では、

所定の数の前記暗号化データブロックから、前記暗号化データブロックの一部である部分暗号化データを読み出し、第6レジスタに格納する第8処理と、

前記第6レジスタに格納される前記部分暗号化データを復号した前記部分データを第7レジスタに格納する第9処理と、

前記第6レジスタに格納される前記暗号化部分データを用いて、前記第2誤り符号を生成するための第2演算を実行し、前記第2演算の結果を第8レジスタに格納する第10処理と、

が繰り返し実行され、

前記第2検査処理は、

第9レジスタに、所定の数の前記暗号化データブロックの前記第2データ保全性フィールドを読み出す処理と、

前記第8レジスタに格納される前記第2誤り符号と、前記第9レジスタに格納される前記第1データ保全性フィールドに含まれる前記第2誤り符号とを比較することによって、前記記憶媒体から読み出された前記暗号化ユーザデータが破損しているか否かを判定する処理と、

を含むことを特徴とする計算機。 - 請求項10に記載の計算機であって、

前記第2データ保全性フィールドは、前記暗号化データブロックの格納位置を示す第2アドレスを含み、

前記第2検査処理は、

第10レジスタに、所定の数の前記暗号化データブロックに対応する前記第2アドレスを読み出す処理と、

前記第9レジスタに格納される前記第2データ保全性フィールドに含まれる前記第2アドレスと、前記第10レジスタに格納される前記第2アドレスとを比較することによって、前記記憶媒体から読み出された前記暗号化ユーザデータが破損しているか否かを判定する処理と、

を含むことを特徴とする計算機。 - 請求項11に記載の計算機であって、

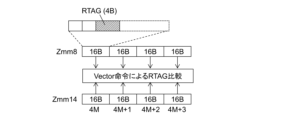

前記第2データ保全性フィールドは、前記データブロックの書き込みの世代を表す第2世代番号を含み、

前記第2検査処理は、

第11レジスタに、所定の数の前記暗号化データブロックに対応する前記第2世代番号を読み出す処理と、

前記第9レジスタに格納される前記第1データ保全性フィールドに含まれる前記第2世代番号と、前記第11レジスタに格納される前記第2世代番号とを比較することによって、前記記憶媒体から読み出された前記暗号化ユーザデータが破損しているか否かを判定する処理と、

を含むことを特徴とする計算機。 - 請求項12に記載の計算機であって、

前記プロセッサは、SIMD命令を用いて、前記複数のデータブロック及び前記複数の暗号化データブロックに対する処理を並列で実行することを特徴とする計算機。 - 複数のデータブロックを含むユーザデータの書き込み及び読み出しを行う計算機が実行するデータ処理方法であって、

前記計算機は、プロセッサ、前記プロセッサに接続されるメモリ、前記プロセッサに接続される記憶媒体、及び前記プロセッサに接続される接続インタフェースを有し、

前記プロセッサは、複数のレジスタを有し、

前記データ処理方法は、

前記プロセッサが、前記ユーザデータの書き込みリクエストを受信するステップと、

前記プロセッサが、前記書き込みリクエストに従って書き込まれる前記ユーザデータを前記メモリに格納するステップと、

前記プロセッサが、前記複数のレジスタを用いて、複数の暗号化データブロックを含む暗号化ユーザデータを生成する暗号化処理を実行するステップと、

前記プロセッサが、前記複数のレジスタを用いて、前記ユーザデータの破損を検出するための検査処理を実行するステップと、

前記プロセッサが、前記暗号化ユーザデータに含まれる前記複数の暗号化データブロックの各々に、第1誤り符号を含む第1データ保全性フィールドを付加するステップと、

前記プロセッサが、前記暗号化ユーザデータを前記記憶媒体に格納するステップと、

を含み、

前記暗号化処理では、

所定の数の前記データブロックから、前記データブロックの一部である部分データを読み出し、第1レジスタに格納する第1処理と、

前記第1レジスタに格納される前記部分データを暗号化した暗号化部分データを第2レジスタに格納する第2処理と、

前記第2レジスタに格納される前記暗号化部分データを用いて、前記第1誤り符号を算出するための第1演算を実行し、前記第1演算の結果を第3レジスタに格納する第3処理と、

が繰り返し実行され、

前記検査処理は、

第4レジスタに、所定の数の前記データブロックの前記第1データ保全性フィールドを読み出す処理と、

前記第3レジスタに格納される前記第1誤り符号と、前記第4レジスタに格納される前記第1データ保全性フィールドに含まれる前記第1誤り符号とを比較することによって、前記メモリから読み出された前記ユーザデータが破損しているか否かを判定する処理と、

を含むことを特徴とするデータ処理方法。 - 複数のデータブロックを含むユーザデータの書き込み及び読み出しを行う計算機であって、

プロセッサ、前記プロセッサに接続されるメモリ、前記プロセッサに接続される記憶媒体、及び前記プロセッサに接続される接続インタフェースを備え、

前記プロセッサは、

複数のレジスタを有し、

前記ユーザデータの書き込みリクエストを受信し、

前記書き込みリクエストに従って書き込まれる前記ユーザデータを前記メモリに格納し、

前記複数のレジスタを用いて、複数の暗号化データブロックを含む暗号化ユーザデータを生成する暗号化処理を実行し、

前記暗号化ユーザデータに含まれる前記複数の暗号化データブロックの各々に、第1誤り符号を含む第1データ保全性フィールドを付加し、

前記暗号化ユーザデータを前記記憶媒体に格納し、

前記暗号化処理では、

所定の数の前記データブロックから、前記データブロックの一部である部分データを読み出し、第1レジスタに格納する第1処理と、

前記第1レジスタに格納される前記部分データを暗号化した暗号化部分データを第2レジスタに格納する第2処理と、

前記第2レジスタに格納される前記暗号化部分データを用いて、前記第1誤り符号を算出するための第1演算を実行し、前記第1演算の結果を第3レジスタに格納する第3処理と、

が繰り返し実行され、

前記第1データ保全性フィールドには、前記暗号化データブロックの格納位置を示す第1アドレスを設定することができ、

前記プロセッサは、

第4レジスタに、所定の数の前記暗号化データブロックの前記第1誤り符号を読み出し、

前記第4レジスタに格納される前記第1誤り符号に、当該第1誤り符号が付加される前記暗号化データブロックの前記第1アドレスを追加することによって、前記第1データ保全性フィールドを生成し、

前記第1データ保全性フィールドには、前記データブロックの書き込みの世代を表す第1世代番号を設定することができ、

前記プロセッサは、前記第4レジスタに格納される前記第1誤り符号に、当該第1誤り符号が付加される前記暗号化データブロックの前記第1世代番号を追加することによって、前記第1データ保全性フィールドを生成することを特徴とする計算機。 - 請求項15に記載の計算機であって、

前記プロセッサは、

前記暗号化ユーザデータの読み出しリクエストを受信し、

前記記憶媒体から、前記読み出しリクエストによって指定された前記暗号化ユーザデータを読み出し、前記メモリに格納し、

前記複数のレジスタを用いて、前記暗号化ユーザデータを復号する復号処理を実行し、

復号された前記ユーザデータに含まれる前記複数のデータブロックの各々に、第2誤り符号を含む第2データ保全性フィールドを付加し、前記メモリに格納し、

前記復号処理では、

所定の数の前記暗号化データブロックから、前記暗号化データブロックの一部である部分暗号化データを読み出し、第5レジスタに格納する第4処理と、

前記第5レジスタに格納される前記部分暗号化データを復号した前記部分データを第6レジスタに格納する第5処理と、

前記第6レジスタに格納される前記部分データを用いて、前記第2誤り符号を算出するための第2演算を実行し、前記第2演算の結果を第7レジスタに格納する第8処理と、

が繰り返し実行されることを特徴とする計算機。 - 請求項16に記載の計算機であって、

前記第2データ保全性フィールドには、前記暗号化データブロックの格納位置を示す第2アドレスを設定することができ、

前記プロセッサは、

第8レジスタに、所定の数の前記データブロックの前記第2誤り符号を読み出し、

前記第8レジスタに格納される前記第2誤り符号に、当該第2誤り符号が付加される前記データブロックの前記第2アドレスを追加することによって、前記第2データ保全性フィールドを生成することを特徴とする計算機。 - 請求項17に記載の計算機であって、

前記第2データ保全性フィールドには、前記データブロックの書き込みの世代を表す第2世代番号を設定することができ、

前記プロセッサは、前記第8レジスタに格納される前記第2誤り符号に、当該第2誤り符号が付加される前記データブロックの前記第2世代番号を追加することによって、前記第2データ保全性フィールドを生成することを特徴とする計算機。 - 請求項18に記載の計算機であって、

前記プロセッサは、SIMD命令を用いて、前記複数のデータブロック及び前記複数の暗号化データブロックに対する処理を並列で実行することを特徴とする計算機。 - 複数のデータブロックを含むユーザデータの書き込み及び読み出しを行う計算機が実行するデータ処理方法であって、

前記計算機は、プロセッサ、前記プロセッサに接続されるメモリ、前記プロセッサに接続される記憶媒体、及び前記プロセッサに接続される接続インタフェースを備え、

前記プロセッサは、複数のレジスタを有し、

前記データ処理方法は、

前記プロセッサが、前記ユーザデータの書き込みリクエストを受信するステップと、

前記プロセッサが、前記書き込みリクエストに従って書き込まれる前記ユーザデータを前記メモリに格納するステップと、

前記プロセッサが、前記複数のレジスタを用いて、複数の暗号化データブロックを含む暗号化ユーザデータを生成する暗号化処理を実行するステップと、

前記プロセッサが、2以上の第1データ保全性フィールドを第1レジスタに格納するステップと、

前記プロセッサが、前記第1レジスタに格納された前記2以上の前記第1データ保全性フィールドの各々に、前記暗号化データブロックの格納位置を示す第1アドレスを設定する設定処理を並列に実行するステップと、

前記プロセッサが、前記暗号化ユーザデータに含まれる前記複数の暗号化データブロックの各々に、前記第1アドレスが設定された第1データ保全性フィールドを付加するステップと、

前記プロセッサが、前記暗号化ユーザデータを前記記憶媒体に格納するステップと、

を含むことを特徴とするデータ処理方法。 - 複数のデータブロックを含むユーザデータの書き込み及び読み出しを行う計算機が実行するデータ処理方法であって、

プロセッサ、前記プロセッサに接続されるメモリ、前記プロセッサに接続される記憶媒体、及び前記プロセッサに接続される接続インタフェースを有し、

前記プロセッサは、複数のレジスタを有し、

前記データ処理方法は、

前記プロセッサが、前記ユーザデータの書き込みリクエストを受信するステップと、

前記プロセッサが、前記書き込みリクエストに従って書き込まれる前記ユーザデータを前記メモリに格納するステップと、

前記プロセッサが、前記複数のレジスタを用いて、複数の暗号化データブロックを含む暗号化ユーザデータを生成する暗号化処理を実行するステップと、

前記プロセッサが、前記暗号化ユーザデータに含まれる前記複数の暗号化データブロックの各々に、第1誤り符号を含む第1データ保全性フィールドを付加するステップと、

前記プロセッサが、前記暗号化ユーザデータを前記記憶媒体に格納するステップと、

を含み、

前記暗号化処理では、

所定の数の前記データブロックから、前記データブロックの一部である部分データを読み出し、第1レジスタに格納する第1処理と、

前記第1レジスタに格納される前記部分データを暗号化した暗号化部分データを第2レジスタに格納する第2処理と、

前記第2レジスタに格納される前記暗号化部分データを用いて、前記第1誤り符号を算出するための第1演算を実行し、前記第1演算の結果を第3レジスタに格納する第3処理と、

が繰り返し実行され、

前記第1データ保全性フィールドには、前記暗号化データブロックの格納位置を示す第1アドレスを設定することができ、

前記プロセッサは、

第4レジスタに、所定の数の前記暗号化データブロックの前記第1誤り符号を読み出し、

前記第4レジスタに格納される前記第1誤り符号に、当該第1誤り符号が付加される前記暗号化データブロックの前記第1アドレスを追加することによって、前記第1データ保全性フィールドを生成し、

前記第1データ保全性フィールドには、前記データブロックの書き込みの世代を表す第1世代番号を設定することができ、

前記プロセッサは、前記第4レジスタに格納される前記第1誤り符号に、当該第1誤り符号が付加される前記暗号化データブロックの前記第1世代番号を追加することによって、前記第1データ保全性フィールドを生成することを特徴とするデータ処理方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2022141346A JP7583000B2 (ja) | 2022-09-06 | 2022-09-06 | 計算機及びデータ処理方法 |

| US18/112,079 US12430475B2 (en) | 2022-09-06 | 2023-02-21 | Computer and data processing method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2022141346A JP7583000B2 (ja) | 2022-09-06 | 2022-09-06 | 計算機及びデータ処理方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2024036837A JP2024036837A (ja) | 2024-03-18 |

| JP7583000B2 true JP7583000B2 (ja) | 2024-11-13 |

Family

ID=90060644

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022141346A Active JP7583000B2 (ja) | 2022-09-06 | 2022-09-06 | 計算機及びデータ処理方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US12430475B2 (ja) |

| JP (1) | JP7583000B2 (ja) |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20210150074A1 (en) | 2020-12-23 | 2021-05-20 | Jose Niell | Vm encryption of block storage with end-to-end data integrity protection in a smartnic |

| JP2021132342A (ja) | 2020-02-20 | 2021-09-09 | 株式会社日立製作所 | ストレージシステム及び暗号処理方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8194854B2 (en) | 2008-02-27 | 2012-06-05 | Intel Corporation | Method and apparatus for optimizing advanced encryption standard (AES) encryption and decryption in parallel modes of operation |

| US10320558B2 (en) | 2012-05-07 | 2019-06-11 | Dark Signal Research, Llc | Method and apparatus for a secure and deduplicated write once read many virtual disk |

| CN116134421A (zh) * | 2020-07-14 | 2023-05-16 | 微软技术许可有限责任公司 | 向多瓦片处理系统流式传输数据 |

| KR20220124923A (ko) * | 2021-03-04 | 2022-09-14 | 삼성전자주식회사 | 스토리지 장치 및 스토리지 장치의 동작 방법 |

-

2022

- 2022-09-06 JP JP2022141346A patent/JP7583000B2/ja active Active

-

2023

- 2023-02-21 US US18/112,079 patent/US12430475B2/en active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2021132342A (ja) | 2020-02-20 | 2021-09-09 | 株式会社日立製作所 | ストレージシステム及び暗号処理方法 |

| US20210150074A1 (en) | 2020-12-23 | 2021-05-20 | Jose Niell | Vm encryption of block storage with end-to-end data integrity protection in a smartnic |

Non-Patent Citations (2)

| Title |

|---|

| Keith Holt,"End-to-End Data Protection Justification",T10/03-224r0,T10 Technical Committee,2003年06月01日,[2024年5月17日検索],インターネット <URL:https://www.t10.org/ftp/t10/document.03/03-224r0.pdf> |

| 岡田 尚也,"ストレージシステム適用に向けたプロセッサPCIe性能の評価",FIT2016 第15回情報科学技術フォーラム 講演論文集 第1分冊,2016年 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20240078347A1 (en) | 2024-03-07 |

| JP2024036837A (ja) | 2024-03-18 |

| US12430475B2 (en) | 2025-09-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11301344B2 (en) | Aggregate GHASH-based message authentication code (MAC) over multiple cachelines with incremental updates | |

| US10761928B2 (en) | Combined secure mac and device correction using encrypted parity with multi-key domains | |

| US9819659B2 (en) | Iterative data secret-sharing transformation | |

| CN103975302B (zh) | 矩阵乘法累加指令 | |

| US8150031B2 (en) | Method and apparatus to perform redundant array of independent disks (RAID) operations | |

| US8464125B2 (en) | Instruction-set architecture for programmable cyclic redundancy check (CRC) computations | |

| TWI642294B (zh) | 具有鑑認指令之密碼訊息之電腦程式產品、系統及方法 | |

| US10235134B1 (en) | Rotating bit values while generating a large, non-compressible data stream | |

| US10656996B2 (en) | Integrated security and data redundancy | |

| CN109800103B (zh) | 密码系统存储器管理 | |

| US20120166909A1 (en) | Method and apparatus for increasing data reliability for raid operations | |

| US10038733B1 (en) | Generating a large, non-compressible data stream | |

| US12341532B2 (en) | Accelerated polynomial coding system and method | |

| US10163371B1 (en) | Rotating bit values based on a data structure while generating a large, non-compressible data stream | |

| JP2023130311A (ja) | サイドチャネル攻撃から電子コンピュータを保護する方法及び電子コンピュータ | |

| JP2010532880A (ja) | データセキュリティのためにデータを処理するシステム及び方法 | |

| JP7583000B2 (ja) | 計算機及びデータ処理方法 | |

| CN117331746A (zh) | 用于独立磁盘冗余阵列的设备 | |

| CN108572882B (zh) | 一种数据存储的方法及存储设备 | |

| CN117850667A (zh) | 数据保护和恢复 | |

| JP5278115B2 (ja) | 冗長符号生成方法及び装置、データ復元方法及び装置、並びにraid記憶装置 | |

| US12130701B1 (en) | Residue-code-based error detection for cipher generation | |

| Klein et al. | Storage architecture with integrity, redundancy and encryption | |

| CN117331747A (zh) | 非缓存数据传送 | |

| HK40003948B (en) | Cipher message with authentication instruction |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230522 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240528 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20240709 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20240814 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240924 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20241008 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20241031 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7583000 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |