JP7581370B2 - ニューラルネットワークパラメーターの表現の改良された概念 - Google Patents

ニューラルネットワークパラメーターの表現の改良された概念 Download PDFInfo

- Publication number

- JP7581370B2 JP7581370B2 JP2022562943A JP2022562943A JP7581370B2 JP 7581370 B2 JP7581370 B2 JP 7581370B2 JP 2022562943 A JP2022562943 A JP 2022562943A JP 2022562943 A JP2022562943 A JP 2022562943A JP 7581370 B2 JP7581370 B2 JP 7581370B2

- Authority

- JP

- Japan

- Prior art keywords

- representation

- parameters

- parameter

- matrix

- deriving

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/06—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons

- G06N3/063—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons using electronic means

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F17/00—Digital computing or data processing equipment or methods, specially adapted for specific functions

- G06F17/10—Complex mathematical operations

- G06F17/16—Matrix or vector computation, e.g. matrix-matrix or matrix-vector multiplication, matrix factorization

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F5/00—Methods or arrangements for data conversion without changing the order or content of the data handled

- G06F5/01—Methods or arrangements for data conversion without changing the order or content of the data handled for shifting, e.g. justifying, scaling, normalising

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/38—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation

- G06F7/48—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation using non-contact-making devices, e.g. tube, solid state device; using unspecified devices

- G06F7/52—Multiplying; Dividing

- G06F7/523—Multiplying only

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/045—Combinations of networks

- G06N3/0455—Auto-encoder networks; Encoder-decoder networks

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/0464—Convolutional networks [CNN, ConvNet]

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/0495—Quantised networks; Sparse networks; Compressed networks

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/0499—Feedforward networks

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- General Engineering & Computer Science (AREA)

- Computing Systems (AREA)

- Data Mining & Analysis (AREA)

- Software Systems (AREA)

- Biophysics (AREA)

- Biomedical Technology (AREA)

- Life Sciences & Earth Sciences (AREA)

- Health & Medical Sciences (AREA)

- General Health & Medical Sciences (AREA)

- Molecular Biology (AREA)

- Evolutionary Computation (AREA)

- Computational Linguistics (AREA)

- Artificial Intelligence (AREA)

- Pure & Applied Mathematics (AREA)

- Computational Mathematics (AREA)

- Mathematical Analysis (AREA)

- Mathematical Optimization (AREA)

- Algebra (AREA)

- Databases & Information Systems (AREA)

- Neurology (AREA)

- Compression, Expansion, Code Conversion, And Decoders (AREA)

Description

output=L2(L1(input))

ここで、

Li(X)=Ni(Bi(X))

であり、式中、Biは層iのアフィン変換であり、Niは層iの何らかの非線形関数である。

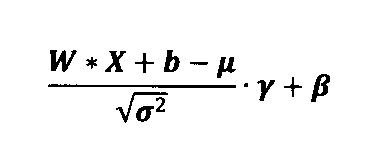

いわゆる「バイアス層」の場合、Biは、層iに関連する重みパラメーター(エッジ重み)Wiと層iの入力Xiとの行列乗算と、それに続くバイアスbiとの和である。

Bi(X)=Wi*Xi+bi

Wiは、次元ni×kiを有する重み行列であり、Xiは、次元ki×miを有する入力行列である。バイアスbiは、長さniの転置ベクトルである。演算子*は、行列乗算を示すものとする。バイアスbiとの和は、行列の列に対する要素ごとの演算である。より正確には、Wi*Xi+biは、biがWi*Xiの各列に追加されることを意味する。

ニューラルネットワーク層のアフィン変換のより洗練された変形例として、以下のような、いわゆるバイアス及びバッチノルム演算が挙げられる。

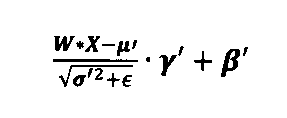

式1:

対照的に、ε並びにμ及びβの全てのベクトル要素が0に設定され、γ及びσ2の全ての要素が1に設定される場合、バッチノルムのない層(バイアスのみ)が処理される。

パラメーターW、b、μ、σ2、γ、及びβは、集合的に層のパラメーターを示すものとする。それらは通常、ビットストリーム中でシグナリングされる必要がある。例えば、それらは32ビットの浮動小数点数として表すことができ、又は整数表現に量子化することができる。εは通常、ビットストリーム中でシグナリングされないことに留意されたい。

本発明の第1の態様によれば、本出願の発明者らは、ニューラルネットワーク(NN)表現が直面する1つの問題が、ニューラルネットワークが数百万のパラメーターを含み、したがってその表現のために数百メガバイトを必要とし得るという事実から生じることを認識した。したがって、その推論手順には、大きな行列間の多くの内積演算の計算が含まれるため、その実行には高い計算リソースが必要となる。本出願の第1の態様によれば、この困難は、NNパラメーターの量子化を使用することによって克服され、浮動小数点演算をほとんど又は全く用いずに推論が可能となる。本発明者らは、乗数及びビットシフト数を導出することができる量子化パラメーターを決定することが有利であることを見出した。これは、ビットレートに関して、32ビット浮動小数点値の代わりに量子化パラメーター及び量子化値(quantization value)のみをシグナリングすることが効率的であるという着想に基づいている。NNパラメーターの量子化された値(quantized value)は、乗数、ビットシフト数、及び量子化値を使用して算出することができるため、浮動小数点領域の代わりに整数領域において、計算、例えばNNパラメーターの和及び/又はNNパラメーターとベクトルとの乗算を実行することが可能である。したがって、提示するNN表現を用いて、推論の効率的な計算を達成することができる。

μ、σ2、γ、及びβは、バッチノルムパラメーター、例えば、各出力ノードについて1つの成分を含む転置ベクトルであり、

Wは、重み行列であり、例えば、その各行は1つの出力ノードに対するものであり、それぞれの行の各成分はXの1つの行に関連付けられており、

Xは、NN層の活性化から導出される入力行列であり、

bは、バイアスを形成する転置ベクトル、例えば、各出力ノードに対して1つの成分を含む転置ベクトルであり、

εは、ゼロ除算回避のための定数であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示す。

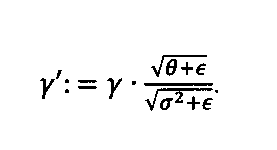

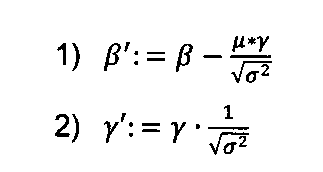

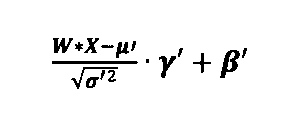

装置は、b及びμ及びγ及びβ及びσ2又はσを受信し、

加えて、装置は、β’及びγ’をNN表現に符号化するように構成され、例えば、出力ノードごとに1つの成分を含む転置ベクトルもバッチノルム演算子のNNパラメーターとして符号化するように構成され、バッチノルム演算子を

σ’2:=θ、μ’:=0、b’:=0であり、ここで、θは所定のパラメーターである。

μ、σ2、γ、及びβは、バッチノルムパラメーター、例えば、各出力ノードについて1つの成分を含む転置ベクトルであり、

Wは、重み行列であり、例えば、その各行は1つの出力ノードに対するものであり、それぞれの行の各成分はXの1つの行に関連付けられており、

Xは、NN層の活性化から導出される入力行列であり、

bは、バイアスを形成する転置ベクトル、例えば、各出力ノードに対して1つの成分を含む転置ベクトルであり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示す。

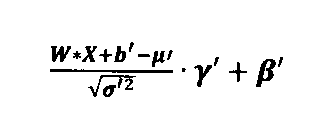

装置は、b及びμ及びγ及びβ及びσ2又はσを受信し、

加えて、装置は、バッチノルム演算子のNNパラメーターとしてβ’及びγ’をNN表現に符号化するように構成され、バッチノルム演算子を

σ’2:=1、μ’:=0、b’:=0である。

μ、σ2、γ、及びβは、バッチノルムパラメーター、例えば、各出力ノードについて1つの成分を含む転置ベクトルであり、

Wは、重み行列であり、例えば、その各行は1つの出力ノードに対するものであり、それぞれの行の各成分はXの1つの行に関連付けられており、

Xは、NN層の活性化から導出される入力行列であり、

εは、ゼロ除算回避のための定数であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示す。

装置は、μ及びγ及びβ及びσ2又はσを受信し、

加えて、装置は、バッチノルム演算子のNNパラメーターとしてβ’及びγ’をNN表現に符号化するように構成され、バッチノルム演算子を

σ’2:=θ、μ’:=0であり、θは所定のパラメーターである。

μ、σ2、γ、及びβは、バッチノルムパラメーター、例えば、各出力ノードについて1つの成分を含む転置ベクトルであり、

Wは、重み行列であり、例えば、その各行は1つの出力ノードに対するものであり、それぞれの行の各成分はXの1つの行に関連付けられており、

Xは、NN層の活性化から導出される入力行列であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示す。

装置は、μ及びγ及びβ及びσ2又はσを受信し、

加えて、装置は、バッチノルム演算子のNNパラメーターとしてβ’及びγ’をNN表現に符号化するように構成され、バッチノルム演算子を

σ’2:=1、μ’:=0である。

加えて、方法は、β’及びγ’をバッチノルム演算子のNNパラメーターとしてNN表現に符号化することであって、バッチノルム演算子を

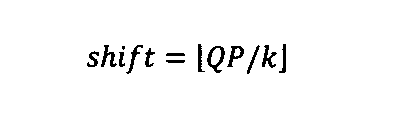

mul=k+QP%k

Δ=mul・2shift-t

一実施形態によれば、NNパラメトライザー410は、装置300を介して、第1のNNパラメーター及び第2のNNパラメーターのうちの少なくとも1つを導出するように構成され、それにより、第1のNNパラメーターは、第1の量子化値と第1の因数との間の積であって、第1のビット数だけビットシフトされた積に対応し、第2のNNパラメーターは、第2の量子化値と第2の因数との間の積であって、第2のビット数だけビットシフトされた積に対応する。

D=Δb・Dbが成り立つ第2の量子化行列Dbを考える。

すなわち、Caは、QPaを使用して量子化され、Dbは、QPbを使用して量子化されている。

両方の行列は、同じ次元を有する。図2で説明した量子化値152は、Caの1つの成分又はDbの1つの成分を表すことができる。例えば、Caは、複数の第1の量子化値152を含むことができ、Dbは、複数の第2の量子化値152を含むことができる。

一実施形態によれば、NNパラメトライザー410は、装置300を介して、第3のNNパラメーター及び第4のNNパラメーターのうちの少なくとも1つを導出するように構成され、それにより、第3のNNパラメーターは、第3の量子化値と第3の因数との間の積であって、第3のビット数だけビットシフトされた積に対応し、第4のNNパラメーターは、第4の量子化値と第4の因数との間の積であって、第4のビット数だけビットシフトされた積に対応する。

γ=Δb・γbが成り立つ量子化された転置ベクトルγbを考える。

すなわち、Waは、QPaを使用して量子化され、γbは、QPbを使用して量子化されている。

図2で説明した量子化値152は、Waの1つの成分又はγbの1つの成分を表すことができる。例えば、Waは複数の量子化値152を含むことができ、γbは複数の量子化値152を含むことができる。

一実施形態によれば、デバイス400は、例えば装置300を使用して、活性化を量子化された値、例えばX’’に量子化することによって、活性化について第5の量子化パラメーターQP、すなわち量子化パラメーター142、及び第5の量子化値、例えばX’、すなわち量子化値152を決定することによって、NN入力X440を量子化するように構成され、それにより、第5の量子化パラメーターQPからの第5の乗数mul、すなわち乗数144の導出は、第5の量子化パラメーターによって導出された被除数と、活性化に関連する精度パラメーターk、すなわち精度パラメーター145によって導出された除数との間の除算の剰余と、除算の商の丸めに基づく第5のビットシフト数shift、すなわちビットシフト数146とに基づいて、第5の量子化値と第5の乗数に依存する因数mul/k、すなわち因数148との間の積に対応する量子化された値が、第5のビットシフト数に依存する第5のビット数だけビットシフトされることをもたらす。

好ましい実施形態において、パラメーターQP、すなわち量子化パラメーター142は、以下の定義に従って、K次の符号付き指数ゴロム符号を使用して、装置100/装置300によってビットストリーム200内に符号化/ビットストリーム200から復号化される。

符号なし整数の符号なし指数ゴロム符号は、高効率ビデオ符号化(HEVC:High Efficiency Video Coding)規格において定義されているシンタックス要素ue(v)の復号化仕様に従うものとする。

leadingZeroBits=-1

for(b=0;!b;leadingZeroBits++)

b=read_bits(1)

decNum=(2leadingZeroBits-1)*2K+read_bits(leadingZeroBits+K)

符号付き整数の符号なし指数ゴロム符号は、高効率ビデオ符号化(HEVC)規格において定義されているシンタックス要素se(v)の復号化仕様に従うものとする。

好ましい実施形態において、パラメーターk、すなわち精度パラメーター145は、2tに設定され、パラメーターtは、bits_tビットを有する(例えば、bits_t=3又はbits_t=4を有する)符号なし整数表現を使用して符号化される。

図5に示される更なる好ましい実施形態は、重みパラメーターW545の表現に関する。すなわち、それらをベクトル546と行列544との合成W→s・W’として因数分解する。W及びW’、すなわち重み行列544は、次元n×mの行列であり、sは、長さnの転置ベクトル546である。ベクトルs546の各要素は、重み行列W’544の行方向のスケーリングファクターとして使用される。換言すれば、s546は、W’544の各列と要素ごとに乗算される。s546をローカルスケーリングファクター又はローカルスケール適応(LSA:local scale adaptation)と称する。

図6に示す一実施形態は、バッチノルム圧縮を改善することに関する。図6は、NNのバッチノルム演算子710のNNパラメーター610、例えば、μ、σ2、γ、β、及び任意選択でbをNN表現110に符号化する装置600と、NN表現110からNNのバッチノルム演算子710のNNパラメーター610、例えば、γ722及びβ724及びパラメーター732、すなわち、μ、σ2、及び任意選択でbを復号化する装置700とを示している。4つの実施形態が示されており、第1の実施形態は一般的な場合を説明し、他の実施形態は特別な場合を対象とする。

μ、σ2、γ、及びβは、バッチノルムパラメーター、例えば、各出力ノードについて1つの成分を含む転置ベクトルであり、

Wは、重み行列であり、例えば、その各行は1つの出力ノードに対するものであり、それぞれの行の各成分はXの1つの行に関連付けられており、

Xは、NN層の活性化から導出される入力行列であり、

bは、バイアスを形成する転置ベクトル、例えば、各出力ノードに対して1つの成分を含む転置ベクトルであり、

εは、ゼロ除算回避のための定数であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示す。

4)μ:=0

5)b:=0

Claims (62)

- NN表現(110)を生成する装置(100)であって、前記NN表現(110)は、NNパラメーター(130)を表すために、量子化パラメーター(142)及び量子化値(152)を含み、前記装置(100)は、

量子化パラメーター(142)から、

前記量子化パラメーター(142)によって導出された被除数と精度パラメーター(145)によって導出された除数との間の除算の剰余に基づく乗数(144)と、

前記除算の商の丸めに基づくビットシフト数(146)と、

が導出可能であるように、NNパラメーター(120)の前記量子化パラメーター(142)及び量子化値(152)を決定(140)することによって、前記NNパラメーター(120)を量子化された値(130)に量子化するように構成され、

それにより、前記NNパラメーター(120)の前記量子化された値(130)は、前記量子化値(152)と前記乗数(144)に依存する因数(148)との間の積であって、前記ビットシフト数(146)に依存するビット数だけビットシフトされた積に対応する、装置。 - NN表現(110)からNNパラメーターを導出する装置であって、

前記NN表現(110)から量子化パラメーター(142)を導出することと、

前記NN表現(110)から量子化値(152)を導出することと、

前記量子化パラメーター(142)から、

前記量子化パラメーター(142)によって導出された被除数と精度パラメーター(145)によって導出された除数との間の除算の剰余に基づく乗数(144)と、

前記除算の商の丸めに基づくビットシフト数(146)と、

を導出することと、

を行うように構成され、

前記NNパラメーター(130)は、前記量子化値(152)と前記乗数(144)に依存する因数(148)との間の積であって、前記ビットシフト数(146)に依存するビット数だけビットシフトされた積に対応する、装置。 - 前記NN表現(110)から前記精度パラメーター(145)を導出するように更に構成されている、請求項2に記載の装置。

- 前記NNパラメーター(130)は、

一対のニューロン(10)間のニューロン間活性化フィードフォワード(12)に重み付けする重みパラメーター、

ニューラルネットワーク層のアフィン変換をパラメーター化するバッチノルムパラメーター、及び

所定のニューラルネットワークニューロン(10)のインバウンドニューロン間活性化フィードフォワード(12)の和にバイアスをかけるバイアス、

のうちの1つである、請求項2又は3に記載の装置。 - 前記NNパラメーター(130)は、NNの複数のニューロン間活性化フィードフォワード(122)のうちの単一のニューロン間活性化フィードフォワード(12)に関して前記NNをパラメーター化し、前記装置は、前記複数のニューロン間活性化フィードフォワード(122)の各々について、前記NN表現(110)から、対応するNNパラメーター(130)を、

前記複数のニューロン間活性化フィードフォワード(122)の各々(12)について、

前記NN表現(110)から前記それぞれのニューロン間活性化フィードフォワード(12)に関連付けられた関連量子化パラメーター(142)を導出することと、

前記NN表現(110)から前記それぞれのニューロン間活性化フィードフォワード(12)に関連付けられた関連量子化値(152)を導出することと、

前記関連量子化パラメーター(142)から、

前記関連量子化パラメーター(142)によって導出された被除数と、前記それぞれのニューロン間活性化フィードフォワード(12)に関連付けられた関連精度パラメーター(145)によって導出された除数との間の除算の剰余に基づいて、前記それぞれのニューロン間活性化フィードフォワード(12)に関連付けられた関連乗数(144)と、

前記除算の商の丸めに基づいて、前記それぞれのニューロン間活性化フィードフォワード(12)に関連付けられた関連ビットシフト数(146)と、を導出することと、

によって導出するように構成され、

前記それぞれのニューロン間活性化フィードフォワード(12)の前記対応するNNパラメーター(130)は、前記関連量子化値(152)と前記関連乗数(144)に依存する因数(148)との間の積であって、前記関連ビットシフト数(146)に依存するビット数だけビットシフトされた積に対応する、請求項2~4のいずれか一項に記載の装置。 - 前記装置は、NNの複数のニューロン間活性化フィードフォワード(122)をニューロン間活性化フィードフォワードのサブグループ(122a、122b)に細分するように構成され、それにより、各サブグループ(122a、122b)が、前記NNの関連する一対のNN層に関連付けられ、前記関連する一対のNN層の間のニューロン間活性化フィードフォワードを含み、前記関連する一対の層以外の更なる一対のNN層の間のニューロン間活性化フィードフォワードを除外し、2つ以上のサブグループ(122a、122b)が、所定のNN層に関連付けられ、

前記NNパラメーター(130)は、前記NNの前記複数のニューロン間活性化フィードフォワード(122)のうちの単一のニューロン間活性化フィードフォワード(12)に関して前記NNをパラメーター化し、前記装置は、前記複数のニューロン間活性化フィードフォワード(122)の各々について、前記NN表現(110)から、対応するNNパラメーター(130)を、

ニューロン間活性化フィードフォワードの各サブグループ(122a、122b)について、

前記NN表現(110)から前記それぞれのサブグループ(122a、122b)に関連付けられた関連量子化パラメーター(142)を導出することと、

前記関連量子化パラメーター(142)から、

前記関連量子化パラメーター(142)によって導出された被除数と、前記それぞれのサブグループ(122a,122b)に関連付けられた関連精度パラメーター(145)によって導出された除数との間の除算の剰余に基づいて、前記それぞれのサブグループ(122a,122b)に関連付けられた関連乗数(144)と、

前記除算の商の丸めに基づいて、前記それぞれのサブグループ(122a、122b)に関連付けられた関連ビットシフト数(146)と、を導出することと、

前記複数のニューロン間活性化フィードフォワード(122)の各々について、

前記NN表現(110)から前記それぞれのニューロン間活性化フィードフォワード(12)に関連付けられた関連量子化値(152)を導出することと、

によって導出するように構成され、

前記それぞれのニューロン間活性化フィードフォワード(12)の前記対応するNNパラメーター(130)は、前記それぞれのニューロン間活性化フィードフォワード(12)が含まれる前記サブグループ(122a、122b)に関連付けられた、前記関連量子化値(152)と前記関連乗数(144)に依存する因数(148)との間の積であって、前記それぞれのニューロン間活性化フィードフォワード(12)が含まれる前記サブグループ(122a、122b)の前記関連ビットシフト数(146)に依存するビット数だけビットシフトされた積に対応する、請求項2~4のいずれか一項に記載の装置。 - 前記関連精度パラメーター(145)は、前記NNにわたって又は各NN層内でグローバルに等しく評価される、請求項5又は6に記載の装置。

- 前記NN表現(110)から前記関連精度パラメーター(145)を導出するように構成されている、請求項5~7のいずれか一項に記載の装置。

- 前記NN表現(110)から前記関連量子化パラメーター(142)を基準量子化パラメーターとの差分の形態で導出するように構成されている、請求項5~8のいずれか一項に記載の装置。

- 前記量子化パラメーター(142)から、前記乗数(144)及び前記ビットシフト数(146)を、

mul=k+QP%k

(mul/k)・2 shift ・P

であり、式中、Pは、前記量子化値(152)である、請求項2~9のいずれか一項に記載の装置。 - 前記精度パラメーター(145)は、2の累乗である、請求項2~10のいずれか一項に記載の装置。

- コンテキスト適応型二値算術復号化の使用によって、又は

前記NN表現(110)から前記量子化パラメーター(142)を表すビットを直接読み出すことによって、又は

前記装置のコンテキスト適応型二値デコーダーの等確率バイパスモードを介して、前記NN表現(110)から前記量子化パラメーター(142)を表すビットを導出することによって、

前記NN表現(110)から前記量子化パラメーター(142)を導出するように構成されている、請求項2~11のいずれか一項に記載の装置。 - 二値化方式を使用してビンストリングを非二値化することによって、前記NN表現(110)から前記量子化パラメーター(142)を導出するように構成されている、請求項2~12のいずれか一項に記載の装置。

- 前記二値化方式は、指数ゴロム符号である、請求項13に記載の装置。

- 固定小数点表現の形態で前記NN表現(110)から前記量子化パラメーター(142)を導出するように構成されている、請求項2~14のいずれか一項に記載の装置。

- 前記精度パラメーター(145)は、2 t であり、前記固定小数点表現のビット長は、前記NNに対して一定になるように設定されるか、又は前記NNに対して一定である基底ビット長とtとの和になるように設定される、請求項15に記載の装置。

- 整数値シンタックス要素として前記NN表現(110)から前記量子化パラメーター(142)を導出するように構成されている、請求項2~16のいずれか一項に記載の装置。

- 前記NN表現(110)から前記精度パラメーター(145)を表すビットを直接読み出すことによって、又は前記装置のコンテキスト適応型二値デコーダーの等確率バイパスモードを介して前記NN表現(110)から前記精度パラメーター(145)を表すビットを導出することによって、前記NN表現(110)から前記精度パラメーター(145)を導出するように構成されている、請求項2~17のいずれか一項に記載の装置。

- 固定小数点表現の形態で前記NN表現(110)から前記量子化値(152)を導出するように構成されている、請求項2~18のいずれか一項に記載の装置。

- 二値化方式に従ってビンストリングから前記量子化値(152)を非二値化し、コンテキスト適応算術復号化を使用して前記NN表現(110)から前記ビンストリングのビットを復号化することによって、前記NN表現(110)から前記量子化値(152)を導出するように構成されている、請求項2~19のいずれか一項に記載の装置。

- 二値化方式に従ってビンストリングから前記量子化値(152)を非二値化し、コンテキスト適応算術復号化を使用して前記NN表現(110)から前記ビンストリングの第1のビットを復号化し、等確率バイパスモードを使用して前記ビンストリングの第2のビットを復号化することによって、前記NN表現(110)から前記量子化値(152)を導出するように構成されている、請求項2~20のいずれか一項に記載の装置。

- NN(20)を使用して推論を実行するデバイス(400)であって、前記デバイス(400)は、

前記NN(20)をパラメーター化するように構成されたNNパラメトライザー(410)であって、前記NNパラメトライザー(410)は、請求項2~21のいずれか一項に記載のNN表現(110)からNNパラメーター(130)を導出する装置(300)を備える、NNパラメトライザー(410)と、

前記NN(20)を使用してNN入力(440)に基づいて推論出力(430)を計算するように構成された計算ユニット(420)と、

を備える、デバイス。 - 請求項22に記載のデバイス(400)であって、

前記NNパラメトライザー(410)は、

前記装置(300)を介して、第1のNNパラメーター(130)及び第2のNNパラメーター(130)のうちの少なくとも1つを導出することであって、それにより、前記第1のNNパラメーター(130)は、第1の量子化値(152)と第1の因数(148)との積であって、第1のビット数(146)だけビットシフトされた積に対応し、前記第2のNNパラメーター(130)は、第2の量子化値(152)と第2の因数(148)との積であって、第2のビット数(146)だけビットシフトされた積に対応することと、

前記第1のNNパラメーター(130)の第1の量子化値(152)によって形成され、前記第1の乗数(144)で重み付けされた第1の加数と、前記第1のNNパラメーター(130)の第2の量子化値(152)によって形成され、前記第2の乗数(144)で重み付けされ、前記第1のビット数(146)及び前記第2のビット数(146)の差だけビットシフトされた第2の加数との間の和を形成することと、前記第1の加数及び前記第2の加数の前記和を、前記第1のビット数(146)及び前記第2のビット数(146)のうちの1つに依存するビット数だけビットシフトすることと、によって、前記第1のNNパラメーター(130)及び前記第2のNNパラメーター(130)に加算を施して、前記NN(20)の最終NNパラメーター(130)を生成することと、

を行うように構成されている、デバイス。 - 請求項23に記載のデバイス(400)であって、

前記第1のNNパラメーター(130)は、前記NN(20)のベース層表現を表し、前記第2のNNパラメーター(130)は、前記NNのエンハンスメント層表現を表すか、又は

前記第1のNNパラメーター(130)は、前記NN(20)の現在の表現を表し、前記第2のNNパラメーター(130)は、前記現在のNN表現(110)の更新を表すか、又は

前記第1のNNパラメーター(130)は、所定のニューラルネットワークニューロン(10)のインバウンドニューロン間活性化フィードフォワード(12)の和にバイアスをかけるバイアスを表し、前記第2のNNパラメーター(130)は、ニューラルネットワーク層のアフィン変換をパラメーター化するバッチノルムパラメーターを表す、デバイス。 - 請求項22~24のいずれか一項に記載のデバイス(400)であって、

前記NNパラメトライザー(410)は、

前記装置(300)を介して、第3のNNパラメーター(130)及び第4のNNパラメーター(130)のうちの少なくとも1つを導出するように構成され、それにより、前記第3のNNパラメーター(130)は、第3の量子化値(152)と第3の因数(148)との積であって、第3のビット数(146)だけビットシフトされた積に対応し、前記第4のNNパラメーター(130)は、第4の量子化値(152)と第4の因数(148)との積であって、第4のビット数(146)だけビットシフトされた積に対応し、

前記計算ユニット(420)は、前記計算を実行する際に、

前記第3のNNパラメーター(130)及び前記第4のNNパラメーター(130)に乗算を施して、前記第3のNNパラメーター(130)の第3の量子化値(152)によって形成される第1の因数と、前記第3の乗数(144)によって形成される第2の因数と、前記第4のNNパラメーター(130)の第4の量子化値(152)によって形成される第3の因数と、前記第4の乗数(144)によって形成される第4の因数との積であって、前記第3のビット数によって形成される第1の加数と前記第4のビット数によって形成される第2の加数とを含む和に対応するビット数だけビットシフトされた積を形成することによって積を生成するように構成される、デバイス。 - 請求項25に記載のデバイス(400)であって、

前記第3のNNパラメーター(130)は、第1のNN層(114)の第1のニューロン(101)から第2のNN層(116)の第2のニューロン(10 2 )へのニューロン間活性化フィードフォワード(12)を重み付けする重みパラメーターを表し、前記第4のNNパラメーター(130)は、バッチノルムパラメーターを表す、デバイス。 - 請求項26に記載のデバイス(400)であって、前記バッチノルムパラメーターは、前記第2のNN層に対して前記第1のニューロン(10 1 )の活性化フィードフォワード増幅を調整するものである、デバイス。

- 請求項22~27のいずれか一項に記載のデバイス(400)であって、

活性化について第5の量子化パラメーター(142)及び第5の量子化値(152)を決定することによって、前記活性化を量子化された値(130)に量子化することによって前記NN入力(440)を量子化し、前記第5の量子化パラメーター(142)から、前記第5の量子化パラメーター(142)によって導出された被除数と前記活性化に関連付けられた精度パラメーター(145)によって導出された除数との間の除算の剰余に基づく第5の乗数(144)と、前記除算の商の丸めに基づく第5のビットシフト数(146)とを導出することにより、前記第5の量子化値(152)と前記第5の乗数(144)に依存する因数(148)との間の積であって、前記第5のビットシフト数(146)に依存する第5のビット数だけビットシフトされた積に対応する前記量子化された値(130)が得られるように更に構成されている、デバイス。 - 請求項28に記載のデバイス(400)であって、

前記NNパラメトライザー(410)は、

前記装置(300)を介して、第6のNNパラメーター(130)を導出することであって、それにより、前記第6のNNパラメーター(130)は、第6の量子化値(152)と第6の因数(148)との積であって、第6のビット数(146)だけビットシフトされた積に対応することと、

前記第6のNNパラメーター(130)及び前記活性化に乗算を施して、前記第6のNNパラメーター(130)の第6の量子化値(152)によって形成される第1の因数と、前記第6の乗数(144)によって形成される第2の因数と、前記第5の量子化値(152)によって形成される第3の因数と、前記第5の乗数(144)によって形成される第4の因数との積であって、前記第6のビット数によって形成される第1の加数と前記第4のビット数(146)によって形成される第2の加数と、を含む和に対応するビット数だけビットシフトされた積を形成することによって積を生成することと、

を行うように構成されている、デバイス。 - NN(20)を使用して推論を実行するデバイス(500)であって、前記デバイス(500)は、前記NN(20)を使用してNN入力(440)に基づいて推論出力(430)を計算するように構成され、前記NN(20)は、一対のNN層と、前記一対のNN層のうちの第1のNN層から前記一対のNN層のうちの第2のNN層へのニューロン間活性化フィードフォワード(12)とを含み、前記デバイス(500)は、

前記第1のNN層の前記ニューラルネットワークニューロン(10)の前記活性化から行列X(532)を形成(530)することと、

s・W’*Xを計算(540)することであって、式中、*は、行列乗算を表し、W’は、n及びm∈Nである次元n×mの重み行列(544)であり、sは、長さnの転置ベクトル(546)であり、・は、・の一方の側の行列と・の他方の側の転置ベクトルとの間の列に関するアダマール乗算を示すことと、

によって、前記第1のNN層の前記ニューラルネットワークニューロン(10)の前記活性化に基づいて、前記第2のNN層の前記ニューラルネットワークニューロン(10)の活性化を計算するように構成され、

前記デバイス(500)が、NN表現(110)からW’(544)を導出するように構成されたNNパラメトライザー(410)を備え、前記NNパラメトライザー(410)は、請求項2~21のいずれか一項に記載のNN表現(110)からNNパラメーター(130)を導出する装置(300)を備えている、デバイス。 - 請求項30に記載のデバイス(500)であって、nビット固定小数点演算を使用して前記行列乗算を計算(540)して、内積を生成し、m>nであるmビット固定小数点演算を使用して前記内積をs(546)と乗算するように構成されている、デバイス。

- 請求項30又は31に記載のデバイス(500)であって、s(546)は、W’(544)を符号化するためのより高い圧縮及び/又はより高い推論忠実度に関するW’(544)の最適化の結果である、デバイス。

- 請求項30~32のいずれか一項に記載のデバイス(500)であって、前記NNパラメトライザー(410)は、W’(544)に関連するNNパラメーター(130)と比較して異なる量子化パラメーター(142)を使用して、前記NN表現(110)からs(546)を導出するように更に構成されている、デバイス。

- NN(20)のバッチノルム演算子(710)のNNパラメーターをNN表現(110)に符号化する装置(600)であって、前記バッチノルム演算子(710)は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

bは、バイアスを形成する転置ベクトルであり、

εは、ゼロ除算回避のための定数であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記装置(600)は、

b、μ、σ 2 又はσ、γ、及びβ(610)を受信することと、

β’及びγ’を前記バッチノルム演算子(710)のNNパラメーターとして前記NN表現(110)に符号化することであって、前記バッチノルム演算子(710)を

3)σ’ 2 :=θ

4)μ’:=0

5)b’:=0であり、ここで、θは所定のパラメーターであることと、

を行うように構成されており、

装置(600)が、β’及びγ’を量子化して前記NN表現(110)に符号化する、請求項1に記載の装置(100)を更に備える、装置。 - 請求項34に記載の装置(600)であって、前記所定のパラメーターは、1又は1-εである、装置。

- NNのバッチノルム演算子(710)のNNパラメーターをNN表現(110)に符号化する装置(600)であって、前記バッチノルム演算子(710)は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり

Xは、NN層の活性化から導出される入力行列であり、

bは、バイアスを形成する転置ベクトルであり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記装置(600)は、

b、μ、σ 2 又はσ、γ、及びβ(610)を受信することと、

β’及びγ’を前記バッチノルム演算子(710)のNNパラメーターとして前記NN表現(110)に符号化することであって、前記バッチノルム演算子(710)を

3)σ’ 2 :=1

4)μ’:=0

5)b’:=0であることと、

を行うように構成され、

装置(600)が、β’及びγ’を量子化して前記NN表現(110)に符号化する、請求項1に記載の装置(100)を更に備える、装置。 - NNのバッチノルム演算子(710)のNNパラメーターをNN表現(110)に符号化する装置(600)であって、前記バッチノルム演算子(710)は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

εは、ゼロ除算回避のための定数であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記装置(600)は、

μ、σ 2 又はσ、γ、及びβ(610)を受信することと、

β’及びγ’を前記バッチノルム演算子(710)のNNパラメーターとして前記NN表現(110)に符号化することであって、前記バッチノルム演算子(710)を

3)σ’ 2 :=θ

4)μ’:=0であり、ここで、θは所定のパラメーターであることと、

を行うように構成され、

装置(600)が、β’及びγ’を量子化して前記NN表現(110)に符号化する、請求項1に記載の装置(100)を更に備える、装置。 - 請求項37に記載の装置(600)であって、前記所定のパラメーターは、1又は1-εである、装置。

- NNのバッチノルム演算子(710)のNNパラメーターをNN表現(110)に符号化する装置(600)であって、前記バッチノルム演算子(710)は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記装置(600)は、

μ、σ 2 又はσ、γ、及びβ(610)を受信することと、

β’及びγ’を前記バッチノルム演算子(710)のNNパラメーターとして前記NN表現(110)に符号化することであって、前記バッチノルム演算子(710)を

3)σ’ 2 :=1

4)μ’:=0であることと、

を行うように構成され、

装置(600)が、β’及びγ’を量子化して前記NN表現(110)に符号化する、請求項1に記載の装置(100)を更に備える、装置。 - 請求項34~39のいずれか一項に記載の装置(600)であって、

前記表現において、σ’ 2 の全ての成分が互いに等しいこと、及びその値を示し、及び/又は

前記表現において、μ’の全ての成分が互いに等しいこと、及びその値を示し、及び/又は

前記表現において、存在する場合、b’の全ての成分が互いに等しいこと、及びその値を示すように更に構成されている、装置。 - 請求項34~39のいずれか一項に記載の装置(600)であって、2つのバッチノルム符号化モードの間で切り替え可能であるように更に構成され、第1のバッチノルム符号化モードでは、前記装置(600)は、β’及びγ’の前記計算及び前記符号化を実行するように構成され、第2のバッチノルム符号化モードでは、前記装置(600)は、前記受信されたμ、σ 2 又はσ、γ、及びβ、並びに存在する場合、bを符号化するように構成されている、装置。

- NN表現(110)からNNのバッチノルム演算子(710)のNNパラメーターを復号化する装置(700)であって、前記バッチノルム演算子(710)は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

bは、バイアスを形成する転置ベクトルであり、

εは、ゼロ除算回避のための定数であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記装置(700)は、

前記NN表現(110)からγ(722)及びβ(724)を導出(720)することと、

その全ての成分に適用される1つのシグナリング(734)によって、

1)σ’ 2 :=θ

2)μ’:=0

3)b’:=0であり、ここで、θは所定のパラメーターであることを推論又は導出(730)することと、

を行うように構成され、

前記NN表現(110)からβ及びγを導出する、請求項2~21のいずれか一項に記載の装置(300)を更に備える、装置。 - 請求項42に記載の装置(700)であって、前記所定のパラメーターは、1又は1-εである、装置。

- NN表現(110)からNNのバッチノルム演算子(710)のNNパラメーターを復号化する装置(700)であって、前記バッチノルム演算子(710)は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

bは、バイアスを形成する転置ベクトルであり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記装置(700)は、

前記NN表現(110)からγ(722)及びβ(724)を導出(720)することと、

その全ての成分に適用される1つのシグナリング(734)によって、

1)σ 2 :=1

2)μ:=0

3)b:=0であることを推論又は導出(730)することと、

を行うように構成され、

前記NN表現(110)からβ及びγを導出する、請求項2~21のいずれか一項に記載の装置(300)を更に備える、装置。 - NN表現(110)からNNのバッチノルム演算子(710)のNNパラメーターを復号化する装置(700)であって、前記バッチノルム演算子(710)は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

εは、ゼロ除算回避のための定数であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記装置(700)は、

前記NN表現(110)からγ(722)及びβ(724)を導出(720)することと、

その全ての成分に適用される1つのシグナリング(734)によって、

1)σ 2 :=θ

2)μ:=0であり、ここで、θは所定のパラメーターであることを推論又は導出(730)することと、

を行うように構成され、

前記NN表現(110)からβ及びγを導出する、請求項2~21のいずれか一項に記載の装置(300)を更に備える、装置。 - 請求項45に記載の装置(700)であって、前記所定のパラメーターは、1又は1-εである、装置。

- NN表現(110)からNNのバッチノルム演算子(710)のNNパラメーターを復号化する装置(700)であって、前記バッチノルム演算子(710)は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記装置(700)は、

前記NN表現(110)からγ(722)及びβ(724)を導出(720)することと、

その全ての成分に適用される1つのシグナリング(734)によって、

1)σ 2 :=1

2)μ:=0であることを推論又は導出(730)することと、

を行うように構成され、

前記NN表現(110)からβ及びγを導出する、請求項2~21のいずれか一項に記載の装置(300)を更に備える、装置。 - 請求項42~47のいずれか一項に記載の装置(700)であって、

前記表現から、σ’ 2 の全ての成分が互いに等しいこと、及びその値を導出し、及び/又は

前記表現から、μ’の全ての成分が互いに等しいこと、及びその値を導出し、及び/又は

存在する場合、前記表現から、b’の全ての成分が互いに等しいこと、及びその値を導出するように更に構成されている、装置。 - 請求項42~48のいずれか一項に記載の装置(700)であって、2つのバッチノルム符号化モード間で切り替え可能であるように更に構成され、第1のバッチノルム符号化モードでは、前記装置(700)は、前記導出することと、前記推論又は導出することと、を実行するように構成され、第2の第1のバッチノルム符号化モードでは、前記装置(700)は、μ、σ 2 又はσ、γ、及びβ、並びに存在する場合、bを前記表現から復号化するように構成されている、装置。

- NN表現を生成する方法であって、

前記NN表現は、NNパラメーターを表すために、量子化パラメーター及び量子化値を含み、

量子化パラメーターから、

前記量子化パラメーターによって導出された被除数と精度パラメーターによって導出された除数との間の除算の剰余に基づく乗数と、

前記除算の商の丸めに基づくビットシフト数と、

が導出可能であるように、NNパラメーターの前記量子化パラメーター及び量子化値を決定することによって、前記NNパラメーターを量子化された値に量子化することであって、

それにより、前記NNパラメーターの前記量子化された値は、前記量子化値と前記乗数に依存する因数との積であって、前記ビットシフト数に依存するビット数だけビットシフトされた積に対応することを含む、方法。 - NN表現からNNパラメーターを導出する方法であって、

前記NN表現から量子化パラメーターを導出することと、

前記NN表現から量子化値を導出することと、

前記量子化パラメーターから、

前記量子化パラメーターによって導出された被除数と精度パラメーターによって導出された除数との間の除算の剰余に基づく乗数と、

前記除算の商の丸めに基づくビットシフト数と、

を導出することと、

を含み、

前記NNパラメーターは、前記量子化値と前記乗数に依存する因数との積であって、前記ビットシフト数に依存するビット数だけビットシフトされた積に対応する、方法。 - NNを使用して推論を実行する方法であって、

NN表現からNNパラメーターを導出するために請求項51に記載の方法を使用して、前記NNをパラメーター化することと、

前記NNを使用して、NN入力に基づいて推論出力を計算することと、

を含む、方法。 - NNを使用して推論を実行する方法であって、前記NNを使用してNN入力に基づいて推論出力を計算することを含み、前記NNは、一対のNN層と、前記一対のNN層のうちの第1のNN層から前記一対のNN層のうちの第2のNN層へのニューロン間活性化フィードフォワードとを含み、前記方法は、

前記第1のNN層の前記ニューラルネットワークニューロンの前記活性化から行列Xを形成することと、

s・W’*Xを計算することであって、式中、*は、行列乗算を表し、W’は、n及びm∈Nである次元n×mの重み行列であり、sは、長さnの転置ベクトルであり、・は、・の一方の側の行列と・の他方の側の転置ベクトルとの間の列に関するアダマール乗算を示すことと、

によって、前記第1のNN層の前記ニューラルネットワークニューロンの活性化に基づいて、前記第2のNN層の前記ニューラルネットワークニューロンの活性化を計算することを含み、

前記方法が、請求項51に記載のNN表現(110)からNNパラメーターを導出する方法を用いて、NN表現からW’を導出する、方法。 - NNのバッチノルム演算子のNNパラメーターをNN表現に符号化する方法であって、前記バッチノルム演算子は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

bは、バイアスを形成する転置ベクトルであり、

εは、ゼロ除算回避のための定数であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記方法は、

b、μ、σ 2 又はσ、γ、及びβを受信することと、

β’及びγ’を前記バッチノルム演算子のNNパラメーターとして前記NN表現に符号化することであって、前記バッチノルム演算子を

3)σ’ 2 :=θ

4)μ’:=0

5)b’:=0であり、ここで、θは所定のパラメーターであることと、を含み、

前記方法が、β’及びγ’を量子化して前記NN表現に符号化する、請求項50に記載の方法を更に備える、方法。 - NNのバッチノルム演算子のNNパラメーターをNN表現に符号化する方法であって、前記バッチノルム演算子は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

bは、バイアスを形成する転置ベクトルであり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記方法は、

b、μ、σ 2 又はσ、γ、及びβを受信することと、

β’及びγ’を前記バッチノルム演算子のNNパラメーターとして前記NN表現に符号化することであって、前記バッチノルム演算子を

3)σ’ 2 :=1

4)μ’:=0

5)b’:=0であることと、を含み、

前記方法が、β’及びγ’を量子化して前記NN表現に符号化する、請求項50に記載の方法を更に備える、方法。 - NNのバッチノルム演算子のNNパラメーターをNN表現に符号化する方法であって、前記バッチノルム演算子は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

εは、ゼロ除算回避のための定数であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記方法は、

μ、σ 2 又はσ、γ、及びβを受信することと、

β’及びγ’を前記バッチノルム演算子のNNパラメーターとして前記NN表現に符号化することであって、前記バッチノルム演算子を

3)σ’ 2 :=θ

4)μ’:=0であり、ここで、θは所定のパラメーターであることと、を含み、

前記方法が、β’及びγ’を量子化して前記NN表現に符号化する、請求項50に記載の方法を更に備える、方法。 - NNのバッチノルム演算子のNNパラメーターをNN表現に符号化する方法であって、前記バッチノルム演算子は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記方法は、

μ、σ 2 又はσ、γ、及びβを受信することと、

β’及びγ’を前記バッチノルム演算子のNNパラメーターとして前記NN表現に符号化することであって、前記バッチノルム演算子を

3)σ’ 2 :=1

4)μ’:=0であることと、を含み、

前記方法が、β’及びγ’を量子化して前記NN表現に符号化する、請求項50に記載の方法を更に備える、方法。 - NN表現からNNのバッチノルム演算子のNNパラメーターを復号化する方法であって、前記バッチノルム演算子は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

bは、バイアスを形成する転置ベクトルであり、

εは、ゼロ除算回避のための定数であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記方法は、

前記NN表現からγ及びβを導出することと、

その全ての成分に適用される1つのシグナリングによって、

1)σ’ 2 :=θ

2)μ’:=0

3)b’:=0であり、ここで、θは所定のパラメーターであることを推論又は導出することと、を含み、

前記NN表現からβ及びγを導出する、請求項51に記載の方法を更に備える、方法。 - NN表現からNNのバッチノルム演算子のNNパラメーターを復号化する方法であって、前記バッチノルム演算子は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

bは、バイアスを形成する転置ベクトルであり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記方法は、

前記NN表現からγ及びβを導出することと、

その全ての成分に適用される1つのシグナリングによって、

1)σ 2 :=1

2)μ:=0

3)b:=0であることを推論又は導出することと、を含み、

前記NN表現からβ及びγを導出する、請求項51に記載の方法を更に備える、方法。 - NN表現からNNのバッチノルム演算子のNNパラメーターを復号化する方法であって、前記バッチノルム演算子は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

εは、ゼロ除算回避のための定数であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記方法は、

前記NN表現からγ及びβを導出することと、

その全ての成分に適用される1つのシグナリングによって、

1)σ 2 :=θ

2)μ:=0であり、ここで、θは所定のパラメーターであることを推論又は導出することと、を含み、

前記NN表現からβ及びγを導出する、請求項51に記載の方法を更に備える、方法。 - NN表現からNNのバッチノルム演算子のNNパラメーターを復号化する方法であって、前記バッチノルム演算子は、

μ、σ 2 、γ、及びβは、バッチノルムパラメーターであり、

Wは、重み行列であり、

Xは、NN層の活性化から導出される入力行列であり、

・は、・の一方の側の行列と他方の側の転置ベクトルとの間の列に関するアダマール乗算を示し、

*は、行列乗算を示し、

前記方法は、

前記NN表現からγ及びβを導出することと、

その全ての成分に適用される1つのシグナリングによって、

1)σ 2 :=1

2)μ:=0であることを推論又は導出することと、を含み、

前記NN表現からβ及びγを導出する、請求項51に記載の方法を更に備える、方法。 - コンピュータープログラムがコンピューターで実行される時、請求項50~61のいずれか一項に記載の方法を実行するコンピュータープログラム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2024190377A JP2025014032A (ja) | 2020-04-14 | 2024-10-30 | ニューラルネットワークパラメーターの表現の改良された概念 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP20169502 | 2020-04-14 | ||

| EP20169502.0 | 2020-04-14 | ||

| PCT/EP2021/059592 WO2021209469A1 (en) | 2020-04-14 | 2021-04-13 | Improved concept for a representation of neural network parameters |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2024190377A Division JP2025014032A (ja) | 2020-04-14 | 2024-10-30 | ニューラルネットワークパラメーターの表現の改良された概念 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2023522886A JP2023522886A (ja) | 2023-06-01 |

| JP7581370B2 true JP7581370B2 (ja) | 2024-11-12 |

Family

ID=70456712

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022562943A Active JP7581370B2 (ja) | 2020-04-14 | 2021-04-13 | ニューラルネットワークパラメーターの表現の改良された概念 |

| JP2024190377A Pending JP2025014032A (ja) | 2020-04-14 | 2024-10-30 | ニューラルネットワークパラメーターの表現の改良された概念 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2024190377A Pending JP2025014032A (ja) | 2020-04-14 | 2024-10-30 | ニューラルネットワークパラメーターの表現の改良された概念 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20230075514A1 (ja) |

| EP (1) | EP4136582A1 (ja) |

| JP (2) | JP7581370B2 (ja) |

| KR (1) | KR20230010854A (ja) |

| CN (1) | CN115917556A (ja) |

| WO (1) | WO2021209469A1 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11842484B2 (en) | 2021-01-04 | 2023-12-12 | James R. Glidewell Dental Ceramics, Inc. | Teeth segmentation using neural networks |

| US12136208B2 (en) | 2021-03-31 | 2024-11-05 | James R. Glidewell Dental Ceramics, Inc. | Automatic clean up of jaw scans |

| US12210802B2 (en) | 2021-04-30 | 2025-01-28 | James R. Glidewell Dental Ceramics, Inc. | Neural network margin proposal |

| US12295806B2 (en) | 2022-01-10 | 2025-05-13 | James R. Glidewell Dental Ceramics, Inc. | Automatic determination of trim-line for aligners |

| KR102809046B1 (ko) * | 2022-11-11 | 2025-05-19 | 삼성전자주식회사 | 양자화 스케일링 장치 및 양자화를 위한 스케일링 파라미터의 계산 방법 |

| CN116312534B (zh) * | 2022-12-15 | 2025-12-19 | 科大讯飞股份有限公司 | 语音识别方法、硬件调用方法及相关装置、处理器和介质 |

| KR20240120352A (ko) * | 2023-01-31 | 2024-08-07 | 삼성전자주식회사 | 곱셈기와 누적기를 이용한 양자화를 수행하는 전자 장치 및 그 제어 방법 |

| KR102822740B1 (ko) * | 2023-02-08 | 2025-06-19 | 리벨리온 주식회사 | 클러스터를 이용한 딥러닝 뉴럴 네트워크 모델 가속화 방법 및 장치 |

| KR20240160765A (ko) * | 2023-05-03 | 2024-11-12 | 한화비전 주식회사 | 객체 재인식을 위한 신경망 모델의 적응적 업데이트 |

| CN116432715B (zh) * | 2023-06-14 | 2023-11-10 | 深圳比特微电子科技有限公司 | 一种模型压缩方法、装置和可读存储介质 |

| WO2024261091A1 (en) | 2023-06-19 | 2024-12-26 | Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V. | Client device and method for participating in federated learning of a neural network |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019008752A1 (ja) | 2017-07-07 | 2019-01-10 | 三菱電機株式会社 | データ処理装置、データ処理方法および圧縮データ |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6183980B1 (ja) * | 2016-12-02 | 2017-08-23 | 国立大学法人東京工業大学 | ニューラルネットワーク回路装置、ニューラルネットワーク、ニューラルネットワーク処理方法およびニューラルネットワークの実行プログラム |

| JP6933367B2 (ja) * | 2017-09-20 | 2021-09-08 | Tokyo Artisan Intelligence株式会社 | ニューラルネットワーク回路装置、システム、処理方法および実行プログラム |

-

2021

- 2021-04-13 WO PCT/EP2021/059592 patent/WO2021209469A1/en not_active Ceased

- 2021-04-13 KR KR1020227039626A patent/KR20230010854A/ko active Pending

- 2021-04-13 JP JP2022562943A patent/JP7581370B2/ja active Active

- 2021-04-13 CN CN202180042521.1A patent/CN115917556A/zh active Pending

- 2021-04-13 EP EP21717115.6A patent/EP4136582A1/en active Pending

-

2022

- 2022-10-13 US US18/046,406 patent/US20230075514A1/en active Pending

-

2024

- 2024-10-30 JP JP2024190377A patent/JP2025014032A/ja active Pending

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019008752A1 (ja) | 2017-07-07 | 2019-01-10 | 三菱電機株式会社 | データ処理装置、データ処理方法および圧縮データ |

Non-Patent Citations (3)

| Title |

|---|

| CAI, Yaohui et al.,"ZeroQ: A Novel Zero Shot Quantization Framework",arXiv [online],2020年01月,[2023年10月11日検索],インターネット<URL:https://arxiv.org/abs/2001.00281v1>,2001.00281v1 |

| FLYNN, David et al.,"G-PCC: Integer step sizes for in-tree geometry quantisation",MPEG Point Cloud Compression [online],2020年01月,[2023年10月11日検索],インターネット<URL:https://mpeg-pcc.org/index.php/public-contributions/m52522-g-pcc-integer-step-sizes-for-in-tree-geometry-quantisation/>,m52522 |

| JACOB, Benoit et al.,"Quantization and Training of Neural Networks for Efficient Integer-Arithmetic-Only Inference",arXiv [online],2017年12月,[2023年10月11日検索],インターネット<URL:https://arxiv.org/abs/1712.05877v1>,1712.05877v1 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2021209469A1 (en) | 2021-10-21 |

| JP2023522886A (ja) | 2023-06-01 |

| JP2025014032A (ja) | 2025-01-28 |

| US20230075514A1 (en) | 2023-03-09 |

| EP4136582A1 (en) | 2023-02-22 |

| KR20230010854A (ko) | 2023-01-19 |

| CN115917556A (zh) | 2023-04-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7581370B2 (ja) | ニューラルネットワークパラメーターの表現の改良された概念 | |

| CN101399989B (zh) | 减少位深的量子化方法 | |

| CN102007489B (zh) | 逆向离散余弦变换的计算期间的误差减少 | |

| WO2020190772A1 (en) | Neural network model compression and optimization | |

| US7912318B2 (en) | Data transform apparatus and control method thereof | |

| JP5086274B2 (ja) | 共通因数を用いる変換 | |

| KR20220058628A (ko) | 신경망 모델 압축 | |

| CN114450692B (zh) | 神经网络解码的方法、装置、计算机设备及计算机可读介质 | |

| Zhang et al. | Lossless image compression using a multi-scale progressive statistical model | |

| Kuroki et al. | Lossless image compression by two-dimensional linear prediction with variable coefficients | |

| JPH0715346A (ja) | 2ベクトルのスカラ積を決定するためのデジタル信号の符号化方法および回路 | |

| TWI869668B (zh) | 用以解碼類神經網路參數之設備、方法及電腦程式與使用更新模型用以編碼類神經網路參數之設備、方法及電腦程式 | |

| US5625713A (en) | Apparatus and method for increasing the throughput of an acoustic or image compression system | |

| Sitaram et al. | Efficient codebooks for vector quantization image compression with an adaptive tree search algorithm | |

| Khataei et al. | Optimizing hybrid binary-unary hardware accelerators using self-similarity measures | |

| EP4690000A1 (en) | Coding video data on a gpu | |

| JP2024097030A (ja) | モード-グローバル設定によるマトリックスベースのイントラ予測 | |

| CN117767959A (zh) | 通过乘加阵列对特征数据进行处理的方法和装置 | |

| JP4933405B2 (ja) | データ変換装置及びその制御方法 | |

| JP6102707B2 (ja) | デジタル符号化装置 | |

| Sano et al. | Segment-parallel predictor for FPGA-based hardware compressor and decompressor of floating-point data streams to enhance memory I/O bandwidth | |

| Mohsen et al. | L1-based prediction for lossless image compression | |

| US20230289588A1 (en) | Deep Neural Network Processing Device with Decompressing Module, Decompressing Method and Compressing Method | |

| Shyam et al. | Image quality compression based on non-zeroing bit truncation using discrete cosine transform | |

| He et al. | Post-training quantization is all you need to perform cross-platform learned image compression |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20221213 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230516 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230517 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20221214 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20231017 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20240116 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240318 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240625 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240912 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20241001 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20241030 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7581370 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |