JP7577643B2 - 撮像素子および撮像装置 - Google Patents

撮像素子および撮像装置 Download PDFInfo

- Publication number

- JP7577643B2 JP7577643B2 JP2021504891A JP2021504891A JP7577643B2 JP 7577643 B2 JP7577643 B2 JP 7577643B2 JP 2021504891 A JP2021504891 A JP 2021504891A JP 2021504891 A JP2021504891 A JP 2021504891A JP 7577643 B2 JP7577643 B2 JP 7577643B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- pixel signal

- unit

- control unit

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000006243 chemical reaction Methods 0.000 claims description 102

- 238000012546 transfer Methods 0.000 claims description 28

- 238000003908 quality control method Methods 0.000 claims description 10

- 230000007423 decrease Effects 0.000 claims description 3

- 238000003384 imaging method Methods 0.000 description 160

- 239000012528 membrane Substances 0.000 description 100

- 239000000758 substrate Substances 0.000 description 76

- 239000004065 semiconductor Substances 0.000 description 71

- 239000010410 layer Substances 0.000 description 65

- 238000010586 diagram Methods 0.000 description 38

- 239000011229 interlayer Substances 0.000 description 35

- 230000004048 modification Effects 0.000 description 26

- 238000012986 modification Methods 0.000 description 26

- 238000001514 detection method Methods 0.000 description 23

- 238000000034 method Methods 0.000 description 20

- 238000004891 communication Methods 0.000 description 19

- 238000009792 diffusion process Methods 0.000 description 19

- 238000007667 floating Methods 0.000 description 19

- 238000012545 processing Methods 0.000 description 18

- 230000000694 effects Effects 0.000 description 17

- 230000002093 peripheral effect Effects 0.000 description 17

- 230000006870 function Effects 0.000 description 13

- 230000003287 optical effect Effects 0.000 description 13

- 230000003321 amplification Effects 0.000 description 12

- 238000005516 engineering process Methods 0.000 description 12

- 238000003199 nucleic acid amplification method Methods 0.000 description 12

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 12

- 229910052581 Si3N4 Inorganic materials 0.000 description 10

- 230000015556 catabolic process Effects 0.000 description 10

- 238000006731 degradation reaction Methods 0.000 description 10

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 10

- 238000002674 endoscopic surgery Methods 0.000 description 8

- 239000011810 insulating material Substances 0.000 description 7

- 229910000530 Gallium indium arsenide Inorganic materials 0.000 description 6

- 230000005540 biological transmission Effects 0.000 description 6

- 229910052814 silicon oxide Inorganic materials 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- 239000010949 copper Substances 0.000 description 5

- 230000006866 deterioration Effects 0.000 description 5

- 239000000463 material Substances 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- 238000001356 surgical procedure Methods 0.000 description 5

- 239000010936 titanium Substances 0.000 description 5

- 230000008859 change Effects 0.000 description 4

- 229910052681 coesite Inorganic materials 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 229910052906 cristobalite Inorganic materials 0.000 description 4

- 230000005284 excitation Effects 0.000 description 4

- 230000007246 mechanism Effects 0.000 description 4

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 4

- 238000002161 passivation Methods 0.000 description 4

- 229910052682 stishovite Inorganic materials 0.000 description 4

- 229910052905 tridymite Inorganic materials 0.000 description 4

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 3

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 3

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- 238000010336 energy treatment Methods 0.000 description 3

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(iv) oxide Chemical compound O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 229920006395 saturated elastomer Polymers 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 2

- 210000004204 blood vessel Anatomy 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- DVRDHUBQLOKMHZ-UHFFFAOYSA-N chalcopyrite Chemical group [S-2].[S-2].[Fe+2].[Cu+2] DVRDHUBQLOKMHZ-UHFFFAOYSA-N 0.000 description 2

- 239000003153 chemical reaction reagent Substances 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 229910052593 corundum Inorganic materials 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 238000005401 electroluminescence Methods 0.000 description 2

- 239000000284 extract Substances 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- MOFVSTNWEDAEEK-UHFFFAOYSA-M indocyanine green Chemical compound [Na+].[O-]S(=O)(=O)CCCCN1C2=CC=C3C=CC=CC3=C2C(C)(C)C1=CC=CC=CC=CC1=[N+](CCCCS([O-])(=O)=O)C2=CC=C(C=CC=C3)C3=C2C1(C)C MOFVSTNWEDAEEK-UHFFFAOYSA-M 0.000 description 2

- 229960004657 indocyanine green Drugs 0.000 description 2

- 238000009434 installation Methods 0.000 description 2

- 230000001678 irradiating effect Effects 0.000 description 2

- 230000031700 light absorption Effects 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 2

- 229910001845 yogo sapphire Inorganic materials 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- KXNLCSXBJCPWGL-UHFFFAOYSA-N [Ga].[As].[In] Chemical compound [Ga].[As].[In] KXNLCSXBJCPWGL-UHFFFAOYSA-N 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000000740 bleeding effect Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 238000002485 combustion reaction Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- -1 for example Substances 0.000 description 1

- 230000004313 glare Effects 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 239000003595 mist Substances 0.000 description 1

- 230000000116 mitigating effect Effects 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 239000013307 optical fiber Substances 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 239000002096 quantum dot Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 229910001928 zirconium oxide Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

- H04N25/778—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components comprising amplifiers shared between a plurality of pixels, i.e. at least one part of the amplifier must be on the sensor array itself

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/78—Readout circuits for addressed sensors, e.g. output amplifiers or A/D converters

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

1.第1の実施の形態(撮像素子)…図1~図7

2.第1の実施の形態の変形例(撮像素子)…図8~図26

3.第2の実施の形態(撮像装置)…図27、図28

4.第2の実施の形態の変形例(撮像装置)…図29

5.応用例

応用例1(移動体)…図30、図31

応用例2(手術システム)…図32、図33

[構成]

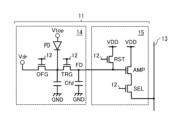

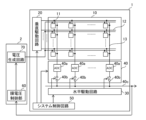

本開示の第1の実施形態に係る撮像素子1について説明する。図1は、撮像素子1の概略構成例を表したものである。撮像素子1は、例えば赤外線イメージセンサであり、例えば波長800nm以上の光に対しても感度を有している。撮像素子1は、光電変換素子を含む複数のセンサ画素11が行列状(マトリックス状)に2次元配置されてなる画素アレイ部10を備えている。センサ画素11は、例えば、図2に示したように、光電変換を行う画素回路14と、画素回路14から出力された電荷に基づく画素信号を出力する読み出し回路15とによって構成されている。

[画質調整]

次に、図7を参照して、撮像素子1の画質調整手順について説明する。図7は、撮像素子1の画質調整手順の一例を表したものである。システム制御回路50は、撮像指令を受けると、膜電圧設定指令を膜電圧制御部60に出力する。膜電圧制御部60は、膜電圧設定指令を受けると、まず、膜電圧VfをVfaに設定する(ステップS101)。具体的には、膜電圧制御部60は、Vtop(第1電圧)とVdr(第2電圧)との電位差(Vtop-Vdr)がVfaとなるように、VtopおよびVdrを設定する。例えば、膜電圧制御部60は、Vtopを+2Vに設定し、Vdrを+1Vに設定する。膜電圧制御部60は、VtopおよびVdrの設定値を電圧生成回路70に出力する。電圧生成回路70は、膜電圧制御部60から入力された設定値に基づいて、フォトダイオードPDのアノードに接続された電源線に対して、Vtop=+2Vの電圧を印加し、排出トランジスタOFGのドレインに接続された電源線に対して、Vdr=+1Vの電圧を印加する。

本実施形態では、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg)に基づく膜電圧Vfを各フォトダイオードPD(n型半導体膜21)に印加することにより、画素信号から得られる画像データの画質が制御される。具体的には、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg)が閾値Vth1を超えたときに膜電圧Vfを相対的に大きくし、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg)が閾値Vth2を下回ったときに膜電圧Vfを相対的に小さくする。このように、本実施形態では、高輝度のときは、膜電圧Vfを相対的に大きくして、光ショットノイズの影響を低減し、低輝度のときは、膜電圧Vfを相対的に小さくして、S/N比を高くしている。これにより、画質劣化を抑制することができる。

[[変形例A]]

上記実施の形態では、膜電圧制御部60および電圧生成回路70は、撮像素子1内に設けられていたが、例えば、図8に示したように、撮像素子1とは別体の画質制御回路2内に設けられていてもよい。この場合、膜電圧制御部60は、例えば、図8に示したように、撮像素子1の出力に基づいて、膜電圧Vfを設定してもよい。このようにした場合であっても、上記実施の形態と同様の効果を奏する。

上記実施の形態において、撮像素子1は、例えば、図9に示したように、アナログレンジ制御部80を更に備えていてもよい。アナログレンジ制御部80は、膜電圧制御部60から入力される判定結果(つまり、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg))に基づいて、ADC40aのアナログレンジRを制御する。具体的には、アナログレンジ制御部80は、膜電圧制御部60から入力される判定結果(つまり、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg))に基づくレンジ設定値をADC40aに出力することにより、画素信号から得られる画像データの画質を制御する。

次に、図11を参照して、本変形例に係る撮像素子1の画質調整手順について説明する。図11は、本変形例に係る撮像素子1の画質調整手順の一例を表したものである。なお、本変形例では、撮像素子1は、図7に記載の画質調整手順を実行するとともに、図11に記載の画質調整手順を実行する。

本変形例では、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg)に基づく膜電圧Vfを各フォトダイオードPD(n型半導体膜21)に印加することにより、画素信号から得られる画像データの画質が制御される。具体的には、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg)が閾値Vth1を超えたときに膜電圧Vfを相対的に大きくし、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg)が閾値Vth2を下回ったときに膜電圧Vfを相対的に小さくする。このように、本変形例では、高輝度のときは、膜電圧Vfを相対的に大きくして、光ショットノイズの影響を低減し、低輝度のときは、膜電圧Vfを相対的に小さくして、S/N比を高くしている。これにより、画質劣化を抑制することができる。

上記変形例Bでは、膜電圧制御部60、電圧生成回路70およびアナログレンジ制御部80は、撮像素子1内に設けられていたが、例えば、図12に示したように、撮像素子1とは別体の画質制御回路2内に設けられていてもよい。この場合、膜電圧制御部60は、例えば、図12に示したように、撮像素子1の出力に基づいて、膜電圧Vfを設定してもよい。このようにした場合であっても、上記実施の形態と同様の効果を奏する。

上記変形例Bでは、膜電圧制御部60、電圧生成回路70およびアナログレンジ制御部80は、撮像素子1内に設けられていた。しかし、例えば、図13に示したように、膜電圧制御部60および電圧生成回路70が、撮像素子1とは別体の画質制御回路2内に設けられ、アナログレンジ制御部80が撮像素子1内に設けられていてもよい。

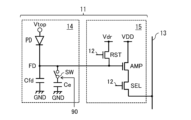

上記実施の形態において、撮像素子1は、例えば、図14に示したように、効率変換制御部90を更に備えていてもよい。効率変換制御部90は、膜電圧制御部60から入力される判定結果(つまり、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg))に基づいて、画素回路14の変換効率ηを制御する。具体的には、効率変換制御部90は、膜電圧制御部60から入力される判定結果(つまり、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg))に基づく制御信号を後述のスイッチ素子SWに出力することにより、画素信号から得られる画像データの画質を制御する。

次に、図17を参照して、撮像素子1の画質調整手順について説明する。図17は、撮像素子1の画質調整手順の一例を表したものである。なお、本変形例では、撮像素子1は、図7に記載の画質調整手順を実行するとともに、図17に記載の画質調整手順を実行する。

本変形例では、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg)に基づく膜電圧Vfを各フォトダイオードPD(n型半導体膜21)に印加することにより、画素信号から得られる画像データの画質が制御される。具体的には、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg)が閾値Vth1を超えたときに膜電圧Vfを相対的に大きくし、撮像素子1の出力(画素信号の振幅Vdの平均値Vdavg)が閾値Vth2を下回ったときに膜電圧Vfを相対的に小さくする。このように、本変形例では、高輝度のときは、膜電圧Vfを相対的に大きくして、光ショットノイズの影響を低減し、低輝度のときは、膜電圧Vfを相対的に小さくして、S/N比を高くしている。これにより、画質劣化を抑制することができる。

上記変形例Eでは、膜電圧制御部60、電圧生成回路70および効率変換制御部90は、撮像素子1内に設けられていた。しかし、例えば、図18に示したように、膜電圧制御部60、電圧生成回路70および効率変換制御部90が、撮像素子1とは別体の画質制御回路2内に設けられていてもよい。この場合、膜電圧制御部60は、例えば、図18に示したように、撮像素子1の出力に基づいて、膜電圧Vfを設定してもよい。このようにした場合であっても、上記実施の形態と同様の効果を奏する。

上記変形例Eでは、膜電圧制御部60、電圧生成回路70および効率変換制御部90は、撮像素子1内に設けられていた。しかし、例えば、図19に示したように、膜電圧制御部60および電圧生成回路70が、撮像素子1とは別体の画質制御回路2内に設けられ、効率変換制御部90が撮像素子1内に設けられていてもよい。

上記実施の形態およびその変形例において、画素回路14は、例えば、図20、図21に示したように、排出トランジスタOFGが省略されてもよい。このとき、膜電圧制御部60は、n型半導体層24に印加する電圧Vtopと、転送トランジスタTRGがオンしているときにリセットトランジスタRSTによって印加されたp型半導体層22の電極Vdrとの電位差(Vtop-Vdr)が膜電圧Vfとなるように、画素信号に基づいて電圧Vtopを生成してもよい。

上記実施の形態およびその変形例A~Hでは、受光基板100と駆動基板200とが、バンプ接合されていた。しかし、上記実施の形態およびその変形例A~Hにおいて、受光基板100と駆動基板200とが、Cu-Cu接合されていてもよい。図24は、本変形例に係る撮像素子1の断面構成の一変形例を表したものである。

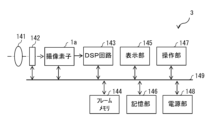

図27は、上記実施の形態、上記変形例B、上記変形例Eおよび上記変形例Hに係る撮像素子1(以下、「撮像素子1a」と称する。)を備えた撮像装置3の概略構成の一例を表したものである。

上記第2の実施の形態において、撮像装置3は、撮像素子1aの代わりに、上記変形例A、上記変形例C、上記変形例D、上記変形例F、上記変形例Gおよび上記変形例Hに係る撮像素子1(以下、「撮像素子1b」と称する。)を備えていてもよい。この場合、撮像装置3は、例えば、図29に示したように、画質制御回路2を備えていてもよい。このようにした場合であっても、上記適用例と同様、撮像素子1bの画質調整を自動的に行うことができる。

[応用例1]

本開示に係る技術(本技術)は、様々な製品へ応用することができる。例えば、本開示に係る技術は、自動車、電気自動車、ハイブリッド電気自動車、自動二輪車、自転車、パーソナルモビリティ、飛行機、ドローン、船舶、ロボット等のいずれかの種類の移動体に搭載される装置として実現されてもよい。

図32は、本開示に係る技術(本技術)が適用され得る内視鏡手術システムの概略的な構成の一例を示す図である。

(1)

各々が光電変換部と、前記光電変換部から出力された電荷に基づく画素信号を出力する読み出し回路とを含む複数のセンサ画素と、

前記画素信号に基づく制御電圧を各前記光電変換部に印加する電圧制御部と

を備えた撮像素子。

(2)

前記電圧制御部は、前記画素信号が第1閾値を超えたときに前記制御電圧を相対的に大きくし、前記画素信号が前記第1閾値よりも小さな第2閾値を下回ったときに前記制御電圧を相対的に小さくする

(1)に記載の撮像素子。

(3)

各前記センサ画素は、前記光電変換部を挟み込む第1電極および第2電極を更に有し、

前記電圧制御部は、前記第1電極に印加する第1電圧と、前記第2電極に印加する第2電圧との電位差が前記制御電圧となるように、前記画素信号に基づいて前記第1電圧および前記第2電圧を生成する

(1)または(2)に記載の撮像素子。

(4)

各前記センサ画素は、

前記光電変換部から転送された電荷を保持する電荷保持部と

前記第2電極に電気的に接続され、前記光電変換部から前記電荷保持部に電荷を転送する転送トランジスタと

前記第2電極に電気的に接続され、前記光電変換部の電荷を初期化する排出トランジスタと

を更に含み、

前記電圧制御部は、前記排出トランジスタがオンしているときに、前記第2電極に前記第2電圧を印加する

(3)に記載の撮像素子。

(5)

各前記画素は、

前記光電変換部を挟み込む第1電極および第2電極と、

前記光電変換部から転送された電荷を保持する電荷保持部と

前記第2電極に電気的に接続され、前記光電変換部から前記電荷保持部に電荷を転送する転送トランジスタと

を更に含み、

前記読み出し回路は、前記電荷保持部の電位を初期化するリセットトランジスタを有し、

前記電圧制御部は、前記第1電極に印加する第1電圧と、前記転送トランジスタがオンしているときに前記リセットトランジスタによって印加された前記第2電極の第2電圧との電位差が前記制御電圧となるように、前記画素信号に基づいて前記第1電圧を生成する

(1)または(2)に記載の撮像素子。

(6)

各前記画素は、前記光電変換部から転送された電荷を保持する電荷保持部を更に含み、

前記読み出し回路は、前記電荷保持部の電位を初期化するリセットトランジスタを有し、

前記電圧制御部は、前記第1電極に印加する第1電圧と、前記リセットトランジスタによって印加された前記第2電極の第2電圧との電位差が前記制御電圧となるように、前記画素信号に基づいて前記第1電圧を生成する

(1)または(2)に記載の撮像素子。

(7)

前記画素信号をAD(Analog-to-Digital)変換するAD変換回路と、

前記画素信号に基づくレンジ設定値を前記AD変換回路に出力するレンジ制御部と

を更に備えた

(1)ないし(6)のいずれか1つに記載の撮像素子。

(8)

前記レンジ制御部は、前記画素信号が第1閾値を超えたときに前記レンジ設定値を相対的に大きくし、前記画素信号が前記第1閾値よりも小さな第2閾値を下回ったときに前記レンジ設定値を相対的に小さくする

(7)に記載の撮像素子。

(9)

各前記センサ画素は、

前記光電変換部から転送された電荷を保持する電荷保持部と

前記光電変換部から前記電荷保持部に電荷を転送する転送トランジスタと

前記電荷保持部に接続されたスイッチ素子と、

前記スイッチ素子を介して前記電荷保持部の容量と並列に接続された補助容量と、

前記画素信号に基づいて前記スイッチ素子のオンオフを制御する変換効率制御部と

を更に備えた

(1)ないし(6)のいずれか1つに記載の撮像素子。

(10)

前記変換効率制御部は、前記画素信号が第1閾値を超えたときに前記スイッチ素子をオフし、前記画素信号が前記第1閾値よりも小さな第2閾値を下回ったときに前記前記スイッチ素子をオンする

(9)に記載の撮像素子。

(11)

各々が光電変換部と、前記光電変換部から出力された電荷に基づく画素信号を出力する読み出し回路とを含む複数のセンサ画素を有する撮像素子と、

前記画素信号に基づく制御電圧を各前記光電変換部に印加する画質制御回路と

を備えた

撮像装置。

Claims (7)

- 各々が光電変換部と、前記光電変換部から出力された電荷に基づく画素信号を出力する読み出し回路とを含む複数のセンサ画素と、

前記画素信号に基づく制御電圧を各前記光電変換部に印加する電圧制御部と、

変換効率制御部と

を備え、

各前記センサ画素は、

前記光電変換部から転送された電荷を保持する電荷保持部と、

前記光電変換部から前記電荷保持部に電荷を転送する転送トランジスタと、

前記電荷保持部に接続されたスイッチ素子と、

前記スイッチ素子を介して前記電荷保持部の容量と並列に接続された補助容量と

を更に有し、

前記変換効率制御部は、前記画素信号に基づいて前記スイッチ素子のオンオフを制御し、

前記変換効率制御部は、前記画素信号が第1閾値を超えたときに前記スイッチ素子をオフし、前記画素信号が前記第1閾値よりも小さな第2閾値を下回ったときに前記スイッチ素子をオンする

撮像素子。 - 前記電圧制御部は、前記画素信号が前記第1閾値を超えたときに前記制御電圧を、前記第2閾値を下回ったときの前記制御電圧と比べて相対的に大きくし、前記画素信号が前記第2閾値を下回ったときに前記制御電圧を、前記画素信号が前記第1閾値を超えたときの前記制御電圧と比べて相対的に小さくする

請求項1に記載の撮像素子。 - 各前記センサ画素は、前記光電変換部を挟み込む第1電極および第2電極を更に有し、

前記電圧制御部は、前記第1電極に印加する第1電圧と、前記第2電極に印加する第2電圧との電位差が前記制御電圧となるように、前記画素信号に基づいて前記第1電圧および前記第2電圧を生成する

請求項1に記載の撮像素子。 - 各前記センサ画素は、前記光電変換部の電荷を初期化する排出トランジスタを更に含み、

前記転送トランジスタは、前記第2電極に電気的に接続され、

前記排出トランジスタは、前記第2電極に電気的に接続され、

前記電圧制御部は、前記排出トランジスタがオンしているときに、前記第2電極に前記第2電圧を印加する

請求項3に記載の撮像素子。 - 各前記センサ画素は、前記光電変換部を挟み込む第1電極および第2電極を更に含み、

前記転送トランジスタは、前記第2電極に電気的に接続され、

前記読み出し回路は、前記電荷保持部の電位を初期化するリセットトランジスタを有し、

前記電圧制御部は、前記第1電極に印加する第1電圧と、前記転送トランジスタがオンしているときに前記リセットトランジスタによって印加された前記第2電極の第2電圧との電位差が前記制御電圧となるように、前記画素信号に基づいて前記第1電圧を生成する

請求項1に記載の撮像素子。 - 各前記センサ画素は、前記光電変換部を挟み込む第1電極および第2電極を更に含み、

前記読み出し回路は、前記電荷保持部の電位を初期化するリセットトランジスタを有し、

前記電圧制御部は、前記第1電極に印加する第1電圧と、前記リセットトランジスタによって印加された前記第2電極の第2電圧との電位差が前記制御電圧となるように、前記画素信号に基づいて前記第1電圧を生成する

請求項1に記載の撮像素子。 - 各々が光電変換部と、前記光電変換部から出力された電荷に基づく画素信号を出力する読み出し回路とを含む複数のセンサ画素を有する撮像素子と、

前記画素信号に基づく制御電圧を各前記光電変換部に印加する画質制御回路と

を備え、

各前記センサ画素は、

前記光電変換部から転送された電荷を保持する電荷保持部と

前記光電変換部から前記電荷保持部に電荷を転送する転送トランジスタと

前記電荷保持部に接続されたスイッチ素子と、

前記スイッチ素子を介して前記電荷保持部の容量と並列に接続された補助容量と、

前記画素信号に基づいて前記スイッチ素子のオンオフを制御する変換効率制御部と

を更に有し、

前記変換効率制御部は、前記画素信号が第1閾値を超えたときに前記スイッチ素子をオフし、前記画素信号が前記第1閾値よりも小さな第2閾値を下回ったときに前記スイッチ素子をオンする

撮像装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019043786 | 2019-03-11 | ||

| JP2019043786 | 2019-03-11 | ||

| PCT/JP2020/007045 WO2020184149A1 (ja) | 2019-03-11 | 2020-02-21 | 撮像素子および撮像装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JPWO2020184149A1 JPWO2020184149A1 (ja) | 2020-09-17 |

| JPWO2020184149A5 JPWO2020184149A5 (ja) | 2023-02-22 |

| JP7577643B2 true JP7577643B2 (ja) | 2024-11-05 |

Family

ID=72427897

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021504891A Active JP7577643B2 (ja) | 2019-03-11 | 2020-02-21 | 撮像素子および撮像装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US11838670B2 (ja) |

| JP (1) | JP7577643B2 (ja) |

| CN (1) | CN113330541B (ja) |

| DE (1) | DE112020001187T5 (ja) |

| TW (1) | TWI846824B (ja) |

| WO (1) | WO2020184149A1 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2022118538A1 (ja) * | 2020-12-01 | 2022-06-09 | ソニーセミコンダクタソリューションズ株式会社 | 受光素子及び電子機器 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016134909A (ja) | 2015-01-22 | 2016-07-25 | キヤノン株式会社 | 撮像装置及びその制御方法 |

| WO2017150167A1 (ja) | 2016-02-29 | 2017-09-08 | ソニー株式会社 | 固体撮像素子 |

| JP2018098690A (ja) | 2016-12-15 | 2018-06-21 | キヤノン株式会社 | 撮像装置、撮像装置の駆動方法及び撮像システム |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1956490B (zh) * | 2005-10-28 | 2012-06-20 | 索尼株式会社 | 固态成像器件、驱动固态成像器件的方法和成像设备 |

| JP4375364B2 (ja) * | 2006-07-14 | 2009-12-02 | ソニー株式会社 | 固体撮像装置の駆動方法 |

| JP5167677B2 (ja) | 2007-04-12 | 2013-03-21 | ソニー株式会社 | 固体撮像装置、固体撮像装置の駆動方法、固体撮像装置の信号処理方法および撮像装置 |

| JP2012204938A (ja) * | 2011-03-24 | 2012-10-22 | Nikon Corp | 撮像装置 |

| US9137432B2 (en) * | 2011-09-16 | 2015-09-15 | Samsung Electronics Co., Ltd. | Backside illumination image sensor, operating method thereof, image processing system and method of processing image using the same |

| JP6171997B2 (ja) * | 2014-03-14 | 2017-08-02 | ソニー株式会社 | 固体撮像素子およびその駆動方法、並びに電子機器 |

| JP6541347B2 (ja) | 2014-03-27 | 2019-07-10 | キヤノン株式会社 | 固体撮像装置および撮像システム |

| CN104124256B (zh) * | 2014-07-01 | 2017-06-20 | 上海奕瑞光电子科技有限公司 | 一种像素aec平板探测器 |

| US9736406B2 (en) | 2015-01-22 | 2017-08-15 | Canon Kabushiki Kaisha | Image capturing apparatus and control method thereof |

| WO2017057397A1 (ja) * | 2015-09-30 | 2017-04-06 | 株式会社ニコン | 撮像素子および電子カメラ |

| US10063797B2 (en) * | 2016-12-22 | 2018-08-28 | Raytheon Company | Extended high dynamic range direct injection circuit for imaging applications |

| JP7053191B2 (ja) | 2017-08-30 | 2022-04-12 | 株式会社オーク製作所 | オゾン生成装置および紫外線照射装置 |

-

2020

- 2020-02-21 CN CN202080010370.7A patent/CN113330541B/zh active Active

- 2020-02-21 WO PCT/JP2020/007045 patent/WO2020184149A1/ja not_active Ceased

- 2020-02-21 DE DE112020001187.9T patent/DE112020001187T5/de active Pending

- 2020-02-21 JP JP2021504891A patent/JP7577643B2/ja active Active

- 2020-02-21 US US17/310,797 patent/US11838670B2/en active Active

- 2020-02-24 TW TW109105793A patent/TWI846824B/zh active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016134909A (ja) | 2015-01-22 | 2016-07-25 | キヤノン株式会社 | 撮像装置及びその制御方法 |

| WO2017150167A1 (ja) | 2016-02-29 | 2017-09-08 | ソニー株式会社 | 固体撮像素子 |

| JP2018098690A (ja) | 2016-12-15 | 2018-06-21 | キヤノン株式会社 | 撮像装置、撮像装置の駆動方法及び撮像システム |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2020184149A1 (ja) | 2020-09-17 |

| CN113330541A (zh) | 2021-08-31 |

| TW202044571A (zh) | 2020-12-01 |

| DE112020001187T5 (de) | 2022-03-17 |

| US20220124277A1 (en) | 2022-04-21 |

| JPWO2020184149A1 (ja) | 2020-09-17 |

| TWI846824B (zh) | 2024-07-01 |

| US11838670B2 (en) | 2023-12-05 |

| CN113330541B (zh) | 2025-03-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7631384B2 (ja) | 半導体素子および電子機器 | |

| JP7642528B2 (ja) | 撮像素子および半導体素子 | |

| KR102653046B1 (ko) | 수광 소자 및 전자 기기 | |

| JP7676319B2 (ja) | 撮像装置および電子機器 | |

| KR102761019B1 (ko) | 고체 촬상 장치 및 전자 기기 | |

| JP7634991B2 (ja) | 半導体素子 | |

| JP7660642B2 (ja) | 半導体素子 | |

| KR20230012667A (ko) | 수광 소자, 수광 소자의 제조 방법, 촬상 소자 및 전자 기기 | |

| CN108475688A (zh) | 受光元件、受光元件的制造方法、成像元件以及电子设备 | |

| JP7631226B2 (ja) | 固体撮像装置および電子機器 | |

| CN114586338A (zh) | 半导体装置、摄像元件和电子设备 | |

| JP7520499B2 (ja) | 半導体素子および電子機器 | |

| JP7524160B2 (ja) | 受光素子の製造方法 | |

| JP7577643B2 (ja) | 撮像素子および撮像装置 | |

| US12335642B2 (en) | Solid-state imaging device and electronic device | |

| WO2021085290A1 (ja) | 過光量検知回路、受光素子、および電子機器 | |

| JP7653788B2 (ja) | 撮像素子および電子機器 | |

| WO2024253074A1 (ja) | 光検出装置および電子機器 | |

| WO2024202672A1 (ja) | 光検出装置および電子機器 | |

| WO2024181273A1 (ja) | 光検出装置及び電子機器 | |

| WO2024154646A1 (ja) | 光検出装置および光検出装置の製造方法 | |

| KR20240116912A (ko) | 수광 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230214 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230214 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240319 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240507 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240813 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240903 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20240924 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20241023 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7577643 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |