JP7520064B2 - 遊技機 - Google Patents

遊技機 Download PDFInfo

- Publication number

- JP7520064B2 JP7520064B2 JP2022032873A JP2022032873A JP7520064B2 JP 7520064 B2 JP7520064 B2 JP 7520064B2 JP 2022032873 A JP2022032873 A JP 2022032873A JP 2022032873 A JP2022032873 A JP 2022032873A JP 7520064 B2 JP7520064 B2 JP 7520064B2

- Authority

- JP

- Japan

- Prior art keywords

- control board

- main control

- register

- command

- value

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 claims description 653

- 230000008569 process Effects 0.000 claims description 612

- 238000003860 storage Methods 0.000 claims description 19

- 238000012545 processing Methods 0.000 description 190

- 238000004364 calculation method Methods 0.000 description 179

- 239000000872 buffer Substances 0.000 description 77

- 230000000052 comparative effect Effects 0.000 description 70

- 238000001514 detection method Methods 0.000 description 70

- 238000010586 diagram Methods 0.000 description 59

- 230000015654 memory Effects 0.000 description 44

- 238000012544 monitoring process Methods 0.000 description 36

- 238000012790 confirmation Methods 0.000 description 30

- 230000005856 abnormality Effects 0.000 description 24

- 238000012795 verification Methods 0.000 description 19

- 230000008859 change Effects 0.000 description 17

- 238000007792 addition Methods 0.000 description 15

- FFBHFFJDDLITSX-UHFFFAOYSA-N benzyl N-[2-hydroxy-4-(3-oxomorpholin-4-yl)phenyl]carbamate Chemical compound OC1=C(NC(=O)OCC2=CC=CC=C2)C=CC(=C1)N1CCOCC1=O FFBHFFJDDLITSX-UHFFFAOYSA-N 0.000 description 12

- 230000004913 activation Effects 0.000 description 11

- 230000005540 biological transmission Effects 0.000 description 10

- 230000001276 controlling effect Effects 0.000 description 8

- 239000013256 coordination polymer Substances 0.000 description 7

- 239000011521 glass Substances 0.000 description 7

- 238000012360 testing method Methods 0.000 description 6

- 230000002159 abnormal effect Effects 0.000 description 5

- 230000009467 reduction Effects 0.000 description 5

- 230000007704 transition Effects 0.000 description 5

- 238000004458 analytical method Methods 0.000 description 4

- 230000000295 complement effect Effects 0.000 description 4

- 238000005034 decoration Methods 0.000 description 4

- 239000002131 composite material Substances 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- QMBJSIBWORFWQT-DFXBJWIESA-N Chlormadinone acetate Chemical compound C1=C(Cl)C2=CC(=O)CC[C@]2(C)[C@@H]2[C@@H]1[C@@H]1CC[C@@](C(C)=O)(OC(=O)C)[C@@]1(C)CC2 QMBJSIBWORFWQT-DFXBJWIESA-N 0.000 description 2

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 239000000284 extract Substances 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 238000011084 recovery Methods 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- QVWYCTGTGHDWFQ-AWEZNQCLSA-N (2s)-2-[[4-[2-chloroethyl(2-methylsulfonyloxyethyl)amino]benzoyl]amino]pentanedioic acid Chemical compound CS(=O)(=O)OCCN(CCCl)C1=CC=C(C(=O)N[C@@H](CCC(O)=O)C(O)=O)C=C1 QVWYCTGTGHDWFQ-AWEZNQCLSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000033228 biological regulation Effects 0.000 description 1

- 244000145845 chattering Species 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 230000009191 jumping Effects 0.000 description 1

- 230000005389 magnetism Effects 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000012806 monitoring device Methods 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E60/00—Enabling technologies; Technologies with a potential or indirect contribution to GHG emissions mitigation

- Y02E60/10—Energy storage using batteries

Landscapes

- Pinball Game Machines (AREA)

Description

解決手段A1:本解決手段の遊技機は、遊技の実行を制御する遊技制御手段と、記憶領域に設けられた使用領域内に遊技の実行に必要となる情報を格納し、前記使用領域とは別に設けられた領域外に遊技の実行に必要とならない情報を格納することが可能な記憶手段とを備え、前記遊技制御手段は、遊技の実行中に前記領域外の情報を用いてエラーに関する判定を実行し、当該判定の結果を示す結果情報を生成して前記領域外に保存する一方、前記使用領域の情報を用いて前記領域外の前記結果情報を参照することで、前記判定の結果を外部に通知するための通知情報(例えば、サブコマンド)を生成して前記使用領域(例えば、サブコマンドバッファ)に保存することを特徴とする遊技機である。

(1)遊技制御手段(主制御基板)が設けられている。遊技制御手段には、例えば主制御CPUが搭載されている。

(1)遊技制御手段は、領域外の情報を用いて複数種類のエラー(例えば、スイッチ異常エラー、扉開放エラー、磁気検出エラー、電波検出エラー等)に関する判定を実行する。いずれかの種類のエラーに関して何らかの判定をした場合、結果情報をエラーの種類毎に生成して領域外に保存するが、このとき結果情報の数も合わせて保存しておく。逆に、全ての種類のエラーに関して何も判定しなければ(例えば、全ての種類のエラーの発生又は解除があったと判定しなければ)、結果情報を生成しないので、結果情報の数は0が保存される。

解決手段B1:本解決手段の遊技機は、遊技の実行を制御する遊技制御手段を備えた遊技機であって、前記遊技制御手段は、電源投入時の初期化処理が完了した後のメインループ処理に移行すると、割込み禁止状態にして前記メインループ処理内の全ての処理を実行し、終了後に前記メインループ処理の末尾から先頭に戻る期間のみを割込み許可状態とすることを特徴とする遊技機である。

(1)遊技制御手段(主制御基板)が設けられている。遊技制御手段には、例えば主制御CPUが搭載されている。

(3)このとき遊技制御手段は、メインループ処理全体を割込み禁止命令と割込み許可命令で囲んだロジックを実行する。すなわち、遊技制御手段は、メインループ処理に移行すると、割込み禁止状態にして全ての処理を実行する。割込み許可状態にするのは、全ての処理の実行終了後にメインループ処理の末尾から先頭に戻る期間だけとする。

(1)メインループ処理の実行中に、割込み処理(例えば、タイマ割込み処理、電断予告時割込み処理)が発生する。

(2)割込み処理の実行時は、メインループ処理に関するレジスタの退避及び復帰の処理を実行しない。

解決手段C1:本解決手段の遊技機は、遊技の実行を制御する遊技制御手段と、遊技に関する情報を記憶可能な記憶領域を有する記憶手段とを備え、前記遊技制御手段は、前記記憶領域で指定した範囲の先頭アドレス及び領域数に基づき、単一の命令を実行することで前記指定した範囲のチェックサムの算定処理を実行することを特徴とする遊技機である。

(1)遊技制御手段(主制御基板)が設けられている。遊技制御手段には、例えば主制御CPUが搭載されている。

(2)記憶手段が設けられている。記憶手段には、ROM、RWM等の記憶領域が含まれる。

(1)記憶領域で第1範囲のチェックサム算定処理を実行する場合、第1範囲についての第1先頭アドレス及び第1領域数を指定し、単一の命令を実行する。

(2)他に、記憶領域で別の第2範囲のチェックサム算定処理を実行する場合は、第2範囲についての第2先頭アドレス及び第2領域数を指定し、単一の命令を実行する。

すなわち、第1の範囲のチェックサム算定処理では、特定の命令を実行可能である。また、第2の範囲のチェックサム算定処理では、特殊な命令を実行可能である。

(1)チェックサムの算定処理は、電源投入時の初期化処理及び電源断時の割込み処理においてそれぞれ実行する。

(2)電源投入時の初期化処理では、チェックサムの算定結果を記憶領域(例えば、RWM)に保存する。

(3)電源断時の割込み処理では、チェックサムの算定結果の符号を反転させて記憶領域(例えば、RWM)に保存する。

解決手段D1:本解決手段の遊技機は、遊技の実行を制御する遊技制御手段と、遊技に関する情報を記憶可能な記憶領域を有する記憶手段とを備え、前記記憶手段は、前記記憶領域に互いにビット数が異なる第1データ及び第2データが組として設定されたテーブル領域を有し、前記遊技制御手段は、前記テーブル領域から第1レジスタと第2レジスタのペアに前記第1データと前記第2データの組を読み込んだ後、前記第1レジスタの値を所定値で除算したときの商を前記第1レジスタに格納し、その余りを第3レジスタに格納する命令を実行することで、前記第3レジスタと前記第2レジスタのペアによって前記第2データを生成することを特徴とする遊技機である。

(1)遊技制御手段(主制御基板)が設けられている。遊技制御手段には、例えば主制御CPUが搭載されている。

(2)記憶手段が設けられている。記憶手段には、ROM、RWM等の記憶領域が含まれる。

遊技制御手段は、生成した第2データを取得した乱数値と比較し、その結果に基づいて選択結果を返す。このとき選択結果は、第1レジスタに格納した内容、つまり、第1データと対応付けられた値(例えば、テーブル領域のアドレスで指し示される値)となる。

解決手段E1:本解決手段の遊技機は、遊技の実行を制御する遊技制御手段を備え、遊技に関して算定可能な複数種類の性能を有した遊技機であって、前記遊技制御手段は、制御に際してタイマ割込み処理を繰り返し実行しつつ、前記複数種類の性能を算定する複数の算定処理のうち、1回のタイマ割込み処理の中ではいずれか1つの算定処理のみを実行可能とすることを特徴とする遊技機である。

(1)遊技制御手段(主制御基板)が設けられている。遊技制御手段には、例えば主制御CPUが搭載されている。

(2)遊技に関して算定可能な複数種類の性能を有している。複数種類の性能は、例えば、ベース値、役物比率、連続役物比率等である。

(1)複数の算定処理には、予め優先度が設定されている。例えば、優先度の高い順にベース値の算定処理→役物比率の算定処理→連続役物比率の算定処理である。

(2)今回のタイマ割込み処理の中で、複数の算定処理を実行する条件が満たされているとした場合でも、複数を実行することとせず、優先度の高い算定処理だけを実行する。

図1は、管理遊技機のブロック図である。

管理遊技機100は、管理遊技機遊技盤10と、管理遊技機枠20とを備えており、機械単体内で一定数の遊技球を循環させ、遊技に用いる遊技球や遊技者に遊技球を直接払い出すことを不要とした封入式の遊技機である。管理遊技機100は、管理遊技機専用の専用ユニット(ICカードユニット)と接続することで遊技が可能になる。

管理遊技機の概要は、以下の通りである。

(1)管理遊技機100は、パチンコ機と同一の分類に属し、遊技者は、遊技球を管理遊技機遊技盤10の盤面に打ち出すことにより、遊技を行う。

(2)管理遊技機100は、構造的に上皿・下皿が無く、遊技者が直接遊技球に触れることができない。

(3)管理遊技機100は、発射に必要な最小数の遊技球を管理遊技機100内で循環させ、循環途中には、発射装置、球磨き装置、及び、遊技球循環装置が設けられている。

(4)発射装置は、現行遊技機の発射性能を有しており、下部発射であっても上部発射であってもよい。

(5)球磨き装置は、遊技球の汚れを落とすための研磨布がカセット内に収納されており、一定期間毎に交換する。

(6)遊技球数や獲得遊技球数は、数値データとして管理遊技機100(枠制御基板50)で管理して、表示する。

(7)遊技終了時は、計数スイッチ54(計数ボタン)を押下することで管理遊技機100(枠制御基板50)が管理していた遊技球数を専用ユニットに移行して管理することができる。

主制御基板30は、主制御基板30は、主制御CPU31を有しており、遊技の進行に関する内容(又は遊技の実行)を制御する。演出制御基板40は、演出制御CPU41を有しており、遊技の演出に関する内容を制御する。主制御基板30は、演出制御基板40及び枠制御基板50と通信可能である。演出制御基板40は、主制御基板30と通信可能であるが、この通信は、主制御基板30から演出制御基板40への片方向のみで行われ、双方向の通信は行われない。

主制御基板30(主制御CPU31)が用いるメモリ領域は、ROMに割り当てられたメモリ領域(0000H~2FFFH)と、RAM(RWM)に割り当てられたメモリ領域(F000H~F3FFH)とを含んでいる。

アドレス1000H~1BFFHの領域(第1領域)には、使用領域のプログラムデータ(第1情報)、及び、遊技の実行に必要とならないプログラムデータ(第2情報)のうちの一部の情報である特別プログラムデータ(特別情報)が格納されている。

アドレスF200H~F3FFHの領域は、領域外のワーク領域及びスタックRWMとして用いられる。

これらの領域は、使用領域のプログラムが実行されている際や領域外のプログラムが実行されている際に、一時的に用いられる領域やデータを一時的に退避させるスタック領域として用いられる。

このため、本実施形態では、領域外に関する処理を実行する場合よりも、使用領域に関する処理を実行する場合の方が、処理速度が速い。

以上が管理遊技機100の制御に関する構成例である。

管理遊技機100に電源が投入されると、主制御基板30がCPU初期化処理を開始する。CPU初期化処理は、前回の電源遮断時に保存されたバックアップ情報を元に遊技状態を復旧(いわゆる復電)したり、逆にバックアップ情報をクリアしたりすることで、管理遊技機100の初期状態を整えるための処理である。また、CPU初期化処理は、初期状態の調整後に管理遊技機100の安定した遊技動作を保証するためのメイン処理(メイン制御プログラム)として位置付けられる。

ステップS230:主制御基板30は、スタックエリアベースアドレスをセットする処理を実行する。

ステップS231:主制御基板30は、内蔵レジスタ設定テーブルのアドレスをセットする処理を実行する。

ステップS232:主制御基板30は、内蔵レジスタアドレスの上位バイト及び設定データ数をロードする処理を実行する。

ステップS233:主制御基板30は、内蔵レジスタ(FFxxH)を設定する処理を実行する。

ステップS234:主制御基板30は、内蔵レジスタアドレスの上位バイト及び設定データ数をロードする処理を実行する。

ステップS235:主制御基板30は、内蔵レジスタ(FFxxH)及び発射許可信号の設定する処理を実行する。

ステップS236:主制御基板30は、Qレジスタに作業領域先頭アドレスの上位バイトをセットする処理を実行する。

ステップS237:主制御基板30は、電源投入時の入力サポートの状態を取得する処理を実行する。

ステップS238:主制御基板30は、サブ制御起動待ち(演出制御基板の起動待ち)、かつ、主制御基板の電源が安定することを確認する処理を実行する。

ステップS240:主制御基板30は、設定確認及び不正検出状態をクリアする処理を実行する。

ステップS241:主制御基板30は、チェックサム確認処理を呼び出す処理を実行する。

その結果、チェックサムが正常であることを確認した場合(Yes)、主制御基板30は、ステップS243を実行する。一方、チェックサムが正常であることを確認できない場合(No)、主制御基板30は、外部結合子(2)に移行してステップS246(図4)を実行する。

その結果、RWMクリアスイッチが押下されていたことを確認した場合(Yes)、主制御基板30は、外部結合子(3)に移行してステップS247(図4)を実行する。一方、RWMクリアスイッチが押下されていたことを確認できない場合(No)、主制御基板30は、ステップS244を実行する。

ステップS245:主制御基板30は、設定確認処理への移行確認を実行する。

ステップS245の処理を終えると、主制御基板30は、外部結合子(1)に移行してステップS253(図4)を実行する。

ステップS247:主制御基板30は、作業領域初期化処理を実行する。

その結果、RWM異常であることを確認した場合(Yes)、主制御基板30は、ステップS249を実行する。一方、RWM異常であることを確認できない場合(No)、主制御基板30は、ステップS250を実行する。

その結果、設定変更条件を満たしたことを確認した場合(Yes)、主制御基板30は、ステップS251を実行する。一方、設定変更条件を満たしたことを確認できない場合(No)、主制御基板30は、ステップS252を実行する。

ステップS252:主制御基板30は、遊技機状態フラグを更新する処理を実行する。

ステップS253:主制御基板30は、電源投入時設定処理を呼び出す処理を実行する。

ステップS254:主制御基板30は、枠コマンド待機状態をセットする処理を実行する。

ステップS255:主制御基板30は、デイジーチェーンをリセットする処理を実行する。

ステップS256:主制御基板30は、割込みを禁止する処理(割込み禁止命令)を実行する。

ステップS257:主制御基板30は、初期値乱数更新処理を呼び出す処理を実行する。

ステップS259:主制御基板30は、サブコマンド送信処理を呼び出す処理を実行する。

ステップS260:主制御基板30は、割込みを許可する処理(割込み許可命令)を実行する。

ステップS259の処理を終えると、主制御基板30は、ステップS256の処理に戻って処理を継続する。これにより、メインループ処理が開始する。

ここで、本実施形態の第2の技術的特徴について、複数の例を挙げて説明する。なお、本実施形態の技術的特徴は、第1から第5までが存在するが、説明の都合上、順番が入れ替わっている。したがって、第1の技術的特徴及び第3以降の技術的特徴については、第2の技術的特徴より後で説明することとする。

使用領域のプログラム容量(コード量)の削減を実現する。本課題は、管理遊技機100以外のパチンコ機であっても、記憶手段に使用領域及び領域外を有する場合には該当する。

本実施形態では、メインプログラム容量を削減するため、割込み処理内のプログラムコードを削減できる構成とした。図4の割込み待ちメインループ処理(1)は、本解決手段の1つを構成するものである。

すなわち、割込み待ちメインループ処理(1)は、主制御基板30が図4の点線枠で囲った部分(符号ML)をループする処理である。本実施形態では、割込み待ちメインループ処理(1)の中で実行する全ての処理、つまり、初期値乱数更新処理(ステップS257)及びサブコマンド送信処理(ステップS259)を割込み禁止命令(ステップS256)と割込み許可命令(ステップS260)で囲んでいる。このため、割込み待ちメインループ処理(1)の中で割込み許可状態となるのは、割込み許可命令(ステップS260)の実行後、プログラム末尾から先頭に戻る命令を実行してから割込み禁止命令(ステップS256)を実行するまでの期間となる。

「DI」は、割込み禁止状態にする命令である。これにより、割込み待ちメインループ処理(1)の開始時に割込み禁止状態となる。

「CALLF INI_RND」は、初期値乱数更新処理を呼び出す処理である。本処理では、各種のソフトウェア乱数の初期値をランダムに更新する処理を実行する。

「CALLF SBC_OUT」は、サブコマンド送信処理を呼び出す処理である。本処理では、サブコマンドバッファに格納されているサブコマンドをポート出力する処理を実行する。

「JR CPUINIT_80」は、割込み待ちメインループ処理(1)の先頭アドレスにジャンプする命令である。

EI命令はその仕様上、実行した直後は割込みが発生せずに次の命令が実行される。このため、割込み待ちメインループ処理(1)の中で割込みが発生する可能性があるのは、「JR CPUINIT_80」命令を実行した直後だけに限定されることになる。

図6は、割込み待ちメインループ処理(2)の手順例を示すフローチャートである。本実施形態では、このような割込み待ちメインループ処理(2)を採用することもできる。以下、図4の割込み待ちメインループ処理(1)と異なる点を説明する。

「CALLF PY_CMDA」は、主コマンド解析処理を呼び出す処理である。本処理では、枠制御基板50から送信されているコマンド(主コマンド)を解析する処理を実行する。

図8は、比較例の割込み待ちメインループ処理の手順例を示すフローチャートである。ここでは、本実施形態との比較のため、割込み待ちメインループ処理の中に割込み許可状態で実行される処理が存在している例を挙げるものとする。

ステップS142:本実施形態と同様の初期値乱数更新処理を実行する。

ステップS143:本実施形態と同様の主コマンド解析処理を実行する。

ステップS144:本実施形態と同様のサブコマンド送信処理を実行する。

ステップS146:本実施形態と同様に、割込み許可命令を実行し、次の処理実行時から割込み許可状態とする。

「LD A,R」は、Rレジスタ値をセットする命令である。

「LDQ HL,(LOW R_RND_TZ__MOD)」は、特別図柄リーチモード決定乱数をロードする命令である。

「ADDWB HL,A」、「INC HL」は、特別図柄リーチモード決定乱数を更新する命令である。

「LD BC,@RND_MOD_MAX+1」は、特別図柄リーチモード決定乱数上限値をセットする命令である。

プログラムコードは続いているが、以下の〔1〕と〔2〕の間にタイマ割込みが発生した場合を想定する。

〔1〕「DIV HL,BC」は、更新結果を特別図柄リーチモード決定乱数上限値で除算する命令である。

〔2〕「LDQ (LOW R_RND_TZ__MOD),BC」は、特別図柄リーチモード決定乱数に剰余をセーブする命令である。

上記〔1〕と〔2〕の間に割込み処理が発生しても、復帰後はその他乱数更新処理が続行されるが、処理の中でAレジスタの他にBCレジスタを使用していることが分かる。このため、タイマ割込み処理中にBCレジスタの値が変化した状態で戻ってくると、〔2〕で特別図柄リーチモード決定乱数にセーブするBCレジスタの値と、〔1〕で演算した結果設定されたBCレジスタは全く無関係な値となる。

したがって、タイマ割込み処理側では、処理の開始時にBCレジスタ等を退避し、タイマ割込み処理の終了時にBCレジスタ等を復帰する必要がある。

〔特別図柄変動パターン乱数更新処理〕

「LD DE,@RND_PAT_MAX*256+LOW R_RND_TZ__PAT」は、特別図柄変動パターン乱数上限値及び特別図柄変動パターン乱数のアドレスの下位バイトをセットする命令である。

「RST COUNTUP」は、カウントアップ処理を呼び出す処理である。

「RET」は、呼び出し元の割込み待ちメインループ処理に復帰する命令である。

以下に、本実施形態と比較例とをプログラム上で対比して説明する。

図11は、タイマ割込み処理のプログラムを示す図である。ここでは、対比の結果が明白となる部分を取り上げて説明する。タイマ割込み処理のプログラム(コード)は、以下の通りである。

「PUSH GPR」は、AF,BC,DE,HLレジスタを退避する命令である。

ここで、図中に「比較例:必要/本実施形態:不要」と示したように、比較例のプログラムでは本処理が必要となるが、本実施形態では本処理が全く不要となる点で異なる。

「CALLF DYM_OUT」は、ダイナミックポート出力処理を呼び出す処理である。

(中略)

「CALLEX E_SFSET」は、安全装置発動管理フェーズ設定処理を呼び出す処理である。

「POP GPR」は、HL,DE,BC,AFレジスタを復帰する命令である。

ここで、図中に「比較例:必要/本実施形態:不要」と示したように、比較例のプログラムでは本処理が必要となるが、本実施形態では本処理が全く不要となる点で異なる。

「TMR_IPT_30」は、割込み許可処理の開始を示すラベルである。

「EI」は、割込み許可状態にする命令である。

「RETI」命令により、割込み発生前に復帰する。

「PUSH AF」は、AFレジスタを退避する命令である。ここで、図中に「比較例:必要/本実施形態:不要」と示したように、比較例のプログラムでは本命例の実行が必要となるが、本実施形態では不要となる。

「JIBIT Z,@IN3_PWF_POS,(LOW @IN3_PRT),PRFPROC_10」は、入力ポート3の電源断予告信号ビットが0であれば、「PRFPROC_10」に分岐する命令である。

「POP AF」は、AFレジスタを復帰する命令であるが、ここでも図中に「比較例:必要/本実施形態:不要」と示したように、比較例のプログラムでは本命例の実行が必要となるが、本実施形態では不要となる。

「EI」命令で割込み許可状態とする。

「RETI」命令で電源断時の退避処理発生前に復帰する。

「PRFPROC_10:」は、出力ポートクリア処理の開始を示すラベルである。

「OUT (LOW @OT1_PRT),@OT1_LCE_BIT」は、出力ポート1に発射許可信号を出力する命令である。

「LDF HL,D_OUT_PRT」は、出力ポートアドレステーブルのアドレスをセットする命令である。

「LD B,@PRT_CLR_LOP」は、出力ポート初期化ループカウンタをセットする命令である。

「XOR A,A」は、[00H]をセットする命令である。

(以下略)

図13は、タイマ割込み処理の手順例を示すフローチャートである。図13のフローチャートは、図11のプログラムに一部対応している。図13では、比較例では実行する必要があるが、本実施形態では実行する必要がない手順を点線で示している。

上記のように、本実施形態ではレジスタ退避処理(ステップS300)が不要となる。したがって、ダイナミックポート出力処理(ステップS302)から開始する。

外部情報管理処理では、「設定変更中又は設定確認中」等である場合に、外部信号(セキュリティ信号)を出力する。

ここで上記のように、本実施形態ではレジスタ復帰処理(ステップS320)が不要となる。

上記のように、本実施形態では、図中に点線で示したレジスタ退避処理(ステップS270)が不要となる。したがって、電源断予告信号検出確認処理(ステップS280)から開始する。

ステップS280:主制御基板30は、電源断予告信号がONであるか否かを確認(再確認)する処理を実行する。

その結果、電源断予告信号がONであることを確認した場合(Yes)、主制御基板30は、ステップS282を実行する。一方、電源断予告信号がONであることを確認できない場合(No)、主制御基板30は、ステップS281を実行する。

ステップS281の処理を終えると、主制御基板30は、割込み前のアドレスに戻る。

ここで、上記のように本実施形態では、電源断状態ではなくなったために割込み前に復帰する場合でも、図中に点線で示したレジスタ復帰処理(ステップS272)が不要となる。

ステップS283:主制御基板30は、出力ポートアドレステーブルのアドレスをセットする処理を実行する。

ステップS284:主制御基板30は、出力ポート初期化ループカウンタをセットする処理を実行する。

ステップS285:主制御基板30は、Aレジスタに[00H]をセットする処理を実行する。

ステップS286:主制御基板30は、対象アドレスの内容をロードする処理を実行する。

ステップS287:主制御基板30は、出力ポートに[00H]を出力する処理を実行する。

ステップS288:主制御基板30は、HLレジスタをインクリメントする処理を実行する。

その結果、ループ継続であることを確認した場合(Yes)、主制御基板30は、ステップS286を実行する。一方、ループ継続であることを確認できない場合(No)、主制御基板30は、外部結合子(1)に移行してステップS290(図15)を実行する。

ステップS291:主制御基板30は、RWMアクセスプロテクトレジスタにRAMアクセス禁止値を出力する処理を実行する。

ステップS292:主制御基板30は、電源断予告信号確認設定値をセットする処理を実行する。

その結果、電源断予告信号がオンであることを確認した場合(Yes)、主制御基板30は、ステップS292を実行する。一方、電源断予告信号がオンであることを確認できない場合(No)、主制御基板30は、ステップS294を実行する。

その結果、第2ゼロフラグが0であることを確認した場合(Yes)、主制御基板30は、ステップS293を実行する。一方、第2ゼロフラグが0であることを確認できない場合(No)、主制御基板30は、[0000H]番地にジャンプする処理を実行する。

ここで、本実施形態の第3の技術的特徴について説明する。第3の技術的特徴は、電源断時の退避処理の中で実行されるチェックサム算定処理(図15のステップS290)、及びCPU初期化処理の中で実行されるチェックサム確認処理(図3のステップS241)に特定の命令を使用した構成である。

電源断時のチェックサムの算定、電源再投入時のチェックサムの確認にかかる時間を短縮することを課題とする。

すなわち、管理遊技機100のような遊技機では、電源投入時にバックアップチェックデータ及びチェックサムの確認を行い、異常であった場合(初回起動時を含む)は全てのRWMをクリアしている。

このとき、バックアップチェックデータ及びチェックサムの設定は、電源断時の退避処理で作成、保存を行うことになるが、既に電源供給は絶たれているため、チェックサムの算定及び確認については、いずれも可能な限り短い時間で処理を終わらせる必要がある。

チェックサムの算定方法は、「スタック領域の2バイトを除く使用領域の全領域と領域外の使用RWMを減算した結果の下位1バイト」とする。例えば、算定対象のRWMの値が1,2,3,4である場合は、0-1-2-3-4=-10となる。

チェックサムは符号なしの1バイトの整数(0~255)であるため、RWMに保存される値は-10+256=246となる。

図16は、比較例のチェックサム算定処理のプログラムを示す図である。比較例では、本実施形態で使用する特定の命令を使用しない構成である。なお、図16のプログラムコード中、各行に付記している括弧書きの数値は、主制御CPU31が命令を実行するために必要とする内部クロック数(ステート数)を示している。比較例のチェックサム算定処理のプログラム(コード)は、以下の通りである。

(中略)

(1)「XOR A,A」は、Aレジスタに[00H]をセットする命令である。ステート数は1である。

(3)「LD HL,@RM_RAMADR」は、HLレジスタに作業領域先頭アドレスをセットする命令である。ステート数は3である。

(3)「LD BC,@CHK_ARE」は、BCレジスタにチェックサム算定領域数をセットする命令である。ステート数は3である。

「E_CLSUM_10:」は、ループ処理の先頭アドレスを示すラベルである。

(2)「SUB A,(HL)」は、HLレジスタに現状セットされているアドレスのRWMチェックサムを算定する命令である。ステート数は2である。

(1)「INC HL」は、HLレジスタをインクリメントし、次のRWMアドレスをセットする命令である。ステート数は1である。

(2)「DEC BC」は、チェックサム算定領域数を1減算する命令である。チェックサム算定領域を全て算定するとBCレジスタが0になる。ステート数は2である。

(3/2)「JR NTZ,E_CLSUM_10」は、チェックサム算定領域を全て算定しておらず、ループ継続であれば先頭に分岐する命令である。ステート数は、分岐の場合は3となり、非分岐の場合は2となる。

(2)「LDQ HL,LOW @RM_EXTADR」は、HLレジスタに領域外作業領域先頭アドレスをセットする命令である。ステート数は2である。

(2)「LD B,@EXD_USE_ERW」は、Bレジスタに領域外RWM使用領域数をセットする命令である。ステート数は2である。

(2)「SUB A,(HL)」は、HLレジスタに現状セットされているアドレスのRWMチェックサムを算定する命令である。ステート数は2である。

(1)「INC HL」は、HLレジスタをインクリメントし、次のRWMアドレスをセットする命令である。ステート数は1である。

(3/2)「DJNZ E_CLSUM_20」は、領域外RWM使用領域を全て算定しておらず(Bレジスタを減算して0でなく)、ループ継続であれば先頭に分岐する命令である。ステート数は、分岐の場合は3となり、非分岐の場合は2となる。

(3)「LDQ (LOW R_ERW_SUM),A」は、サムチェックバッファに算定結果をセーブする命令である。ステート数は3である。

以上より、例えばチェックサム対象となる使用領域のRWMが510バイト、領域外のRWMが170バイトであるとすると、チェックサムの算定に必要な総ステート数は、1+3+3+(510-1)*(2+1+2+3)+(2+1+2+2)+2+2+(170-1)*(2+1+3)+(2+1+2)+2=5112となる。したがって、主制御CPU31の内部システムクロックが16MHzである場合、比較例のチェックサム算定処理の実行時間は0.3195msとなる。

チェックサムの確認方法は、「スタック領域の2バイトを除く使用領域の全領域と領域外の使用RWMを減算した結果の下位1バイトが0であるか」とする。例えば、RWMの値が1,2,3,4であり、チェックサムとして246が保存されている場合は、1+2+3+4+246=256となり、下位1バイトは0となるので、この場合はチェックサムが正しく保存されていると確認することができる。

図17は、比較例のチェックサム確認処理のプログラムを示す図である。ここでも同様に、比較例では、本実施形態で使用する特定の命令を使用しない構成である。また、図17のプログラムコード中、各行に付記している括弧書きの数値はステート数を示している。比較例のチェックサム確認処理のプログラム(コード)は、以下の通りである。

(中略)

(1)「XOR A,A」は、Aレジスタに[00H]をセットする命令である。ステート数は1である。

(3)「LD HL,@RM_RAMADR」は、HLレジスタに作業領域先頭アドレスをセットする命令である。ステート数は3である。

(3)「LD BC,@CHK_ARE」は、BCレジスタにチェックサム算定領域数をセットする命令である。ステート数は3である。

(2)「ADD A,(HL)」は、HLレジスタに現状セットされているアドレスのRWMチェックサムを算定する命令である。ステート数は2である。

(1)「INC HL」は、HLレジスタをインクリメントし、次のRWMアドレスをセットする命令である。ステート数は1である。

(2)「DEC BC」は、チェックサム算定領域数を1減算する命令である。チェックサム算定領域を全て算定するBCレジスタが0になる。ステート数は2である。

(3/2)「JR NTZ,E_CKSUM_10」は、チェックサム算定領域を全て算定しておらず、ループ継続であれば先頭に分岐する命令である。ステート数は、分岐の場合は3となり、非分岐の場合は2となる。

(2)「LDQ HL,LOW @RM_EXTADR」は、HLレジスタに領域外作業領域先頭アドレスをセットする命令である。ステート数は2である。

(2)「LD B,@EXD_USE_ERW」は、Bレジスタに領域外RWM使用領域数をセットする命令である。ステート数は2である。

(2)「ADD A,(HL)」は、HLレジスタに現状セットされているアドレスのRWMチェックサムを算定する命令である。ステート数は2である。

(1)「INC HL」は、HLレジスタをインクリメントし、次のRWMアドレスをセットする命令である。ステート数は1である。

(3/2)「DJNZ E_CKSUM_20」は、領域外RWM使用領域を全て算定しておらず(Bレジスタを減算して0でなく)、ループ継続であれば先頭に分岐する命令である。ステート数は、分岐の場合は3となり、非分岐の場合は2となる。

(3)「LDQ (LOW R_ERW_BRS),A」は、チェックサム結果フラグに値をセーブする命令である。ステート数は3である。

以上より、電源投入時のチェックサム確認処理でチェックサムの算定に必要な総ステート数は、電源断時と同じく5112ステートとなる。したがって、比較例のチェックサム確認処理の実行時間は同じく0.3195msとなる。

図18は、本実施形態のチェックサム算定処理のプログラムを示す図である。本実施形態では、チェックサムの算定及び確認にADDIR命令及びADDIRS命令を使用している。ADDIR命令及びADDIRS命令は、HLレジスタが指定した開始番地から、BCレジスタ(ADDIRS命令はBレジスタ)で指定したバイト数のRWMの和を計算する命令である。なお、和ではなく差を計算する命令は存在しないため、電源断時の退避処理でサムチェックバッファの値を設定する際は、一旦、和を計算してから2の補数を取る(符号を反転する)こととする。以下、比較例と同じ命令については説明を省略し、本実施形態に特有の命令を中心に説明する。本実施形態のチェックサム算定処理のプログラム(コード)は、以下の通りである。

(中略)

(1)「XOR A,A」:比較例と同じ。

(3)「LD HL,@RM_RAMADR」:比較例と同じ。

(3)「LD BC,@CHK_ARE」比較例と同じ。

(3)「ADDIR」は、ブロックサーチ命令である。具体的には、開始アドレス(@RM_RAMADR)からチェックサム算定領域数(@CHK_ARE)で指定したバイト数のRWMの和を計算する。ここでは、加算1バイトあたりのステート数が3である。

(2)「LDQ HL,LOW @RM_EXTADR」:比較例と同じ。

(2)「LD B,@EXD_USE_ERW」:比較例と同じ。

(3)「ADDIRS」は、ブロックサーチ命令である。具体的には、開始アドレス(@RM_EXTADR)からチェックサム算定領域数(@EXD_USE_ERW)で指定したバイト数のRWMの和を計算する。ここでは、加算1バイトあたりのステート数が3である。

(2)「NEG」は、2の補数をセットする命令である。ステート数は2である。

(3)「LDQ (LOW R_ERW_SUM),A」は、サムチェックバッファに値をセーブする命令である。ステート数は3である。

以上より、比較例と同じくチェックサム対象となる使用領域のRWMが510バイト、領域外のRWMが170バイトであるとすると、本実施形態でチェックサムの算定に必要な総ステート数は、1+3+3+510*3+2+2+170*3+2+3=2056となる。したがって、主制御CPU31の内部システムクロックが16MHzである場合、本実施形態では処理時間が0.1285msに短縮されることになる。

図19は、本実施形態のチェックサム確認処理のプログラムを示す図である。本実施形態のチェックサム確認処理のプログラム(コード)は、以下の通りである。

(中略)

(1)「XOR A,A」:比較例と同じ。

(3)「LD HL,@RM_RAMADR」:比較例と同じ。

(3)「LD BC,@CHK_ARE」:比較例と同じ。

(3)「ADDIR」は、ブロックサーチ命令である(電源投入時のチェックサム確認であるため、ブロックサーチと表現する)。具体的には、開始アドレス(@RM_RAMADR)からチェックサム算定領域数(@CHK_ARE)で指定したバイト数のRWMの和を計算する。そして、加算1バイトあたりのステート数は3である。

(2)「LDQ HL,LOW @RM_EXTADR」:比較例と同じ。

(2)「LD B,@EXD_USE_ERW」:比較例と同じ。

(3)「ADDIRS」は、ブロックサーチ命令である。具体的には、開始アドレス(@RM_EXTADR)からチェックサム算定領域数(@EXD_USE_ERW)で指定したバイト数のRWMの和を計算する。そして、加算1バイトあたりのステート数は3である。

(3)「LDQ (LOW R_ERW_BRS),A」は、チェックサム結果フラグに値をセーブする命令である。ステート数は3である。

以上より、本実施形態のチェックサム確認処理でチェックサムの算定に必要な総ステート数は、1+3+3+510*3+2+2+170*3+3=2054となる。NEG命令を使用して符号の反転を行う必要がないため、電源断時よりステート数が2少なく、処理時間が0.128375msに短縮されることになる。

図20は、本実施形態による処理時間の短縮化の検証結果を示す図である。図20の検証結果から、以下の優位性が明らかである。

(1)チェックサム算定処理の処理時間を比較例から約59.78%改善することができる。

(2)チェックサム確認処理の処理時間を比較例から約59.82%改善することができる。

(3)総合すると、チェックサムの算定に要する時間を概ね1/2.5に短縮することができる。

(4)これにより、電源投入時はより早期にメインループ処理に移行することができる。

(5)特に電源断時は、電源供給が完全に途絶えてしまう前に確実にチェックサム算定を完了させることができ、退避処理の確実性を向上させることができる。

(6)管理遊技機100がスロット機である場合も同様の有用性を得ることができる。

次に、本実施形態の第1の技術的特徴について説明する。

使用領域のプログラム容量(コード量)の削減を実現する。本課題は、管理遊技機100以外のパチンコ機であっても、記憶手段に使用領域及び領域外を有する場合には該当する。

本実施形態では、領域外に格納したプログラムを実行してエラーの発生、解除を判定する。領域外でエラーの発生又は解除と判定した場合、サブコマンドを生成して領域外のRWMに保存する。使用領域に格納したプログラムは、領域外のRWMにサブコマンドが保存された場合、それを読み込んで使用領域にサブコマンドバッファを設定する構成とした。

図21は、使用領域の状態管理処理のプログラムを示す図である。状態管理処理のプログラム(コード)は、以下の通りである。なお、図21のプログラムコード中、各行に付記している括弧書きの数値は、使用バイト数を示している。

(2)「CALLEX E_CKERR」は、領域外のエラー確認処理を呼び出す処理である。ここでのコード量は2バイトである。

なお、領域外のエラー確認処理では、エラーに係るサブコマンド等を領域外のRWMに設定する。この処理の終了後、以下のプログラムで入賞異常系のエラーフラグ(R_ERR_FLG)をクリアする。このように、入賞異常系のエラーは、設定した直後の状態管理処理でフラグをクリアされるが、クリアされる前にサブコマンドの設定、遊技停止要求フラグの設定、不正検知1情報ビットタイマの設定を行うこととする。

(2)「CLRQ (LOW R_ERR_FLG)」は、入賞異常系のエラーフラグをクリアする命令である。ここでのコード量は2バイトである。

以下のプログラムでは、エラー確認処理で領域外のRWMに設定したサブコマンドを読み出し、サブコマンドセット処理(SBCMDST)を呼び出す。

(3)「LD HL,R_ERW_SBC」は、HLレジスタにサブコマンド要求カウンタのアドレスをセットする命令である。ここでのコード量は3バイトである。

(1)「LD B,(HL)」は、HLレジスタで指定される対象アドレスの内容をロードする命令である。具体的には、領域外で設定したサブコマンドの数をロードする。ここでのコード量は1バイトである。

(2)「JR TZ,STC_PRC_20」は、第2ゼロフラグが1であればラベル「STC_PRC_20」に分岐する命令である。具体的には、ロードしたサブコマンドの数が0の場合に分岐する。ここでのコード量は2バイトである。

〔サブコマンドセット処理〕

(2)「INLD DE,(HL)」は、サブコマンドをロードする命令である。具体的には、サブコマンド要求バッファ(R_ERW_SCD)から、先行コマンドと後続コマンドをロードする。サブコマンド要求バッファは、サブコマンド要求カウンタの直後に配置されており、INLD命令でHLレジスタを更新しながらDEレジスタにサブコマンド要求バッファの値をロードする。ここでのコード量は2バイトである。

(1)「RST SBCMDST」は、サブコマンドセット処理を呼び出す処理である。ここでは、サブコマンドバッファにサブコマンドを設定する。なお、領域外で設定したサブコマンドは、すべて加算不許可(Eレジスタのbit0を「1」)としている。これは、使用領域でAレジスタのクリア(「XOR A,A」等)を省略するためである。ここでのコード量は1バイトである。

(2)「DJNZ STC_PRC_10」は、サブコマンドを全てセットしておらず(Bレジスタを減算して0でなく)、ループ継続であれば先頭「STC_PRC_10」に分岐する命令である。すなわち、領域外で設定したサブコマンドをすべて読み込んでいない場合、ループ先頭へ戻る。ここでのコード量は2バイトである。

〔遊技盤エラー状態フラグ更新処理〕

領域外のエラー確認処理において、遊技を停止しなければならない致命的な異常があると判定(エラーを判定)した場合、領域外の遊技停止要求フラグに遊技停止を表す値(@YUG_HNF,06H)が設定されることになる。

以下の使用領域のプログラムでは、この値を使用領域の遊技盤エラー状態フラグ(R_YUG_ERR)と論理和する。なお、遊技盤エラー状態フラグの取り得る値は「00H」か「06H」のいずれかである。

(3)「LD A,(R_ERW_YER)」は、遊技停止要求フラグをロードする命令である。ここでのコード量は3バイトである。

(3)「ORQ (LOW R_YUG_ERR),A」は、遊技停止要求フラグを遊技盤エラー状態フラグと論理和する命令である。ここでのコード量は3バイトである。

(2)「LDQ A,(LOW R_IN1_PRT)」は、入力ポート1状態フラグをロードする命令である。ここでのコード量は2バイトである。

(2)「AND A,@IN1_HDL_BIT」は、入力ポート1状態フラグとハンドル検出信号を論理積する命令である。ここでのコード量は2バイトである。

(3)「RCPQ Z,A,(LOW R_HDL_STS)」は、ハンドルステータスと比較し、ゼロフラグが1であれば呼び出し元に復帰する命令である。ここでのコード量は3バイトである。

ハンドル検出は不正防止対策ではないため、使用領域で確認する必要がある。

以下のプログラムでは、ハンドル検出信号が変化しない場合はそのまま呼び出し元に戻り、ハンドル検出信号が変化した場合はサブコマンドを送信する。なお、チャタリングなどにより検出・非検出が短時間で変化することが考えられるが、その場合でもすべてサブコマンドを送信し、対処を行うか否かは演出制御基板40(演出制御CPU41)側のプログラムで判断することとしている。

(2)「LDQ (LOW R_HDL_STS),A」は、ハンドルステータスにセーブ(ステータスを更新)する命令である。ここでのコード量は2バイトである。

(3)「LD DE,@CMD_STS_HDL」は、サブコマンドのハンドル検出指定(@CMD_STS_HDL)をセットする命令である。ここでのコード量は3バイトである。

(1)「RST SBCMDST」は、サブコマンドセット処理を呼び出す処理である。ここでのコード量は1バイトである。

(1)「RET」は、呼び出し元に復帰する命令である。コード量は1バイトである。

ステップS502:主制御基板30は、サブコマンド要求カウンタをロードする。

ステップS503:主制御基板30は、ロードしたサブコマンド要求カウンタの値が0であるか否かを確認する。

その結果、ロードした値が0であることを確認した場合(Yes)、主制御基板30はステップS507を実行する。一方、ロードした値が0あることを確認できない場合(No)、主制御基板30はステップS504を実行する。

ステップS505:主制御基板30は、サブコマンドセット処理を呼び出す処理を実行する。この処理において、主制御基板30は使用領域のサブコマンドバッファを設定する。

ステップS506:主制御基板30は、全てのサブコマンドをセット(ロードした領域外の全サブコマンドに対応するサブコマンドバッファを設定)したか否かを確認する。全サブコマンドをセットしたことを確認できた場合(Yes)、主制御基板30はステップS507を実行する。一方、未だ全サブコマンドをセットしたことを確認できない場合(No)、主制御基板30はステップS504を実行してループを継続する。

ステップS508:主制御基板30は、遊技盤エラー状態フラグに遊技停止要求フラグを論理和する。

ステップS509:主制御基板30は、入力ポート1状態フラグをロードする。

ステップS510:主制御基板30は、入力ポート1状態フラグとハンドル検出信号を論理積する。

ステップS511:主制御基板30は、ステップS510の値がハンドルステータスと一致するか否かを確認する。その結果、ハンドルステータスと一致する(ハンドル検出信号が変化しない)ことを確認した場合(Yes)、主制御基板30は呼び出し元に復帰する。一方、ハンドルステータスと一致することを確認できない(ハンドル検出信号が変化した)場合(No)、主制御基板30はステップS512を実行する。

ステップS512:主制御基板30は、ハンドルステータスを更新する。

ステップS513:主制御基板30は、サブコマンドの「ハンドル検出指定」をセットする。

ステップS514:主制御基板30は、サブコマンドセット処理を呼び出す処理を実行する。この処理では、主制御基板30は、サブコマンドバッファに「ハンドル検出指定」のサブコマンドを設定する。

以上の手順を終えると、主制御基板30は、呼び出し元に戻る。

以上のように、使用領域のプログラムコード量は(図21)35バイト(フローチャートで示す手順数15ステップ)であり、プログラム容量の増大を抑えることができる。なお、ハンドル検出信号に関しては使用領域で処理を行っているが、それでも簡略化のために検出用タイマを持たず、信号のオンエッジ/オフエッジだけでサブコマンドを送信するロジックとし、コード量の増大を抑えることができている。

図23から図27は、領域外に格納されるエラー確認処理のプログラムを示す図である。上記のように、使用領域ではエラー発生又は解除の判定を行わないこととしている分、領域外には処理に必要な相当量のプログラムを格納している。エラー確認処理のプログラム(コード)は、以下の通りである。なお、特に省略しない限り、プログラムは図23~図27で一連のものである。

「JP E_CKERR_01」は、ラベル「E_CKERR_01」のアドレスへジャンプする命令である。

(中略)

上記の「JP E_CKERR_01」は、そのための2バイトのジャンプ命令である。ジャンプ先のアドレスは2000H~20FFHでなくてもよいので、ラベル「E_CKERR_01」のアドレスはそれ以降のアドレスに記述されている。

初期化処理は、「JP E_CKERR_01」命令で呼び出される。

「E_CKERR_01:」は、初期化処理の開始を示すラベルである。

「LD Q,HIGH @RM_EXTADR」は、領域外作業領域先頭アドレスの上位バイトをセットする命令である。

ここで、本実施形態では、CALLEX命令によりレジスタセットのバンクが「バンク0」から「バンク1」に変更され、また、RETEX命令によりバンクが「バンク1」から「バンク0」に変更される。バンク0のQレジスタとバンク1のQレジスタは、機能としては同等のものであるが、値は互いに独立している。例えば、バンク0のQレジスタにF0Hという値を設定したとしても、バンク1のQレジスタの値は変化しない。

上記のように記憶手段のRWMには、F000H~F3FFHまでの4キロバイトが実装されているが、使用領域のRWMとしてF000H~F1FFH、領域外のRWMとしてF300H~F3FFHを使用している(図2のメモリマップ参照)。また、F200H~F2FFHは未使用である。

このとき、領域外用(「バンク1」とする)のQレジスタにはF3Hを設定する。これにより、F300H~F3FFHのRWMに対してQレジスタを用いた命令を使用することができることになる。領域外のプログラムコードは、規則上の制限を受けないが、より長さを抑えたコードを使用した方が実行時間も長期化を抑えることができるため、領域外についてもコードを短縮化することが望ましい。

「CLRQ (LOW R_ERW_SBC)」は、サブコマンド要求カウンタをクリアする命令である。本命令により、領域外でセットするサブコマンドの数が初期化される。

ループ設定処理1では、エラー確認用のループで使用するテーブルのアドレス及びループ回数を設定する。ハンドル検出は使用領域で行うため、ここで判定するエラーは、「スイッチ異常」、「扉開放」、「盤面磁気エラー1」、「盤面磁気エラー2」及び「電波エラー」の5種類である。なお、エラーの種類は、機種(盤面の種類)によって異なる場合がある。

「LD HL,D_ETB_ER1」は、エラー管理処理テーブル1のアドレスをセットする命令である。なお、エラー管理処理テーブル1については後述する。

「LD B,@D_ETB_ER1_NUM」は、状態項目数をセットする命令である。

「E_CKERR_10:」は、監視対象信号ビットデータ判定処理の開始を示すラベルである。

「LDIN DE,(HL)」は、入力ポート状態フラグのアドレスをロードする命令である。

「LD A,(DE)」は、ロードした対象アドレスの内容をAレジスタにロードする命令である。

「LD C,0」は、Cレジスタに0をセットする命令である。

「AND A,(HL)」は、監視対象ビットデータと論理積する命令である。つまり、上の命令で先ずCレジスタに0を設定し、本命令では目的のビット以外をすべて0にする。

「JR Z,E_CKERR_20」は、ゼロフラグが1であれば分岐する命令である。

「INC C」は、Cレジスタをインクリメントする命令である。すなわち、目的のビットが0の場合は、上の命令で「E_CKERR_20」に分岐し、そうでない場合は本命令でCレジスタに1を設定することになる。これにより、エラー検出時はCレジスタに1が設定され、エラー未検出時はCレジスタに0が設定されることになる。

監視対象ステータス今回値処理は、上記の「JR Z,E_CKERR_20」命令でゼロフラグが1の場合に呼び出される。

「E_CKERR_20:」は、監視対象ステータス今回値処理の開始を示すラベルである。監視対象ステータス今回値処理は、以下の監視対象ステータス今回値更新処理及び監視対象ステータス今回値判定処理を含む構成である。

「INLD DE,(HL)」は、監視対象ステータス前回値のアドレスをロードする命令である。

「LD A,(DE)」は、対象アドレスの内容をロードする命令である。ここでは、上の命令で監視対象ステータス前回値のアドレスをロードし、本命令でAレジスタに前回値をロードする。

「CP A,C」は、AレジスタとCレジスタを比較する命令である。ここでは、監視対象ステータス前回値と監視対象ステータス今回値を設定し、ゼロフラグを更新する。

「LD (DE),C」は、対象アドレスの内容にセーブする命令である。ここでは、監視対象ステータス今回値を監視対象ステータス前回値にセーブする。

「INC DE」は、DEレジスタをインクリメントする命令である。すなわち、監視対象ステータス前回値を指しているDEレジスタに1を加算し、当該エラーの監視タイマのアドレスを指した状態にする。

「INC HL」は、HLレジスタをインクリメントする命令である。ここでは、テーブルを指しているHLレジスタに1を加算し、当該エラーの監視タイマ値のアドレスを指した状態にする。

「JR Z,E_CKERR_30」は、ゼロフラグが1であれば分岐する命令である。ここでは、先の「CP A,C」命令で設定したゼロフラグを確認し、ゼロフラグがセット(Z)である場合、すなわち監視対象ステータス前回値と監視対象ステータス今回値が一致するものであれば、「E_CKERR_30」のアドレスに分岐する。一方、ゼロフラグがリセット(NZ)である場合は以下となる。

「LD A,(HL)」は、対象アドレスの内容をロードする命令である。ここでは、当該エラーの監視タイマ値をロードする。

「LD (DE),A」は、対象アドレスの内容にセーブする命令である。ここでは、監視タイマをセーブする。

監視タイマ値判定処理は、監視対象ステータス前回値と監視対象ステータス今回値が一致する場合に呼び出される。

「E_CKERR_30:」は、監視タイマ値判定処理の開始を示すラベルである。

本実施形態では、エラー状態が一定時間以上継続した時点で正式にエラー発生と判定する。エラー解除も同様に、エラー解除状態が一定時間以上継続した時点で正式にエラー解除と判定する。このため、エラーの発生及び解除の判定には、タイマの設定及び減算を行う処理が必要となる。本処理では、タイマの設定及び減算を行うこととする。

「INC HL」は、HLレジスタをインクリメントする命令である。

「LD A,(DE)」は、対象アドレスの内容をロードする命令である。

「JT Z,A,E_CKERR_40」は、ゼロフラグが1であれば分岐する命令である。ここでは、監視タイマがゼロである場合、「E_CKERR_40」へ分岐する。なお、監視タイマの減算は以下の処理で実行している。

「DEC A」は、タイマ値を1減算する命令である。すなわち、上の命令で監視タイマがゼロでない場合、監視タイマから1を減算する。

「LD (DE),A」は、対象アドレスの内容にセーブする命令である。ここでは、監視タイマ値が更新される。

「JT NZ,A,E_CKERR_40」は、ゼロフラグが0であれば分岐する命令である。上記の「DEC A」命令でタイマ値を1減算するが、その結果、監視タイマが0でない場合もやはり、「E_CKERR_40」へ分岐することになる。なお、「E_CKERR_40」の処理は後述する。

一方、監視タイマが1から0になった場合、以下のエラーフラグ判定処理1へ進む。

「INC DE」は、DEレジスタをインクリメントする命令である。

「LD A,(DE)」は、対象アドレスの内容をロードする命令である。

「CP A,C」は、AレジスタとCレジスタを比較する命令である。

「JR Z,E_CKERR_40」は、ゼロフラグが1であれば分岐する命令である。

「LD A,C」は、ステータス今回値をセットする命令である。

「LD (DE),A」は、対象アドレスの内容にセーブする命令である。

「EX DE,HL」は、DEレジスタとHLレジスタを交換する命令である。

このように、監視タイマが1から0になった場合、エラーフラグ判定処理1で改めてエラーフラグ(現在のエラー状態)と監視対象ステータス今回値を比較する。その結果、エラーフラグと監視対象ステータス今回値が一致した場合は、「E_CKERR_40」に分岐する。

一方、エラーフラグと監視対象ステータス今回値が不一致である場合は、エラーフラグに監視対象ステータス今回値をセーブし、以下のサブコマンド設定処理1へ進む。

サブコマンド設定処理1は、エラー発生又は解除と判定した場合、サブコマンドをセットする処理である。ただし、領域外の処理から使用領域のサブコマンドセット処理を呼び出したり、使用領域のサブコマンドバッファを書き換えたりすることは不可であるため、仮のサブコマンドを領域外のRWM(バッファ)に設定する。これにより、設定したサブコマンドを使用領域から参照可能とすることができる。

「LDQ HL,LOW R_ERW_SBC」は、サブコマンド要求カウンタのアドレスをHLレジスタにセットする命令である。

「INC (HL)」は、HLレジスタのサブコマンド要求カウンタを1加算する命令である。

「LD A,(HL)」は、対象アドレスの内容をロードする命令である。ここでは、加算後のHLレジスタのサブコマンド要求カウンタ値をAレジスタにロードする。

「ADDWB HL,A」は、HLレジスタにAレジスタを加算する命令である。

「ADDWB HL,A」は、HLレジスタにAレジスタを加算する命令である。これにより、HLレジスタにカウンタ値を2回加算したことになる。

「LD (HL),@CMD_STS_HED」は、対象アドレスの内容に状態指定先行コマンドをセーブする命令である。ここでは、先行コマンドとして、すべてのエラー発生・解除に共通のコマンド(85H)をセーブする。

「DEC HL」は、HLレジスタをデクリメントする命令である。ここでは、HLレジスタを1減算することにより、後続コマンドのアドレスを指した状態にする。

「LD A,C」は、監視対象ステータス今回値をセットする命令である。

〔ステータス今回値判定処理1〕

「ADD A,A」は、Aレジスタに値を加算する命令である。

「ADD A,(DE)」は、監視対象ステータス今回値にサブコマンドを加算する命令である。すなわち、上記の「LD A,C」命令でセットした監視対象ステータス今回値の2倍を算定して後続コマンド値を加算する。

「LD (HL),A」は、対象アドレスの内容にセーブする命令である。ここで後続コマンドをHLレジスタにセーブする。

なお、監視対象ステータス今回値を2倍する理由は、サブコマンドセット処理(SBCMDST)で要求しているコマンドの形式に合わせるためである。例えば、後続コマンドは00H~7FHのいずれかとなるが、サブコマンドセット処理を呼び出す際にEレジスタに設定する値は、後続コマンドの2倍に加算許可フラグ(0:加算許可、1:加算不許可)を加えたものであるため、監視対象ステータス今回値の2倍を加算する必要がある。

以下のRWM書き換え処理は、エラー発生に伴うRWMの書き換えを行う処理である。

「EX DE,HL」は、DEレジスタとHLレジスタを交換する命令である。

「JT Z,C,E_CKERR_40」は、ゼロフラグが1であれば分岐する命令である。ここでは、エラー発生時であるかエラー解除時であるかを判定し、エラー解除時であれば「E_CKERR_40」へ分岐する。

「LD E,(HL+1)」は、エラー発生時設定対象ラムアドレス下位バイトをロードする命令である。ここでは、エラー発生時に書き換えを行うRWMの下位バイトをロードする。

「JR TZ,E_CKERR_40」は、第2ゼロフラグが1であれば分岐する命令である。ここでは、ロードした値が0である場合、エラー発生時にRWMの書き換えを行わないものとして「E_CKERR_40」へ分岐する。

一方、ロードした値が0でなく、RWMの書き換えを行う場合は以下となる。

「LD A,(HL+2)」は、エラー発生時設定データをロードする命令である。ここでは、書き換えを行うためのデータをロードしている。

「LD (DE),A」は、ロードしたデータを対象アドレスの内容にセーブする命令である。

以下のループ終了処理判定1処理では、次のエラーに係る処理を行うため、テーブルアドレスに3を加算し、ループ終了でなければ「E_CKERR_10」に戻る。

「E_CKERR_40:」は、ループ終了処理判定1処理の開始を示すラベルである。

「ADDWB HL,003H」は、HLレジスタに[003H]を加算する命令である。

〔ループ終了判定1〕

「DJNZ E_CKERR_10」は、ループ継続であれば分岐する命令である。ここでは、上記のようにループ終了でなければ「E_CKERR_10」に戻ることになる。

以下のループ設定処理2からループ終了判定2処理では、入賞異常系のエラーの確認、及びサブコマンドのセットを行う。ここでは、スイッチ異常等の確認を行うループ処理と比較して、「エラー発生のみでエラー解除の判定を行わない」、「タイマを持たず、エラーが発生した場合はただちにサブコマンド等をセットする」という違いがある。

「LD HL,D_ETB_ER2」は、エラー管理処理テーブル2のアドレスをセットする命令である。なお、エラー管理処理テーブル2の内容は後述する。

「LD B,@D_ETB_ER2_NUM」は、状態項目数をセットする命令である。

「E_CKERR_50:」は、エラーフラグ判定処理2の開始を示すラベルである。

「LD A,(R_ERR_FLG)」は、エラーフラグをロードする命令である。

「AND A,(HL)」は、エラーフラグと監視対象ビットデータを論理積する命令である。

「JR Z,E_CKERR_60」は、ゼロフラグが1であれば「E_CKERR_60」に分岐する命令である。

「LD A,01H」は:Aレジスタに[01H]をセットする命令である。

「INC HL」は、HLレジスタをインクリメントする命令である。

「LDIN DE,(HL)」は、エラー発生フラグのアドレスをロードする命令である。

「LD (DE),A」は、対象アドレスの内容にエラー発生フラグをセーブする命令である。

〔ステータス今回値判定処理〕

「JT Z,A,E_CKERR_70」は、ゼロフラグが1であれば「E_CKERR_70」に分岐する命令である。

「EX DE,HL」は、DEレジスタとHLレジスタを交換する命令である。

「LDQ HL,LOW R_ERW_SBC」は、HLレジスタにサブコマンド要求カウンタのアドレスをセットする命令である。

「INC (HL)」は、サブコマンド要求カウンタを1加算する命令である。

「LD A,(HL)」は、対象アドレスの内容をロードする命令である。ここでは、サブコマンド要求カウンタの値をAレジスタにロードする。

「ADDWB HL,A」は、HLレジスタにAレジスタを加算する命令である。

「ADDWB HL,A」は、HLレジスタにAレジスタを加算する命令である(2回目)。

「LD (HL),@CMD_STS_HED」は、対象アドレスの内容に状態指定先行コマンド(@CMD_STS_HED)をセーブする命令である。

「DEC HL」は、HLレジスタをデクリメントする命令である。

「LD A,(DE)」は、対象アドレスの内容をロードする命令である。ここでは、DEレジスタの内容をAレジスタにロードする。

「LD (HL),A」は、対象アドレスの内容にセーブする命令である。ここでは、HLレジスタにAレジスタの内容をセーブする。

「EX DE,HL」は、DEレジスタとHLレジスタを交換する命令である。

「LD E,(HL+1)」は、エラー発生時設定対象ラムアドレス下位バイトをロードする命令である。

「JR TZ,E_CKERR_70」は、第2ゼロフラグが1であれば「E_CKERR_70」に分岐する命令である。

「LD A,(HL+2)」は、エラー発生時設定データをロードする命令である。

「LD (DE),A」は、対象アドレスの内容にセーブする命令である。ここでは、DEレジスタの内容にAレジスタの内容をセーブする。

「ADDWB HL,003H」は、HLレジスタに[003H]を加算する命令である。

「DJNZ E_CKERR_50」は、ループ継続であれば「E_CKERR_50」に分岐する命令である。

以下のエラーフラグ判定処理3では、不正検知1情報出力のためのタイマを設定する。具体的には、入賞異常系のエラーが発生したと判定するか、スイッチ異常、盤面磁気エラー1、盤面磁気エラー2、電波エラーのいずれかが発生したと判定した場合、不正検知1情報ビットタイマに1秒をセーブする。

「ORQ A,(LOW R_ERW_SEF)」は、スイッチエラーフラグとAレジスタを論理和する命令である。

「ORQ A,(LOW R_ERW_M1F)」は、盤面磁気エラー1フラグとAレジスタを論理和する命令である。

「ORQ A,(LOW R_ERW_M2F)」は、盤面磁気エラー2フラグとAレジスタを論理和する命令である。

「ORQ A,(LOW R_ERW_D1F)」は、電波エラー1フラグとAレジスタを論理和する命令である。

「JT Z,A,E_CKERR_80」は、ゼロフラグが1であれば「E_CKERR_80」に分岐する命令である。

「LDQ (LOW R_ERW_I1T),@TMR_HLD_SEC」は、不正検知1情報ビットタイマに不正検知情報1保持時間をセーブする命令である。

「RETEX」は、呼び出し元に復帰する命令である。

図28及び図29は、エラー管理処理テーブル1の構成例を示す図である。

「D_ETB_ER1:」は、エラー管理処理テーブル1の開始アドレスを示すラベルである。

「DW R_IN1_PRT」は、入力ポート1状態フラグのアドレスを示すラベルである。

「DB @IN1_SWE_BIT」は、スイッチ異常信号ビットデータである。

「DW R_ERW_SEO」は、スイッチステータス前回値のアドレスである。

「DB @TMR_CHK_SWI」は、スイッチ異常監視タイマ値である。

「DB LOW @CMD_ERR_SWI」は、サブコマンド(スイッチエラー指定)である。

「DB 0」は、スイッチエラー指定時のエラー発生時設定対象ラムアドレスである。

「DB 0」は、スイッチエラー指定時のエラー発生時設定データである。したがって、スイッチエラー指定の場合、遊技は停止されない。

「DB @IN1_DRE_BIT」は、扉開放スイッチ信号ビットデータである。

「DW R_ERW_DEO」は、扉開放ステータス前回値のアドレスである。

「DB @TMR_CHK_DOR」は、扉監視タイマ値である。

「DB LOW @CMD_ERR_BDR」は、サブコマンド(扉開放エラー指定)である。

「DB 0」は、扉開放エラー指定時のエラー発生時設定対象ラムアドレスである。

「DB 0」は、扉開放エラー指定時のエラー発生時設定データである。したがって、扉開放エラー指定の場合、遊技は停止されない。

「DB @IN1_M1E_BIT」は、盤面磁気検出センサ1信号ビットデータである。

「DW R_ERW_M1O」は、盤面磁気検出センサ1ステータス前回値のアドレスである。

「DB @TMR_CHK_MAG」は、磁気監視タイマ値である。

「DB LOW @CMD_ERR_MG2」は、サブコマンド(盤面磁気エラー2指定)である。

「DB LOW R_ERW_YER」は、盤面磁気エラー2指定時のエラー発生時設定対象ラムアドレスである。

「DB @YUG_HNF」は、盤面磁気エラー2指定時のエラー発生時設定データである。盤面磁気エラー2指定の場合、遊技が停止される。

「DB @IN1_M2E_BIT」は、盤面磁気検出センサ2信号ビットデータである。

「DW R_ERW_M2O」は、盤面磁気検出センサ2ステータス前回値である。

「DB @TMR_CHK_MAG」は、磁気監視タイマ値である。

「DB LOW @CMD_ERR_MG3」は、サブコマンド(盤面磁気エラー3指定)である。

「DB LOW R_ERW_YER」は、盤面磁気エラー3指定時のエラー発生時設定対象ラムアドレスである。

「DB @YUG_HNF」は、盤面磁気エラー3指定時のエラー発生時設定データである。盤面磁気エラー3指定の場合、遊技が停止される。

「DB @IN0_D1E_BIT」は、電波検出センサ1ビットデータである。

「DW R_ERW_D1O」は、電波検出センサ1ステータス前回値である。

「DB @TMR_CHK_DEN」は、電波監視タイマ値である。

「DBLOW @CMD_ERR_DE1」は、サブコマンド(電波エラー1指定)である。

「DB 0」は、電波エラー1指定時のエラー発生時設定対象ラムアドレスである。

「DB 0」は、電波エラー1指定時のエラー発生時設定データである。したがって、電波エラー1指定の場合、遊技は停止されない。

図30は、エラー管理処理テーブル2の構成例を示す図である。

「D_ETB_ER2:」は、エラー管理処理テーブル2の開始アドレスを示すラベルである。

「DB @ERF_IL1_BIT」は、不正入賞1エラービットデータである。

「DW R_ERW_FS1」は、不正入賞1エラーフラグである。

「DB LOW @CMD_ERR_FS1」は、サブコマンド(不正入賞エラー1発生指定)である。

「DB LOW R_ERW_YER」は、不正入賞エラー1発生指定時のエラー発生時設定対象ラムアドレスである。

「DB @YUG_HNF」は、不正入賞エラー1発生指定時のエラー発生時設定データである。不正入賞エラー1発生指定の場合、遊技が停止される。

「DW R_ERW_FS3」は、不正入賞3エラーフラグである。

「DB LOW @CMD_ERR_FS3」は、サブコマンド(不正入賞エラー3発生指定)である。

「DB 0」は、不正入賞エラー3発生指定時のエラー発生時設定対象ラムアドレスである。

「DB 0」は、不正入賞エラー3発生指定時のエラー発生時設定データである。したがって、不正入賞エラー3発生指定の場合、遊技は停止されない。

「DW R_ERW_FDN」は、普電異常入賞エラーフラグである。

「DB LOW @CMD_ERR_FDN」は、サブコマンド(普電異常入賞エラー発生指定)である。

「DB 0」は、普電異常入賞エラー発生指定時のエラー発生時設定対象ラムアドレスである。

「DB 0」は、普電異常入賞エラー発生指定時のエラー発生時設定データである。したがって、普電異常入賞エラー発生指定の場合、遊技は停止されない。

ステップS401:主制御基板30は、サブコマンド要求カウンタをクリアする。

ステップS402:主制御基板30は、エラー管理処理テーブル1のアドレスをセットする。

ステップS403:主制御基板30は、状態項目数をセットする。

ステップS404:主制御基板30は、入力ポート状態フラグのアドレスをロードする。

ステップS405:主制御基板30は、対象アドレスの内容をロードする。

ステップS406:主制御基板30は、Cレジスタに0をセットする。

ステップS408:主制御基板30は、対象アドレスの内容と監視対象ビットを論理積する。

ステップS409:主制御基板30は、ゼロフラグが1か否か(異常未発生か?)を確認する。その結果、ゼロフラグが1であることを確認した場合(Yes)、主制御基板30はステップS411を実行する。一方、ゼロフラグが1であることを確認できない場合(No)、主制御基板30はステップS410を実行する。

ステップS411:主制御基板30は、ステータス前回値のアドレスをロードする。

ステップS412:主制御基板30は、対象アドレスの内容をロードする。

ステップS413:主制御基板30は、ロードした内容とCレジスタを比較してゼロフラグを更新する。

ステップS414:主制御基板30は、対象アドレスにCレジスタ(ステータス今回値)をセーブする。

ステップS415:主制御基板30は、DEレジスタをインクリメント(タイマのアドレスをセット)する。

ステップS416:主制御基板30は、HLレジスタをインクリメント(タイマ値のアドレスを指す)する。

ステップS417:主制御基板30は、ゼロフラグが1か否かを確認する。その結果、ゼロフラグが1であることを確認した場合(Yes)、主制御基板30はステップS420を実行する。一方、ゼロフラグが1であることを確認できない場合(No)、主制御基板30はステップS418を実行する。

ステップS418:主制御基板30は、タイマ値をロードする。

ステップS419:主制御基板30は、タイマにタイマ値をセーブする。

ステップS420:主制御基板30は、HLレジスタをインクリメントする。

ステップS421:主制御基板30は、タイマをロードする。

ステップS422:主制御基板30は、タイマの値が0か否かを確認する。その結果、タイマの値が0であることを確認した場合(Yes)、主制御基板30は、外部結合子(4)に移行してステップS446(図34)を実行する。一方、ゼロフラグが1であることを確認できない場合(No)、主制御基板30はステップS423を実行する。

ステップS424:主制御基板30は、減算後のタイマの値が0でないか否かを確認する。その結果、タイマの値が0でないことを確認した場合(Yes)、主制御基板30は、外部結合子(4)に移行してステップS446(図34)を実行する。一方、タイマの値が0でないことを確認できない場合(No)、主制御基板30はステップS425を実行する。

ステップS426:主制御基板30は、エラーフラグをロードする。

ステップS427:主制御基板30は、エラーフラグとステータス今回値が一致するか否かを確認する。その結果、一致することを確認した場合(Yes)、主制御基板30は、外部結合子(4)に移行してステップS446(図34)を実行する。一方、一致を確認できない場合(No)、主制御基板30はステップS428を実行する。

ステップS429:主制御基板30は、DEレジスタとHLレジスタを交換する。

ステップS430:主制御基板30は、HLレジスタにサブコマンド要求カウンタのアドレスをセットする。

ステップS431:主制御基板30は、サブコマンド要求カウンタを1加算する。

ステップS432:主制御基板30は、サブコマンド要求カウンタをロードする。

ステップS433:主制御基板30は、HLレジスタにサブコマンド要求カウンタ値を2回加算する。

ステップS434:主制御基板30は、サブコマンド要求バッファに状態指定先行コマンド(85H)をセーブする。

ステップS435:主制御基板30は、HLレジスタを1減算する。

ステップS436:主制御基板30は、ステータス今回値をセットする。

ステップS437:主制御基板30は、ステータス今回値を2倍する。

ステップS438:主制御基板30は、ステータス今回値の2倍に後続コマンド値を加算する。

ステップS439:主制御基板30は、サブコマンド要求バッファに加算結果をセーブする。

ステップS440:主制御基板30は、DEレジスタとHLレジスタを交換する。

ステップS441:主制御基板30は、ステータス今回値が0か否かを確認する。その結果、ステータス今回値が0であることを確認した場合(Yes)、主制御基板30はステップS446を実行する。一方、ステータス今回値が0であることを確認できない場合(No)、主制御基板30は、ステップS442を実行する。

ステップS442:主制御基板30は、エラー発生時設定対象ラムアドレス下位バイトをロードする。

ステップS443:主制御基板30は、ロードした値が0か否かを確認する。その結果、ロードした値が0であることを確認した場合(Yes)、主制御基板30はステップS446を実行する。一方、ロードした値が0であることを確認できない場合(No)、主制御基板30は、ステップS444を実行する。

ステップS445:主制御基板30は、対象ラムアドレスにセーブする。

ステップS446:主制御基板30は、HLレジスタに3を加算する。

ステップS447:主制御基板30は、ループ継続か否かを確認する。その結果、ループ継続であることを確認した場合(Yes)、主制御基板30は、外部結合子(1)に移行してステップS404(図31)を実行する。一方、ループ継続であることを確認できない場合(No)、主制御基板30は、外部結合子(6)に移行してステップS448(図35)を実行する。

ステップS448:主制御基板30は、エラー管理処理テーブル2のアドレスをセットする。

ステップS449:主制御基板30は、状態項目数をセットする。

ステップS450:主制御基板30は、エラーフラグをロードする。

ステップS451:主制御基板30は、エラーフラグと監視対象ビットを論理積する。

ステップS452:主制御基板30は、ゼロフラグが1か否か(異常未発生か?)を確認する。その結果、ゼロフラグが1であることを確認した場合(Yes)、主制御基板30はステップS454を実行する。一方、ゼロフラグが1であることを確認できない場合(No)、主制御基板30は、ステップS453を実行する。

ステップS454:主制御基板30は、HLレジスタをインクリメント(エラー発生フラグのアドレスを指す)する。

ステップS455:主制御基板30は、エラー発生フラグのアドレスをロードする。

ステップS456:主制御基板30は、エラー発生フラグにAレジスタをセーブする。

ステップS457:主制御基板30は、ゼロフラグが1か否か(異常未発生か?)を確認する。その結果、ゼロフラグが1であることを確認した場合(Yes)、主制御基板30は外部結合子(9)に移行してステップS472(図36)を実行する。一方、ゼロフラグが1であることを確認できない場合(No)、主制御基板30は、ステップS458を実行する。

ステップS459:主制御基板30は、HLレジスタにサブコマンド要求カウンタのアドレスをセットする。

ステップS460:主制御基板30は、サブコマンド要求カウンタを1加算する。

ステップS461:主制御基板30は、サブコマンド要求カウンタをロードする。

ステップS462:主制御基板30は、HLレジスタにサブコマンド要求カウンタ値を2回加算する。

ステップS463:主制御基板30は、サブコマンド要求バッファに状態指定先行コマンド(85H)をセーブする。

ステップS464:主制御基板30は、HLレジスタを1減算する。

ステップS465:主制御基板30は、後続コマンドをロードする。

ステップS466:主制御基板30は、サブコマンド要求バッファに後続コマンドをセーブする。

ステップS467:主制御基板30は、DEレジスタとHLレジスタを交換する。

ステップS468:主制御基板30は、エラー発生時設定対象ラムアドレス下位バイトをロードする。

ステップS469:主制御基板30は、ロードした値が0か否かを確認する。その結果、値が0であることを確認した場合(Yes)、主制御基板30はステップS472を実行する。一方、値が0であることを確認できない場合(No)、主制御基板30は、ステップS470を実行する。

ステップS471:主制御基板30は、ロードした内容を対象ラムアドレスにセーブする。

ステップS472:主制御基板30は、HLレジスタに3を加算する。

ステップS473:主制御基板30は、ループ継続か否かを確認する。その結果、ループ継続であることを確認した場合(Yes)、主制御基板30は、外部結合子(8)に移行してステップS450(図35)を実行する。一方、ループ継続であることを確認できない場合(No)、主制御基板30は、外部結合子(10)に移行してステップS474(図37)を実行する。

ステップS474:主制御基板30は、エラーフラグをロードする。

ステップS475:主制御基板30は、ロードしたエラーフラグをスイッチエラーフラグと論理和する。

ステップS476:主制御基板30は、ロードしたエラーフラグを盤面磁気1エラーフラグと論理和する。

ステップS477:主制御基板30は、ロードしたエラーフラグを盤面磁気2エラーフラグと論理和する。

ステップS478:主制御基板30は、ロードしたエラーフラグを電波エラーフラグと論理和する。

ステップS480:主制御基板30は、不正検知1情報ビットタイマにタイマ値をセットする。

以上の手順を終了すると、主制御基板30は呼び出し元に戻る。

以上のような状態管理処理及びエラー確認処理のプログラム構成によれば、使用領域及びデータ領域のコード量の増大を抑えることができる。

次に、本実施形態の第4の技術的特徴について説明する。第4の技術的特徴は、変動パターン選択2処理にけるコード使用量の増大を抑える構成である。

変動パターン選択2処理は、特別図柄の変動パターンを決定する処理において呼び出されるモジュールであり、遊技の進行(実行)に関する内容を制御するため、使用領域にプログラムを配置する必要がある。先ず、変動パターン決定処理の概要を説明する。

図38は、変動パターン決定処理の手順例を示すフローチャートである。このフローチャートは、主制御基板30(主制御CPU31)により実行される。

ステップS600:主制御基板30は、状態別及び停止図柄別テーブルアドレスをセットする。ここでセットされるテーブルアドレスは、以後の手順において最終的に変動パターンを決定(乱数抽選により選択)するための基礎となるテーブルマスタの場所を指定するためのものである。本実施形態では、はずれ時又は大当り時のいずれについても処理が共通となっているが、変動パターンの決定に用いるテーブルの場所(テーブルアドレス)については、現在の遊技状態別及び停止図柄別のものがROMに記憶したテーブルで規定されている。

ステップS604:主制御基板30は、第1段階変動グループ決定処理(変動パターン選択1処理)を実行する。この処理は、上記のように変動グループ決定乱数を用いて変動パターンの第1カテゴリ抽選(変動グループの抽選)を行い、取得した変動グループ指定オフセット値を戻り値としてセットするものである。

ステップS608:主制御基板30は、第2段階変動モード決定処理(本実施形態の変動パターン選択2処理)を実行する。この処理は、上記のように変動モード決定乱数を用いて変動パターンの第2カテゴリ抽選(変動モードの抽選)を行い、取得した変動モード指定オフセット(パターン選択オフセット)値を戻り値としてセットするものである。ここで取得した変動モード指定オフセット(パターン選択オフセット)は、最終第3段階の変動パターン決定処理で用いられる変動パターン選択テーブルのアドレスを指定するものとなる。なお、具体的な処理の内容については、比較例との対比とともに後述する。

ステップS611:主制御基板30は、第3段階変動パターン決定処理を実行する。この処理では、主制御基板30は変動パターン決定乱数に基づき、上記の「第3段階選択用テーブル(変動モード別変動パターン選択テーブル)」から対応する変動パターン番号を選択する。また主制御基板30は、選択した変動パターン番号を戻り値にセットする。ここで選択した変動パターン番号は、最終的に当該変動で行われる一意の変動パターン(変動開始から予告の発生、テンパイまでの時間、リーチ態様、リーチ変動時間、最終停止表示に至るまでの変動態様)を表すものであり、この変動パターン番号から当該変動におけるトータルの変動時間(変動秒数)が一意に定まることになる。

上記のように、変動パターン選択2処理において使用領域のプログラム使用量(コード量)の増大を抑えたい。

一般に、データテーブル構成においてデータAとデータBがペアになっており、データAの範囲が0~10、データBの範囲が0~4000であるとする場合を考える。この場合、普通にデータAとデータBをテーブルに記載した場合、データAの記載に1バイト、データBの記載に2バイト、合計3バイトが必要となる。

ここで、データA×4096+データBで構成した別の「データC」を考えた場合、データCの範囲は0~53960であるため、この構成であれば、2バイトのデータとして記載できる。

比較例では、モード番号データと比較値データの組をテーブルデータから先ず16ビットのデータとして読み込み、上位4ビットを0にすることで、比較値データを生成する。そして、比較値データと乱数値を比較し、条件を満たした場合、再度テーブルからデータを読み込み、今度は上位4ビットを有効にするという処理を行う。

〔モード選択テーブルアドレス選択処理〕

(2)「LDF HL,D_MOD_SEL」は、モード選択テーブルのアドレスをセットする命令である。ここでのコード量は2バイトである。

(1)「RST WORDSEL」は、ワードデータ選択処理を呼び出す処理である。ここでのコード量は1バイトである。

〔比較値取得処理〕

(2)「LDIN AE,(HL)」は、比較値及びモード番号データをロードしてテーブルアドレスを2加算する命令である。ここでのコード量は2バイトである。

(2)「AND A,00FH」は、Aレジスタを[00FH]と論理積する命令である。ここでのコード量は2バイトである。

(1)「LD D,A」は、Dレジスタに抽出値(Aレジスタ)をセットする命令である。ここでのコード量は1バイトである。

(2)「CP BC,DE」は、BCレジスタの乱数値とDEレジスタの比較値を比較する命令である。ここでのコード量は2バイトである。

(2)「JR C,HPT_MOD_20」は、キャリーフラグが1であれば「HPT_MOD_20」に分岐する命令である。ここでのコード量は2バイトである。

(1)「INC HL」は、HLレジスタで示すテーブルアドレスを1加算して次のデータブロックへ更新する命令である。ここでのコード量は1バイトである。

(2)「JR HPT_MOD_10」は、「HPT_MOD_10」にジャンプする命令である。ここでのコード量は2バイトである。

〔パターン選択オフセット設定処理〕

(1)「LD B,(HL)」は、HLレジスタで示す対象アドレスの内容をBレジスタにロードする命令である。ここでのコード量は1バイトである。

〔モード番号データ設定処理〕

(1)「DEC HL」は、HLレジスタのテーブルアドレスを1減算する命令である。ここでのコード量は1バイトである。

(1)「LD A,(HL)」は、HLレジスタで示す対象アドレスの内容をロードする命令である。ここでのコード量は1バイトである。

(3)「SRL A,4」は、Aレジスタを4ビット右シフトしてモード番号データを算出する命令である。ここでのコード量は3バイトである。

(1)「RET」は、呼び出し元に復帰する命令である。ここでのコード量は1バイトである。

ステップS701:主制御基板は、ワードデータ選択処理を呼び出す処理を実行する。

ステップS702:主制御基板は、比較値及びモード番号データをロードし、HLレジスタを2加算する。

ステップS703:主制御基板は、Aレジスタと[0FH]を論理積し、比較値の上位4ビットを抽出する。

ステップS704:主制御基板は、DレジスタにAレジスタをセットする。

ステップS705:主制御基板は、乱数値(BCレジスタ)と比較値(DEレジスタ)を比較する。

ステップS706:主制御基板は、キャリーフラグが1か否か(乱数値が比較値未満か?)を確認する。その結果、キャリーフラグが1であることを確認した場合(Yes)、主制御基板はステップS708を実行する。一方、キャリーフラグが1であることを確認できない場合(No)、主制御基板は、ステップS707を実行する。

ステップS707:主制御基板は、HLレジスタを1加算してステップS702を実行する。

ステップS709:主制御基板は、HLレジスタを1減算する。

ステップS710:主制御基板は、比較値及びモード番号の上位バイトデータをロードする。

ステップS711:主制御基板は、Aレジスタの内容を4ビット右シフトし、モード番号を抽出する。

以上の手順を終了すると、主制御基板は呼び出し元に戻る。

次に、本実施形態の変動パターン選択2処理の構成について説明する。

本実施形態においても、比較例と同様に、変動パターン選択2処理を呼び出すにあたり、Aレジスタにモード選択オフセット、BCレジスタに乱数値をセットしておくこととする。そして本実施形態では、Aレジスタにモード番号データ、Bレジスタにパターン選択オフセットがセットされることとなる。本実施形態の変動パターン選択2処理で使用するコード量は16バイトである。

〔モード選択テーブルアドレス選択処理〕

(2)「LDF HL,D_MOD_SEL」は、モード選択テーブルのアドレスをセットする命令である。ここでのコード量は2バイトである。

(1)「RST WORDSEL」は、ワードデータ選択処理を呼び出す処理である。ここでのコード量は1バイトである。

〔比較値取得処理〕

(2)「LDIN AE,(HL)」は、比較値及びモード番号データをロードしてテーブルアドレスを2加算する命令である。ここでは、テーブルから比較値及びモード番号をAEレジスタにロードしつつ、テーブルアドレスに2を加算する。この結果、Aレジスタの上位4ビットはモード番号、下位4ビットは比較値の上位バイト、Eレジスタは比較値の下位バイトが設定される。ここでのコード量は2バイトである。

(1)「INC HL」は、HLレジスタをインクリメントする命令である。テーブルアドレスはパターン選択オフセットを指し示しているため、ここではHLレジスタが示すテーブルアドレスに1を加算し、次の比較値及びモード番号を指し示す状態にする。ここでのコード量は1バイトである。

(3)「DIV D,A,16」は、モード番号を算定する命令である。「DIV D,A,16」命令は、「モード番号と比較値の分離」及び「モード番号の右シフト」を単一の命令で実行するものである。すなわち、ここではAレジスタを16で除算し、Aレジスタに商(モード番号データ)、Dレジスタに余り(比較値の上位バイト)を設定する処理である。この結果、DEレジスタには乱数との比較値が設定(比較値データが生成)される。ここでのコード量は3バイトである。

(2)「CP BC,DE」は、BCレジスタの乱数値とDEレジスタの比較値の内容を比較する命令である。ここでは、乱数値(BCレジスタ)と比較値(DEレジスタ)を比較し、キャリーフラグをセットする。例えば、DEレジスタの値が3368である場合、BCレジスタの値が0~3367であればキャリーフラグがセット(C)され、3368以上であればキャリーフラグがリセット(NC)される。ここでのコード量は2バイトである。

(2)「JR NC,HPT_MOD_10」は、キャリーフラグが0であれば「HPT_MOD_10」に分岐する命令である。ここでは、上で設定したキャリーフラグを確認し、リセット(NC)であれば、「HPT_MOD_10」に戻る。HLレジスタは次の比較値及びモード番号を指しているため、戻った先のLDIN命令で次の値をロードすることができる。ここでのコード量は2バイトである。

(1)「DEC HL」は、HLレジスタをデクリメントする命令である。すなわち、上記の「INC HL」命令で進めたテーブルアドレスを1減算し、再びパターン選択オフセットを指す状態とする。ここでのコード量は1バイトである。

(1)「LD B,(HL)」は、対象アドレスの内容をロードする命令である。ここでは、Bレジスタをパターン選択オフセットで上書きする。ここでのコード量は1バイトである。

(1)「RET」は、呼び出し元に復帰する命令である。ここでのコード量は1バイトである。

モード番号データは、モード番号データ設定処理でAレジスタに設定された状態を保持しており、比較例のように再びテーブルから値を読み出して加工する必要はない。

モード選択テーブルアドレス選択処理では、呼び出し時に設定されたモード選択オフセット(Aレジスタ)に応じて、比較値、モード番号データ及びパターン選択オフセットが記載されたテーブルのアドレスをHLレジスタに設定する。図41中(B)がテーブル構成例である。

「D_MOD_SEL_07:」は、テーブルの先頭を示すラベルである。

「DW 3368 + 1000H * 004H」は、比較値とモード番号データの合成値である。

「DB @D_PAT_SEL_10 」は、パターン選択10オフセットである。

「DW 3868 + 1000H * 005H」は、比較値とモード番号データの合成値である。

「DB @D_PAT_SEL_11」は、パターン選択11オフセットである。

「DW @STP + 1000H * 006H」は、比較値とモード番号データの合成値である。

「DB @D_PAT_SEL_12」は、パターン選択12オフセットである。

図42は、テーブル「D_MOD_SEL_07」を使用した振り分けを示す図である。すなわち、図41中(B)のテーブルを選択した場合、BCレジスタに設定された乱数値に応じて以下の振り分けを行うことになる。なお、処理の呼び出し時に設定される乱数は、0~4092までの4093通りであるとする。

取得した乱数値が0~3367の場合、モード番号データは04Hとなり、パターン選択オフセットは「10(@D_PAT_SEL_10)」となる。

取得した乱数値が3368~3867の場合、モード番号データは05Hとなり、パターン選択オフセットは「11(@D_PAT_SEL_11)」となる。

取得した乱数値が3868以上の場合、モード番号データは06Hとなり、パターン選択オフセットは「12(@D_PAT_SEL_12)」となる。

ステップS800:主制御基板30は、HLレジスタにモード選択テーブルのアドレスをセットする。

ステップS801:主制御基板30は、ワードデータ選択処理を呼び出す処理を実行する。

ステップS802:主制御基板30は、比較値及びモード番号データをロードし、HLレジスタを2加算する。

ステップS803:主制御基板30は、HLレジスタを1加算する。

ステップS804:主制御基板30は、Aレジスタを16で除算し、商(モード番号データ)をAレジスタ、余り(比較値)をDレジスタにセットする。

ステップS805:主制御基板30は、乱数値(BCレジスタ)と比較値(DEレジスタ)を比較する。

ステップS806:主制御基板30は、キャリーフラグが0であるか否か(乱数値が比較値以上か?)を確認する。その結果、キャリーフラグが0であることを確認した場合(Yes)、主制御基板30は、ステップS802を実行する。一方、キャリーフラグが0であることを確認できない場合(No)、主制御基板30は、ステップS807を実行する。

ステップS808:主制御基板30は、Bレジスタにパターン選択オフセットをロードする。

以上の手順を終了すると、主制御基板30は、呼び出し元に戻る。

以上のように、本実施形態では、変動パターン選択2処理のプログラムコード量を比較例の場合よりも6バイト削減することができる。したがって、プログラム容量の増大を抑えることができる。

次に、本実施形態の第5の技術的特徴について説明する。第5の技術的特徴は、管理遊技機100の性能を算出する処理を実行するタイミングに関する構成である。

管理遊技機100の性能として、ベース値、役物比率及び連続役物比率がある。これらの性能値を算出する処理は、タイマ割込み処理中の性能表示モニタ制御処理(E_SHYMT)で実行する。このとき、ベース、役物比率及び連続役物比率の算定時間が長くなることを抑えたい。

タイマ割込み処理を終了させる必要がある時間が限られるため、1回のタイマ割込み処理の中では、ベース値、役物比率及び連続役物比率をそれぞれ算定する処理について、2つ以上の処理を実行しない構成とする。なお、ベース値、役物比率及び連続役物比率は、それぞれ以下の条件を満たした場合に算定することとする。

ア 区間内の総アウト数が299(初回のみ)又は60000個に達した場合

イ 「現在のベース値」の表示開始タイミング

ウ 前回のタイマ割込みでベース値を算定した場合

エ 「未定の賞球」を「連続役物賞球カウンタ」に加算した場合

オ 今回のタイマ割込みで賞球が発生した場合

カ 前回のタイマ割込みで役物比率を算定した場合

図44から図46は、性能表示モニタ表示処理の手順例を示すフローチャートである。性能モニタ表示処理は、タイマ割込み処理の中で呼び出し実行されるモジュール(図13のステップS319)である。本実施形態の第5の技術的特徴となる構成は、性能モニタ表示処理の中に組み込まれているので、以下、性能モニタ表示処理について説明する。性能モニタ表示処理は、主制御基板30(主制御CPU31)が実行する。

ステップS901:主制御基板30は、今回アウト数の算定処理を実行する。

ステップS902:主制御基板30は、役物作動確認処理を実行する。

ステップS903:主制御基板30は、今回賞球数の算定処理を実行する。

ステップS904:主制御基板30は、総賞球カウンタ更新処理を実行する。

ステップS905:主制御基板30は、役物賞球カウンタ更新処理を実行する。

ステップS906:主制御基板30は、未定賞球カウンタ更新処理を実行する。

ステップS907:主制御基板30は、大当り中又は小当り中であるか否かを確認する。その結果、大当り中又は小当り中であることを確認した場合(Yes)、主制御基板30は、ステップS908を実行する。一方、大当り中又は小当り中であることを確認できない場合(No)、主制御基板30は、ステップS911を実行する。

ステップS910:主制御基板30は、連続役物賞球カウンタに未定賞球カウンタを加算する。

ステップS911:主制御基板30は、未定賞球カウンタをクリアする。

ステップS912:主制御基板30は、通常遊技時であるか否かを確認する。その結果、通常遊技時であることを確認した場合(Yes)、主制御基板30は、ステップS913を実行する。一方、通常遊技時であることを確認できない場合(No)、主制御基板30は、ステップS915を実行する。

ステップS914:主制御基板30は、通常アウトカウンタ更新処理を実行する。

ステップS915:主制御基板30は、総アウトカウンタ更新処理を実行する。

ステップS916:主制御基板30は、総アウトカウンタが比較値以上であるか否かを確認する。比較値は、299個(初回のみ)又は60000個である。その結果、総アウトカウンタが比較値以上であることを確認した場合(Yes)、主制御基板30は、ステップS919を実行する。一方、総アウトカウンタが比較値以上であることを確認できない場合(No)、主制御基板30は、ステップS917を実行する。

ステップS918:主制御基板30は、ベース値(現在)の表示開始タイミングか否かを確認する。なお、管理遊技機100の性能表示モニタ37には、「現在のベース値」、「前回区間のベース値」、「前々回区間のベース値」及び「3回前区間のベース値」を約5秒ごとに切り替えて表示する。このとき、「3回目区間のベース値」から「現在のベース値」に表示を切り替えるタイミングが表示開始タイミングとなるので、その確認を行う。その結果、現在のベース値の表示開始タイミングであることを確認した場合(Yes)、主制御基板30は、ステップS919を実行する。一方、表示開始タイミングであることを確認できない場合(No)、主制御基板30は、外部結合子(3)に移行してステップS922(図46)を実行する。

ステップS920:主制御基板30は、ベース値の更新処理を実行する。

ステップS921:主制御基板30は、算定管理バッファに「次回役物比率算定指定値」をセーブする。

ステップS922:主制御基板30は、今回賞球数が0以外であるか否かを確認する。その結果、今回賞球数が0以外であること確認した場合(Yes)、主制御基板30は、ステップS926を実行する。一方、今回賞球数が0以外であることを確認できない場合(No)、主制御基板30は、ステップS923を実行する。

ステップS924:主制御基板30は、ロードした算定管理バッファが「次回役物比率算定指定値」であるか否かを確認する。その結果、「次回役物比率算定指定値」であることを確認した場合(Yes)、主制御基板30は、ステップS926を実行する。一方、「次回役物比率算定指定値」であることを確認できない場合(No)、主制御基板30は、ステップS925を実行する。

ステップS927:主制御基板30は、算定管理バッファに「次回連続役物比率算定指定値」をセーブする。

ステップS928:主制御基板30は、連続役物比率算定処理を実行する。

ステップS929:主制御基板30は、算定管理バッファをクリアする。

ステップS930:主制御基板30は、識別セグデータ設定処理を実行する。

ステップS931:主制御基板30は、比率セグデータ設定処理を実行する。

以上の手順を終了すると、主制御基板30は呼び出し元に戻る。

以上のように、性能表示モニタ表示処理において、性能値としてベース値の算定処理(ステップS919)、役物比率算定処理(ステップS926)及び連続役物比率算定処理(ステップS928)があるが、これらの処理は、1回あたりのタイマ割込み処理の中では2つ以上が実行されない。

図47は、未定賞球カウンタ加算処理(図44のステップS906)のプログラムを示す図である。本実施形態では、未定賞球カウンタ(R_ERW_MTS)に今回連続役物賞球数(R_ERW_PRN)を加算することとしている。「今回連続役物賞球数」は、今回のタイマ割込み処理の中で、(連続役物作動時の)大入賞口入賞により獲得した賞球数の合計である。

(中略)

〔1〕「LDQ A,(LOW R_ERW_PRN)」は、今回連続役物賞球数をロードする命令である。ここでは、今回連続役物賞球数をロードする。

〔2〕「LDQ HL,(LOW R_ERW_MTS+0)」は、未定賞球カウンタ+0をロードする命令である。ここでは、未定賞球カウンタの下位2バイトをロードする。本実施形態の管理遊技機100は、いわゆる1種2種の遊技を混合した仕様であることから、大入賞口への入賞で得られる賞球は、小当り中であることもあり、賞球数を連続役物比率算定の数に入れるか否かは大当りとなるまで確定しない。そこで本実施形態では、大当り中か否かを問わず、大入賞口への入賞による賞球数は、必ず一度未定の賞球に加算することとしている。

〔3〕「ADDWB HL,A」は、HLレジスタにAレジスタを加算する命令である。ここでは、未定賞球カウンタと今回連続役物賞球数の和を算定する。

〔4〕「LDQ (LOW R_ERW_MTS+0),HL」は、未定賞球カウンタ+0にセーブする命令である。ここでは、算定結果を今回連続役物賞球数の下位2バイトにセーブする。なお、〔3〕においてオーバーフローが発生した場合、キャリーフラグがセットされ、発生していない場合はリセットされている。

〔5〕「LDQ A,(LOW R_ERW_MTS+2)」は、未定賞球カウンタ+2をロードする命令である。ここでは、未定賞球カウンタの上位1バイトをロードする。

〔6〕「ADC A,0」は、未定賞球カウンタの3バイト目にキャリーフラグを加算する命令である。ここでは、「未定賞球カウンタの上位1バイト+0+キャリーフラグ」の和を算定する。すなわち、キャリーフラグがセットであれば、未定賞球カウンタの上位1バイトに1を加算することになる。

〔7〕「LDQ (LOW R_ERW_MTS+2),A」は、未定賞球カウンタ+2にセーブする命令である。ここでは、〔6〕で算定した結果を新たな未定賞球カウンタの上位1バイトとしてセーブする。

本実施形態の性能表示モニタ表示処理では、遊技機の遊技状態及び未定賞球カウンタの値を確認し、連続役物比率対象の賞球への振り替えを行うか否かを決定している。これは、図44のステップS907~ステップS909等で行う内容に相当する。

〔1〕「LD A,(R_TOK_PHS)」は、特別遊技管理フェーズをロードする命令である。

〔2〕「JCP C,A,@SHT_PRE,E_SHYMT_42」は、小当り大入賞口開始ウエイト状態指定値と比較し、キャリーフラグが1であれば分岐する命令である。ここでは、特別遊技管理フェーズの値を確認し、小当りでも大当りでもなければ、「E_SHYMT_42」へ分岐する。

〔3〕「LD A,(R_BIG_FLG)」は、条件装置作動中フラグをロードする命令である。

〔4〕「JCP NZ,A,@TZ__BHT,E_SHYMT_43」は、特別図柄大当り情報と比較し、ゼロフラグが0であれば分岐する命令である。ここでは、条件装置作動中フラグの値を確認し、大当りでなければ「E_SHYMT_43」へ分岐する。

〔5〕「JTQ NZ,(LOW R_ERW_MTS+2),E_SHYMT_41」は、未定賞球カウンタ+2が0以外であれば分岐する命令である。

〔5〕「JTWQ Z,(LOW R_ERW_MTS+0),E_SHYMT_43」は、未定賞球カウンタ+0,+1が0であれば分岐する命令である。

上の2つの〔5〕では、遊技状態が大当り中である場合、未定賞球カウンタの値を確認する。そして、未定賞球カウンタの値が0でない場合は、「E_SHYMT_41」以降の処理を行い、0である場合は「E_SHYMT_43」へ分岐する。

〔6〕「LDQ (LOW R_ERW_TSK),@EXD_TSK_YKH」は、算定管理バッファに次回役物比率算定指定値をセーブする命令である。ここでは、算定管理バッファに「次回役物比率算定指定値」をセーブする。

なお、ここで「次回連続役物比率算定指定値」ではなく、「次回役物比率算定指定値」をセーブしている理由は、このとき算定管理バッファには既に「次回役物比率算定指定値」が設定されている場合があることを考慮したものである。

本実施形態の性能表示モニタ表示処理では、未定賞球カウンタの賞球を連続役物賞球カウンタへ移し替える処理(図44のステップS905,ステップS910,ステップS911等)を行っている。以下、これらを連続役物賞球カウンタ等更新処理として説明する。

〔連続役物賞球カウンタ更新処理〕

〔1〕「LDQ HL,(LOW R_ERW_RYS+0)」は、連続役物賞球カウンタ+0をロードする命令である。

〔2〕「LDQ DE,(LOW R_ERW_MTS+0)」は、未定賞球カウンタ+0をロードする命令である。上記〔1〕と〔2〕では、連続役物賞球カウンタ及び未定賞球カウンタの下位2バイトをロードする。

〔3〕「ADD HL,DE」は、連続役物賞球カウンタに未定賞球カウンタを加算する命令である。

〔4〕「LDQ (LOW R_ERW_RYS+0),HL」は、連続役物賞球カウンタ+0にセーブする命令である。上記〔3〕で和を求め、〔4〕で連続役物賞球カウンタの下位2バイトをセーブする。

〔5〕「LDQ A,(LOW R_ERW_RYS+2)」は、連続役物賞球カウンタ+2をロードする命令である。

〔6〕「LDQ HL,LOW R_ERW_MTS+2」は、未定賞球カウンタ+2のアドレスをセットする命令である。上記〔5〕では連続役物賞球カウンタの上位1バイトをロードし、〔6〕では未定賞球カウンタの上位1バイトのアドレスをセットする。

〔7〕「ADC A,(HL)」は、連続役物賞球カウンタの3バイト目に未定賞球カウンタの3バイト目及びキャリーフラグを加算する命令である。

〔8〕「LDQ (LOW R_ERW_RYS+2),A」は、連続役物賞球カウンタ+2にセーブする命令である。上記〔7〕では連続役物賞球カウンタの上位1バイトと、未定賞球カウンタの上位1バイト及びキャリーフラグの和を算定し、〔8〕ではその結果をセーブする。

〔未定賞球カウンタクリア処理〕

〔9〕「CLRWQ (LOW R_ERW_MTS+0)」は、未定賞球カウンタ+0をクリアする命令である。

〔10〕「CLRQ (LOW R_ERW_MTS+2)」は、未定賞球カウンタ+2をクリアする命令である。上記〔9〕及び〔10〕では未定賞球カウンタのクリアを行う。このクリアは、遊技状態が大当り及び小当りのどちらでもない場合にも行われる。

本実施形態の性能表示モニタ制御処理では、ベース値の算定を行った場合、算定管理バッファに次回役物比率算定指定値をセーブする処理(図46のステップS926,ステップS927)を行っている。以下、これをベース値算定後の算定管理バッファ設定処理として説明する。

〔算定管理バッファ更新処理1〕

「E_SHYMT_57:」は、算定管理バッファ更新処理1の開始を示すラベルである。

「LDQ (LOW R_ERW_TSK),@EXD_TSK_YKH」は、算定管理バッファに次回役比算定指定値をセーブする命令である。

「JP E_SHYMT_90」は、「E_SHYMT_90」へジャンプする命令である。

本実施形態の性能表示モニタ制御処理においてベース値の算定を行わなかった場合、算定管理バッファ(R_ERW_TSK)を確認し、処理の振り分けを行っている(図46のステップS922,ステップSS923,ステップS924,ステップS925,ステップS926等)。具体的には、役物比率の算定を行う場合は、「E_SHYMT_70」へ分岐し、連続役物比率の算定を行う場合は、「E_SHYMT_80」へ分岐する。いずれも行わない場合は、「E_SHYMT_90」へ分岐する。以下、この処理を算定管理バッファに基づく処理の振り分けとして説明する。

「E_SHYMT_60:」は、処理の開始を示すラベルである。

〔ベースを算定しない場合は役物比率算定、連続役物比率算定を行うかを確認する〕

〔1〕「JTQ NZ,(LOW R_ERW_PAY),E_SHYMT_70」は、今回賞球数が0以外であれば分岐する命令である。ここでは、今回賞球数(R_ERW_PAY)が0でない場合にE_SHYMT_70へ分岐する。

〔2〕「LDQ A,(LOW R_ERW_TSK)」は、算定管理バッファをロードする命令である。

〔2〕「JCP Z,A,@EXD_TSK_YKH,E_SHYMT_70」は、次回役物比率算定指定値と比較し、ゼロフラグが1であれば分岐する命令である。

上の2つの〔2〕では、算定管理バッファが次回役比算定指定値(@EXD_TSK_YKH(1))である場合に「E_SHYMT_70」へ分岐する。

〔3〕「CP A,@EXD_TSK_RYH」は、次回連続役物比率算定指定値と比較する命令である。ここでは、算定管理バッファと次回連役算定指定値(@EXD_TSK_RYH(2))を比較する。

〔4〕「JP Z,E_SHYMT_80」は、ゼロフラグが1であれば分岐する命令である。ここでは、上記〔3〕で一致した場合は「E_SHYMT_80」へ分岐する。

「JP E_SHYMT_90」は、「E_SHYMT_90」へ分岐する命令である。上記〔3〕で一致しなかった場合、ここで「E_SHYMT_90」へ分岐する。

図52は、役物比率算定後の算定管理バッファ設定処理のプログラムを示す図である。この処理では、役物比率の算定を行った場合、算定管理バッファに次回連続役物比率算定指定値をセーブする。

「E_SHYMT_72:」は、処理の開始を示すラベルである。

「LDQ (LOW R_ERW_YAK),A」は、役物比率バッファにセーブする命令である。

「LDQ (LOW R_ERW_TSK),@EXD_TSK_RYH」は、算定管理バッファに次回連役算定指定値をセーブする命令である。

「JP E_SHYMT_90」は、「E_SHYMT_90」にジャンプする命令である。

図53は、連続役物比率算定後の算定管理バッファ設定処理のプログラムを示す図である。この処理では、役物比率の算定を行った場合、算定管理バッファをクリアする。

「E_SHYMT_82:」は、処理の開始を示すラベルである。

「LDQ (LOW R_ERW_REN),A」は、連続役物比率バッファにセーブする命令である。

「CLRQ (LOW R_ERW_TSK)」は、算定管理バッファをクリアする命令である。

以上のように、タイマ割込み処理中における性能値(ベース値、役物比率及び連続役物比率)の算定時間が長期化することを抑え、かつ、算定の遅れも最小限にすることができる。

以上で本実施形態の有用性は明らかとなっているが、以下にステート数による検証を追加する。

図54及び図55は、ベース値の算定部分のプログラムを示す図である。なお、プログラムコード中、命令の左の数値は、当該命令の実行に必要なステート数(クロック数)を示している。また、数値が2種類記載されている場合、左側が分岐を行う場合のステート数で、右側が分岐を行わない場合のステート数である。

〔除数設定レジスタ更新処理〕

1 「XOR A,A」は、Aレジスタに[00H]をセットする命令である。

5 「LDQ BC,(LOW R_ERW_TJS)」は、通常賞球カウンタをロードする命令である。

4 「LDQ HL,(LOW R_ERW_TJO)」は、通常アウトカウンタをロードする命令である。

3/2 「JR TZ,E_SHYMT_54」は、第2ゼロフラグが1であれば「E_SHYMT_5」に分岐する命令である。

5 「OUT (LOW @DIVB32_+0),HL」は、除数設定レジスタの最下位アドレス+0に出力する命令である。

2 「CLR HL」は、HLレジスタに[0000H]をセットする命令である。

5 「OUT (LOW @DIVB32_+2),HL」は:除数設定レジスタの最下位アドレス+2に出力する命令である。

以下は、通常賞球数の200倍を算定する命令である。

1 「LD A,C」

4 「MUL HL,A,200」

1 「EX DE,HL」

1 「LD A,B」

4 「MUL HL,A,200」

2 「ADDWB HL,D」

1 「LD A,E」

5 「OUT (LOW @DIVA32_+1),HL」は、被除数設定レジスタの最下位アドレス+1に出力する命令である。

4 「OUT (LOW @DIVA32_+3),0」は、被除数設定レジスタの最下位アドレス+3に0を出力する命令である。

2 「LD B,2」は、Bレジスタに2をセットする命令である。

「E_SHYMT_51:」は、処理の開始を示すラベルである。

3/2 「DJNZ E_SHYMT_51」は、ループ継続であれば「E_SHYMT_51:」に分岐する命令である。

〔除算結果確認処理〕

2 「LD A,100」は、Aレジスタに100をセットする命令である。

5 「IN HL,(LOW @DIV32__+2)」は、除算結果レジスタの最下位アドレス+2を入力する命令である。

3/2 「JR NTZ,E_SHYMT_54」は、第2ゼロフラグが0であれば「E_SHYMT_54」に分岐する命令である。

5 「IN HL,(LOW @DIV32__)」は、除算結果レジスタの最下位アドレスを入力する命令である。

4 「CP HL,100*2」は、除算結果の1,2バイト目を確認する命令である。

3/2 「JR NC,E_SHYMT_54」は、キャリーフラグが0であれば「E_SHYMT_54」に分岐する命令である。

1 「LD A,L」は、除算結果をセットする命令である。

2 「SRL A」は、1ビット右シフトして値を算出する命令である。

2 「ADC A,0」は、キャリーフラグを加算してベース算定値を算定する命令である。

〔ベース算定値更新処理〕

2 「LDQ HL,LOW R_ERW_BAS」は、ベース算定値のアドレスをセットする命令である。

2 「LD (HL),A」は、対象アドレスの内容にセーブする命令である。

ベース算定値更新処理では、2+2=4ステートを必要とする。

よって、ベース値を算定し、結果を保存するまでのステート数の合計は、24+26+7+25+4=86ステートである。

役物比率の算定はベース値同様に行うが、結果を保存するまでのステート数の合計は81ステートである。

連続役物比率の算定はベース値同様に行うが、結果を保存するまでのステート数の合計は81ステートである。

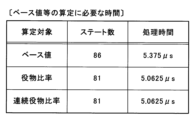

図56は、各種性能値の算定に必要となる時間を示す図である。

主制御CPU31の内部システムクロックが16MHzであるとする。この場合、1ステート=1600万分の1秒となるため、ベース値等の算定に必要な時間は以下の通りとなる。

ベース値算定は、86ステートで5.375μsの処理時間である。

役物比率算定は、81ステートで5.0625μsの処理時間である。

連続役物比率算定は、81ステートで5.0625μsの処理時間である。

したがって、ベース値、役物比率及び連続役物比率をすべて算定した場合、248ステート(15.5μs)が必要となるが、本実施形態のように1回のタイマ割込み処理中で1つしか算定しない場合、最大86ステート(5.375μs)となる。

次に、算出処理時間を抑えるための別案について説明する。

別案では、ベース値算定フラグ、役物比率算定フラグ及び連続役物比率算定フラグを用意し、算定が必要となった場合にフラグをセット、算定を行った場合にフラグをリセットする。複数のフラグがセットされている場合、最も優先度の高いもの1つのみを算定する。この別案においても、本実施形態と同様の有用性が得られるが、若干プログラムが複雑になる。以下、より詳細に説明する。

別案においては、以下のフラグを使用する。

以下のフラグはRWM初期化時にリセットし、電源投入時(電源復帰時)は現状維持とする。

・ ベース値算定フラグ

・ 役物比率算定フラグ

・ 連続役物比率算定フラグ

これらのフラグはそれぞれが別のRWMでもよいし、同一RWM内の別bitでも良い。

以下の条件を満たした場合にそれぞれのフラグをセットする。なお、すでに当該フラグがセットされていた場合、セット状態を継続する。

「ベース値算定フラグ」

以下の場合にベース値算定フラグをセットする。

・ ベース値の表示内容切り替えによって、現在ベース値の表示を開始する場合

・ 総アウト数があらかじめ定められた値(60000個、初回のみ299個)に達した場合

「役物比率算定フラグ」

以下の場合に役物比率算定フラグをセットする。

・ 賞球が発生した場合

「連続役物比率算定フラグ」

以下の場合に連続役物比率算定フラグをセットする。

・ 賞球が発生した場合

・ 未定の賞球を連続役物比率対象の賞球に加算した場合

図57は、別案で算定フラグと実行する処理の対応関係を示す図である。

ベース値算定フラグ等の状態により、タイマ割込み処理内で実行する処理は、図57に示すように決定する。なお、算定を行った場合、対応するフラグはリセットする。

(1)管理遊技機100の場合で説明したが、管理遊技機100の構成を有しない既存のパチンコ機にも適用可能である。

(2)上述したプログラム及びフローチャートはあくまで例示であり、本発明はこれらに限定されるものではない。

この場合、主制御基板が、遊技で消費したメダル枚数情報と、遊技で獲得したメダル枚数情報とをメダル数制御基板に送信し、メダル数制御基板が差枚数を算出する。そして、メダル数制御基板が算出した差枚数情報を主制御基板に送信し、主制御基板は受信した差枚数情報に基づいて遊技停止状態を設定してもよい。

また、主制御基板が、遊技で獲得したメダル枚数情報をメダル数制御基板に送信し、メダル数制御基板が、遊技で獲得したメダル枚数情報と遊技で消費したメダル枚数情報とに基づいて差枚数を算出する。そして、メダル数制御基板が算出した差枚数情報を主制御基板に送信し、主制御基板は受信した差枚数情報に基づいて遊技停止状態を設定してもよい。

20 管理遊技機枠

30 主制御基板

32 入賞口スイッチ

33 アウトスイッチ

34 盤面磁気検出第1センサ

35 盤面磁気検出第2センサ

36 電波検出センサ

37 性能表示モニタ

38 扉開放スイッチ

40 演出制御基板

50 枠制御基板

100 管理遊技機

Claims (1)

- 遊技の実行を制御する遊技制御手段と、

遊技に関する情報を記憶可能な記憶領域を有する記憶手段とを備え、

前記記憶手段は、

前記記憶領域に互いにビット数の異なる第1データ及び第2データが組として設定されるとともに、前記第1データと対応付けた結果データが設定されたテーブル領域を有し、

前記遊技制御手段は、

前記テーブル領域から第1レジスタと第2レジスタのペアに前記第1データと前記第2データの組を読み込んだ後、前記第1レジスタの値を所定値で除算したときの商を前記第1レジスタに格納し、その余りを第3レジスタに格納する命令を実行することで、前記第3レジスタと前記第2レジスタのペアによって前記第2データを生成し、取得した乱数値と生成した前記第2データとを比較した結果に基づいて、前記第2データと組になる前記第1データと対応付けて前記テーブル領域に設定された前記結果データを選択結果として第4レジスタに格納し、前記第1レジスタと前記第4レジスタに格納された2つのデータを用いて、前記第1レジスタに格納した内容と前記第4レジスタに格納した前記選択結果とを返す処理をさらに実行することを特徴とする遊技機。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2022032873A JP7520064B2 (ja) | 2022-03-03 | 2022-03-03 | 遊技機 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2022032873A JP7520064B2 (ja) | 2022-03-03 | 2022-03-03 | 遊技機 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2023128498A JP2023128498A (ja) | 2023-09-14 |

| JP7520064B2 true JP7520064B2 (ja) | 2024-07-22 |

Family

ID=87973017

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022032873A Active JP7520064B2 (ja) | 2022-03-03 | 2022-03-03 | 遊技機 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP7520064B2 (ja) |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003000889A (ja) | 2001-06-22 | 2003-01-07 | Fuji Shoji:Kk | 弾球遊技機 |

| JP2016187615A (ja) | 2016-07-07 | 2016-11-04 | 株式会社大都技研 | 遊技台 |

| JP2021180775A (ja) | 2020-05-19 | 2021-11-25 | サミー株式会社 | 遊技機 |

-

2022

- 2022-03-03 JP JP2022032873A patent/JP7520064B2/ja active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003000889A (ja) | 2001-06-22 | 2003-01-07 | Fuji Shoji:Kk | 弾球遊技機 |

| JP2016187615A (ja) | 2016-07-07 | 2016-11-04 | 株式会社大都技研 | 遊技台 |

| JP2021180775A (ja) | 2020-05-19 | 2021-11-25 | サミー株式会社 | 遊技機 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2023128498A (ja) | 2023-09-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7778011B2 (ja) | 遊技機 | |

| JP7290393B2 (ja) | 遊技機 | |

| JP2023111365A (ja) | 遊技機 | |

| JP6554398B2 (ja) | スロットマシン | |

| JP6554402B2 (ja) | スロットマシン | |

| JP6566735B2 (ja) | 遊技機 | |

| JP2019013346A (ja) | 遊技機 | |

| JP7412031B2 (ja) | 遊技機 | |

| JP2023111342A (ja) | 遊技機 | |

| JP6577256B2 (ja) | スロットマシン | |

| JP6371956B1 (ja) | 遊技機 | |

| JP7499799B2 (ja) | 遊技機 | |

| JP7510451B2 (ja) | 遊技機 | |

| JP2018175502A (ja) | 遊技機 | |

| JP7520064B2 (ja) | 遊技機 | |

| JP7520063B2 (ja) | 遊技機 | |

| JP2023128499A (ja) | 遊技機 | |

| JP7290395B2 (ja) | 遊技機 | |

| JP2018046948A (ja) | スロットマシン | |

| JP2017143881A (ja) | スロットマシン | |

| JP6554399B2 (ja) | スロットマシン | |

| JP6554401B2 (ja) | スロットマシン | |

| JP6554400B2 (ja) | スロットマシン | |

| JP4913363B2 (ja) | 遊技機 | |

| JP7593685B2 (ja) | 遊技機 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230524 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20240220 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240312 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240412 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20240702 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20240709 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7520064 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |