JP7193692B2 - Timing for IC chip - Google Patents

Timing for IC chip Download PDFInfo

- Publication number

- JP7193692B2 JP7193692B2 JP2019522737A JP2019522737A JP7193692B2 JP 7193692 B2 JP7193692 B2 JP 7193692B2 JP 2019522737 A JP2019522737 A JP 2019522737A JP 2019522737 A JP2019522737 A JP 2019522737A JP 7193692 B2 JP7193692 B2 JP 7193692B2

- Authority

- JP

- Japan

- Prior art keywords

- chip

- signal

- radar

- clock

- hardware

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000001360 synchronised effect Effects 0.000 claims description 24

- 230000004044 response Effects 0.000 claims description 14

- 238000001514 detection method Methods 0.000 claims description 10

- 238000012545 processing Methods 0.000 claims description 7

- 238000012360 testing method Methods 0.000 claims description 5

- 230000005540 biological transmission Effects 0.000 claims description 4

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 claims description 3

- 238000010586 diagram Methods 0.000 description 27

- 238000005070 sampling Methods 0.000 description 21

- 230000006870 function Effects 0.000 description 13

- 238000000034 method Methods 0.000 description 8

- 230000003111 delayed effect Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- JPOPEORRMSDUIP-UHFFFAOYSA-N 1,2,4,5-tetrachloro-3-(2,3,5,6-tetrachlorophenyl)benzene Chemical compound ClC1=CC(Cl)=C(Cl)C(C=2C(=C(Cl)C=C(Cl)C=2Cl)Cl)=C1Cl JPOPEORRMSDUIP-UHFFFAOYSA-N 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- 230000000295 complement effect Effects 0.000 description 2

- 230000000977 initiatory effect Effects 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- 101100434411 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) ADH1 gene Proteins 0.000 description 1

- 101150102866 adc1 gene Proteins 0.000 description 1

- 101150042711 adc2 gene Proteins 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 235000019800 disodium phosphate Nutrition 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 230000001960 triggered effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/0635—Clock or time synchronisation in a network

- H04J3/0685—Clock or time synchronisation in a node; Intranode synchronisation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01S—RADIO DIRECTION-FINDING; RADIO NAVIGATION; DETERMINING DISTANCE OR VELOCITY BY USE OF RADIO WAVES; LOCATING OR PRESENCE-DETECTING BY USE OF THE REFLECTION OR RERADIATION OF RADIO WAVES; ANALOGOUS ARRANGEMENTS USING OTHER WAVES

- G01S13/00—Systems using the reflection or reradiation of radio waves, e.g. radar systems; Analogous systems using reflection or reradiation of waves whose nature or wavelength is irrelevant or unspecified

- G01S13/02—Systems using reflection of radio waves, e.g. primary radar systems; Analogous systems

- G01S13/06—Systems determining position data of a target

- G01S13/08—Systems for measuring distance only

- G01S13/32—Systems for measuring distance only using transmission of continuous waves, whether amplitude-, frequency-, or phase-modulated, or unmodulated

- G01S13/34—Systems for measuring distance only using transmission of continuous waves, whether amplitude-, frequency-, or phase-modulated, or unmodulated using transmission of continuous, frequency-modulated waves while heterodyning the received signal, or a signal derived therefrom, with a locally-generated signal related to the contemporaneously transmitted signal

- G01S13/343—Systems for measuring distance only using transmission of continuous waves, whether amplitude-, frequency-, or phase-modulated, or unmodulated using transmission of continuous, frequency-modulated waves while heterodyning the received signal, or a signal derived therefrom, with a locally-generated signal related to the contemporaneously transmitted signal using sawtooth modulation

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01S—RADIO DIRECTION-FINDING; RADIO NAVIGATION; DETERMINING DISTANCE OR VELOCITY BY USE OF RADIO WAVES; LOCATING OR PRESENCE-DETECTING BY USE OF THE REFLECTION OR RERADIATION OF RADIO WAVES; ANALOGOUS ARRANGEMENTS USING OTHER WAVES

- G01S13/00—Systems using the reflection or reradiation of radio waves, e.g. radar systems; Analogous systems using reflection or reradiation of waves whose nature or wavelength is irrelevant or unspecified

- G01S13/87—Combinations of radar systems, e.g. primary radar and secondary radar

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01S—RADIO DIRECTION-FINDING; RADIO NAVIGATION; DETERMINING DISTANCE OR VELOCITY BY USE OF RADIO WAVES; LOCATING OR PRESENCE-DETECTING BY USE OF THE REFLECTION OR RERADIATION OF RADIO WAVES; ANALOGOUS ARRANGEMENTS USING OTHER WAVES

- G01S7/00—Details of systems according to groups G01S13/00, G01S15/00, G01S17/00

- G01S7/02—Details of systems according to groups G01S13/00, G01S15/00, G01S17/00 of systems according to group G01S13/00

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/12—Synchronisation of different clock signals provided by a plurality of clock generators

Landscapes

- Engineering & Computer Science (AREA)

- Radar, Positioning & Navigation (AREA)

- Remote Sensing (AREA)

- Computer Networks & Wireless Communication (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Signal Processing (AREA)

- Probability & Statistics with Applications (AREA)

- General Engineering & Computer Science (AREA)

- Radar Systems Or Details Thereof (AREA)

- Microelectronics & Electronic Packaging (AREA)

Description

本願は、全体的に、集積回路(IC)チップに関し、特に、無線周波数(RF)レシーバのサンプリングを制御するためのタイミングを生成するICチップに関する。 TECHNICAL FIELD This application relates generally to integrated circuit (IC) chips, and more particularly to IC chips that generate timing for controlling sampling in radio frequency (RF) receivers.

クロック信号は、高状態と低状態の間で振動する特定のタイプの信号である。より複雑な配置も用いられるが、最も一般的なクロック信号は、50%デューティーサイクルを有する矩形波の形式であり、通常、固定の一定周波数を有する。同期のためにクロック信号を用いる回路は、立ち上がりエッジ又は立ち下がりエッジ、或いは、ダブルデータレートの場合にクロックサイクルの立ち上がりエッジと立ち下がりエッジの両方、のいずれかにおいてアクティブになり得る。クロック信号は、デジタル回路における構成要素の行為を調整するために用いられる。クロック信号はクロック生成器によって生成される。一例として、レーダーシステムは、トランスミッタ、レシーバ、及び他の構成要素の動作を同期させるために、クロック信号を用いる。 A clock signal is a particular type of signal that oscillates between high and low states. Although more complex arrangements are also used, the most common clock signal is in the form of a square wave with a 50% duty cycle and usually has a fixed constant frequency. Circuitry that uses the clock signal for synchronization can be active either on the rising edge or on the falling edge, or on both the rising and falling edges of the clock cycle in the case of double data rate. Clock signals are used to coordinate the behavior of components in digital circuits. A clock signal is generated by a clock generator. As an example, radar systems use clock signals to synchronize the operation of transmitters, receivers, and other components.

一つの例は、スタートトリガ信号に基づいてフレームパルスを生成するルートタイマを含み得る集積回路(IC)チップに関連する。ICチップはまた、ルートタイマ及び他のICチップの一方から提供されるフレームパルス及び同期信号の選択される1つに基づいてクロック信号を提供するハードウェアクロック制御を含み得る。ICチップは更に、アナログデジタルコンバータ(ADC)を含み得る。ADCの各々は、クロック信号に基づいて、複数の無線周波数(RF)レシーバのそれぞれ1つのRFレシーバの出力をサンプリングするように構成される。 One example relates to an integrated circuit (IC) chip that may contain a root timer that generates a frame pulse based on a start trigger signal. The IC chip may also include a hardware clock control that provides a clock signal based on selected ones of frame pulses and synchronization signals provided from one of the root timer and the other IC chip. The IC chip may also include an analog-to-digital converter (ADC). Each ADC is configured to sample the output of a respective one of a plurality of radio frequency (RF) receivers based on a clock signal.

別の例は、ソフトウェアトリガ信号を生成するマイクロコントローラ、及びソフトウェアトリガ信号を受信し、同期信号を選択してスタートトリガ信号を提供するトリガセレクタを含み得るICチップに関連する。ICチップはまた、スタートトリガ信号に基づいて同期信号を生成するルートタイマを含み得る。同期信号は、ICチップの同期入力ポートに結合されるICチップの同期出力ポートに提供され得る。ICチップは更に、同期入力ポートにおいて受信される同期信号に基づいてクロック信号を提供するハードウェアクロック制御を含み得る。ICチップは更に、各々がクロック信号に基づいて複数のレシーバのそれぞれ1つの出力をサンプリングするように構成されるADCを含む。 Another example relates to an IC chip that may include a microcontroller that generates a software trigger signal and a trigger selector that receives the software trigger signal, selects a synchronization signal, and provides a start trigger signal. The IC chip may also contain a root timer that generates a synchronization signal based on the start trigger signal. A sync signal may be provided to a sync output port of the IC chip coupled to a sync input port of the IC chip. The IC chip may also include a hardware clock control that provides a clock signal based on the synchronization signal received at the synchronization input port. The IC chip further includes ADCs each configured to sample a respective one output of the plurality of receivers based on the clock signal.

更に別の例は、オブジェクトの位置を判定するためにレーダーデータを処理するレーダーコントローラを含み得るレーダーシステムに関連する。レーダーシステムはまた、マスターレーダー集積回路(IC)チップを含み得る。マスターICチップは、所定のインスタンスにおいて、受信されたRF信号をサンプリングするように構成され得る。サンプリングのタイミングは、マスターICチップによって生成される同期信号に基づく。マスターICチップはまた、同期信号に対応するタイミングに基づいてソフトウェア動作を実施し得る。レーダーシステムは更に、1つ又は複数のスレーブICチップを含み得る。1つ又は複数のスレーブICチップの各々は、所定のインスタンスにおいて、受信されたRF信号をサンプリングするように構成され得る。サンプリングのタイミングは、マスターICチップによって生成される同期信号に基づき得る。各スレーブICチップはまた、同期信号に対応するタイミングに基づいてソフトウェア動作を実施するように構成され得る。 Yet another example relates to radar systems that may include radar controllers that process radar data to determine the position of objects. A radar system may also include a master radar integrated circuit (IC) chip. A master IC chip may be configured to sample the received RF signal at predetermined instances. The sampling timing is based on a synchronization signal generated by the master IC chip. The master IC chip may also implement software operations based on timing corresponding to the synchronization signal. A radar system may also include one or more slave IC chips. Each of the one or more slave IC chips may be configured to sample the received RF signal at predetermined instances. The sampling timing may be based on a synchronization signal generated by the master IC chip. Each slave IC chip may also be configured to perform software operations based on timing corresponding to the synchronization signal.

説明される例において、集積回路(IC)チップが、ICチップ内、及び他のICチップ内の種々の構成要素の動作を制御するために、クロック信号を生成し得る。ICチップは、シングルモード、マスターモード、又はスレーブモードで動作するようにプログラム/設定され得る。ICチップは、相対的に高度な同期(例えば、10ナノ秒以内)を必要とする無線周波数(RF)レシーバをサンプリングするアナログデジタルコンバータ(ADC)を含むモジュールを制御するための機能を含む。ICチップはまた、約10マイクロ秒のタイミング内の同期を必要とするソフトウェア機能(例えば、較正及び組み込み自己テスト(BIST))の動作を制御し得る。 In the example described, an integrated circuit (IC) chip may generate clock signals to control the operation of various components within the IC chip and within other IC chips. The IC chip can be programmed/configured to operate in single mode, master mode, or slave mode. The IC chip contains functionality for controlling modules including analog-to-digital converters (ADCs) that sample radio frequency (RF) receivers that require a relatively high degree of synchronization (eg, within 10 nanoseconds). The IC chip may also control the operation of software functions (eg, calibration and built-in self-test (BIST)) that require synchronization within timing of approximately 10 microseconds.

シングルモードにおいて、ICチップは、それ自体のタイミング動作を制御し得る。マスターモードにおいて、ICチップは、スレーブモードで動作する1つ又は複数のICチップに提供される同期信号を生成するために用いられ得る。同期信号は、「ルート」トリガ(例えば、フレームパルス)を生成するために用いられ得、「ルート」トリガは、ICチップ上で動作するモジュール(例えば、ADC)のタイミングを制御するために用いられる1つ又は複数の「リーフ」トリガを生成するために用いられ得る。また、ルートトリガは、ソフトウェア機能の動作を制御するために、処理ユニット(例えば、マイクロコントローラ)によって用いられ得る。このように、同じICレーダーチップ設計が、単一のICチップソリューション又は多数のICチップのソリューションにおいて用いられ得る。本明細書における多くの例において、タイミングは、1つ又は複数のレーダーICチップにおいて実装される構成要素の同等の行為の文脈で説明される。しかしながら、本明細書において説明されるアプローチは、チップ間同期を提供するため等の、他のタイプのICチップに適用可能である。 In single mode, the IC chip can control its own timing operations. In master mode, an IC chip can be used to generate synchronization signals that are provided to one or more IC chips operating in slave mode. The synchronization signal can be used to generate a "root" trigger (e.g. frame pulse), which is used to control the timing of modules (e.g. ADC) operating on the IC chip. It can be used to generate one or more "leaf" triggers. Root triggers can also be used by processing units (eg, microcontrollers) to control the operation of software functions. In this way, the same IC radar chip design can be used in a single IC chip solution or a multiple IC chip solution. In many examples herein, timing is described in the context of equivalent acts of components implemented in one or more radar IC chips. However, the approaches described herein are applicable to other types of IC chips, such as for providing inter-chip synchronization.

図1は、ICチップ2の一例のブロック図を示す。例えば、ICチップ2はレーダーシステムに用いられ得る。そのような状況において、ICチップ2は、衝突回避システム、自動レーンシフトシステム、オートクルーズ制御システム等の、レーダーを用いるオートモーティブ検出システムに用いられ得る。本明細書に説明するように、ICチップ2は、単一のICチップ2ソリューションにおいて実装され得るか、又は、類似の様式で動作する1つ又は複数の付加的なICチップ2と通信状態とされ得る。

FIG. 1 shows a block diagram of an example of an

ICチップ2は、ICチップ2の或る動作を実施するためのモジュールを含み得る。また、ICチップ2のモジュールは、或るレーダー関連の機能を実施するものとして説明されるが、他の例において、異なるモジュールが、本明細書で説明される以外の機能を実施し得る。

ICチップ2はマイクロコントローラユニット(MCU)6を含み得る。MCU6は、非一時的機械可読媒体にストアされる機械可読命令を実行するように構成されるプロセッサコアを含み得る。非一時的機械可読媒体は、MCU6に埋め込まれ得るか、又はMCU6の外にあり得る。幾つかの例において、MCU6は、デジタル信号プロセッサ(DSP)として動作し得る。

ICチップ2は、既知周波数の信号であるシステムクロックを有する。システムクロックは、直接的に、又はチップにおけるデジタルハードウェア回路及びプロセッサによる除算又は積算の後、間接的に用いられ得る。幾つかの例において、システムクロックは、例えばオシレータ又は位相同期ループ等により、ICチップ2内で(例えば、ローカルで)生成され得る。或いは、他の例において、システムクロックは、ICチップ2の入力ピンにおいて、外部ソースから受け取られ得る。

The

ICチップ2は、シングルモード、マスターモード、又はスレーブモードを含み得るような、複数のモードの任意のモードで動作するように設定され得る。ICチップ2は、モード制御信号(図1において、「MODE CONTROL」と示される)によって制御され得るトリガセレクタ8を含み得る。例えば、トリガセレクタ8はマルチプレクサであり得る。また、モード制御信号はローカルで(例えば、MCU6によって)生成され得るか、又は、モード制御信号は外部ソース(例えば、レーダーコントローラ)から提供され得る。更に他の例において、モード制御信号はICチップ2の入力ピンによって制御され得る。

The

ICチップ2がシングルモードで動作している状況において、MCU6は、MCU6上で実行するソフトウェアによって生成され得るソフトウェアトリガをトリガセレクタ8に提供し得る。ソフトウェアトリガはルートタイマ10にパスされ得、ルートタイマ10は、ソフトウェアトリガに応答して、ルートトリガ(例えば、フレームパルス)を生成し得る。そのような状況において、ルートトリガは、ソフトウェアトリガのパススルーバージョン(例えば、遅延、又は非遅延)であり得る。ルートトリガは、ハードウェアクロック制御12に提供され得、MCU6に戻され得る。これに応答して、ハードウェアクロック制御12は、リーフタイマ(ルートタイマ10によって生成されるルートトリガに対してスレーブであるタイマ)を生成し得、リーフタイマは、トランシーバ14及び/又はICチップ2の他の回路又は外部回路の構成要素の動作を制御し得る。ハードウェアクロック制御12は、タイミング信号を生成及び制御し得る離散回路構成要素(例えば、タイマ、デジタル論理ゲート、トランジスタ、及びスイッチ)で形成され得る。

In situations where

トランシーバ14は、M個のトランスミッタ16を含み得、Mは1に等しいかそれより大きい整数である。また、トランシーバ14は、N個のレシーバ18を含み得、Nは1に等しいかそれより大きい整数である。幾つかの例は、トランスミッタ16より多くのレシーバ18(又はその逆)を有する。例えば、トランシーバ14は、3個のトランスミッタ及び4個のレシーバを含み得る。幾つかの例は、等しい数のレシーバ18及びトランスミッタ16を有する。各トランスミッタ16は、周波数帯域における特定の周波数で無線周波数(RF)信号を放射し得る送信アンテナに結合され得る。また、各レシーバ18は、周波数帯域内のRF信号を検出し得る受信アンテナに結合され得る。幾つかの例において、M個のトランスミッタ16及びN個のレシーバ18の周波数帯域は、約80ギガヘルツ(GHz)から約81GHzの範囲であり得る。他の例において、約76GHzの周波数等の異なる周波数が用いられ得る。

トランシーバ14は、トランスミッタ16によって送信される信号の生成を促進するためのローカルオシレータ(LO)22等の構成要素を含み得る。トランシーバ14はまた、それぞれ(マッチングされる)レシーバ18に結合されるN個のアナログデジタルコンバータ(ADC)を含み得る。各ADC20は、対応するレシーバ18によって受信される信号をサンプリングするように構成され得る。言い換えると、第2のADC20(図2において「ADC2」と示される)は、第2のレシーバ18(図1において「RX2」と示される)によって検出されるRF信号をサンプリングするように構成され得る。各ADC20は、所定のクロックレートで、それぞれのレシーバ18によって検出されるRF信号をサンプリングするように構成され得る。幾つかの例において、所定のクロックレートは約1.8GHzであり得、他の例において、それより高い又は低いサンプリングレートが用いられ得る。

シングルモードにおいて、ルートトリガに基づいて、ハードウェアクロック制御12は、トランスミッタ16がRF信号を送信する時間期間、及びトランスミッタ16がRF信号を(LO22を介して)送信する周波数を制御し得る。また、ハードウェアクロック制御12は、レシーバ18が着信RF信号を受信する時間を制御し得る。また、ハードウェアクロック制御12は、対応するレシーバ18によって検出されるRF信号をADC20の各々がサンプリングする時間を制御し得る。このように、ハードウェアクロック制御12は、ICチップ2上の構成要素の動作の継続時間及び順番を制御し得る。

In single mode, based on the root trigger,

サンプルRF信号はMCU6に提供され得る。MCU6は、オートモーティブ検出システムにおける検出されたオブジェクトの存在(又は不在)を示すデータを引き出すために、レーダーチャープにおいて、サンプリングされたRF信号を処理し得る。幾つかの例において、MCU6は、オブジェクトの位置に関する判定を行い得る。それに加えて又はその代わりに、MCU6は、オートモーティブ検出システムに対するオブジェクトの位置を判定するために複数のICチップ2からのデータを連携させるように、外部システム(例えば、レーダーコントローラ)にデータを提供し得る。

A sample RF signal may be provided to

ルートタイマ10はまた、ルートトリガをMCU6に提供し得る。これに応答して、MCU6におけるソフトウェアモジュール(例えば、ソフトウェアプロセッサタイミングモジュール)が、ソフトウェア動作及び/又はハードウェアテストのスケジューリングを制御し得る。例えば、MCU6は、M個のトランスミッタ16及びN個のレシーバ18の各々に対して較正テストをスケジューリングし得る。そのような状況において、MCU6は、任意の所与の時間において、トランスミッタ16及び/又はレシーバ18の特定のセットのみが較正されることを確実にし得、それによって、意図しない干渉を回避する。また、MCU6は、組み込み自己テスト(BIST)、レーダーチャープ等を実行するための時間を決定するためにルートトリガを用い得る。

シングルモードにおいて、ハードウェアクロック制御12によって制御される動作は、「タイトウィンドウ」内で同期され得る。本明細書において用いられるように、用語「タイトウィンドウ」は、事前定義された時間内で動作が発生し、その際、その事前定義された時間の周囲に約0.3nsの不確実性を備えることを示す。システムにおいて用いられるクロック周波数に応じ、不確実性は最大約10nsであり得る。また、MCU6によって制御されるソフトウェア動作は、約10μsの「ルーズウィンドウ」内で同期され得る。本明細書において用いられるように、用語「ルーズウィンドウ」は、事前定義された時間内に動作が発生し、その際、事前定義された時間の周囲に、タイトウィンドウの不確実性より相対的に大きい、最大約10μsの不確実性を備えることを示す。用語「タイトウィンドウ」及び「ルーズウィンドウ」は、この意味で、本明細書を通して複数回用いられる。

In single mode, operations controlled by the

ICチップ2がマスターモードで動作する状況において、ルートタイマ10は、その出力ピンを介して、同期信号を別のICチップ2(図示されない)に提供する。この別のICチップ2は、ICチップ2と同一であり得るが、モード制御信号に応答してスレーブモードで動作し得る。また、マスターモードにおいて、同期信号はハードウェアクロック制御12に供給される。上述したように、ハードウェアクロック制御12はまた、モード制御信号を受信する。モード制御信号がマスターに設定され、同期トリガがアクティベートされることに応答して、ハードウェアクロック制御12は、動作のシングルモード(これは動作がルートトリガに基づく)に関して説明した方法と同様の様式で、同期信号に基づいてトランシーバ14を制御する。また、マスターモードにおいて、MCU6は、トランシーバの動作(例えば、較正、BIST、レーダーチャープ等)を制御する。

In situations where an

ICチップ2がスレーブモードで動作する状況において、同期信号は、ICチップの入力において、マスターモードで動作する別の外部ICチップから受信される。同期信号は、トリガセレクタ8及びハードウェアクロック制御12に提供される。また、モード制御信号は、スレーブに設定され、ICチップ内で分配されてトリガセレクタ8及びハードウェアクロック制御12に提供される。モード制御信号(スレーブに設定されている)は、ルートタイマ10及びハードウェアクロック制御12においてクロック信号の生成を制御するために、トリガセレクタ8及びハードウェアクロック制御12に、同期トリガを選択させる。例えば、同期信号におけるパルスが、ルートタイマ10によって出力されたルートトリガを、同期信号に調整させるようにリセットさせ得る。また、ハードウェアクロック制御12及びMCU6は、シングルモード及びマスターモードの動作と同様に動作を継続し、タイミングは同期信号によって指示される。1つのICチップ2がマスターモードで動作し、1つ又は複数のICチップ2がスレーブモードで動作するマルチチップ例において、スレーブモードで動作するICチップ2の動作は、ローカルで(例えば、ICチップ2に対してローカルな構成要素によって)実行される。また、そのような動作のタイミングは、同期信号を提供する外部ソース(別のICチップ2)によって制御される。

In situations where the

マルチチップ例(1つのICチップ2がマスターモードで動作し、1つ又は複数の残りのICチップがスレーブモードで動作する)においてICチップ2を動作させることによって、チップ間ハードウェア動作(例えば、ADC20のサンプリング)は、「タイトウィンドウ」内で同期され得る。また、そのようなタイトな同期を必要としない複数のICチップ2にわたるソフトウェア動作は、「ルーズウィンドウ」内で同期され得る。また、同期信号が各ICチップ2の間で共通であるので、マスターモードで動作するICチップ2とスレーブモードで動作する残りの1つ又は複数のICチップ2との間でハンドシェイクプロシージャ(例えば、新しいチャネルを確立するためのプロシージャ)を実装する必要がない。

Inter-chip hardware operations (e.g.,

説明されるように、同じICチップ2が、それ自体(例えば、シングルモード)によって配備され得るか又は、1つのICチップ2がマスターとして(マスターモードで)動作し、残りの1つ又は複数のICチップがスレーブとして(スレーブモードで)動作するマルチチップシステム(例えば、マルチチップレーダーシステム)において配備され得る。

As described, the

図2は、マルチチップレーダーシステムにおけるハードウェアADCの調整された(同期された)サンプリングの例を図示するタイミング図50を示す。図3は、マルチチップレーダーシステムにおけるレーダーチップの調整されたソフトウェアタイミングの例を示す別のタイミング図60を図示する。タイミング図50及びタイミング図60は、図1に図示されるタイプの4個のICチップ2を想定し、第1のレーダーチップ2がマスターモードで動作し、第2から第4のレーダーチップ2がスレーブモードで動作する。また、各レーダーチップ2は4個のADC20を有し、合計16個のADC20を有する(図2にADC1~ADC16として示される信号に対応する)。このように、図2及び図3の説明に関連して、図1の例示のICチップ2を参照する。

FIG. 2 shows a timing diagram 50 illustrating an example of coordinated (synchronized) sampling of a hardware ADC in a multichip radar system. FIG. 3 illustrates another timing diagram 60 showing an example of coordinated software timing of radar chips in a multi-chip radar system. Timing diagram 50 and timing diagram 60 assume four

図2の例において、タイミング図50は、トランスミッタ16の出力周波数(LO22によって制御される)を、マイクロ秒(μs)における時間の関数として、プロットする。タイミング図50に図示されるように、周波数は、約80μsの時間にわたり、80GHzから81GHzにランプされる。また、16個のADC20の各々が、各周波数ランプの間、タイトウィンドウ内で、対応するレシーバをサンプリングするように構成される。

In the example of FIG. 2, timing diagram 50 plots the output frequency of transmitter 16 (controlled by LO 22) as a function of time in microseconds (μs). As illustrated in timing diagram 50, the frequency is ramped from 80 GHz to 81 GHz over a period of approximately 80 μs. Also, each of the 16

タイミング図40は、時間に対するRF周波数の挙動を図示する。周波数変調連続波レーダー(FMCWレーダー)システムにおいて、LO22は、90マイクロ秒(90μs)にわたり、80GHzから81GHzに、時間内に線形に変化(ランプアップ又はダウン)する周波数を有する信号を生成する。図1に図示されるM個のトランスミッタ16の1つ又は複数が、アンテナを用いてこの信号を増幅及び送信し得る。電磁信号は、アンテナ、及び図1に図示されるN個のレシーバ18の1つ又はそれ以上のレシーバ18に存在する回路構成要素を用いて受け取られる。図1に図示されるN個のADC20の各々は、N個のレシーバ18の対応する1つのレシーバ18の出力をサンプリングする。タイミング図50において、0μsと100μsとの間の時間が1チャープと呼ばれる。レーダーフレームが、一連のチャープを含む。レーダーフレームのプロパティには、特定された数及びシーケンスのチャープ、及びレーダーフレームの構成チャープのプロパティが含まれる。チャープのプロパティには、いつ、どれくらいの間、LO周波数がランプアップ又はダウンを開始すべきか、いつトランスミッタ16及びレシーバ18がアクティベート及びディアクティベートされるべきか、いつADC20がレシーバ18出力をサンプリングするべきかを示す情報を含まれる。

Timing diagram 40 illustrates the behavior of RF frequency with respect to time. In a Frequency Modulated Continuous Wave Radar (FMCW Radar) system, LO22 produces a signal with a frequency that varies (ramps up or down) linearly in time from 80 GHz to 81 GHz over 90 microseconds (90 μs). One or more of the

マルチチップレーダーシステムの動作の一例として、16個のADC20の各々をほぼ同じ時間にサンプリングすることは、マルチチップレーダーシステムのどのレシーバ18が、検出されたオブジェクトによって反射された送信された信号(これは、反射された信号と称され得る)を受信し、どのレシーバ18が、反射された信号を受信しないかを示す情報を提供し得る。オブジェクトとマルチチップレーダーシステムとの間の距離が、例えば、送信された信号の送信の時間と、反射された信号のサンプリングの時間とにおける周波数の差などに基づいて判定され得る。例えば、周波数における差は、送信信号及び反射された信号の飛行時間(time of flight)を判定するために用いられ得、それは、検出されたオブジェクトに対する距離を計算するために用いられ得る。

As an example of the operation of a multichip radar system, sampling each of the 16

図3の例において、タイミング図60は、出力周波数をミリ秒(ms)における時間の関数としてプロットする。説明を簡素化するために、タイミング図50及び60は、同じランプ出力信号を異なるスケール(タイミング図50ではμs、及びタイミング図60ではms)でプロットする。図3のタイミング図60において示されるように、特定のスケジュールされた時間(これは周期的又は非同期的であり得る)で、トランシーバ較正(タイミング図60において「CAL」と示される)が実施される。説明されるように、各MCU6上で実行するソフトウェアは、相互の較正、レーダーチャープ、及び/又はBISTを実施するために、及び種々のICチップ2の間の不要な干渉を回避するために、較正、レーダーチャープのトリガ、BIST(及び/又はその他のソフトウェア動作)の実行を同期して(例えば、約10μs以内に)スケジューリングする。

In the example of FIG. 3, timing diagram 60 plots output frequency as a function of time in milliseconds (ms). For ease of illustration, timing diagrams 50 and 60 plot the same lamp output signal on different scales (μs for timing diagram 50 and ms for timing diagram 60). As shown in timing diagram 60 of FIG. 3, at specific scheduled times (which can be periodic or asynchronous), transceiver calibration (denoted as "CAL" in timing diagram 60) is performed. . As will be explained, software running on each

タイミング図50及び60の各々において、フレームトリガ(FT)が図示される。FTは、フレームパルスにおけるクロックエッジの例であり得る。FTは、同期信号によって提供され得、同期信号は、マスターICチップ2のルートタイマ10によって生成され得、3個のスレーブICチップ2に提供され得る。ソフトウェア動作が、レーダーシステムにおけるICチップ2の各々を横切って、約10μs以内に同期され得る。このように、ICチップ2をマスターモード及びスレーブモードで動作させることによって、ハードウェア動作(例えば、ADC20のサンプリング)がタイトウィンドウ内で同期され得、一方、そのようなタイトな同期を必要とする複数のICチップ2にわたるソフトウェア動作がルーズウィンドウ内で同期され得る。複数のICチップ2を用いることで、(例えば、16個又はそれ以上のレシーバ18を用いて)ビーム形成が可能になる。従って、ICチップ2は、オートモーティブ検出システムにおける短距離又は長距離レーダー(例えば、10~200メートル以内)検出に用いられ得る。他の例において、ICチップ2はまた、ビーム形成を備えるレーダーを必要とする産業用システムに用いられ得る。

In each of timing diagrams 50 and 60 a frame trigger (FT) is illustrated. FT can be an example of a clock edge in a frame pulse. FT may be provided by a synchronization signal, which may be generated by the

ハードウェア動作(例えば、レシーバのサンプリング)とソフトウェア動作を同期させることは、ICチップ2に関連するトランスミッタ16及びレシーバ18の自己較正の間の相互RF干渉を回避する。

Synchronizing hardware operations (eg, receiver sampling) and software operations avoids mutual RF interference during self-calibration of

図4は、レーダーICチップ100の例の構成要素図を示す。レーダーICチップ100は、図1のICチップ2を実装するために用いられ得る。レーダーICチップ100はMCU102を含み得る。MCU102は、DSP等のマイクロコントローラであり得る。MCU102は、タイミング機能を処理するための機械実行可能命令を含み得る。説明を簡略化する目的で、ソフトウェアタイミング104と示される別個の構成要素が、MCU102の外部にあるように図示されている。しかしながら、ソフトウェアタイミング104は、MCU102上で実行するソフトウェアモジュール(例えば、機械可読命令)を表す。

FIG. 4 shows a component diagram of an example

ICチップ2は、マルチプレクサ等のトリガセレクタ106を含み得る。トリガセレクタ106は、スタートトリガ信号(図4において「スタートトリガ」と示される)を出力するように構成され得、スタートトリガ信号は、ソフトウェアトリガ(図4において「SWトリガ」と示される)とトリガセレクタ106において受信され得るハードウェアトリガ(図4において「HWトリガ」と示される)の一方に基づく。ソフトウェアトリガは、チップ上で生成され得、MCU102から提供され得る。ハードウェアトリガ(同期信号として用いられる)は、同期入力ポート105(図4において「SYNCH INPUT」として示される)から提供され得、それは、100チップ(マスターモードにおける場合)によって、又は別のチップ(スレーブモードにおける場合)によって生成され得る。トリガセレクタ106は、モード制御信号(図4において「MODE CONTROL」として示される)に基づいて、ソフトウェアトリガ又はハードウェアトリガのいずれかを選択し得る。モード制御信号は、MCU102又は外部ソースから提供され得る。或いは、他の例において、モード制御信号は、トリガセレクタ106にハード配線され得る。更に他の例において、トリガセレクタ106は、ICチップ2が実装されるチップ又はシステムに関連する事象又は状態を検出することに応答して、トリガセレクタ106を選択するための内部論理を含み得る。

例えば、スタートトリガは、フレームパルス信号であり得る。本明細書において用いられるように、用語「フレームパルス」は、各フレームの開始においてクロックエッジを有する、又は所定の数のフレームの開始においてクロックエッジを有するパルス信号を指す。このように、スタートトリガは、フレームの開始(例えば、およそ40ms毎)又は所定の数のフレームの開始を示すクロックパルスを有するパルス信号であり得る。スタートトリガはルートタイマ108に提供され得る。スタートトリガにおける各パルスに応答して、ルートタイマ108はルートトリガ(例えば、フレームパルス)を生成し得、ルートトリガもフレームの開始を示す。従って、幾つかの例において、ルートトリガは、スタートトリガのパススルーバージョンであり得る。或いは、ルートトリガは、スタートトリガの遅延バージョンであり得る(例えば、1又は複数クロックパルス遅延される)。ルートトリガは、ハードウェアクロック制御111の構成要素に出力され得る。ハードウェアクロック制御111の構成要素は、図1のハードウェアクロック制御12を実装し得る。

For example, the start trigger can be a frame pulse signal. As used herein, the term "frame pulse" refers to a pulse signal having a clock edge at the beginning of each frame or having a clock edge at the beginning of a predetermined number of frames. Thus, the start trigger can be a pulse signal with a clock pulse indicating the start of a frame (eg approximately every 40 ms) or a predetermined number of frames. A start trigger may be provided to root timer 108 . In response to each pulse in the start trigger, root timer 108 may generate a root trigger (eg, frame pulse), which also marks the start of a frame. Thus, in some examples, the root trigger can be a pass-through version of the start trigger. Alternatively, the root trigger can be a delayed version of the start trigger (eg, delayed by one or more clock pulses). The root trigger may be output to the

一例として、ルートトリガは、ハードウェアクロック制御111のクロックセレクタ112の入力に提供され得る。クロックセレクタ112は、ルートトリガか、又は同期入力ポート105(本明細書において説明される)において受信される同期信号のいずれかに対応するスタートクロック信号(図4において「START CLK」と示される)を出力し得る。クロックセレクタ112は、モード制御信号によって制御され得る。

As an example, a root trigger may be provided to the input of

ルートタイマ108はまた、フリーランニングカウンタ(FRC)信号(図4において「FRC」と示される)をハードウェアクロック制御111のハードウェアリーフタイマモジュール114に提供し得る。ハードウェアリーフタイマモジュール114は、各々が1つ又は複数のタイミング信号を生成するハードウェアリーフタイマの集合を表す。ハードウェアリーフタイマモジュール114は、レーダーICチップ100における種々のアクティビティのタイミングを制御するハードウェアリーフタイマを介して、幾つかのデジタル信号(タイミング信号)を生成し得る。これらのアクティビティには、種々のレシーバ、トランスミッタ、及び/又はLO回路のイネーブル及びディスエーブル、LO出力信号周波数のランプアップ又はダウンの開始及び停止、ADC出力のデジタル処理の開始等が含まれ得る。ハードウェアリーフタイマは、ルートタイマ108から提供されるルートトリガに基づいて同期されるタイミング信号及び/又はタイミング制御信号を生成し得る回路構成要素を含み得る。同様に、ルートタイマ108は、FRC信号を、(MCU102の)ソフトウェアタイミングモジュール104に提供し得る。また、マスターモード及びスレーブモード等の動作の幾つかのモードにおいて、ルートタイマ108は、同期信号(これは、ハードウェアトリガ信号に対応し得る)を、レーダーICチップ100の同期出力ポート115(図4において「SYNCH OUTPUT」と示される)において出力し得る。幾つかの例において、同期信号は、FRCが所定の値に達する毎にパルス発振され得る。

Root timer 108 may also provide a free running counter (FRC) signal (denoted “FRC” in FIG. 4) to hardware

クロックセレクタ112は、スタートクロック信号を、ハードウェアクロック制御111の同期ゲータ116の入力に提供し得る。同期ゲータ116はまた、フレームパルス又は同期信号の後、事前定義された時間に、ハードウェアリーフタイマモジュール114からクロックストップ信号(図4において「STOP CLK」と示される)を受信し得る。同期ゲータ116は、ハードウェアクロック制御111のADCクロック生成器118からクロック信号を受信し得る。ADCクロック生成器118からのクロック信号は、特定のインスタンス(例えば、約2~10μs毎)においてクロックパルスを有し得る。同期ゲータ116は、入力クロックがグリッチ無しに出力に転送されることを確実にする、論理ゲート及びラッチ又はフリップフロップを含むデジタル回路として設計され得る。

同期ゲータ116は、1つ又は複数のデジタル論理ゲート及びラッチ又はフリップフロップを含むデジタル回路として実装され得る。同期ゲータ116は、スタートクロックにおいて開始されるフレームパルスから、ストップクロック信号がハードウェアリーフタイマモジュール114からパルス発振されるまでの時間において、ADCクロック生成器118からのクロック信号のクロックエッジが、同期ゲータ116の出力において出力されることを可能にするように構成され得る。出力クロックのイネーブル及びディスエーブルは、いずれの時間にも、出力クロックにおけるグリッチを防止するように成される。同期ゲータ116の出力は、4個のADC120の各々に結合され、ADC120、及びADC120の構成要素によるサンプリングクロック及びデジタル状態機械クロックによって用いられる。ADC120の各々は、それぞれのレシーバ(例えば、図1のレシーバ18)に結合され得る。幾つかの例において、レシーバは、レーダーICチップ100の外部にあり得る。他の例において、レシーバはレーダーICチップ100内に統合され得る。上述したように、同期ゲータ116は、出力においてグリッチを防止する。従って、同期ゲータ116の出力を用いるハードウェアリーフタイマは、ハードウェアリーフタイマが動作する必要がある期間の間、クロック入力を受け取るように動作し、その期間の終わりにおいて、各ハードウェアリーフタイマの入力クロックが自動的にゲーティングされる。

説明を簡潔にするために、多くの例がハードウェアリーフタイマモジュール114を備えて本明細書において説明され、図6~図8において示される。ハードウェアリーフタイマモジュール114は、ルートタイマ108から直接的にFRC及びルートトリガを受け取る幾つかのハードウェアリーフタイマを含む。しかしながら、多くの例において、ハードウェアリーフタイマモジュール114又はハードウェアリーフタイマモジュール114のハードウェアリーフタイマの幾つかは、同期ゲータ116の出力クロックを受け取り、それにより、同期ゲータ116を介してルートタイマ108に間接的に同期する。それは、タイトな同期を可能にし、一方で、他の構成要素の動作は、本明細書の例に説明されるのと同じままである。

For simplicity of explanation, many examples are described herein with a hardware

4個のADC120の各々は、内部クロック、シリアルツーパラレル(S2P)インタフェース、有限状態機械(FSM)、及び/又は、所定のレート(例えば、1.8GHz)においてそれぞれのレシーバの出力のサンプリングをイネーブルするためのその他の回路構成要素を含み得る。各ADC120は、信号パルスに応答してそれぞれのレシーバの出力をサンプリングするシグマデルタモジュレータ(SDM)を含み得る。例えば、各ADC120は、同期ゲータ116の出力におけるクロックパルスが、各ADC120のSDMをアンゲートし得、それにより、ADC120の各々に、各それぞれのレシーバの出力をサンプリングさせるように設計され得る。S2Pインタフェースは、それぞれのADC120によってサンプリングされたビットを連結し得る。また、特定の時間インスタンスにおいて、各ADC120をリセットするために、ハードウェアリーフタイマモジュール114からリセット信号が提供され得る。このように、ADCクロック生成器118によって生成されるスタートクロック信号は、ADC120に提供され、そのため、各ADC120のFSM及びS2Pインタフェースは、調整された位相を用いてサンプリングサイクルを開始する。

Each of the four

ハードウェアリーフタイマモジュール114によって生成されるハードウェアリーフタイマはまた、関連するトランスミッタ(例えば、図1のトランスミッタ16)及び/又はLO(例えば、図1に図示されるLO22)上の動作を制御し得る。トランスミッタ及び/又はLOは、レーダーICチップ100に対して内部又は外部にあり得る。また、ハードウェアリーフタイマは、DSP及び/又はデジタルデータパス等のプロシージャにおける動作の順を制御し得る。このように、レシーバ出力のサンプリングを含む、ハードウェアリーフタイマモジュール114によって生成されるハードウェアリーフタイマによって制御される動作は、タイトウィンドウに同期され得る。

The hardware leaf timers generated by hardware

ソフトウェアタイミングモジュール104は、較正、BIST、レーダーチャープ等の動作をスケジューリングし得る。ソフトウェアタイミングモジュール104によって制御される動作は、ルーズウィンドウ内でICチップを横断して同期され得る。

1つの例示のソフトウェア動作として、サンプルRF信号は、ADC120の各々からMCU102に提供され得る。MCU102は、オートモーティブ検出システムにおいて、検出されたオブジェクトの存在(又は不在)を示すデータを引き出すために、サンプリングされたRF信号をレーダーチャープにおいて処理し得る。幾つかの例において、MCU102は、オブジェクトの位置に関する判定を行い得る。それに加えて又はその代わりに、MCU102は、オートモーティブ検出システムに対するオブジェクトの位置を判定するために、複数のレーダーICチップ100からのデータを連携させるため、データを外部システム(例えば、別のレーダーICチップ又はレーダーコントローラ)に提供し得る。また、レーダーコントローラ(又は他の外部システム)は、他のレーダーICチップ100との干渉を避けるために、ソフトウェアタイミングモジュール104の動作の順を制御し得るタイミング情報をMCU102に提供し得る。

As one example software operation, a sample RF signal may be provided to

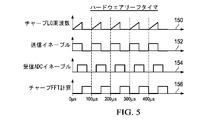

図5は、ハードウェアリーフタイマモジュール114により出力されるハードウェアリーフタイマのセットを示すタイミングチャート150、152、154、及び156の例を図示する。図5におけるチャートの各々が、約500μsの同じフレームに対してスケーリングされる。タイミングチャート150において、LOチャープ信号周波数(図5において「CHARP LO FREQ」と示される)は、時間の関数としてプロットされる。一例において、LOチャープ信号の周波数は80GHzから81GHzの範囲にわたり得る。別の例において、LOチャープ信号の周波数は20GHzから21GHzの範囲にわたり得る。更に他の例において、他の周波数が用いられ得る。タイミングチャート152において、送信信号(図5において「TX ENBLE」と示される)電圧が、時間の関数としてプロットされる。送信イネーブル信号は、トランスミッタに、LOチャープ信号に対応する周波数において信号を送信させる。

FIG. 5 illustrates example timing diagrams 150 , 152 , 154 , and 156 showing a set of hardware leaf timers output by hardware

タイミングチャート154は、レシーバADCイネーブル信号(ストップクロック信号の相補(complement)に対応する)の電圧を、時間の関数としてプロットする。レシーバADCイネーブル信号は、受信ADC120に、対応するレシーバをサンプリングさせる。また、タイミングチャート156は、チャープ高速フーリエ変換(FFT)コンピューティング信号の電圧を時間の関数としてプロットする。チャープFFTコンピューティング信号は、MCU102に、ADC120の出力を読み出させる。これは、例えば、オートモーティブ検出システム又はその他のレーダーシステムにおけるオブジェクトの位置及び/又は距離の計算に(例えば、デジタル信号処理を介して)用いられ得る。タイミングチャート150~156によって示されるように、ハードウェアリーフタイマモジュール114によって生成されるハードウェアリーフタイマは、レーダーICチップ100の動作を、タイトウィンドウ内で制御し得る。また、図5における例示のハードウェアリーフタイマのリストは網羅的ではない。幾つかの例において、ハードウェアリーフタイマモジュール114によって生成されるハードウェアリーフタイマは、それに加えて又はその代わりに、レーダーチャープの生成及び/又は送信、レシーバ回路のイネーブル及びディスエーブル、及び/又は、ほぼ全てのレーダー動作の開始を制御する。

更にまた、ハードウェアリーフタイマモジュール114は、トランスミッタ及び/又はレシーバの電力制御等のレーダーチャープに調整される信号生成を制御するハードウェアリーフタイマを生成し得る。例えば、ハードウェアリーフタイマは、トランスミッタ及び/又はレシーバに、レーダーチャープの間、高性能、高電力状態で動作させ得、レーダーチャープが終了すると低性能、低電力状態で動作させ得る。

Furthermore, hardware

上述したように、レーダーICチップ100は、モード制御信号に基づいて、シングルモード、マスターモード、又はスレーブモードで動作し得る。図6は、シングルモードで動作するレーダーチップ100の例を図示する。図4及び図6において、同じ構造を示すために同じ用語及び参照番号が用いられる。また、説明を簡素化するために、シングルモードでの信号フローを図示するために、図4に示される幾つかの信号は図6から省かれる。

As described above, the

モード制御信号は、トリガセレクタ106が、スタートトリガとして、MCU102からソフトウェアトリガを出力するように、シングルモードに設定され得る。このように、ルートタイマ108の出力は、MCU102によって制御される。また、クロックセレクタ112は、(モード制御信号に応答して)ルートタイマ108によって出力されるルートトリガ(フレームパルス)を選択する。従って、同期ゲータ116の出力は、MCU102によって制御される。また、シングルモードにおいて、レーダーICチップ100は、別のレーダーICチップと同期する必要がない。このように、シングルモードにおいて、外部ハードウェアトリガを受け取る可能性がなく、同期信号が提供される必要がない。従って、シングルモードにおいて、MCU102は、ADC120のサンプリング、ハードウェアリーフタイマモジュール114によって生成されるハードウェアリーフタイマ、及びソフトウェアタイミングモジュール104を制御し得る。

The mode control signal can be set to single mode so that

図7は、マスターモードで動作し、スレーブモードで動作する別のレーダーICチップ100に結合される、レーダーチップ100の例を図示する。図4及び図7において、同じ構造を示すために同じ用語及び参照番号が用いられる。また、説明を簡素化するために、マスターモードでの信号フローを図示するために、図4において示される幾つかの信号は、図7から省かれる。

FIG. 7 illustrates an

モード制御信号は、スタートトリガとして、トリガセレクタ106がMCU102からソフトウェアトリガを出力するように、マスターモードに設定され得る。このように、ルートタイマ108の出力はMCU102によって制御される。同期信号(フレームパルス)は、同期出力ポート115において、ルートタイマ108によって出力される。そのような状況において、ルートタイマ108によって出力される同期信号は、ルートトリガ信号において動作する。また、同期信号は、同期入力ポート105においてレーダーICチップ100にフィードバックされ、クロックセレクタ112に結合される。同期入力ポート105と同期出力ポート115との間の接続は、レーダーICチップ100のピン間の外部接続であり得、或いは、それはレーダーICチップ100内の内部接続によって実装され得る。そのような状況において、伝播遅延を、スレーブモードで動作する別のレーダーICチップ100にマッチさせるために、内部接続において、遅延(例えば、スイッチ及び/又はタイマ)が実装され得る。

The mode control signal can be set to master mode so that

また、同期入力ポート105において受信される同期信号は、(モード制御信号に応答して)クロックセレクタ112によって選択される。従って、同期ゲータ116の出力は、MCU102によって制御される。また、マスターモードにおいて、同期信号は、1つ又は複数のスレーブレーダーICチップに提供され得る。このように、マスターモードにおいて、MCU102は、レーダーICチップに対してローカルであるADC120のサンプリング、ハードウェアリーフタイマモジュール114によって生成されるハードウェアリーフタイマ、及びソフトウェアタイミングモジュール104を制御し得る。

The sync signal received at

図8は、スレーブモードで動作するレーダーチップ100の例を図示し、レーダーICチップ100は、マスターモードで動作する別のレーダーICチップに結合される。図4、図7、及び図8において、同じ構造を示すために同じ用語及び参照番号が用いられる。また、説明を簡素化するために、スレーブモードにおいて信号フローを図示するために、図4に示される幾つかの信号は図8から省かれている。

FIG. 8 illustrates an

スレーブモードにおいて、同期信号が同期入力ポート105において受信される。同期信号は、マスターモードで動作するレーダーICチップから提供され得、ハードウェアトリガ(例えば、フレームパルス)として、トリガセレクタ106に提供される。

In slave mode, a sync signal is received at

モード制御信号は、トリガセレクタ106が、スタートトリガとして、MCU102からハードウェアトリガを出力するように、スレーブモードに設定され得る。これに応答して、ルートタイマ108は、スタートトリガに基づいて、ルートトリガをリスタートし得る。スタートトリガは、マスターモードで動作するICチップによって生成される同期信号に基づく。このように、ハードウェアトリガは、スレーブモードで動作するレーダーICチップ100のルートタイマ108を再同期させ、そのため、スレーブモードで動作するレーダーICチップ100のルートタイマ108がマスターモードで動作するICチップのルートタイマに調整される。このように、ルートタイマ108の出力は、マスターモードで動作するレーダーICチップによって制御される。そのような再同期は、或る時間期間にわたって、タイマドリフトを低減し得る。

The mode control signal may be set to slave mode so that

また、同期入力ポート105において受信された同期信号は、(モード制御信号に応答して)クロックセレクタによって選択される。従って、同期ゲータ116の出力は、マスターモードで動作するレーダーICチップによって制御される。このように、スレーブモードにおいて、マスターモードで動作するレーダーICチップによって提供される同期信号は、ADC120のサンプリング、ハードウェアリーフタイマモジュール114によって生成されるハードウェアリーフタイマ、及びスレーブモードで動作するレーダーICチップ200に対してローカルであるソフトウェアタイミングモジュール104を制御し得る。

Also, the sync signal received at

スレーブモードで動作するレーダーチップ100のルートタイマ108が、(同期信号を介して)マスターモードで動作するレーダーチップのルートタイマと同期するので、スレーブモードで動作するレーダーチップ100及びマスターモードで動作するレーダーチップは、構成要素(例えば、トランスミッタ及び/又はレシーバ)の較正、BIST、種々のレーダーチップ100間のアクティビティの監視及び機能的レーダーチャープを同期し得る。また、図7及び図8に図示されるように、同期信号は、2つのレーダーICチップ間の適切な伝播遅延マッチを確実にするために、(図7における)マスターモードで動作するレーダーICチップ100、及び(図8における)スレーブモードで動作するレーダーICチップ100の両方における同期入力ポート105に提供される。

Since the root timer 108 of the

図4~図8に図示されるように、同じレーダーICチップ100が、シングルモード、マスターモード、又はスレーブモードで動作し得る。従って、複数のレーダーICチップ100が必要とされる状況において、マスターモードで動作するレーダーICチップ100は、接続されているレーダーICチップ100の各々に対する全体的なタイミングを制御し得る。また、1つのみのレーダーICチップ100が必要とされている状況において、異なるレーダーICチップ100を再設計/製造する必要性が存在しない。

As illustrated in FIGS. 4-8, the same

また、レーダーICチップ100がスレーブモードで動作する状況においても、較正及び/又はレーダーチャープの制御等のソフトウェア動作が、レーダーICチップ100のMCU102上で実施され得る。このアーキテクチャは、各接続されているレーダーICチップ100のMCU102間で、そのようなソフトウェア動作の処理負荷を分散する。

Software operations such as calibration and/or control of radar chirp may also be performed on the

図4~図8に関して図示及び説明されるように、複数のレーダーICチップ100にわたるハードウェア動作(ADC120のサンプリングを含む)が、タイトウィンドウ内で同期され得る。そのようなタイトな同期を必要としない、複数のレーダーICチップ100にわたるソフトウェア動作は、ルーズウィンドウ内で同期され得る。このように、マルチチップシステムにおいて、複数のレーダーICチップ100間で2つのレベルの同期(ルーズとタイト)を達成するために、同じレーダーICチップ100が用いられ得る。また、(図7及び図8に示されるように)同期信号は、各レーダーICチップ100の間で共通なので、マスターレーダーICチップ100と1つ又は複数のスレーブレーダーICチップ100との間で、ハンドシェイクプロシージャを実装する必要性が存在しない。

As illustrated and described with respect to FIGS. 4-8, hardware operations (including

図9は、レーダーICチップ2及び/又は図5~図8に図示されるレーダーICチップ100を用い得るレーダーシステム200の例を図示する。レーダーシステム200の構成要素は、印刷回路基板(PCB)202上に搭載され得る。例えば、レーダーシステム200は、オートモーティブ検出システム又はその他のレーダーシステムに用いられ得る。レーダーシステム200は、レーダーICチップからの(例えば、その上で動作するMCUからの)レーダーデータを処理するために、レーダー制御204を含み得る。レーダー制御204は、機械可読命令をストアするメモリにアクセスする、マイクロコントローラ又は1つ又は複数のプロセッサコアとして実装され得る。

FIG. 9 illustrates an

レーダーシステム200はまた、マスターレーダーICチップ206、及びK個のスレーブレーダーICチップ208を含み得、Kは、1に等しいか又はそれ以上の整数である。マスターレーダーICチップ206は、図1に図示されるレーダーチップ2、及び/又は図5及び図7に図示されマスターモードで動作するレーダーICチップ100として実装され得る。K個のスレーブレーダーICチップ208の各々は、図1に図示されるICチップ2、及び/又は図5及び図8に図示されスレーブモードで動作するレーダーICチップ100として実装され得る。従って、マスターレーダーICチップ206及びK個のスレーブレーダーICチップ208の各々は、同じチップ設計の異なるインスタンスであり得る。マスターレーダーICチップ206及びK個のスレーブレーダーICチップ208の動作のモードは、それぞれのローカルソフトウェア構成に基づいて、及び/又はPCB202上のICチップピン構成に基づいて設定され得る。

マスターレーダーICチップ206は、K個のスレーブレーダーICチップ208の各々に提供され、マスターレーダーICチップ206にフィードバックされる、同期信号(例えば、図9において「SYNC SIGNAL」と示されるフレームパルス)を生成し得る。同期信号は、マスターICレーダーチップ206及びK個のスレーブレーダーICチップ208の各々の間で、ハードウェア動作(例えば、レシーバのサンプリング)をタイトウィンドウにおいて、及びソフトウェア動作(自己較正、BIST、レーダーチャープ)等をルーズウィンドウにおいて同期させ得る。

The master

例えば、レーダー制御204は、或るソフトウェア機能(例えば、調整及び/又はBIST)を実施するために、時間ウィンドウを(例えば、時分割多重を介して)マスターレーダーICチップ206及びスレーブレーダーICチップ208に割り振り得る。割り振られた時間ウィンドウ及び同期信号に基づいて、マスターレーダーICチップ206、及びスレーブレーダーICチップ208の各々は、調整及び/又はBISTの間に生じ得る相互干渉を回避するために協調して動作し得る。

For example,

また、動作の間、マスターレーダーICチップ206、及びスレーブレーダーICチップ208の各々は、レーダーデータをレーダー制御204に提供し得る。レーダーデータは、レーダーICチップ2に対するオブジェクトの距離及びオブジェクトの方向を判定するために照合され用いられ得るデータを含み得る。

Also, during operation, each of master

また、マスターレーダーICチップ206は、(幾つかの例において)相補型金属酸化物半導体(CMOS)信号ワイヤ等の単一ワイヤを介して提供され得る1つのみの信号を用いて、マスターレーダーICチップ206及びK個のスレーブレーダーICチップ208の動作を同期させ得る。

Also, the master

一例を図4~図9に関連して説明する。PCB202は、レーダーシステム200を含む。レーダーシステム200は、図9において206及び208と示され、各々が図4に示されるレーダーICチップ100として実装される、幾つかのレーダーICチップを含む。レーダー制御204、及びレーダーICチップ206及び208の1つは、レーダーICチップ206及び208の中にレーダーフレームのプロパティを構成する。レーダーICチップの1つ、即ち、図9におけるレーダーICチップ206は、マスターモードで動作するように構成され、残りのレーダーICチップ208はスレーブモードで動作するように構成される。

An example is described in connection with FIGS. 4-9.

マスターモードにおいて、マスターレーダーICチップ206のMCU102(図4に図示される)はソフトウェアトリガを生成し、ソフトウェアトリガは、202において、レーダーフレームが発生すべきであることをレーダーシステムに示す信号事象である。この事象は、上記で定義されるようにフレームパルスと称される、デジタルパルスの形式で示され得る。マスターレーダーICチップ206におけるトリガセレクタ106(マルチプレクサ)は、このソフトウェアトリガをルートタイマ108(図4に図示される)に転送し、ルートタイマ108は、この事象の時間から時間のカウントを開始する(ルートタイマ108は、この事象以来、システムクロックのエッジがいくつ発生したかをカウントすることによってこれを行う)。MCU102(図4に図示される)、又はその他のデジタル状態機械におけるマスターレーダーIC上でのソフトウェア又はファームウェア実行は、事前定義された値にルートタイマ値が達すると、種々のレーダー動作をトリガする。レーダー動作は、レーダー構成要素、或いは、レーダーチャープ又はフレームの較正又はBISTの実行を含み得る。レーダー動作は、MCU102のための、ルートタイマ108による1つ又は複数の後続のソフトウェアトリガの生成も含み得る。ルートタイマ108によって生成されるフレームパルスはまた、フレームパルスを同期ゲータ116に転送するように構成されるクロックセレクタ112(マルチプレクサ)に送られる。

In master mode, the MCU 102 (illustrated in FIG. 4) of the master

同期ゲータ116は、1つ又は複数のデジタル論理ゲート及びフリップフロップのセットとして実装され得る。同期ゲータ116は、フレームパルスからストップクロック信号がハードウェアリーフタイマモジュール114からパルス発振されるまでの時間において、ADCクロック生成器118からのクロック信号のクロックエッジが、ADC1~4 120(図4に図示される)に同時に(又はほぼ同時に)出力されることを可能にする。これは、ADC出力を用いるオブジェクト方向の方向の判定が正確であるように、ADC1~4 120の各々が、それらのそれぞれのレシーバ出力をタイトウィンドウ内でサンプリングすることを確実にする。

ルートタイマ108はまた、マスターレーダーICチップ206における一層多くのカウンタのタイミングを制御し、これらのカウンタは、図4に図示されるハードウェアリーフタイマモジュール114によって集合的に表される。ハードウェアリーフタイマモジュール114は、ハードウェアリーフタイマを介して、幾つかのデジタル信号を生成し得る。デジタル信号は、種々のRX/TX/LO回路のイネーブル及びディスエーブル、LO出力信号周波数のランプアップ又はダウンの開始及び停止、ADC出力のデジタル処理の開始等、マスターレーダーICチップ206における種々のアクティビティのタイミングを制御し得る。

Root timer 108 also controls the timing of more counters in master

スレーブレーダーICチップ208のうちの1つのスレーブレーダーICチップ208の動作が説明され、他のスレーブレーダーICチップ208は同様に動作する。また、マスターレーダーICチップ206のルートタイマ108によって生成されるフレームパルスは、スレーブレーダーICチップ208の同期ゲータ116及びルートタイマ108に、スレーブレーダーICチップ208における、それぞれ、クロックセレクタ112及びトリガセレクタ106の適切な構成を介して、(同期信号として)転送される。フレームパルスを受け取ると、スレーブレーダーICチップ208のルートタイマ108は、それ自体をリセットし、マスターレーダーICチップ206のルートタイマ108とアライメント状態にさせる(アライメントは、同じ値又は既知の差の値を意味し得る)。スレーブレーダーICチップ208における構成要素の動作のリセットは、マスターレーダーICチップ206と同じである。これは、マスターレーダーICチップ206のADC1~4 120及びスレーブレーダーICチップ208のADC1~4 120がそれらのRX出力を同時に(又はほぼ同時に)サンプリングすることを確実にし、そのため、ADC出力を用いるオブジェクト方向の方向の判定が正確となる。1つのみのレーダーICチップを備えるシステムにおけるものより、組み合わされたマスタースレーブシステムにおける一層多くのADC120の存在が、改善されたオブジェクト位置判定機能を提供する。また、これは、マスターレーダーICチップ206及びスレーブレーダーICチップ208におけるハードウェアリーフタイマが、タイトウィンドウ同期で動作することを確実にする。

The operation of one of the slave

一例において、PCB202は、スレーブレーダーICチップ208のみを含み、ソフトウェアトリガ又はフレームパルスの生成の機能は、マスターレーダーICチップ206におけるMCU102の代わりに、レーダー制御204において機能するマイクロコントローラによって実行される。そのような状況において、ソフトウェアトリガ又はフレームパルスは、全てのスレーブレーダーICチップ208に通信され、残りの動作は上述された例に説明されたものに類似する。

In one example,

図10は、レーダーシステム250の別の例を図示する。レーダーシステム250は、マスターICチップ252及びスレーブICチップ254を含み得る。マスターICチップ252は、マスターモードで動作する図4のレーダーICチップ100のインスタンスとして実装され得る。同様に、スレーブICチップ254は、スレーブモードで動作する図4のレーダーICチップ100のインスタンスとして実装され得る。このように、本明細書に説明されるように、マスターICチップ252及びスレーブICチップ254の各々が、同じICチップ設計の異なるインスタンスとして実装され得る。マスターICチップ252及びスレーブICチップ254の各々は、PCB256上に搭載され得る。また、マスターICチップ252及びスレーブICチップ254の各々の動作のモードは、ソフトウェア構成及び/又はPCB256上のICチップピン構成等により、設定され得る。

FIG. 10 illustrates another

マスターICチップ252はルートタイマ258を含み得、ルートタイマ258は、スレーブICチップ254のトリガセレクタ260に提供される同期信号(図10において「SYNC SIGNAL」として示される)を生成し得る。同期信号は、各フレームの開始、又はフレームのセットの開始において、クロックエッジを提供するフレームパルス信号であり得る。トリガセレクタ260は、同期信号をスタートトリガ信号として、スレーブICチップ254のルートタイマ262に転送し得る。スタートトリガ(同期信号に対応する)における各フレームパルスに応答して、ルートタイマ262は、ルートトリガをリスタート/リセットし得、そのため、ルートトリガが同期信号に調整される。

マスターICチップ252及びスレーブICチップ254の各々は、同期信号によって直接的に又は間接的に制御されるタイミングを用いてレーダー動作を実行するためのマイクロコントローラ(プロセッサ)264及び266を含み得る。レーダー動作は、レーダーチャープのトリガ、BISTのスケジューリング及び実行、マスターICチップ252及びスレーブICチップ254の各々に対してローカル又は外部にあり得るRFレシーバ及びRFトランスミッタ回路の較正等を含み得る。また、マイクロコントローラ264及び266は、マスターICチップ252とスレーブICチップ254との間の相互調整に依存する、ほぼ全てのソフトウェア動作を実行するために用いられ得る。

マスターICチップ252及びスレーブICチップ254の各々は、ハードウェアクロック制御268及び270を含み得る。ハードウェアクロック制御268は、同期信号に基づいてマスターICチップ252に対するリーフタイマを生成し得る。同様に、ハードウェアクロック制御270は、ルートタイマ262からのルートトリガに基づいてスレーブICチップ254に対するリーフタイマを生成し得、ルートトリガは同期信号に基づく。また、同期信号に基づいて、ハードウェアクロック制御268は、マスターICチップ252の一層多くのADC272のアナログ入力のサンプリングインスタンスを制御するために、クロックエッジをイネーブルし得、サンプルを特徴づけるデータが、マスターコントローラ264に対して出力される。同様に、ルートトリガ信号(これは同期信号に基づく)に基づいて、ハードウェアクロック制御270は、スレーブICチップ254の1つ又は複数のADC274のアナログ入力のサンプリングインスタンスを制御するために、クロックエッジをイネーブルし得、サンプルを特徴づけるデータがマイクロコントローラ266に出力され得る。

Each of

また、ハードウェアクロック制御268及び270によって生成されるハードウェアリーフタイマは、マスターICチップ252とスレーブICチップ254との間に相互調整を必要とする、様々な異なる動作に対して用いられ得る。そのような動作には、種々のRF受信及び/又はRF送信回路(又は他の回路)のイネーブル/ディスエーブルが含まれ得る。そのような動作はまた、レーダーチャープ周波数生成、チャープの生成/送信、(マイクロコントローラ264及び266又は外部回路による)ADC出力のデジタル処理等のほぼ全てのレーダー動作の開始、及び/又は、RF送信及び/又はRF受信回路の電力制御等のレーダーチャープに調整された信号生成を含み得る。例えば、電力制御は、RF送信及び/又はRF受信回路を、レーダーチャープの間、高性能、高電力状態に設定し得、レーダーチャープが終了した後、低性能、低電力状態に設定し得る。

Also, the hardware leaf timers generated by hardware clock controls 268 and 270 can be used for a variety of different operations that require mutual coordination between

特許請求の範囲内で、説明した実施形態における変更が可能であり、他の実施形態が可能である。 Modifications in the described embodiments are possible and other embodiments are possible within the scope of the claims.

Claims (14)

同期入力端子と、

スタートトリガ信号に基づいてフレームパルスを生成するルートタイマと、

前記フレームパルスと前記同期入力端子に提供される同期信号との選択される1つに基づいてクロック信号を提供するハードウェアクロックコントローラであって、

前記ルートタイマの出力に結合される第1の入力と、前記同期入力端子に結合される第2の入力と、出力とを有するクロックセレクタと、

前記クロックセレクタの出力に結合される入力と、前記クロック信号を出力するように構成される出力とを有する回路要素と、

を含む、前記ハードウェアクロックコントローラと、

前記回路要素の出力に結合される複数のアナログデジタルコンバータ(ADC)であって、前記複数のADCの各々が、前記クロック信号に基づいて複数の無線周波数(RF)レシーバのそれぞれ1つのRFレシーバの出力をサンプリングするように構成される、前記複数のADCと、

を含む、ICチップ。 An integrated circuit (IC) chip,

a sync input terminal;

a root timer that generates a frame pulse based on the start trigger signal;

a hardware clock controller for providing a clock signal based on a selected one of said frame pulse and a synchronization signal provided to said synchronization input terminal ,

a clock selector having a first input coupled to the root timer output, a second input coupled to the synchronization input terminal, and an output;

a circuit element having an input coupled to the output of the clock selector and an output configured to output the clock signal;

the hardware clock controller comprising:

a plurality of analog-to-digital converters (ADCs) coupled to outputs of said circuit element, each of said plurality of ADCs for each one of a plurality of radio frequency (RF) receivers based on said clock signal; the plurality of ADCs configured to sample outputs;

An IC chip, including

前記ルートタイマから提供される前記フレームパルスに基づいてソフトウェア動作のタイミングを制御するマイクロコントローラを更に含み、

前記ハードウェアクロックコントローラにより提供される前記クロック信号によって制御される動作がタイトウィンドウ内で同期され、前記ソフトウェア動作がルーズウィンドウ内で同期される、ICチップ。 The IC chip according to claim 1,

further comprising a microcontroller controlling timing of software operations based on the frame pulse provided from the root timer;

An IC chip wherein operations controlled by said clock signal provided by said hardware clock controller are synchronized within a tight window and said software operations are synchronized within a loose window.

前記ソフトウェア動作が、複数のRFトランスミッタと前記複数のRFレシーバとの1つ又は複数に対する較正と組み込み自己テスト(BIST)との1つ又は複数を含む、ICチップ。 The IC chip according to claim 2,

The IC chip, wherein the software operations include one or more of calibration and built-in self-test (BIST) for one or more of the plurality of RF transmitters and the plurality of RF receivers.

前記ソフトウェア動作がレーダーチャープを更に含む、ICチップ。 The IC chip according to claim 3,

The IC chip, wherein the software operation further includes radar chirp.

前記ルートタイマが前記同期信号を生成し、前記同期信号が前記ICチップの同期出力端子に提供される、ICチップ。 The IC chip according to claim 1,

The IC chip, wherein the root timer generates the synchronization signal, the synchronization signal being provided to a synchronization output terminal of the IC chip.

前記スタートトリガ信号を提供するために前記同期信号を選択するトリガセレクタを更に含み、

前記同期信号が前記同期入力端子に前記同期出力端子を介してフィードバックされる、ICチップ。 The IC chip according to claim 5,

further comprising a trigger selector that selects the synchronization signal to provide the start trigger signal;

An IC chip, wherein the synchronization signal is fed back to the synchronization input terminal through the synchronization output terminal .

前記クロックセレクタが、スタートクロック信号を生成するために前記フレームパルスと前記同期信号との間で選択し、

前記ハードウェアクロックコントローラが、

前記複数のADCに対する前記ハードウェアクロックコントローラの前記クロック信号を生成するADCクロック生成器と、

前記フレームパルスに基づいてストップクロック信号を生成するハードウェアリーフタイマと、

前記クロックセレクタからの前記スタートクロック信号と前記ハードウェアリーフタイマからの前記ストップクロック信号とに基づいて前記クロック信号を出力する同期ゲータと、

を更に含む、ICチップ。 The IC chip according to claim 1,

said clock selector selecting between said frame pulse and said synchronization signal to generate a start clock signal;

the hardware clock controller

an ADC clock generator that generates the clock signal for the hardware clock controller for the plurality of ADCs;

a hardware leaf timer that generates a stop clock signal based on the frame pulse;

a synchronization gate that outputs the clock signal based on the start clock signal from the clock selector and the stop clock signal from the hardware leaf timer;

An IC chip, further comprising:

前記同期ゲータが、前記スタートクロック信号と前記ストップクロック信号とに基づいて前記クロック信号を前記ADCクロック生成器から前記ADCに出力する1つ又は複数のデジタル論理ゲートを含む、ICチップ。 The IC chip according to claim 7,

An IC chip, wherein the synchronization gate includes one or more digital logic gates that output the clock signal from the ADC clock generator to the ADC based on the start clock signal and the stop clock signal.

前記スタートトリガ信号を提供するために前記同期信号とソフトウェアトリガとの間で選択するトリガセレクタを更に含み、

前記クロックセレクタと前記トリガセレクタとが、前記ICチップの動作のモードを設定するモード選択信号に基づいて制御される、ICチップ。 The IC chip according to claim 7,

further comprising a trigger selector that selects between the synchronization signal and a software trigger to provide the start trigger signal;

An IC chip, wherein the clock selector and the trigger selector are controlled based on a mode selection signal that sets an operation mode of the IC chip.

前記ICチップの動作の前記モードが、シングルモードとマスターモードとスレーブモードとの1つである、ICチップ。 The IC chip according to claim 9,

An IC chip, wherein the mode of operation of the IC chip is one of a single mode, a master mode, and a slave mode.

前記スレーブモードで動作する前記ICチップに応答して、前記トリガセレクタが、別のICチップから受信された同期信号を選択し、前記同期信号を前記スタートトリガ信号として提供する、ICチップ。 The IC chip according to claim 10,

An IC chip wherein, in response to said IC chip operating in said slave mode, said trigger selector selects a synchronization signal received from another IC chip and provides said synchronization signal as said start trigger signal .

オブジェクトの検出を促進するために、前記複数のADCの各々によって出力されるデータを解析するマイクロコントローラを更に含む、ICチップ。 The IC chip according to claim 1,

An IC chip further comprising a microcontroller for analyzing data output by each of said plurality of ADCs to facilitate object detection.

RF信号を出力する複数のトランスミッタと、

複数のレシーバと、

を更に含み、

前記ハードウェアクロックコントローラが、前記トランスミッタと前記レシーバとの各々の動作を制御するために前記クロック信号を提供する、ICチップ。 The IC chip according to claim 1,

a plurality of transmitters that output RF signals;

a plurality of receivers;

further comprising

An IC chip, wherein said hardware clock controller provides said clock signal to control operation of each of said transmitter and said receiver.

前記ハードウェアクロックコントローラが、

前記複数のトランスミッタと前記複数のレシーバとをイネーブル及びディスエーブルすることと、レーダーチャープ周波数生成及び/又は送信と、レーダーチャープに調整された信号生成と、前記複数のADCの出力のデジタル処理との少なくとも1つのタイミングを制御するハードウェアリーフタイマを更に含む、ICチップ。 14. The IC chip according to claim 13,

the hardware clock controller

enabling and disabling the plurality of transmitters and the plurality of receivers; radar chirp frequency generation and/or transmission; radar chirp-tuned signal generation; and digital processing of the outputs of the plurality of ADCs. The IC chip further including a hardware leaf timer that controls at least one timing.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US15/334,979 US10142095B2 (en) | 2016-10-26 | 2016-10-26 | Timing for IC chip |

| US15/334,979 | 2016-10-26 | ||

| PCT/US2017/058621 WO2018081481A1 (en) | 2016-10-26 | 2017-10-26 | Timing for ic chip |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2020513539A JP2020513539A (en) | 2020-05-14 |

| JP2020513539A5 JP2020513539A5 (en) | 2020-12-03 |

| JP7193692B2 true JP7193692B2 (en) | 2022-12-21 |

Family

ID=61971039

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019522737A Active JP7193692B2 (en) | 2016-10-26 | 2017-10-26 | Timing for IC chip |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US10142095B2 (en) |

| EP (1) | EP3532907B1 (en) |

| JP (1) | JP7193692B2 (en) |

| CN (1) | CN109863463B (en) |

| WO (1) | WO2018081481A1 (en) |

Families Citing this family (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10908255B2 (en) * | 2017-03-31 | 2021-02-02 | Remote Sensing Solutions, Inc. | Modular object-oriented digital sub-system architecture with primary sequence control and synchronization |

| US10877919B2 (en) * | 2017-07-21 | 2020-12-29 | Integrated Device Technology, Inc. | Method to synchronize integrated circuits fulfilling functional safety requirements |

| DE102017217805B4 (en) * | 2017-10-06 | 2019-05-02 | Vega Grieshaber Kg | Radar level gauge with synchronization signal on different line types |

| EP3467447B1 (en) * | 2017-10-06 | 2019-09-25 | VEGA Grieshaber KG | Fill level measuring device with multiple radar chips |

| DE102018103088A1 (en) * | 2018-02-12 | 2019-08-14 | Infineon Technologies Ag | SEMICONDUCTOR CHIP AND DEVICE AND METHOD FOR CONTROLLING AT LEAST ONE CHANNEL FOR A RADAR SIGNAL |

| DE102019106030A1 (en) * | 2018-03-22 | 2019-09-26 | Infineon Technologies Ag | RADAR SYSTEM WITH MULTIPLE RADAR CHIPS |

| EP3584601B1 (en) * | 2018-06-18 | 2023-10-18 | NXP USA, Inc. | Time-encoded messaging for radar cascaded synchronization system |

| CN108814560B (en) * | 2018-06-26 | 2021-03-02 | 重庆金山医疗器械有限公司 | Synchronous display method and system for gastroesophageal impedance, pH and visual images |

| EP3591432B1 (en) * | 2018-07-02 | 2021-06-30 | NXP USA, Inc. | Communication unit, integrated circuit and method for clock distribution and synchronization |

| EP3591431B1 (en) | 2018-07-02 | 2021-05-05 | NXP USA, Inc. | Communication unit and method for clock distribution and synchronization |

| EP3591433B1 (en) | 2018-07-02 | 2023-06-14 | NXP USA, Inc. | Communication unit, integrated circuits and method for clock and data synchronization |

| EP3591434B1 (en) * | 2018-07-02 | 2023-07-26 | NXP USA, Inc. | Communication unit, integrated circuits and method for clock and data synchronization |

| DE102018123183A1 (en) * | 2018-09-20 | 2020-03-26 | Infineon Technologies Ag | Radar system, integrated radar circuit and method for a radar system |

| DE102018216538A1 (en) * | 2018-09-27 | 2020-04-02 | Robert Bosch Gmbh | Radar sensor with synchronized high-frequency components |

| US11397239B2 (en) * | 2018-10-24 | 2022-07-26 | Infineon Technologies Ag | Radar sensor FSM low power mode |

| US11681017B2 (en) * | 2019-03-12 | 2023-06-20 | Uhnder, Inc. | Method and apparatus for mitigation of low frequency noise in radar systems |

| US11520030B2 (en) | 2019-03-18 | 2022-12-06 | Nxp Usa, Inc. | High resolution automotive radar system with forward and backward difference co-array processing |

| US11092683B2 (en) * | 2019-03-18 | 2021-08-17 | Nxp Usa, Inc. | Distributed aperture automotive radar system with alternating master radar devices |

| US11269049B2 (en) | 2019-03-18 | 2022-03-08 | Nxp Usa, Inc. | Distributed aperture automotive radar system |

| US11782148B2 (en) | 2019-03-25 | 2023-10-10 | Texas Instruments Incorporated | Radar system |

| US11531085B2 (en) * | 2019-05-10 | 2022-12-20 | Infineon Technologies Ag | On-chip noise reduction and power consumption distribution for a radar system |

| CN112764032A (en) * | 2019-10-21 | 2021-05-07 | 常州星宇车灯股份有限公司 | Vehicle driving danger early warning system and control method thereof |

| US11789076B2 (en) * | 2019-11-12 | 2023-10-17 | Mediatek Inc. | Apparatus and method of monitoring chip process variation and performing dynamic adjustment for multi-chip system by pulse width |

| US11808883B2 (en) * | 2020-01-31 | 2023-11-07 | Infineon Technologies Ag | Synchronization of multiple mmWave devices |

| US11888554B2 (en) | 2020-09-23 | 2024-01-30 | Nxp Usa, Inc. | Automotive MIMO radar system using efficient difference co-array processor |

| WO2022080014A1 (en) * | 2020-10-13 | 2022-04-21 | ソニーセミコンダクタソリューションズ株式会社 | Sensor control system and sensor |

| KR102597168B1 (en) | 2021-08-13 | 2023-11-02 | 삼성전기주식회사 | Analog to digital conversion apparatus and camera module including thereof |

| US11561299B1 (en) * | 2022-06-03 | 2023-01-24 | Oculii Corp. | System and method for multi-waveform radar tracking |

| US12113444B2 (en) | 2022-07-01 | 2024-10-08 | Stmicroelectronics S.R.L. | Bidirectional DC/DC converter |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004080229A (en) | 2002-08-14 | 2004-03-11 | Oki Electric Ind Co Ltd | Clock synchronization system, clock synchronization method and clock extractor |

| JP2008032498A (en) | 2006-07-27 | 2008-02-14 | Denso Corp | Signal processing apparatus |

| US20120005516A1 (en) | 2010-07-02 | 2012-01-05 | International Business Machines Corporation | Synchronous clock stop in a multi nodal computer system |

| US20140351359A1 (en) | 2013-05-24 | 2014-11-27 | Arm Limited | Data processing apparatus and method for communicating between a master device and an asychronous slave device via an interface |

| US20160018511A1 (en) | 2014-07-17 | 2016-01-21 | Texas Instruments Incorporated | Distributed Radar Signal Processing in a Radar System |

| JP2017044597A (en) | 2015-08-27 | 2017-03-02 | ラピスセミコンダクタ株式会社 | Semiconductor device |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02148916A (en) * | 1988-11-29 | 1990-06-07 | Yokogawa Electric Corp | A/d converter |

| US6539489B1 (en) * | 2000-03-31 | 2003-03-25 | Siemens Aktiengesellshaft | Apparatus, method and system for synchronizing slave system operations to master system clocking signals in a master-slave asynchronous communication system |

| US20040225814A1 (en) | 2001-05-29 | 2004-11-11 | Ervin Joseph J. | Method and apparatus for constructing wired-AND bus systems |

| US6857035B1 (en) | 2001-09-13 | 2005-02-15 | Altera Corporation | Methods and apparatus for bus mastering and arbitration |

| US7049994B2 (en) * | 2002-03-22 | 2006-05-23 | Thine Electronics, Inc. | Semiconductor integrated circuit |

| GB2401207B (en) | 2003-04-30 | 2006-11-22 | Agilent Technologies Inc | Master slave arrangement |

| US7257756B2 (en) | 2004-03-31 | 2007-08-14 | Intel Corporation | Digital frequency synthesis clocked circuits |

| JP4626238B2 (en) | 2004-09-15 | 2011-02-02 | 日本電気株式会社 | RADIO COMMUNICATION SYSTEM, RADIO COMMUNICATION DEVICE, RADAR DETECTION CIRCUIT AND RADAR DETECTION METHOD USED FOR THEM |

| US7747222B2 (en) * | 2005-12-09 | 2010-06-29 | Marvell World Trade Ltd. | Detection and estimation of radio frequency variations |

| US7870455B2 (en) | 2007-12-12 | 2011-01-11 | Infineon Technologies Ag | System-on-chip with master/slave debug interface |

| US7913012B2 (en) | 2007-12-31 | 2011-03-22 | Silicon Laboratories, Inc. | System and method for connecting a master device with multiple groupings of slave devices via a LINBUS network |

| US20090323880A1 (en) * | 2008-06-27 | 2009-12-31 | Microsoft Corporation | Synchronization of real time data within deterministic clock edge |

| US8744336B2 (en) * | 2008-08-27 | 2014-06-03 | Qualcomm Incorporated | Interference detection apparatus and method |

| US9124277B2 (en) * | 2011-04-20 | 2015-09-01 | Freescale Semiconductor, Inc. | System and method for clock signal generation |

| US20160294591A1 (en) | 2015-03-31 | 2016-10-06 | Alcatel-Lucent Usa Inc. | Multichannel receiver |

| US9204312B2 (en) | 2013-11-27 | 2015-12-01 | Freescale Semiconductor, Inc. | Method for adding leaf node to multi-node base station |

| EP2881752B1 (en) | 2013-12-03 | 2017-05-10 | Nxp B.V. | A multichip automotive radar system, a radar chip for such as system, and a method of operating such a system |

| US9739873B2 (en) * | 2014-08-19 | 2017-08-22 | Navico Holding As | Range sidelobe suppression |

| US9846665B2 (en) | 2014-11-05 | 2017-12-19 | Stmicroelectronics Asia Pacific Pte Ltd | Chip synchronization by a master-slave circuit |

-

2016

- 2016-10-26 US US15/334,979 patent/US10142095B2/en active Active

-

2017

- 2017-10-26 WO PCT/US2017/058621 patent/WO2018081481A1/en unknown

- 2017-10-26 EP EP17866185.6A patent/EP3532907B1/en active Active

- 2017-10-26 JP JP2019522737A patent/JP7193692B2/en active Active

- 2017-10-26 CN CN201780065770.6A patent/CN109863463B/en active Active

-

2018

- 2018-11-26 US US16/200,061 patent/US10659078B2/en active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004080229A (en) | 2002-08-14 | 2004-03-11 | Oki Electric Ind Co Ltd | Clock synchronization system, clock synchronization method and clock extractor |

| JP2008032498A (en) | 2006-07-27 | 2008-02-14 | Denso Corp | Signal processing apparatus |

| US20120005516A1 (en) | 2010-07-02 | 2012-01-05 | International Business Machines Corporation | Synchronous clock stop in a multi nodal computer system |

| US20140351359A1 (en) | 2013-05-24 | 2014-11-27 | Arm Limited | Data processing apparatus and method for communicating between a master device and an asychronous slave device via an interface |

| US20160018511A1 (en) | 2014-07-17 | 2016-01-21 | Texas Instruments Incorporated | Distributed Radar Signal Processing in a Radar System |

| JP2017044597A (en) | 2015-08-27 | 2017-03-02 | ラピスセミコンダクタ株式会社 | Semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| EP3532907B1 (en) | 2023-06-28 |

| EP3532907A1 (en) | 2019-09-04 |

| WO2018081481A1 (en) | 2018-05-03 |

| JP2020513539A (en) | 2020-05-14 |

| CN109863463B (en) | 2023-05-05 |

| CN109863463A (en) | 2019-06-07 |

| US10142095B2 (en) | 2018-11-27 |

| EP3532907A4 (en) | 2020-02-19 |

| US20180115409A1 (en) | 2018-04-26 |

| US20190097651A1 (en) | 2019-03-28 |

| US10659078B2 (en) | 2020-05-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7193692B2 (en) | Timing for IC chip | |

| US20240288539A1 (en) | Multi-chip synchronization for digital radars | |

| EP3611540B1 (en) | Apparatus and methods for synchronization of radar chips | |

| CN106574967B (en) | Loopback technique for synchronizing oscillator signals in radar | |

| CN110740029B (en) | Communication unit, integrated circuit and method for clock and data synchronization | |

| US9547071B2 (en) | Radar transceiver | |

| CN110231599B (en) | Radar apparatus, radar system, and method for generating sampling clock signal | |

| JP6643422B2 (en) | A radar front end that monitors high-frequency oscillators | |

| JP2020513539A5 (en) | ||

| GB2470591A (en) | Pulse width modulation synchronisation of switched mode power converters | |

| EP3859376A1 (en) | Synchronization of multiple mmwave devices | |

| EP3648348A1 (en) | Duty cycle monitor circuit and method for duty cycle monitoring | |

| CN104954009B (en) | Output control circuit for semiconductor device and the output driving circuit including it | |

| CN110736966B (en) | Communication unit, integrated circuit and method for synchronizing clock and data | |

| CN110673124B (en) | Communication unit and method for clock distribution and synchronization | |

| JP2018059871A (en) | Radar system | |

| CN106526582B (en) | Double base Radar system | |

| CN112817368B (en) | Chip synchronization method and related device | |

| CN117155530B (en) | Trigger synchronization precision improving method of cascade trigger system | |

| US20230176180A1 (en) | Efficient programming model for real-time rader sequencing in a radar device | |

| CN117675159A (en) | Cascading synchronization method and cascading system for millimeter wave radar receiving and transmitting front-end chip | |

| CN118688723A (en) | Trigger signaling by clock signal in cascaded radar systems | |

| JP2018046462A (en) | Array Antenna Device | |

| PL222785B1 (en) | Method and system for synchronizing of excitation signals |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20190426 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20201019 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20201019 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20210218 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210323 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210602 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210728 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20211027 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20211227 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220127 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220511 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20220516 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220808 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20221109 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20221114 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7193692 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |