JP7048229B2 - Pachinko machine - Google Patents

Pachinko machine Download PDFInfo

- Publication number

- JP7048229B2 JP7048229B2 JP2017179233A JP2017179233A JP7048229B2 JP 7048229 B2 JP7048229 B2 JP 7048229B2 JP 2017179233 A JP2017179233 A JP 2017179233A JP 2017179233 A JP2017179233 A JP 2017179233A JP 7048229 B2 JP7048229 B2 JP 7048229B2

- Authority

- JP

- Japan

- Prior art keywords

- lottery

- game

- state

- sub

- flag

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Game Rules And Presentations Of Slot Machines (AREA)

Description

本発明は、遊技機に関する。 The present invention relates to a gaming machine.

従来、複数の図柄がそれぞれの表面に設けられた複数のリールと、スタートスイッチと、ストップスイッチと、各リールに対応して設けられたステッピングモータと、制御部とを備えた、パチスロと呼ばれる遊技機が知られている。スタートスイッチは、メダルやコインなどの遊技媒体が遊技機に投入された後、スタートレバーが遊技者により操作されたこと(以下、「開始操作」ともいう)を検出し、全てのリールの回転の開始を要求する信号を出力する。ストップスイッチは、各リールに対応して設けられたストップボタンが遊技者により押されたこと(以下、「停止操作」ともいう)を検出し、該当するリールの回転の停止を要求する信号を出力する。ステッピングモータは、その駆動力を対応するリールに伝達する。また、制御部は、スタートスイッチ及びストップスイッチにより出力された信号に基づいて、ステッピングモータの動作を制御し、各リールの回転動作及び停止動作を行う。 Conventionally, a game called a pachislot machine equipped with a plurality of reels having a plurality of symbols on each surface, a start switch, a stop switch, a stepping motor provided corresponding to each reel, and a control unit. The machine is known. The start switch detects that the start lever is operated by the player (hereinafter, also referred to as "start operation") after the game medium such as a medal or coin is inserted into the game machine, and the rotation of all reels is rotated. Output a signal requesting a start. The stop switch detects that the stop button provided corresponding to each reel is pressed by the player (hereinafter, also referred to as "stop operation"), and outputs a signal requesting the stop of rotation of the corresponding reel. do. The stepping motor transfers its driving force to the corresponding reel. Further, the control unit controls the operation of the stepping motor based on the signals output by the start switch and the stop switch, and performs the rotation operation and the stop operation of each reel.

このような遊技機では、開始操作が検出されると、プログラム上で乱数を用いた抽籤処理(以下、「内部抽籤処理」という)が行われ、その抽籤の結果(以下、「内部当籤役」という)と停止操作のタイミングとに基づいてリールの回転の停止を行う。そして、全てのリールの回転が停止され、入賞の成立に係る図柄の組合せ(表示役)が表示されると、その図柄の組合せに対応する特典が遊技者に付与される。なお、遊技者に付与される特典の例としては、遊技媒体(メダル等)の払い出し、遊技媒体を消費することなく再度、内部抽籤処理を行う再遊技(以下、「リプレイ」ともいう)の作動、遊技媒体の払い出し機会が増加するボーナスゲームの作動等を挙げることができる。 In such a gaming machine, when a start operation is detected, a lottery process using random numbers (hereinafter referred to as "internal lottery process") is performed on the program, and the result of the lottery (hereinafter referred to as "internal winning combination") is performed. The rotation of the reel is stopped based on the timing of the stop operation. Then, when the rotation of all the reels is stopped and the combination of symbols (display combination) related to the establishment of the winning is displayed, the player is given a privilege corresponding to the combination of the symbols. As an example of the privilege given to the player, the payout of the game medium (medals, etc.) and the operation of the re-game (hereinafter, also referred to as "replay") in which the internal lottery process is performed again without consuming the game medium. , The operation of a bonus game that increases the chances of paying out game media can be mentioned.

また、従来、上記構成の遊技機において、特定の小役(遊技媒体の払い出しに係る役)の成立をランプ等でナビゲートする機能、すなわち、アシストタイム(以下、「AT」という)の機能を備える遊技機が開発されている。また、従来、特定の図柄組合せが表示された場合にリプレイの当籤確率が通常時より高い遊技状態が作動する機能、すなわち、リプレイタイム(以下、「RT」という)の機能を備える遊技機も開発されている。さらに、従来、ATとRTとが同時に作動するアシストリプレイタイム(以下、「ART」という)の機能を備えたパチスロが開発されている。 Further, conventionally, in a gaming machine having the above configuration, a function of navigating the establishment of a specific small winning combination (a winning combination related to paying out a gaming medium) with a lamp or the like, that is, a function of assist time (hereinafter referred to as "AT") is provided. A gaming machine is being developed. In addition, we have also developed a gaming machine that has a function to operate a gaming state in which the winning probability of replay is higher than normal when a specific symbol combination is displayed, that is, a function of replay time (hereinafter referred to as "RT"). Has been done. Further, conventionally, a pachi-slot machine having an assist replay time (hereinafter referred to as "ART") function in which AT and RT operate at the same time has been developed.

上述した遊技機は、通常、内部当籤役の決定、各リールの回転及び停止、入賞の有無の判定等の遊技機の主な遊技動作を制御する回路(主制御回路)が実装された主制御基板と、映像の表示等による演出動作を制御する回路(副制御回路)が実装された副制御基板とを備える。そして、遊技動作は、主制御回路に搭載されたCPU(Central Processing Unit)により制御される。この際、CPUの制御により、主制御回路のROM(Read Only Memory)に記憶されたプログラム及び各種テーブルデータ等が主制御回路のRAM(Random Access Memory)に展開され、各種遊技動作に関する処理が実行される。 The above-mentioned gaming machine is usually a main control equipped with a circuit (main control circuit) for controlling the main gaming operation of the gaming machine such as determination of an internal winning combination, rotation and stop of each reel, and determination of presence / absence of winning. It includes a board and a sub-control board on which a circuit (sub-control circuit) for controlling an effect operation by displaying an image or the like is mounted. The game operation is controlled by a CPU (Central Processing Unit) mounted on the main control circuit. At this time, under the control of the CPU, the program stored in the ROM (Read Only Memory) of the main control circuit, various table data, etc. are expanded in the RAM (Random Access Memory) of the main control circuit, and processing related to various game operations is executed. Will be done.

また、従来、上記構成の遊技機において、ソフトウエアによるタイマー減算処理で制御される遊技機が知られている(例えば、特許文献1参照)。 Further, conventionally, in a gaming machine having the above configuration, a gaming machine controlled by a timer subtraction process by software is known (see, for example, Patent Document 1) .

ところで、従来、上述した遊技機特有の制限として、主制御回路のプログラム容量が、規則により小容量に制限されている。さらに、近年、遊技性の複雑化により主制御回路のROMの容量が圧迫されており、主制御回路で管理する処理プログラムやテーブルなどの容量削減が求められている。 By the way, conventionally, as a limitation peculiar to the above-mentioned gaming machine, the program capacity of the main control circuit is limited to a small capacity by a rule. Further, in recent years, the capacity of the ROM of the main control circuit has been squeezed due to the complexity of playability, and there is a demand for reducing the capacity of processing programs and tables managed by the main control circuit .

本発明は、上記課題を解決するためになされたものであり、本発明の目的は、主制御回路で管理する処理プログラムやテーブルなどの容量を削減して主制御回路のROMの空き容量を増やし、該増えた容量分のROMの空き領域を利用して遊技性を高めることが可能な遊技機を提供することである。 The present invention has been made to solve the above problems, and an object of the present invention is to reduce the capacity of processing programs and tables managed by the main control circuit to increase the free space of the ROM of the main control circuit. The present invention is to provide a gaming machine capable of enhancing game playability by utilizing the free area of the ROM corresponding to the increased capacity .

上記課題を解決するために、本発明では、以下のような構成の遊技機を提供する。 In order to solve the above problems, the present invention provides a gaming machine having the following configuration.

遊技動作を制御するための演算処理を行う演算処理手段(例えば、後述のメインCPU101)と、

前記演算処理手段による前記演算処理の実行に必要な情報が記憶された第1記憶手段(例えば、後述のメインROM102)と、

前記演算処理手段による前記演算処理の実行に必要な情報が記憶される第2記憶手段(例えば、後述のメインRAM103)と、を備え、

前記演算処理手段は、

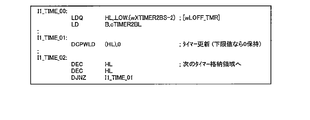

2バイトのソフトタイマーのタイマー値の計数処理(例えば、後述のタイマー更新処理)において、

更新命令、下限判定命令及び判断分岐命令を一つの命令で実行可能な所定の更新命令(例えば、後述の「DCPWLD」命令)を実行することにより、現在の前記ソフトタイマーのタイマー値と前記タイマー値の下限値とを比較するとともに、現在の前記ソフトタイマーのタイマー値が前記下限値より大きければ、前記ソフトタイマーのタイマー値を減算更新し、現在の前記ソフトタイマーのタイマー値が前記下限値以下であれば、前記ソフトタイマーのタイマー値を前記下限値に保持し、

その後、前記第2記憶手段内の前記ソフトタイマーの更新開始アドレスを2バイト分更新し、

前記所定の更新命令では、オペランドとして、前記ソフトタイマーの更新開始アドレスを示す情報、及び、前記タイマー値の下限値が指定され、

前記演算処理手段は、前記演算処理手段による前記演算処理の実行時にデータが格納される2つの汎用レジスタを組み合わせて構成されたペアレジスタと、前記演算処理手段による前記演算処理の実行時に格納されたデータにより前記第2記憶手段内の上位側のアドレスを指定可能な1バイトの拡張レジスタ(例えば、後述のQレジスタ)と、を有し、

前記演算処理手段は、前記拡張レジスタを使用した特定のロード命令(例えば、後述の「LDQ」命令)を実行することにより、前記ソフトタイマーのタイマー値の格納領域のアドレスデータを前記ペアレジスタに格納し、

前記第1記憶手段には、第1の記憶領域(例えば、後述の遊技用ROM領域)及び第2の記憶領域(例えば、後述の規定外ROM領域)が設けられ、

前記第1の記憶領域には、前記計数処理を実行するためのプログラムが記憶され、

前記第2の記憶領域には、試験に用いられる信号を制御するためのプログラムが記憶され、

前記演算処理手段、前記第1記憶手段及び前記第2記憶手段が実装され、かつ、特定の電子部品が実装可能な主制御部をさらに備え、

試験信号出力処理では、

前記主制御部に前記特定の電子部品が実装されている場合に、生成された制御信号が遊技機の外部に出力され、

前記特定の電子部品が前記主制御部に実装されていなくても、前記制御信号が生成され、該生成された制御信号のためのデータが、対象となる出力ポートにセットされる

ことを特徴とする遊技機。

An arithmetic processing means (for example, the

A first storage means (for example, the

A second storage means (for example, a

The arithmetic processing means is

In the timer value counting process of a 2-byte soft timer (for example, the timer update process described later),

By executing a predetermined update instruction (for example, "DCPWLD" instruction described later) that can execute an update instruction, a lower limit determination instruction, and a determination branch instruction with one instruction, the current timer value of the soft timer and the timer value. If the current timer value of the soft timer is larger than the lower limit value, the timer value of the soft timer is subtracted and updated, and the current timer value of the soft timer is equal to or less than the lower limit value. If there is, the timer value of the soft timer is held at the lower limit value,

After that, the update start address of the soft timer in the second storage means is updated by 2 bytes.

In the predetermined update instruction, information indicating the update start address of the soft timer and the lower limit of the timer value are specified as operands.

The arithmetic processing means is stored in a pair register configured by combining two general-purpose registers in which data is stored when the arithmetic processing means executes the arithmetic processing, and when the arithmetic processing means executes the arithmetic processing. It has a 1-byte extension register (for example, a Q register described later) that can specify an upper address in the second storage means by data.

The arithmetic processing means stores the address data of the timer value storage area of the soft timer in the pair register by executing a specific load instruction (for example, a “LDQ” instruction described later) using the expansion register. death,

The first storage means is provided with a first storage area (for example, a gaming ROM area described later) and a second storage area (for example, an unspecified ROM area described later).

A program for executing the counting process is stored in the first storage area.

A program for controlling the signal used for the test is stored in the second storage area.

A main control unit to which the arithmetic processing means, the first storage means, and the second storage means are mounted and to which a specific electronic component can be mounted is further provided.

In test signal output processing,

When the specific electronic component is mounted on the main control unit, the generated control signal is output to the outside of the gaming machine.

Even if the specific electronic component is not mounted on the main control unit, the control signal is generated and the data for the generated control signal is set in the target output port. A game machine to play.

上記構成の本発明の遊技機によれば、主制御回路で管理する処理プログラムやテーブルなどの容量を削減して主制御回路のROM(第1記憶手段)の空き容量を増やし、該増えた容量分のROMの空き領域を利用して遊技性を高めることができる。 According to the gaming machine of the present invention having the above configuration, the capacity of the processing program and the table managed by the main control circuit is reduced to increase the free capacity of the ROM (first storage means) of the main control circuit, and the increased capacity is increased. It is possible to improve the playability by using the free area of the ROM for the minute .

以下、本発明の一実施形態に係る遊技機としてパチスロを例に挙げ、図面を参照しながら、その構成及び動作について説明する。なお、本実施形態では、ボーナス作動機能及びART機能を備えたパチスロについて説明する。 Hereinafter, a pachi-slot machine will be described as an example of a gaming machine according to an embodiment of the present invention, and its configuration and operation will be described with reference to the drawings. In this embodiment, a pachi-slot machine having a bonus operation function and an ART function will be described.

<機能フロー>

まず、図1を参照して、パチスロの機能フローについて説明する。本実施形態のパチスロでは、遊技を行うための遊技媒体としてメダルを用いる。なお、遊技媒体としては、メダル以外にも、例えば、コイン、遊技球、遊技用のポイントデータ又はトークン等を適用することもできる。

<Functional flow>

First, the functional flow of the pachislot machine will be described with reference to FIG. In the pachislot machine of the present embodiment, a medal is used as a game medium for playing a game. In addition to medals, coins, game balls, game point data, tokens, and the like can also be applied as the game medium.

遊技者によりパチスロにメダルが投入され、スタートレバーが操作されると、予め定められた数値範囲(例えば、0~65535)の乱数から1つの値(以下、乱数値という)が抽出される。 When a medal is inserted into a pachislot machine by a player and the start lever is operated, one value (hereinafter referred to as a random number value) is extracted from a random number in a predetermined numerical range (for example, 0 to 65535).

内部抽籤手段は、抽出された乱数値に基づいて抽籤を行い、内部当籤役を決定する。この内部抽籤手段は、後述の主制御回路が備える各種処理手段(処理機能)の一つである。内部当籤役の決定により、後述の有効ライン(入賞判定ライン)に沿って表示を行うことを許可する図柄の組合せが決定される。なお、図柄の組合せの種別としては、メダルの払い出し、再遊技(リプレイ)の作動、ボーナスの作動等といった特典が遊技者に与えられる「入賞」に係るものと、それ以外のいわゆる「はずれ」に係るものとが設けられる。なお、以下では、メダルの払い出しに係る役を「小役」と称し、再遊技(リプレイ)の作動に係る役を「リプレイ役」と称する。また、ボーナスの作動(ボーナスゲーム)に係る役を「ボーナス役」ともいう。 The internal lottery means draws lots based on the extracted random number values, and determines the internal winning combination. This internal lottery means is one of various processing means (processing functions) included in the main control circuit described later. By determining the internal winning combination, the combination of symbols that are permitted to be displayed along the valid line (winning determination line) described later is determined. The types of symbol combinations are those related to "winning" where benefits such as medal payout, replay operation, bonus operation, etc. are given to the player, and other so-called "missing". Such things are provided. In the following, the role related to the payout of medals will be referred to as a "small role", and the role related to the operation of the replay (replay) will be referred to as a "replay role". In addition, the role related to the operation of the bonus (bonus game) is also referred to as a "bonus role".

また、スタートレバーが操作されると、複数のリールの回転が行われる。その後、遊技者により所定のリールに対応するストップボタンが押されると、リール停止制御手段は、内部当籤役とストップボタンが押されたタイミングとに基づいて、該当するリールの回転を停止する制御を行う。このリール停止制御手段は、後述の主制御回路が備える各種処理手段(処理機能)の一つである。 Further, when the start lever is operated, a plurality of reels are rotated. After that, when the stop button corresponding to the predetermined reel is pressed by the player, the reel stop control means controls to stop the rotation of the corresponding reel based on the internal winning combination and the timing when the stop button is pressed. conduct. This reel stop control means is one of various processing means (processing functions) included in the main control circuit described later.

パチスロでは、基本的に、ストップボタンが押されたときから規定時間(190msec)内に、該当するリールの回転を停止する制御が行われる。本実施形態では、この規定時間内にリールの回転に伴って移動する図柄の数を「滑り駒数」という。そして、本実施形態では、規定期間が190msecである場合には、滑り駒数の最大数(最大滑り駒数)を図柄4個分に定める。 In pachislot, basically, control is performed to stop the rotation of the corresponding reel within a specified time (190 msec) from the time when the stop button is pressed. In the present embodiment, the number of symbols that move with the rotation of the reel within this specified time is referred to as "the number of sliding pieces". Then, in the present embodiment, when the specified period is 190 msec, the maximum number of sliding pieces (maximum number of sliding pieces) is set for four symbols.

リール停止制御手段は、入賞に係る図柄の組合せ表示を許可する内部当籤役が決定されているときは、通常、190msec(図柄4駒分)の規定時間内に、その図柄の組合せが有効ラインに沿って極力表示されるようにリールの回転を停止させる。また、リール停止制御手段は、規定時間を利用して、内部当籤役によってその表示が許可されていない図柄の組合せが有効ラインに沿って表示されないようにリールの回転を停止させる。 When the internal winning combination that permits the combination display of the symbols related to the winning is determined, the reel stop control means usually sets the combination of the symbols to the effective line within the specified time of 190 msec (for 4 symbols). Stop the rotation of the reel so that it is displayed as much as possible along the line. Further, the reel stop control means uses a specified time to stop the rotation of the reel so that the combination of symbols whose display is not permitted by the internal winning combination is not displayed along the valid line.

このようにして、複数のリールの回転がすべて停止されると、入賞判定手段は、有効ラインに沿って表示された図柄の組合せが、入賞に係るものであるか否かの判定を行う。この入賞判定手段もまた、後述の主制御回路が備える各種処理手段(処理機能)の一つである。そして、表示された図柄の組合せが、入賞判定手段により入賞に係るものであると判定されると、メダルの払い出し等の特典が遊技者に与えられる。パチスロでは、以上のような一連の流れが1回の遊技(単位遊技)として行われる。 In this way, when all the rotations of the plurality of reels are stopped, the winning determination means determines whether or not the combination of symbols displayed along the valid line is related to the winning. This winning determination means is also one of various processing means (processing functions) included in the main control circuit described later. Then, when it is determined by the winning determination means that the combination of the displayed symbols is related to the winning, a privilege such as a medal payout is given to the player. In pachislot, the above series of flows is performed as one game (unit game).

また、パチスロでは、前述した一連の遊技動作の流れの中で、表示装置などによる映像の表示、各種ランプによる光の出力、スピーカによる音の出力、或いは、これらの組合せを利用して様々な演出が行われる。 In addition, in pachislot, in the flow of the above-mentioned series of game operations, various effects are produced by displaying images by a display device, outputting light by various lamps, outputting sounds by speakers, or a combination of these. Is done.

具体的には、スタートレバーが操作されると、上述した内部当籤役の決定に用いられた乱数値とは別に、演出用の乱数値が抽出される。演出用の乱数値が抽出されると、演出内容決定手段は、内部当籤役に対応づけられた複数種類の演出内容の中から今回実行する演出を抽籤により決定する。この演出内容決定手段は、後述の副制御回路が備える各種処理手段(処理機能)の一つである。 Specifically, when the start lever is operated, a random value for effect is extracted in addition to the random value used for determining the internal winning combination described above. When the random value for the effect is extracted, the effect content determining means determines the effect to be executed this time from a plurality of types of effect contents associated with the internal winning combination by lottery. This effect content determining means is one of various processing means (processing functions) included in the sub-control circuit described later.

次いで、演出内容決定手段により演出内容が決定されると、演出実行手段は、リールの回転開始時、各リールの回転停止時、入賞の有無の判定時等の各契機に連動させて対応する演出を実行する。このように、パチスロでは、例えば、内部当籤役に対応づけられた演出内容を実行することによって、決定された内部当籤役(言い換えると、狙うべき図柄の組合せ)を知る機会又は予想する機会が遊技者に提供され、遊技者の興味の向上を図ることができる。 Next, when the effect content is determined by the effect content determining means, the effect execution means responds in conjunction with each opportunity such as when the reel rotation starts, when the rotation of each reel stops, and when it is determined whether or not there is a prize. To execute. In this way, in pachislot, for example, by executing the production content associated with the internal winning combination, the opportunity to know or anticipate the determined internal winning combination (in other words, the combination of symbols to be aimed at) is a game. It is provided to the player and can improve the interest of the player.

<パチスロの構造>

次に、図2~図4を参照して、本発明の一実施形態に係るパチスロの構造について説明する。

<Structure of pachislot>

Next, the structure of the pachi-slot machine according to the embodiment of the present invention will be described with reference to FIGS. 2 to 4.

[外観構造]

図2は、パチスロ1の外部構造を示す斜視図である。

[Appearance structure]

FIG. 2 is a perspective view showing the external structure of the pachi-

パチスロ1は、図2に示すように、外装体(遊技機本体)2を備える。外装体2は、リールや回路基板等を収容するキャビネット2aと、キャビネット2aの開口を開閉可能に取り付けられるフロントドア2bとを有する。

As shown in FIG. 2, the pachi-

キャビネット2aの内部には、3つのリール3L,3C,3R(変動表示手段、表示列)が横一列に並べて設けられている。以下、各リール3L,3C,3R(メインリール)を、それぞれ左リール3L、中リール3C、右リール3Rともいう。各リール3L,3C,3Rは、円筒状に形成されたリール本体と、リール本体の周面に装着された透光性のシート材を有する。そして、シート材の表面には、複数(例えば20個)の図柄が周方向(リールの回転方向)に沿って所定の間隔をあけて描かれている。

Inside the

フロントドア2bは、ドア本体9と、フロントパネル10と、腰部パネル12と、台座部13とを備える。ドア本体9は、ヒンジ(不図示)を用いてキャビネット2aに開閉可能に取り付けられる。ヒンジは、パチスロ1の前方側(遊技者側)から見て、ドア本体9の左側の側端部に設けられる。

The

フロントパネル10は、ドア本体9の上部に設けられている。このフロントパネル10は、開口10aを有する枠状部材で構成される。フロントパネル10の開口10aは、表示装置カバー30によって塞がれ、表示装置カバー30は、キャビネット2aの内部に配置された後述の表示装置11と対向して配置される。

The

表示装置カバー30は、黒色の半透明な合成樹脂により形成される。それゆえ、遊技者は、後述の表示装置11により表示された映像(画像)を、表示装置カバー30を介して視認することができる。 また、本実施形態では、表示装置カバー30を黒色の半透明な合成樹脂で形成することにより、キャビネット2a内への外光の入り込みを抑制して、表示装置11により表示された映像(画像)を鮮明に視認できるようにしている。

The

フロントパネル10には、ランプ群21が設けられている。ランプ群21は、例えば、遊技者側から見て、フロントパネル10の上部に設けられたランプ21a、21bを含む。ランプ群21を構成する各ランプは、LED(Light Emitting Diode)等で構成され(後述の図7中のLED群85参照)、演出内容に対応するパターンで、光を点灯及び消灯する。

The

腰部パネル12は、ドア本体9の略中央部に設けられる。腰部パネル12は、任意の画像が描かれた装飾パネルと、この装飾パネルを背面側から照明するための光を出射する光源(後述のLED群85に含まれるLED)とを有する。

The

台座部13は、フロントパネル10と腰部パネル12との間に設けられる。台座部13には、図柄表示領域4と、遊技者による操作の対象となる各種装置(メダル投入口14、MAXベットボタン15a、1ベットボタン15b、スタートレバー16、3つのストップボタン17L,17C,17R、精算ボタン(不図示)等)とが設けられる。

The

図柄表示領域4は、正面から見て、3つのリール3L,3C,3Rに重畳する領域で、かつ、3つのリール3L,3C,3Rより遊技者側の位置に配置されており、3つのリール3L,3C,3Rを視認可能にするサイズを有する。この図柄表示領域4は、表示窓としての機能を果たすものであり、その背後に設けられた各リール3L,3C,3Rを視認することが可能な構成になっている。以下、図柄表示領域4を、リール表示窓4という。

The

リール表示窓4は、その背後に設けられた3つのリール3L,3C,3Rの回転が停止されたとき、各リールの周面に設けられた複数の図柄のうち、連続して配置された3つの図柄がその枠内に表示されるように構成されている。すなわち、3つのリール3L,3C,3Rの回転が停止されたとき、リール表示窓4の枠内には、リール毎に上段、中段及び下段の各領域にそれぞれ1個の図柄(合計で3個)が表示される(リール表示窓4の枠内には、3行×3列の態様で図柄が表示される)。そして、本実施形態では、リール表示窓4の枠内において、左リール3Lの中段領域、中リール3Cの中段領域、及び、右リール3Rの中段領域を結ぶ擬似的なライン(センターライン)を、入賞か否かの判定を行う有効ラインとして定義する。

The

リール表示窓4は、台座部13に設けられた枠部材31の開口により形成される。また、リール表示窓4を画成する枠部材31の下方には、略水平面の台座領域が設けられる。そして、遊技者側から見て、台座領域の右側にはメダル投入口14が設けられ、左側にはMAXベットボタン15a及び1ベットボタン15bが設けられる。

The

メダル投入口14は、遊技者によって外部からパチスロ1に投下されるメダルを受け入れるために設けられる。メダル投入口14から受け入れられたメダルは、予め設定された所定枚数(例えば3枚)を上限として1回の遊技に使用され、所定枚数を超えたメダルの枚数分は、パチスロ1の内部に預けることができる(いわゆるクレジット機能(遊技媒体貯留手段))。

The

MAXベットボタン15a及び1ベットボタン15bは、キャビネット2aの内部に預けられているメダルから1回の遊技に使用する枚数を決定するために設けられる。なお、MAXベットボタン15aの内部には、メダル投入が可能な時に点灯するベットボタンLED(不図示)が設けられている。また、精算ボタンは、パチスロ1の内部に預けられているメダルを外部に引き出す(排出する)ために設けられる。

The

なお、遊技者がMAXベットボタン15aを押下操作すると、単位遊技のベット枚数(3枚)のメダルが投入され、有効ラインが有効化される。一方、1ベットボタン15bが1回、押下操作される度に1枚のメダルが投入される。1ベットボタン15bが3回操作されると、単位遊技のベット枚数(3枚)のメダルが投入され、有効ラインが有効化される。

When the player presses the

なお、以下では、MAXベットボタン15aの操作、1ベットボタン15bの操作及びメダル投入口14にメダルを投入する操作(遊技を行うためにメダルを投入する操作)をいずれも「投入操作」という。

In the following, the operation of the

スタートレバー16は、全てのリール(3L,3C,3R)の回転を開始するために設けられる。ストップボタン17L,17C,17Rは、それぞれ、左リール3L、中リール3C、右リール3Rに対応づけて設けられ、各ストップボタンは対応するリールの回転を停止するために設けられる。以下、ストップボタン17L,17C,17Rを、それぞれ左ストップボタン17L、中ストップボタン17C、右ストップボタン17Rともいう。

The

また、リール表示窓4の下方の略水平面の台座領域の略中央には、情報表示器6が設けられる。なお、情報表示器6は、透明の窓カバー(不図示)によって覆われている。

Further, an

情報表示器6には、特典として遊技者に対して払い出されるメダルの枚数(以下、「払出枚数」という)の情報を遊技者に対してデジタル表示(報知)するための2桁の7セグメントLED(以下、「7セグLED」という)や、パチスロ1の内部に預けられているメダルの枚数(以下、「クレジット枚数」という)などの情報を遊技者に対してデジタル表示(報知)するための2桁の7セグLEDが設けられる。なお、本実施形態では、メダルの払出枚数表示用の2桁の7セグLEDは、エラー発生及びエラー種別の情報を遊技者に対してデジタル表示(報知)するための2桁の7セグLEDとしても用いられる。それゆえ、エラー発生時には、メダルの払出枚数表示用の2桁の7セグLEDの表示態様は、払出枚数の表示態様からエラー種別の情報の表示態様に切り替わる。

The

さらに、情報表示器6には、内部当籤役として決定された役に応じた図柄組合せを有効ラインに沿って表示するために必要な停止操作の情報を報知する指示モニタ(不図示)が設けられている。指示モニタ(指示表示器)は、例えば、2桁の7セグメントLEDにより構成される。そして、指示モニタでは、報知する停止操作の情報と一義的に対応する態様で、2桁の7セグLEDが点灯、点滅又は消灯することにより、遊技者に対して必要な停止操作の情報を報知する。

Further, the

なお、ここでいう、報知する停止操作の情報と一義的に対応する態様とは、例えば、押し順「1st(第1停止操作を左リール3Lに対して行うこと)」を報知する場合には指示モニタに数値「1」を表示し、押し順「2nd(第1停止操作を中リール3Cに対して行うこと)」を報知する場合には指示モニタに数値「2」を表示し、押し順「3rd(第1停止操作を右リール3Rに対して行うこと)」を報知する場合には指示モニタに数値「3」を表示するなどの態様のことである。なお、指示モニタにおける停止操作の情報の報知態様(後述のメイン側で決定されるナビデータ)については、後述の図63を参照しながら後で詳述する。

The mode that uniquely corresponds to the information of the stop operation to be notified here is, for example, when the push order "1st (the first stop operation is performed on the

情報表示器6は、後述の図7に示すように、ドア中継基板68及び遊技作動表示基板81を介して主制御基板71に電気的に接続され、情報表示器6の表示動作は、主制御基板71内の後述の主制御回路90により制御される。また、上述した各種7セグLEDの制御方式は、ダイナミック点灯制御である。

As shown in FIG. 7 described later, the

なお、本実施形態のパチスロ1では、主制御基板71により制御される指示モニタに加えて、副制御基板72により制御される他の手段を用いて停止操作の情報を報知する構成を設ける。具体的には、後述のプロジェクタ機構211及び表示ユニット212(図3及び後述の図7参照)により構成される後述の表示装置11により停止操作の情報を報知する。

In the pachi-

このような構成を適用した場合、指示モニタにおける報知の態様と、副制御基板72により制御されるその他の手段における報知の態様とは、互いに異なる態様であってもよい。すなわち、指示モニタでは、報知する停止操作の情報と一義的に対応する態様で報知すればよく、必ずしも、停止操作の情報を直接的に報知する必要はない(例えば、指示モニタにおいて数値「1」が表示されたとしても、遊技者によっては報知内容を特定できない可能性もあり、直接的な報知とは言えない)。一方、後述の表示装置11等のその他の手段によるサブ側(副制御基板側)での報知では、停止操作の情報を直接的に報知してもよい。例えば、押し順「1st」を報知する場合、指示モニタでは報知する押し順と一義的に対応する数値「1」を表示するが、その他の手段(例えば、表示装置11等)では、左リール3Lに対して第1停止操作を行わせるための指示情報を直接的に報知してもよい。

When such a configuration is applied, the mode of notification in the instruction monitor and the mode of notification in other means controlled by the

このような構成のパチスロ1では、副制御基板72の制御だけでなく、主制御基板71の制御によっても、内部当籤役に応じた必要な停止操作の情報を報知することができる。また、このような停止操作の情報の報知の有無は、遊技状態に応じて制御されるようにしてもよい。例えば、後述の一般遊技状態(非ART遊技状態)では停止操作の情報を報知せずに、後述のART遊技状態(後述の図14参照)において停止操作の情報を報知するようにしてもよい。

In the pachi-

また、遊技者側から見て、リール表示窓4の左方には、サブ表示装置18が設けられる。サブ表示装置18は、図2に示すように、ドア本体9の前面部のうち、台座部13の略水平面の台座領域から略垂直に立設するように設けられる。サブ表示装置18は、液晶ディスプレイや有機EL(Electro-Luminescence)ディスプレイで構成され、各種情報を表示する。

Further, a

また、サブ表示装置18の表示面上には、タッチセンサ19が設けられている(後述の図7参照)。タッチセンサ19は、静電容量方式などの所定の動作原理に従い動作し、遊技者の操作を受け付けると、タッチ入力情報として当該操作に応じた信号を出力する。そして、本実施形態のパチスロ1は、タッチセンサ19を介して受け付けた遊技者の操作(タッチセンサ19から出力されるタッチ入力情報)に応じて、サブ表示装置18の表示を切り替え可能にする機能を有する。なお、サブ表示装置18は、タッチセンサ19から出力されるタッチ入力情報に基づいて後述の副制御基板72(後述の図7参照)により制御される。

Further, a

ドア本体9の下部には、メダル払出口24、メダル受皿25、2つのスピーカ用孔20L,20R等が設けられる。メダル払出口24は、後述のメダル払出装置51の駆動により排出されるメダルを外部に導く。メダル受皿25は、メダル払出口24から排出されたメダルを貯める。また、2つのスピーカ用孔20L,20Rからは、演出内容に対応する効果音や楽曲等の音声が出力される。

At the lower part of the

[内部構造]

次に、パチスロ1の内部構造を、図3及び図4を参照しながら説明する。図3は、キャビネット2aの内部構造を示す図であり、図4は、フロントドア2bの裏面側の内部構造を示す図である。

[Internal structure]

Next, the internal structure of the pachi-

キャビネット2aは、図3に示すように、上面板27aと、底面板27bと、左右の側面板27c,27dと、背面板27eとを有する。そして、キャビネット2a内の上部には、表示装置11が配設される。

As shown in FIG. 3, the

表示装置11は、プロジェクタ機構211と、プロジェクタ機構211から投射された映像光が投影される箱状の被投影部材212aとを有し、プロジェクションマッピングによる映像表示を行う。具体的には、表示装置11では、立体物となる被投影部材212aの位置(投影距離や角度など)や形状に基づいて映像光を生成し、その映像光が、プロジェクタ機構211により被投影部材212aの表面に投影される。このような演出機能を設けることにより、高度で且つ迫力のある演出を行うことができる。また、図3には示さないが、箱状の被投影部材212aの裏側には、表示面が湾曲した別の被投影部材が設けられ、遊技状態に応じて、どちらか一方の被投影部材が、映像光が投影されるスクリーンとして使用される。それゆえ、キャビネット2a内は、遊技状態に応じて、被投影部材を切り換える機能(不図示)も設けられる。

The

キャビネット2a内の下部には、メダル払出装置(以下、ホッパー装置という)51と、メダル補助収納庫52と、電源装置53とが配設される。

At the lower part of the

ホッパー装置51は、キャビネット2aにおける底面板27bの中央部に取り付けられる。このホッパー装置51は、多量のメダルを収容可能で、それらを1枚ずつ排出可能な構造を有する。ホッパー装置51は、貯留されたメダルが例えば50枚を超えたとき、又は、精算ボタンが押下されてメダルの精算が実行されるときに、メダルを払い出す。そして、ホッパー装置51によって払い出されたメダルは、メダル払出口24(図2参照)から排出される。

The

メダル補助収納庫52は、ホッパー装置51から溢れ出たメダルを収納する。このメダル補助収納庫52は、キャビネット2a内部を正面から見て、ホッパー装置51の右側に配置される。また、メダル補助収納庫52は、キャビネット2aの底面板27bに対して着脱可能に取り付けられている。

The medal

電源装置53は、電源スイッチ53aと、電源基板53b(電源供給手段)とを有している(後述の図7参照)。この電源装置53は、キャビネット2a内部を正面から見て、ホッパー装置51の左側に配置されており、左側面板27cに取り付けられている。電源装置53は、サブ電源装置(不図示)から供給された交流電圧100Vの電力を各部で必要な直流電圧の電力に変換して、変換した電力を各部へ供給する。

The

また、キャビネット2a内の電源装置53の上方には、副制御基板72(後述の図7参照)を収容する副制御基板ケース57が配設される。副制御基板ケース57に収納された副制御基板72には、後述の副制御回路200(後述の図10参照)が搭載されている。この副制御回路200は、映像の表示等による演出の実行を制御する回路である。副制御回路200の具体的な構成については後述する。

Further, above the

キャビネット2a内の副制御基板ケース57の上方には、副中継基板61が配設される。この副中継基板61は、副制御基板72と後述の主制御基板71とを接続する配線が実装された中継基板である。また、副中継基板61は、副制御基板72と副制御基板72の周辺に配設された基板や各種装置部(ユニット)などとを接続する配線が実装された中継基板である。

The

また、図3には示さないが、キャビネット2a内には、キャビネット側中継基板44(後述の図7参照)が配設される。このキャビネット側中継基板44は、主制御基板71(後述の図7参照)と、ホッパー装置51、遊技メダル補助収納庫スイッチ77(後述の図7参照)及びメダル払出カウントスイッチ(不図示)のそれぞれとを接続する配線が実装された中継基板である。

Further, although not shown in FIG. 3, a cabinet-side relay board 44 (see FIG. 7 described later) is arranged in the

フロントドア2bの裏面側の中央部には、図4に示すように、ミドルドア41が、配設され、リール表示窓4(図2参照)を裏側から開閉可能に取り付けられている。また、図4には示さないが、ミドルドア41のリール表示窓4側には、3つのリール3L,3C,3Rが取り付けられ、ミドルドア41のリール表示窓4側とは反対側には、主制御基板71(後述の図7参照)が収納された主制御基板ケース55が取り付けられている。なお、3つのリール3L,3C,3Rには、所定の減速比をもったギアを介してステッピングモータ(不図示)が接続されている。

As shown in FIG. 4, a

主制御基板ケース55に収納された主制御基板71は、後述する主制御回路90(後述の図9参照)を有する。主制御回路90(主制御手段)は、内部当籤役の決定、各リール3L,3C,3Rの回転及び停止、入賞の有無の判定といった、パチスロ1における遊技の主な流れを制御する回路である。また、本実施形態では、例えば、ARTの決定の有無の抽籤処理、ナビ情報の指示モニタへの表示処理、各種試験信号の送信処理などの制御も主制御回路90により行われる。なお、主制御回路90の具体的な構成は後述する。

The

フロントドア2bの裏面側において、ミドルドア41の下方には、スピーカ65L,65Rが配設される。スピーカ65L,65Rは、それぞれスピーカ用孔20L,20R(図2参照)と対向する位置に配置されている。

また、スピーカ65Lの上方には、セレクタ66と、ドア開閉監視スイッチ67とが配設される。セレクタ66は、メダルの材質や形状等が適正であるか否かを選別する装置であり、メダル投入口14に投入された適正なメダルをホッパー装置51へ案内する。セレクタ66内においてメダルが通過する経路上には、適正なメダルが通過したことを検出するメダルセンサ(遊技媒体検出手段:不図示)が設けられている。

Further, above the

ドア開閉監視スイッチ67は、フロントドア2bを裏面側から見て、セレクタ66の左斜め下に配置される。このドア開閉監視スイッチ67は、フロントドア2bの開閉を報知するためのセキュリティ信号をパチスロ1の外部に出力する。

The door open /

また、図4には示さないが、フロントドア2bを裏面において、ミドルドア41により開閉された領域であり且つリール表示窓4の下方には、ドア中継端子板68が配設される(後述の図7参照)。このドア中継端子板68は、主制御基板ケース55内の主制御基板71と、各種のボタンやスイッチ、副中継基板61、セレクタ66、遊技動作表示基板81、試験機用第1インターフェースボード301及び試験機用第2インターフェースボード302のそれぞれとを接続する配線が実装された中継基板である。なお、各種のボタン及びスイッチとしては、例えば、MAXベットボタン15a、1ベットボタン15b、ドア開閉監視スイッチ67、後述のBETスイッチ77、スタートスイッチ79等が挙げられる。

Further, although not shown in FIG. 4, a door

<サブ表示装置の表示例>

ここで、図5A~図5Eを参照して、サブ表示装置18に表示される各種表示画面について説明する。なお、図5Aは、サブ表示装置18に表示されるトップ画面221を示す図であり、図5Bは、サブ表示装置18に表示されるメニュー画面222を示す図である。また、図5C~図5Eは、サブ表示装置18に表示される遊技情報画面223,224,225を示す図である。

<Display example of sub-display device>

Here, various display screens displayed on the

サブ表示装置18には、遊技者のタッチ操作により様々な表示画面が表示され、図5A~図5Eに示すように、トップ画面221、メニュー画面222及び遊技情報画面223,224,225を含む各種表示画面が表示される。これらの表示画面は、タッチセンサ19を介して受け付けた遊技者の操作信号に基づいて切り替えられる。

Various display screens are displayed on the

トップ画面221は、サブ表示装置18に表示される表示画面のうちの初期画面であり、トップ画面221では、「MENU」ボタン221aと、概要遊技履歴221bとが表示される。「MENU」ボタン221aは、図5Bに示すメニュー画面222を呼び出すための操作ボタンであり、「MENU」ボタン221aに対して遊技者による所定操作(例えばタップ)が行われると、メニュー画面222が呼び出される。また、トップ画面221では、概要遊技履歴221bとして、パチスロ1の一部の遊技履歴(概要遊技履歴)を表示する。本実施形態では、概要遊技履歴221bとして、例えば、ボーナス回数、ART回数及びゲーム数(遊技回数)が表示される。

The

メニュー画面222は、サブ表示装置18で表示可能なメニューを表示する画面であり、メニュー画面222では、「戻る」ボタン222a、「登録」ボタン222b、「説明」ボタン222c、「配列配当」ボタン222d、「リーチ目」ボタン222e、「WEBサイト」ボタン222f及び「音量」ボタン222gが表示される。「戻る」ボタン222aは、トップ画面221を呼び出すための操作ボタンであり、「戻る」ボタン222aに対して遊技者による操作が行われると、トップ画面221が呼び出される。また、「登録」ボタン222b~「音量」ボタン222gは、対応するメニュー内容の表示画面を呼び出すための操作ボタンであり、各ボタンに対して遊技者による操作が行われると、対応するメニュー内容の表示画面が呼び出される。

The

例えば、メニュー画面222において「登録」ボタン222bが遊技者により操作された場合、遊技中の遊技者を登録するための登録画面(不図示)がサブ表示装置18の表示画面に呼び出される。近年のパチスロでは、機種ごとに遊技者を登録しておき、当該遊技者のこれまでの遊技履歴から、定められたミッションの達成状況などの様々な情報を管理するサービスが広く行われている。「登録」ボタン222bにより呼び出される登録画面は、このサービスの提供を受ける際に遊技者を登録するための表示画面である。

For example, when the "register"

また、例えば、メニュー画面222において「説明」ボタン222cが遊技者により操作された場合、パチスロ1の説明画面(不図示)がサブ表示装置18の表示画面に呼び出される。説明画面で表示される情報には、例えば、設定値ごとのボーナス当籤確率やART当籤確率などのパチスロ1の仕様に関する説明や、パチスロ1の演出に登場するキャラクタの紹介説明などが含まれる。

Further, for example, when the "explanation"

また、例えば、メニュー画面222において「配列配当」ボタン222dが遊技者により操作された場合、パチスロ1の配列配当画面(不図示)がサブ表示装置18の表示画面に呼び出される。配列配当画面には、例えば、パチスロ1において入賞と判定される図柄の組合せと、入賞と判定された際の特典との対応関係(配当表)や、各リール3L,3C,3Rに描かれた図柄列(リール配列)などが表示される。

Further, for example, when the "array payout"

また、例えば、メニュー画面222において「リーチ目」ボタン222eが遊技者により操作された場合、パチスロ1のリーチ目画面(不図示)がサブ表示装置18の表示画面に呼び出される。リーチ目画面には、パチスロ1で設定されている「リーチ目」と称される図柄組合せの情報が表示される。なお、「リーチ目」と称する図柄組合せは、該図柄組合せが有効ラインに沿って表示されることにより、特別な特典が付与される図柄組合せであり、本実施形態のパチスロ1では、後述の図28~図30の入賞作動フラグ格納領域の内容欄に示す略称「リーチ目リプ」に対応する図柄組合せが該当する。そして、本実施形態では、「リーチ目リプ」に係る図柄組合せが有効ラインに沿って表示された場合、その後、遊技者にとって有利な状態(例えば、ボーナス状態、通常ART又はCT(後述の図14参照))に移行することが確定する。

Further, for example, when the "reach eye"

また、例えば、メニュー画面222において「WEBサイト」ボタン222fが遊技者により操作された場合、パチスロ1のWEB紹介画面(不図示)がサブ表示装置18の表示画面に呼び出される。WEB紹介画面には、例えば、パチスロ1の機種ごとに設けられた特設WEBサイトやパチスロ1のメーカーのWEBサイトなど任意のWEBサイトのURLを示す二次元コード(例えば、QRコード(登録商標))が表示される。遊技者は、携帯電話などでWEB紹介画面に表示される二次元コードを読み込むことにより、対応するWEBサイトにアクセスすることができる。

Further, for example, when the "WEB site"

また、例えば、メニュー画面222において「音量」ボタン222gが遊技者により操作された場合、スピーカ65L,65Rから出力する音の音量を調整することが可能な音量調整画面(不図示)がサブ表示装置18の表示画面に呼び出される。遊技者は、音量調整画面を介してパチスロ1の演出音の音量を調整することができる。

Further, for example, when the "volume"

なお、サブ表示装置18は、上述した表示装置11(プロジェクタ機構211及び表示ユニット212)とは別体に設けられるため、表示装置11とは別個に制御することができる。それゆえ、本実施形態のパチスロ1では、遊技中(表示装置11による演出の実行中)であっても、サブ表示装置18の表示画面を遊技者の操作により切り替えることができる。その結果、例えば、遊技者が、表示装置11の演出において登場するキャラクタのことを知りたいと思った場合、遊技者は、「説明」ボタン222cを操作して説明画面を呼び出すことにより、キャラクタ間の関係性などの情報を遊技中に把握することができる。また、例えば、遊技者が、遊技中に、いわゆる「レア役」が当籤した場合のリール回転中にレア役を入賞させるために目安とすべき図柄を把握したいと思った場合、遊技者は、「配列配当」ボタン222dを操作して配列配当画面を呼び出すことにより、リール配列を把握することができる。

Since the

遊技情報画面223,224,225は、パチスロ1の遊技履歴のうちのトップ画面221に表示する概要遊技履歴を含む詳細遊技履歴情報を表示する表示画面である。

The game information screens 223, 224, and 225 are display screens that display detailed game history information including an outline game history to be displayed on the

遊技情報画面223には、「戻る」ボタン223aと、「MENU」ボタン223bと、「前へ」ボタン223cと、「次へ」ボタン223dと、遊技履歴223eとが表示される。「戻る」ボタン223a及び「MENU」ボタン223bは、それぞれトップ画面221及びメニュー画面222をサブ表示装置18の表示画面に呼び出すための操作ボタンであり、各ボタンを遊技者が操作することにより、対応する表示画面が呼び出される。また、「前へ」ボタン223c及び「次へ」ボタン223dは、遊技情報画面を所定の順序で切り替えるための操作ボタンであり、「前へ」ボタン223cが遊技者により操作されると、表示画面が遊技情報画面223から遊技情報画面225に切り替わり、「次へ」ボタン223dが遊技者により操作されると、表示画面が遊技情報画面223から遊技情報画面224に切り替わる。また、遊技履歴223eとしては、図5Cに示すように、ゲーム数(遊技回数)、ボーナス回数、ART回数及びCZ(チャンスゾーン)回数が表示される。

On the

遊技情報画面224には、「戻る」ボタン224aと、「MENU」ボタン224bと、「前へ」ボタン224cと、「次へ」ボタン224dと、遊技履歴214eとが表示される。「戻る」ボタン224a及び「MENU」ボタン224bは、それぞれトップ画面221及びメニュー画面222をサブ表示装置18の表示画面に呼び出すための操作ボタンであり、各ボタンを遊技者が操作することにより、対応する表示画面が呼び出される。また、「前へ」ボタン224c及び「次へ」ボタン224dは、遊技情報画面を所定の順序で切り替える操作ボタンであり、「前へ」ボタン224cが遊技者に操作されると、表示画面が遊技情報画面224から遊技情報画面223に切り替わり、「次へ」ボタン224dが遊技者により操作されると、表示画面が遊技情報画面224から遊技情報画面225に切り替わる。また、遊技履歴224eとしては、後述のCZ(チャンスゾーン)の突入回数及び成功回数が表示される。なお、後述するように、本実施形態では、CZとして、CZ1,CZ2,CZ3の3種類のCZが設けられる。それゆえ、遊技履歴224eとしては、図5Dに示すように、CZ1~CZ3のそれぞれの突入回数及び成功回数が表示される。

On the

遊技情報画面225には、「戻る」ボタン225aと、「MENU」ボタン225bと、「前へ」ボタン225cと、「次へ」ボタン225dと、遊技履歴225eとが表示される。「戻る」ボタン225a及び「MENU」ボタン225bは、それぞれトップ画面221及びメニュー画面222をサブ表示装置18の表示画面に呼び出すための操作ボタンであり、各ボタンを遊技者が操作することにより、対応する表示画面が呼び出される。また、「前へ」ボタン225c及び「次へ」ボタン225dは、所定の順序で遊技情報画面を切り替えるための操作ボタンであり、「前へ」ボタン225cが遊技者に操作されると、表示画面が遊技情報画面225から遊技情報画面224に切り替わり、「次へ」ボタン225dが遊技者により操作されると、表示画面が遊技情報画面225から遊技情報画面223に切り替わる。また、遊技履歴225eとしては、図5Eに示すように、小役の当籤回数及び当籤確率(分子が1の分数)が表示される。

On the

なお、サブ表示装置18に表示される表示画面の切り替え手法としては、例えば、それぞれの表示画面に表示される操作ボタンに対するタップ操作に基づいて切り替える手法を採用してもよいし、また、例えば、表示画面に対するスワイプ操作に基づいて切り替える手法を採用してもよい。

As a display screen switching method displayed on the

<サブ表示装置の表示画面の各種切り替え機能>

次に、本実施形態のパチスロ1におけるサブ表示装置18の表示画面の各種切り替え機能について説明する。

<Various switching functions of the display screen of the sub display device>

Next, various switching functions of the display screen of the

[サブ表示装置の表示画面の遷移例]

まず、図6A及び6Bを参照して、本実施形態のパチスロ1におけるサブ表示装置18の表示画面の遷移例(切り替え態様)について説明する。なお、図6Aは、遊技者登録状態がセットされていない状況におけるサブ表示装置18の表示画面の遷移例を示す図であり、図6Bは、遊技者登録状態がセットされている状況におけるサブ表示装置18の表示画面の遷移例を示す図である。

[Example of transition of display screen of sub-display device]

First, a transition example (switching mode) of the display screen of the

遊技者登録状態がセットされていない状況では、図6Aに示すように、サブ表示装置18の表示画面は、トップ画面221とメニュー画面222との間、並びに、メニュー画面222とメニュー画面222から遷移可能な各種表示画面との間でのみ遷移可能であり、これらの表示画面間の遷移は副制御基板72(後述のサブCPU201)により制御される。例えば、副制御基板72は、タッチセンサ19を介して取得したタッチ操作(例えば、所定のボタンに対するタップ操作や、表示画面上におけるスワイプ操作)に基づいて、トップ画面221及びメニュー画面222間で、表示画面を切り替える。しかしながら、遊技者登録状態がセットされていない状況では、副制御基板72は、遊技情報画面223,224,225の表示が不可能となるように制御する。すなわち、遊技者登録状態がセットされていない状況では、遊技者は、サブ表示装置18に遊技情報画面223,224,225を表示することができない。

In the situation where the player registration state is not set, as shown in FIG. 6A, the display screen of the

一方、遊技者登録状態がセットされている状況では、図6Bに示すように、サブ表示装置18の表示画面は、トップ画面221とメニュー画面222との間、並びに、メニュー画面222とメニュー画面222から遷移可能な各種表示画面との間に加え、メニュー画面222と遊技情報画面223,224,225との間においても遷移可能となり、これらの表示画面間の遷移は副制御基板72(後述のサブCPU201)により制御される。すなわち、副制御基板72は、タッチセンサ19を介して取得したタッチ操作に基づいて、トップ画面221とメニュー画面222との間だけでなく、トップ画面221及びメニュー画面222のそれぞれと、遊技情報画面223,224,225との間においても表示画面を切り替えることができる。それゆえ、本実施形態において、遊技者登録状態がセットされている場合、遊技者は、サブ表示装置18に遊技情報画面223,224,225を表示することができる。

On the other hand, in the situation where the player registration state is set, as shown in FIG. 6B, the display screen of the

なお、図6Bに示すように、トップ画面221、メニュー画面222及び遊技情報画面223,224,225間における表示画面の遷移順序は任意である。それゆえ、例えば、トップ画面221から遊技情報画面223,224,225に直接遷移可能となる構成にしてもよいし、トップ画面221からメニュー画面222を介してのみ遊技情報画面223,224,225に遷移可能となる構成にしてもよい。

As shown in FIG. 6B, the transition order of the display screens between the

本実施形態のパチスロ1では、トップ画面221からメニュー画面222を介してのみ遊技情報画面223,224,225に遷移可能な構成(トップ画面221から遊技情報画面223,224,225に直接遷移できない構成)を採用している。なお、本実施形態のパチスロ1では、メニュー画面222において、遊技者が表示画面に対してスワイプ操作(メニュー選択操作ではない)を行うことにより、表示画面をメニュー画面222から遊技情報画面223,224,225に遷移させることができる。

In the pachi-

なお、本実施形態では、遊技情報画面223,224,225は、メニュー画面222とは完全に独立して設けられた表示画面である。すなわち、本実施形態のパチスロ1では、遊技履歴という、遊技者が遊技中に強い関心を抱く遊技の結果を示す情報を、配当配列や音量調節などの遊技の結果とは関係のない情報として独立して表示する。そして、本実施形態では、遊技者登録状態がセットされている状況において、メニュー画面222に対して遊技者がメニュー選択操作を行うことなく、遊技情報画面223,224,225を表示可能にしている。それゆえ、本実施形態では、遊技者登録状態がセットされている場合、遊技者が所望する情遊技履歴情報へのアクセスを容易に行うことができる。

In this embodiment, the game information screens 223, 224, and 225 are display screens provided completely independently of the

また、本実施形態では、メニュー画面222に対するメニュー選択操作では、表示画面を遊技情報画面223,224,225に遷移させることができず、メニュー画面222に対してスワイプ操作(メニュー表示では指定されていない操作)を行わなければ、表示画面を遊技情報画面223,224,225に遷移させることができない。それゆえ、本実施形態のパチスロ1では、表示画面を遊技情報画面223,224,225に遷移させるためのスワイプ操作を、遊技者登録状態がセットされている状況における隠しコマンドとして扱うことができる。この場合、遊技者にとってみれば、パチスロ1に対する自身の知識により、知識の少ない他の遊技者では見ることのできない、より詳細な遊技履歴情報を見ることができるため、当該他の遊技者よりも有利に遊技を行うことができ、結果、遊技者が積極的に遊技を行うことを期待することができる。

Further, in the present embodiment, in the menu selection operation for the

[遊技情報画面からトップ画面への表示切り替え機能]

本実施形態のパチスロ1は、サブ表示装置18の表示画面を、遊技情報画面223,224,225から、遊技者の手動により、又は、自動的に、トップ画面221に遷移させる機能を有する。具体的には、本実施形態では、遊技情報画面223,224,225において「戻る」ボタンが操作されると、表示画面が遊技情報画面223,224,225からトップ画面221に遷移する(手動遷移機能)。また、本実施形態では、遊技情報画面223,224,225が表示されている状態において所定の条件を満たした場合には、遊技者の操作とは関係なく自動的に表示画面がトップ画面221に遷移する(自動遷移機能)。

[Display switching function from game information screen to top screen]

The pachi-

より具体的には、パチスロ1では、遊技情報画面223,224,225が表示されている状態において、投入操作(MAXベットボタン15aへの操作、1ベットボタン15bへの操作及びメダル投入口14にメダルを投入する操作)が行われると、サブ表示装置18の表示画面が自動的にトップ画面221に遷移する。なお、ART遊技状態のように、リプレイ役が内部当籤役として決定される確率が高い遊技状態(高リプ状態)では、リプレイ役入賞に伴う再遊技の作動によりメダルが自動的に投入されてしまう結果、高リプ状態では、遊技情報画面223,224,225を表示する機会が制限されてしまう可能性がある。そこで、本実施形態のパチスロ1では、再遊技の作動によりメダルが自動的に投入された場合には、メダルの投入操作ではなく、開始操作を契機として、自動的に表示画面が遊技情報画面223,224,225からトップ画面221に遷移する。

More specifically, in the pachi-

すなわち、本実施形態では、再遊技が作動し、かつ、遊技情報画面223,224,225が表示されている場合には、開始操作を契機として、自動的に表示画面が遊技情報画面223,224,225からトップ画面221に遷移する。一方、再遊技の作動が行われていない場合には、投入操作を契機として、自動的に表示画面が遊技情報画面223,224,225からトップ画面221に遷移する。

That is, in the present embodiment, when the re-game is activated and the game information screens 223, 224, 225 are displayed, the display screen is automatically changed to the game information screens 223, 224 with the start operation as a trigger. , 225 transitions to the

[メニュー内容表示画面からトップ画面(又はメニュー画面)への表示切り替え機能]

本実施形態のパチスロ1は、サブ表示装置18の表示画面を、メニュー画面222に対するメニュー選択操作により遷移可能な各種メニュー内容表示画面(登録画面、説明画面、配列配当画面、リーチ目画面、WEB紹介画面及び音量調整画面)から、遊技者の手動により、又は、自動的に、トップ画面221(又はメニュー画面222)に遷移させる機能を有する。具体的には、本実施形態では、メニュー内容表示画面において所定のボタン(例えば、「TOPへ戻る」ボタン)が操作されると、表示画面が当該メニュー内容表示画面からトップ画面221に遷移する(手動遷移機能)。また、本実施形態では、メニュー内容表示画面において特定のボタン(例えば、「戻る」ボタン)が操作されると、表示画面が当該メニュー内容表示画面からメニュー画面222に表示画面を遷移する(手動遷移機能)。

[Display switching function from the menu content display screen to the top screen (or menu screen)]

The pachi-

さらに、本実施形態では、メニュー内容表示画面が表示されている状態において所定の時間が経過すると、遊技者の操作とは関係なく、自動的に表示画面がトップ画面221(又はメニュー画面222)に遷移する(自動遷移機能)。なお、この際、トップ画面221(又はメニュー画面222)に自動遷移する契機となる所定の時間は、現在表示しているメニュー内容表示画面の種類に応じて異なる。例えば、パチスロ1から出力する音量の調整を行う音量調整画面を長時間表示していると、音量が誤操作により意図しない音量に調整されてしまうおそれがあるだけでなく、誤操作により他の遊技者を不快にしてしまうおそれもある。それゆえ、音量調整画面では、他のメニュー内容表示画面よりも短い時間で、自動的にトップ画面221(又はメニュー画面222)に遷移するように設定されている。一方、登録画面は、遊技者の登録を行い易くするために、他のメニュー内容表示画面よりも長い時間で、自動的にトップ画面221(又はメニュー画面222)に遷移するように設定されている。

Further, in the present embodiment, when a predetermined time elapses while the menu content display screen is displayed, the display screen automatically changes to the top screen 221 (or menu screen 222) regardless of the player's operation. Transition (automatic transition function). At this time, the predetermined time that triggers the automatic transition to the top screen 221 (or the menu screen 222) differs depending on the type of the menu content display screen currently displayed. For example, if the volume adjustment screen for adjusting the volume output from the

すなわち、各メニュー内容表示画面には、トップ画面221(又はメニュー画面222)に自動遷移する契機となる経過時間(自動遷移時間)が、当該メニュー内容表示画面の種別に応じて適宜設定されており、音量調整画面には、他のメニュー内容表示画面よりも短い自動遷移時間が設定され、登録画面には、他のメニュー内容表示画面よりも長い自動遷移時間が設定されている。 That is, on each menu content display screen, an elapsed time (automatic transition time) that triggers an automatic transition to the top screen 221 (or menu screen 222) is appropriately set according to the type of the menu content display screen. , The volume adjustment screen is set to have a shorter automatic transition time than the other menu content display screens, and the registration screen is set to have a longer automatic transition time than the other menu content display screens.

[メニューの操作可否の選択機能]

本実施形態のパチスロ1では、サブ表示装置18の表示画面を、メニュー画面222から、登録画面、説明画面、配列配当画面、リーチ目画面、WEB紹介画面及び音量調整画面に遷移させることにより、遊技者が、これらのメニュー内容表示画面に応じた各種操作を行うことができ、また、各種情報を確認することができる。なお、このような遊技者がメニュー選択できる機能を遊技店側の設定に応じて制限できるような機能(メニューの操作可否の選択機能)を設けてもよい。

[Menu operation enable / disable selection function]

In the pachi-

例えば、遊技店側の設定により、表示画面をメニュー画面222から音量調節画面に遷移不可能にする(例えば、メニュー画面222に「音量」ボタン222gを表示しない)ようにしてもよい。この場合、遊技者による音量調節を不可能にすることができる。

For example, the display screen may not be transitioned from the

<パチスロが備える制御系>

次に、パチスロ1が備える制御系について、図7を参照して説明する。図7は、パチスロ1の制御系の構成を示す回路ブロック図である。

<Control system provided by pachislot>

Next, the control system included in the pachi-

パチスロ1は、ミドルドア41に設けられた主制御基板71と、フロントドア2bに設けられた副制御基板72とを有する。また、パチスロ1は、主制御基板71に接続された、リール中継端子板74、設定用鍵型スイッチ54(設定スイッチ)及びキャビネット側中継基板44を有する。さらに、パチスロ1は、キャビネット側中継基板44を介して主制御基板71に接続された外部集中端子板47、ホッパー装置51、メダル補助収納庫スイッチ75、リセットスイッチ76及び電源装置53を有する。なお、ホッパー装置51の構成については上述したので、ここでは、その説明を省略する。

The pachi-

リール中継端子板74は、各リール3L,3C,3Rのリール本体の内側に配設されている。リール中継端子板74は、各リール3L,3C,3Rのステッピングモータ(不図示)に電気的に接続されており、主制御基板71からステッピングモータに出力される信号を中継する。

The reel

設定用鍵型スイッチ54は、主制御基板ケース55に設けられる。設定用鍵型スイッチ54は、パチスロ1の設定(設定1~設定6)を変更するとき、もしくは、パチスロ1の設定を確認するときに使用される。

The setting

キャビネット側中継基板44は、主制御基板71と、外部集中端子板47、ホッパー装置51、メダル補助収納庫スイッチ75、リセットスイッチ76及び電源装置53のそれぞれとを接続する配線が実装された中継基板である。外部集中端子板47は、メダル投入信号、メダル払出信号及びセキュリティ信号などの信号をパチスロ1の外部へ出力するために設けられる。メダル補助収納庫スイッチ75は、メダル補助収納庫52に設けられ、メダル補助収納庫52がメダルで満杯になっているか否かを検出する。リセットスイッチ76は、例えば、パチスロ1の設定を変更する際に用いられる。

The cabinet-

電源装置53は、電源基板53bと、電源基板53bに接続された電源スイッチ53aとを有する。電源スイッチ53aは、パチスロ1に必要な電源を供給するときに押下される。電源基板53bは、キャビネット側中継基板44を介して主制御基板71に接続されるとともに、副中継基板61を介して副制御基板72にも接続される。

The

また、パチスロ1は、ドア中継端子板68、並びに、該ドア中継端子板68を介して、主制御基板71に接続された、セレクタ66、ドア開閉監視スイッチ67、BETスイッチ77、精算スイッチ78、スタートスイッチ79、ストップスイッチ基板80、遊技動作表示基板81、副中継基板61、試験機用第1インターフェースボード301及び試験機用第2インターフェースボード302を有する。なお、セレクタ66、ドア開閉監視スイッチ67及び副中継基板61については、上述したので、ここでは、それらの説明を省略する。

Further, the pachi-

BETスイッチ77(投入操作検出手段)は、MAXベットボタン15a又は1ベットボタン15bが遊技者により押下されたことを検出する。精算スイッチ78は、精算ボタン(不図示)が遊技者により押下されたことを検出する。スタートスイッチ79(開始操作検出手段)は、スタートレバー16が遊技者により操作されたこと(開始操作)を検出する。

The BET switch 77 (throwing operation detecting means) detects that the

ストップスイッチ基板80(停止操作検出手段)は、回転しているメインリールを停止させるための回路と、停止可能なメインリールをLEDなどにより表示するための回路とを備える。また、ストップスイッチ基板80には、ストップスイッチ(不図示)が設けられる。ストップスイッチは、各ストップボタン17L,17C,17Rが遊技者により押下されたこと(停止操作)を検出する。

The stop switch board 80 (stop operation detecting means) includes a circuit for stopping the rotating main reel and a circuit for displaying the stoptable main reel by an LED or the like. Further, the

遊技動作表示基板81は、情報表示器(7セグ表示器)6及びLED82に接続される。LED82には、例えば、今回の遊技に投入されたメダルの枚数(以下、「投入枚数」という)に対応して点灯する、メダル投入枚数表示用の3つのLED(以下、「第1LED」~「第3LED」という)や、遊技動作表示基板81から入力される信号に基づいて、メダル投入が可能であることを表示するマーク、遊技開始を表示するマーク、再遊技を行うマークなどを点灯させるLEDなどが含まれる。第1LED~第3LED(表示手段)では、メダルが1枚投入されると、第1LEDが点灯し、メダルが2枚投入されると、第1及び第2LEDが点灯し、メダルが3枚(遊技開始可能枚数)投入されると、第1LED~第3LEDが点灯する。なお、情報表示器6については、上述したので、ここでは、それらの説明を省略する。

The game

試験機用第1インターフェースボード301及び試験機用第2インターフェースボード302はともに、パチスロ1の検定試験(試射試験)において、遊技に関する各種信号を試験機に出力する際に用いられる中継基板である(なお、販売用のリリース製品としてのパチスロ1にはこれらの中継基板は搭載されていないので、販売用の主制御基板71の主制御回路90には、試験機用第1インターフェースボード301及び試験機用第2インターフェースボード302に接続するために必要な各種電子部品もまた実装されていない)。例えば、遊技に係る主要な動作(例えば、内部抽籤、リール停止制御等)を制御するための試験信号は、試験機用第1インターフェースボード301を介して出力され、例えば、主制御基板71で決定された押し順ナビに係る試験信号などは、試験機用第2インターフェースボード302を介して出力される。

Both the

副制御基板72は、ドア中継端子板68及び副中継基板61を介して主制御基板71に接続される。また、パチスロ1は、副中継基板61を介して副制御基板72に接続された、スピーカ群84、LED群85、24hドア開閉監視ユニット63、タッチセンサ19及び表示ユニット212を有する。なお、タッチセンサ19については、上述したので、ここでは、その説明を省略する。

The

スピーカ群84は、スピーカ65L,65Rや図示しない各種スピーカを含んで構成される。LED群85は、フロントパネル10に設けられたランプ群21や、腰部パネル12の装飾パネルを背面側から照明するための光を出射する光源などを含んで構成される。24hドア開閉監視ユニット63は、ミドルドア41の開閉の履歴情報を保存する。また、24hドア開閉監視ユニット63は、ミドルドア41が開放されたときに、表示装置11によりエラー表示を行うための信号を副制御基板72(副制御回路200)に出力する。表示ユニット212は、例えば、表示装置11を構成する被投影部材212a、及び、被投影部材212aの裏側に設けられた表示面が湾曲した別の被投影部材を含んで構成される。

The

また、パチスロ1は、副制御基板72に接続された、ロムカートリッジ基板86及び液晶中継基板87を有する。なお、ロムカートリッジ基板86及び液晶中継基板87は、副制御基板72とともに副制御基板ケース57に収納されている。

Further, the pachi-

ロムカートリッジ基板86は、サブCPU102により実行される各種制御プログラムと、演出用の画像(映像)、音声(スピーカ群84)、光(LED群85)及び通信のデータを管理するための基板である。液晶中継基板87は、副制御基板72と、表示装置11を構成するプロジェクタ機構211、及び、サブ表示装置18との間の接続配線を中継する基板である。なお、プロジェクタ機構211及びサブ表示装置18については、上述したので、ここでは、それらの説明を省略する。

The

<主制御回路>

次に、図8を参照して、主制御基板71に実装される主制御回路90の構成について説明する。図8は、パチスロ1の主制御回路90の構成例を示すブロック図である。

<Main control circuit>

Next, the configuration of the

主制御回路90は、マイクロプロセッサ91と、クロックパルス発生回路92と、電源管理回路93と、スイッチングレギュレータ94(電源供給手段)とを備える。

The

マイクロプロセッサ91は、遊技機用のセキュリティ機能付きマイクロプロセッサである。なお、本実施形態のマイクロプロセッサ91では、後述するように、ソースプログラム上で規定可能な該マイクロプロセッサ91に特有の様々な命令コード(例えば、後述の「LDQ」命令等:以下、「メインCPU101専用命令コード」という)が設けられている。本実施形態では、このメインCPU101専用命令コードを用いることにより、処理の効率化やプログラム容量の削減などを実現している。マイクロプロセッサ91の内部構成については、後述の図9を参照して詳述し、マイクロプロセッサ91に設けられているメインCPU101専用命令コードについては、後述の主制御回路が実行する各種処理において詳述する。

The

クロックパルス発生回路92は、メインCPU作動用のクロックパルス信号を生成し、該生成したクロックパルス信号をマイクロプロセッサ91に出力する。マイクロプロセッサ91は、入力されたクロックパルス信号に基づいて、制御プログラムを実行する。

The clock

電源管理回路93は、電源基板53b(図7参照)から供給される直流12Vの電源電圧の変動を管理する。そして、電源管理回路93は、例えば、電源が投入された際(電源電圧が0Vから起動電圧値(10V)を上回った際)には、リセット信号をマイクロプロセッサ91の「XSRST」端子に出力し、電断が発生した際(電源電圧が12Vから停電電圧値(10.5V)を下回った際)には、電断検知信号をマイクロプロセッサ91の「XINT」端子に出力する。すなわち、電源管理回路93は、電源投入時に、マイクロプロセッサ91にリセット信号(起動信号)を出力する手段(起動手段)、及び、電断発生時に、マイクロプロセッサ91に電断検知信号(停電信号)を出力する手段(停電手段)も兼ねる。

The power

スイッチングレギュレータ94は、DC/DC変換回路であり、マイクロプロセッサ91の直流駆動電圧(直流5Vの電源電圧)を生成し、該生成した直流駆動電圧をマイクロプロセッサ91の「VCC」端子に出力する。

The switching

<マイクロプロセッサ>

次に、図9を参照して、マイクロプロセッサ91の内部構成について説明する。図9は、マイクロプロセッサ91の内部構成を示すブロック図である。

<Microprocessor>

Next, the internal configuration of the

マイクロプロセッサ91は、メインCPU101と、メインROM102(第1記憶手段)と、メインRAM103(第2記憶手段)と、外部バスインターフェース104と、クロック回路105と、リセットコントローラ105と、演算回路107と、乱数回路110と、パラレルポート111と、割込みコントローラ112と、タイマー回路113と、第1シリアル通信回路114と、第2シリアル通信回路115と、を有する。そして、マイクロプロセッサ91を構成するこれらの各部は信号バス116を介して互いに接続されている。

The

メインCPU101は、クロック回路105で生成されたクロックパルスに基づいて、各種制御プログラムを実行して、遊技動作全般に係る制御を行う。ここで、メインCPU101の制御動作の一例としてリール停止制御について説明する。

The

メインCPU101は、リールインデックスを検出してから各リール3L,3C,3L(メインリール)のステッピングモータに対してパルスを出力した回数をカウントする。これにより、メインCPU101は、各リールの回転角度(主に、リールが図柄何個分だけ回転したか)を管理する。なお、リールインデックスとは、リールが一回転したことを示す情報である。このリールインデックスは、例えば、発光部及び受光部を有する光センサと、各リールの所定の位置に設けられ、各メインリールの回転により発光部と受光部との間に介在される検知片とを備えたリール位置検出部(不図示)により検出される。

The

ここで、各リール3L,3C,3L(メインリール)の回転角度の管理について、具体的に説明する。ステッピングモータに対して出力されたパルスの数は、メインRAM103に設けられたパルスカウンタによって計数される。そして、図柄1つ分の回転に必要な所定回数のパルスの出力がパルスカウンタで計数される毎に、メインRAM103に設けられた図柄カウンタが1ずつ加算される。図柄カウンタは、各リールに応じて設けられている。図柄カウンタの値は、リール位置検出部(不図示)によってリールインデックスが検出されるとクリアされる。

Here, the management of the rotation angle of each

すなわち、本実施形態では、図柄カウンタを管理することにより、リールインデックスが検出されてから図柄何個分の回転が行われたのかを管理する。したがって、各リールの各図柄の位置は、リールインデックスが検出される位置を基準として検出される。 That is, in the present embodiment, by managing the symbol counter, it is possible to manage how many symbols have been rotated since the reel index was detected. Therefore, the position of each symbol of each reel is detected with reference to the position where the reel index is detected.

メインROM102には、メインCPU101により実行される各種制御プログラム、各種データテーブル、副制御回路200に対して各種制御指令(コマンド)を送信するためのデータ等が記憶される。メインRAM103には、制御プログラムの実行により決定された内部当籤役等の各種データを格納する格納領域が設けられる。なお、メインROM102及びメインRAM103の内部構成(メモリーマップ)については、後述の図12を参照して詳述する。

The

外部バスインターフェース104は、マイクロプロセッサ91の外部に設けられた各種構成部(例えば、各リール等)が接続された外部信号バス(不図示)と、マイクロプロセッサ104とを電気的に接続するためのインターフェース回路である。クロック回路105は、例えば分周器(不図示)等を含んで構成され、クロックパルス発生回路92から入力されたCPU作動用のクロックパルス信号を、その他の構成部(例えば、タイマー回路113)で使用される周波数のクロックパルス信号に変換する。なお、クロック回路105で生成されたクロックパルス信号は、リセットコントローラ106にも出力される。

The

リセットコントローラ106は、電源管理回路93から入力されたリセット信号に基づいて、IAT(Illegal Address Trap)やWDT(watchdog timer)のリセットを行う。演算回路107は、乗算回路及び除算回路を含んで構成される。例えば、ソースプログラム上において、後述する「MUL(乗算)」命令(後述の図93B参照)を実行するときには、演算回路107がこの「MUL」命令に基づく乗算処理を実行する。

The

乱数回路110は、予め定められた範囲の乱数(例えば、0~65535又は0~255)を発生させる。また、図示しないが、乱数回路110は、2バイトのハードラッチ乱数を得るための乱数レジスタ0と、2バイトのソフトラッチ乱数を得るための乱数レジスタ1~3と、1バイトのソフトラッチ乱数を得るための乱数レジスタ4~7とで構成されている。なお、メインCPU101は、乱数回路110で発生させた所定範囲の乱数の中から1つの値を、例えば内部抽籤用の乱数値として抽出する。パラレルポート111は、マイクロプロセッサ91と、マイクロプロセッサ91の外部に設けられた各種回路(例えば、電源管理回路93等)との間で入出力される信号のポート(メモリーマップI/O)である。また、パラレルポート111は、乱数回路110及び割込みコントローラ112にも接続される。スタートスイッチ79はパラレルポート111のPI0~PI4のいずれかの入力ポートに接続され、スタートスイッチ79がオン状態になったタイミング(オンエッジ)で、パラレルポート111から乱数回路110の乱数レジスタ0へラッチ信号が出力される。そして、乱数回路110では、ラッチ信号が入力されることにより乱数レジスタ0がラッチされ、2バイトのハードラッチ乱数が取得される。

The

割込みコントローラ112は、パラレルポート111を介して電源管理回路93から入力される電断検知信号、又は、タイマー回路113から1.1172ms周期で入力されるタイムアウト信号に基づいて、メインCPU101による割込処理の実行タイミングを制御する。電源管理回路93から電断検知信号が入力された場合、又は、タイマー回路113からタイムアウト信号が入力された場合には、割込みコントローラ112は、割込処理開始指令を示す割込要求信号をメインCPU101に出力する。メインCPU101は、タイマー回路103からのタイムアウト信号に応じて割込みコントローラ112から入力される割込要求信号に基づいて、入力ポートチェック処理、リール制御処理、通信データ送信処理、7セグLED駆動処理、タイマー更新処理等の各種割込処理(後述の図158参照)を行う。

The interrupt

タイマー回路113(PTC)は、クロック回路105で生成されたクロックパルス信号(メインCPU作動用のクロックパルス信号を分周器(不図示)で分周された周波数のクロックパルス信号)で動作する(経過時間をカウントする)。そして、タイマー回路113は、1.1172msecの周期で割込みコントローラ112にタイムアウト信号(トリガー信号)を出力する。

The timer circuit 113 (PTC) operates with a clock pulse signal generated by the clock circuit 105 (a clock pulse signal having a frequency obtained by dividing the clock pulse signal for operating the main CPU by a divider (not shown)) ( Count the elapsed time). Then, the

第1シリアル通信回路114は、主制御基板71から副制御基板72にデータ(各種制御指令(コマンド))を送信する際のシリアル送信動作を制御する回路である。第2シリアル通信回路115は、主制御基板71から試験機用第2インターフェースボード302にデータを送信する際のシリアル送信動作を制御する回路である。

The first

<副制御回路>

次に、図10を参照して、副制御基板72に実装される副制御回路200(副制御手段)の構成について説明する。図10は、パチスロ1の副制御回路200の構成例を示すブロック図である。

<Secondary control circuit>

Next, with reference to FIG. 10, the configuration of the sub-control circuit 200 (sub-control means) mounted on the

副制御回路200は、主制御回路90と電気的に接続されており、主制御回路90から送信されるコマンドに基づいて演出内容の決定や実行等の処理を行う。副制御回路200は、基本的に、サブCPU201、サブRAM202、レンダリングプロセッサ203、描画用RAM204、ドライバ205を含んで構成される。

The

なお、サブCPU201は、ロムカートリッジ基板86に接続される。ドライバ205は、液晶中継基板87に接続される。すなわち、ドライバ205は、液晶中継基板87を介してプロジェクタ機構211及びサブ表示装置18に接続される。

The

サブCPU201は、主制御回路90から送信されたコマンドに応じて、ロムカートリッジ基板86に記憶されている制御プログラムに従い、映像、音、光の出力の制御を行う。ロムカートリッジ基板86は、基本的に、プログラム記憶領域とデータ記憶領域とによって構成される。

The

プログラム記憶領域には、サブCPU201が実行する制御プログラムが記憶される。例えば、制御プログラムには、主制御回路90との通信を制御するための主基板通信タスクや、演出用の乱数値を抽出し、演出内容(演出データ)の決定及び登録を行うための演出登録タスクを実行するための各種プログラムが含まれる。また、制御プログラムには、決定した演出内容に基づいて表示装置11による映像の表示を制御する描画制御タスク、LED群85等の光源による光の出力を制御するランプ制御タスク、スピーカ群84による音の出力を制御する音声制御タスク等を実行するための各種プログラムも含まれる。

The control program executed by the

データ記憶領域には、各種データテーブルを記憶する記憶領域、各演出内容を構成する演出データを記憶する記憶領域、映像の作成に関するアニメーションデータを記憶する記憶領域が含まれる。また、データ記憶領域には、BGMや効果音に関するサウンドデータを記憶する記憶領域、光の点消灯のパターンに関するランプデータを記憶する記憶領域等も含まれる。 The data storage area includes a storage area for storing various data tables, a storage area for storing effect data constituting each effect content, and a storage area for storing animation data related to video creation. Further, the data storage area includes a storage area for storing sound data related to BGM and sound effects, a storage area for storing lamp data related to a pattern of turning on and off light, and the like.

サブRAM202には、決定された演出内容や演出データを登録する格納領域や、主制御回路90から送信されるサブフラグ(内部当籤役)等の各種データを格納する格納領域が設けられる。

The

サブCPU201、レンダリングプロセッサ203、描画用RAM(フレームバッファを含む)204及びドライバ205は、演出内容により指定されたアニメーションデータに従って映像を作成し、作成した映像を表示装置11(プロジェクタ機構211)及び/又はサブ表示装置18に表示させる。なお、表示装置11(プロジェクタ機構211)及びサブ表示装置18は、副制御基板72により、それぞれ個別に制御される。

The

また、サブCPU201は、演出内容により指定されたサウンドデータに従ってBGMなどの音をスピーカ群84により出力させる。また、サブCPU201は、演出内容により指定されたランプデータに従ってLED群85の点灯及び消灯を制御する。

Further, the

<メインCPUが有する各種レジスタ>

次に、図11を参照しながら、メインCPU101が有する各種レジスタについて説明する。なお、図11は、メインCPU101に含まれる各種レジスタの概略構成図である。

<Various registers of the main CPU>

Next, various registers included in the

メインCPU101は、メイン・レジスタとして、アキュームレータA(以下、「Aレジスタ」という)、フラグ・レジスタF(フラグレジスタ)、汎用レジスタB(以下、「Bレジスタ」という)、汎用レジスタC(以下、「Cレジスタ」という)、汎用レジスタD(以下、「Dレジスタ」という)、汎用レジスタE(以下、「Eレジスタ」という)、汎用レジスタH(以下、「Hレジスタ」という)及び汎用レジスタL(以下、「Lレジスタ」という)を有する。また、メインCPU101は、サブ・レジスタとして、アキュームレータA′、フラグ・レジスタF′、汎用レジスタB′、汎用レジスタC′、汎用レジスタD′、汎用レジスタE′、汎用レジスタH′及び汎用レジスタL′を汎用レジスタとして有する。なお、各レジスタは、1バイトのレジスタで構成される。

As the main register, the

また、本実施形態では、BレジスタとCレジスタとをペアレジスタ(以下、「BCレジスタ」という)として用い、DレジスタとEレジスタとをペアレジスタ(以下、「DEレジスタ」という)として用いる。さらに、本実施形態では、HレジスタとLレジスタとをペアレジスタ(以下、「HLレジスタ」という)として用いる。 Further, in the present embodiment, the B register and the C register are used as a pair register (hereinafter referred to as "BC register"), and the D register and the E register are used as a pair register (hereinafter referred to as "DE register"). Further, in the present embodiment, the H register and the L register are used as a pair register (hereinafter referred to as "HL register").

フラグ・レジスタF,F′の各ビットには、図11に示すように、演算処理の結果等を示す所定のフラグ情報がセットされる。例えばビット6(D6)には、演算結果の判定処理において演算結果が「0」であるか否かを示すデータ(ゼロフラグ)がセットされる。具体的には、演算結果が「0」である場合、ビット6にデータ「1」がセットされ、演算結果が「0」でない場合には、ビット6にデータ「0」がセットされる。そして、演算結果の判定処理では、メインCPU101は、ビット6のデータ「0」/「1」を参照して判定(YES/NO)を行う。

As shown in FIG. 11, predetermined flag information indicating the result of arithmetic processing or the like is set in each bit of the flag registers F and F'. For example, the bit 6 (D6) is set with data (zero flag) indicating whether or not the calculation result is “0” in the calculation result determination process. Specifically, when the calculation result is "0", the data "1" is set in the

また、メインCPU101は、拡張レジスタQ(以下、「Qレジスタ」という)を有する。Qレジスタは、1バイトのレジスタで構成される。なお、本実施形態では、後述の各種処理フローの中で説明するように、ソースプログラム上において、このQレジスタを用いてアドレス指定を行う各種メインCPU101専用命令コードが設けられており、この命令コードの使用により、処理の効率化やメインROM102の容量削減などを実現している。なお、Qレジスタを用いてアドレス指定を行う各種メインCPU101専用命令コードでは、Qレジスタには、アドレスの上位側のアドレスデータ(アドレス値)が格納される。なお、Qレジスタには、メインCPU101のリセット直後に、初期値として「F0H」がセットされる。また、Qレジスタを用いた「LD Q,n(8ビットデータ)」命令において、「n」に任意の1バイトのデータをセットして該命令を実行することにより、Qレジスタの値を変更することができる。

Further, the

さらに、メインCPU101は、1バイトのレジスタで構成された、インタラプト・ページアドレス・レジスタI及びメモリ・リフレッシュ・レジスタR、並びに、2バイトのレジスタで構成された、インデックス・レジスタIX、インデックス・レジスタIY、スタックポインタSP及びプログラムカウンタPCを専用レジスタとして有する。

Further, the

<メインROM及びメインRAMの内部構成(メモリマップ)>

次に、図12A~図12Cを参照しながら、主制御回路90(マイクロプロセッサ91)に含まれるメインROM102及びメインRAM103の内部構成(以下「メモリマップ」という)について説明する。なお、図12Aは、メモリ全体のメモリマップを示す図であり、図12Bは、メインROM102のメモリマップを示す図であり、図12Cは、メインRAM103のメモリマップを示す図である。

<Internal configuration of main ROM and main RAM (memory map)>

Next, the internal configurations (hereinafter referred to as “memory maps”) of the

主制御回路90(マイクロプロセッサ91)が備えるメモリ全体のメモリマップでは、図12Aに示すように、アドレスの先頭(0000H)側から、メインROM102のメモリ領域、メインRAM103のメモリ領域、内蔵レジスタエリア及びXCSデコードエリアが、不使用領域を間に挟んでこの順で、それぞれ所定のアドレスに配置される。

In the memory map of the entire memory included in the main control circuit 90 (microprocessor 91), as shown in FIG. 12A, from the head (0000H) side of the address, the memory area of the

メインROM102のメモリマップでは、図12Bに示すように、メインROM102のアドレスの先頭(0000H)側から、プログラムエリア、データエリア、規定外エリア、商標記録エリア、プログラム管理エリア及びセキュリティ設定エリアが、この順で、それぞれ所定のアドレスに配置される。

In the memory map of the

なお、プログラムエリアには、遊技者により実施される遊技の遊技性に関連する各種制御処理において、メインCPU101により実行される各種処理の制御プログラムが記憶される。データエリアには、遊技者により実施される遊技の遊技性に関連する各種制御処理において、メインCPU101により使用される各種データ(例えば、内部抽籤テーブル等のデータテーブル、副制御回路42に対して各種制御指令(コマンド)を送信するためのデータ等)が記憶される。すなわち、プログラムエリアとデータエリアとからなる遊技用ROM領域(遊技用記憶領域)には、遊技店で遊技者が実際に行う遊技の遊技性に関連する制御処理(遊技性に関する処理)に必要な各種プログラム及び各種データが格納される。

In the program area, control programs for various processes executed by the

また、規定外エリアには、遊技者により実施される遊技の遊技性に直接関与しない各種処理(遊技性に影響を与えない処理)の制御プログラム及びデータが記憶される。例えば、パチスロ1の検定試験(試射試験)で使用されるプログラム及びデータ、電断時のチェックサム生成処理や電源復帰時のサムチェック処理などで使用される制御プログラム及びデータ、並びに、不正対策プログラム及びそれに必要なデータ等が、規定外エリアに格納される。

Further, in the non-regulated area, control programs and data of various processes (processes that do not affect the playability) that are not directly related to the playability of the game performed by the player are stored. For example, programs and data used in the

メインRAM103のメモリマップでは、図12Cに示すように、メインRAM103のアドレスの先頭(F000H)側から、遊技用RAM領域(所定格納領域、遊技用一時記憶領域)及び規定外RAM領域(規定外一時記憶領域)が、この順で、それぞれ所定のアドレスに配置される。

In the memory map of the

遊技用RAM領域には、遊技者により実施される遊技の遊技性に関連する制御プログラムの実行により決定された例えば内部当籤役等の各種データを一時的に格納する作業領域及びスタックエリアが設けられる。そして、各種データのそれぞれは、遊技用RAM領域内の所定アドレスの作業領域に格納される。 The game RAM area is provided with a work area and a stack area for temporarily storing various data such as an internal winning combination determined by executing a control program related to the game playability performed by the player. .. Then, each of the various data is stored in the work area of the predetermined address in the game RAM area.

また、規定外RAM領域には、遊技者により実施される遊技の遊技性に直接関与しない各種処理の作業領域となる規定外作業領域と、規定外スタックとが設けられる。本実施形態では、この規定外RAM領域を使用して、例えばサムチェック処理等の遊技者により実施される遊技の遊技性に直接関与しない各種処理が実行される。 Further, the non-standard RAM area is provided with a non-standard work area that is a work area for various processes that are not directly related to the playability of the game performed by the player, and a non-standard stack. In the present embodiment, various processes that are not directly related to the playability of the game performed by the player, such as a thumb check process, are executed using this non-standard RAM area.

上述のように、本実施形態のパチスロ1では、メインROM102内において、遊技者により実施される遊技の遊技性に直接関与しない各種処理に使用される各種プログラム及び各種データ(テーブル)を、遊技用ROM領域とは異なるアドレスに配置された規定外ROM領域(規定外記憶領域)に格納する。また、そのような遊技者により実施される遊技の遊技性に直接関与しない各種処理は、メインRAM103内において、遊技用RAM領域とは異なるアドレスに配置された規定外RAM領域を使用して行われる。

As described above, in the pachi-

このようなメインROM102の構成では、従来の規則上においてプログラム等の配置不可とされていたROM領域(規定外ROM領域)に、遊技者が実際に行う遊技そのものには不要なプログラム及びデータを配置することができる。それゆえ、本実施形態では、遊技用ROM領域の容量の圧迫を回避することができる。

In such a configuration of the

<遊技状態の遷移フロー>

次に、図13及び図14を参照しながら、本実施形態のパチスロ1の主制御回路90(メインCPU101)により管理される各種遊技状態及びその遷移フローについて説明する。なお、図13Aは、パチスロ1の基本的な遊技状態の遷移フロー図であり、図13Bは、その遊技状態の移行条件をまとめた表である。また、図14Aは、報知(ART)機能の作動の有無を考慮した遊技状態の遷移フロー図であり、図14Bは、その遊技状態の移行条件をまとめた表である。

<Transition flow of game state>

Next, various gaming states managed by the main control circuit 90 (main CPU 101) of the pachi-

[基本的な遊技状態の遷移フロー]

本実施形態のパチスロ1では、ボーナスゲームの種類として、ビッグボーナス(以下、「BB」と記す)が設けられる。BBは、第1種特別役物と呼ばれるレギュラーボーナス(以下、「RB」と記す)に係る役物連続作動装置であり、RBを連続して作動させる。

[Basic game state transition flow]

In the pachi-

それゆえ、本実施形態では、主制御回路90は、ボーナス役の当籤/作動(入賞)の有無に基づいて遊技状態を管理する。具体的には、図13Aに示すように、主制御回路90は、ボーナス役(後述の名称「F_BB1」,「F_BB2」の内部当籤役)の当籤/作動(入賞)の有無に基づいて、「ボーナス非当籤状態」、「フラグ間状態」及び「ボーナス状態」と称する3種類の遊技状態を管理する。

Therefore, in the present embodiment, the

なお、ボーナス非当籤状態は、ボーナスに非当籤であり、かつ、ボーナスが作動(入賞)していない状態であり、ボーナス状態は、ボーナスが作動している状態である。また、本実施形態では、ボーナス役が内部当籤役として決定されると、ボーナスが入賞するまで複数回の遊技に渡りボーナス役が内部当籤役として持ち越された状態が発生する。フラグ間状態は、ボーナス役が内部当籤役として持ち越されている状態、すなわち、ボーナス役が当籤し、かつ、ボーナスが作動していない状態である。 The bonus non-winning state is a state in which the bonus is not winning and the bonus is not activated (winning), and the bonus state is a state in which the bonus is activated. Further, in the present embodiment, when the bonus combination is determined as the internal winning combination, the bonus combination is carried over as the internal winning combination over a plurality of games until the bonus is won. The inter-flag state is a state in which the bonus combination is carried over as an internal winning combination, that is, a state in which the bonus combination is winning and the bonus is not activated.

なお、ボーナス役の当籤の有無は、メインRAM103に設けられる後述の当り要求フラグ格納領域(後述の図28~図30参照)及び持越役格納領域(後述の図31参照)に格納されるデータに基づいて管理される。また、ボーナスの作動(入賞)の有無は、メインRAM103に設けられる後述の遊技状態フラグ格納領域(後述の図32参照)に格納されるデータに基づいて管理される。

Whether or not the bonus combination is won is determined by the data stored in the hit request flag storage area (see FIGS. 28 to 30 described later) and the carry-over combination storage area (see FIG. 31 described later) provided in the

また、本実施形態では、図13Aに示すように、ボーナスが作動していない遊技状態(ボーナス非当籤状態及びフラグ間状態)において、リプレイに係る内部当籤役の種別及びその当籤確率が互いに異なる、RT0遊技状態~RT5遊技状態の6種類の状態(以下、それぞれ「RT0状態」~「RT5状態」という)が設けられる。なお、RT0状態、RT2状態及びRT5状態は、リプレイ役が内部当籤役として決定される確率が低確率となる遊技状態であり、RT1状態はリプレイ役が内部当籤役として決定される確率が中程度の中確率となる遊技状態である。また、RT3状態及びRT4状態は、リプレイ役が内部当籤役として決定される確率が高確率となる遊技状態である。なお、本実施形態では、ボーナス非当籤状態のRT状態は、RT0状態~RT4状態のいずれかとなり、フラグ間状態のRT状態はRT5状態となる。 Further, in the present embodiment, as shown in FIG. 13A, in the gaming state in which the bonus is not activated (bonus non-winning state and inter-flag state), the types of internal winning combinations related to the replay and the winning probabilities thereof are different from each other. Six types of states (hereinafter, referred to as "RT0 state" to "RT5 state") are provided from the RT0 gaming state to the RT5 gaming state. The RT0 state, RT2 state, and RT5 state are gaming states in which the probability that the replay combination is determined as the internal winning combination is low, and the RT1 state has a medium probability that the replay combination is determined as the internal winning combination. It is a game state with a medium probability. Further, the RT3 state and the RT4 state are gaming states in which the probability that the replay combination is determined as the internal winning combination is high. In the present embodiment, the RT state in the bonus non-winning state is any of the RT0 state to the RT4 state, and the RT state in the inter-flag state is the RT5 state.

それゆえ、本実施形態では、主制御回路90は、ボーナスが作動していない遊技状態(ボーナス非当籤状態及びフラグ間状態)において、さらに、リプレイに係る内部当籤役の種別及びその当籤確率に基づいて、RT1状態~RT5状態の6種類の状態も管理する。

Therefore, in the present embodiment, the

なお、RT0状態~RT5状態は、メインRAM103に設けられる後述の遊技状態フラグ格納領域(後述の図32参照)に格納されるデータに基づいて管理される。具体的には、本実施形態のパチスロ1では、RT1状態フラグ~RT5状態フラグの5つのRT状態を示すフラグが設けられ、これらのフラグのオン/オフ状態をメインRAM103により管理することによりRT状態が管理される。そして、主制御回路90は、オン状態であるRT状態フラグに対応するRT状態を現在のRT状態として特定する。なお、全てのRT状態フラグがオフ状態である場合には、主制御回路90は、現在のRT状態がRT0状態であると特定する。

The RT0 state to the RT5 state are managed based on the data stored in the game state flag storage area (see FIG. 32 described later) provided in the

図13A及び13Bに示すように、ボーナス非当籤状態においてボーナス役(後述の名称「F_BB1」,「F_BB2」の内部当籤役)が内部当籤役として決定されると(移行条件(1)が成立すると)、主制御回路90は、遊技状態をボーナス非当籤状態からフラグ間状態に移行させる。また、フラグ間状態においてボーナス役が入賞すると(移行条件(2)が成立すると)、主制御回路90は、遊技状態をフラグ間状態からボーナス状態に移行させる。

As shown in FIGS. 13A and 13B, when the bonus combination (internal winning combination of the names "F_BB1" and "F_BB2" described later) is determined as the internal winning combination in the bonus non-winning state (when the transition condition (1) is satisfied). ), The

また、ボーナス状態において規定枚数(216枚)を超えるメダルが払い出され、ボーナス状態が終了すると(移行条件(3)が成立すると)、主制御回路90は、遊技状態をボーナス状態からRT1状態(ボーナス非当籤状態)に移行させる。

Further, when the number of medals exceeding the specified number (216) is paid out in the bonus state and the bonus state ends (when the transition condition (3) is satisfied), the

RT1状態において、20ゲームが経過すると(移行条件(4)が成立すると)、主制御回路90は、遊技状態をRT1状態からRT0状態に移行させる。また、RT1状態において、20ゲームが経過する前に、略称「ベルこぼし目」に係る図柄組合せ(後述の図28参照)が有効ライン上に表示されると(移行条件(5)が成立すると)、主制御回路90は、遊技状態をRT1状態からRT2状態に移行させる。

When 20 games have elapsed in the RT1 state (when the transition condition (4) is satisfied), the

RT0状態において、略称「ベルこぼし目」に係る図柄組合せが有効ライン上に表示されると(移行条件(5)が成立すると)、主制御回路90は、遊技状態をRT0状態からRT2状態に移行させる。RT2状態において、略称「RT3移行リプ」に係る図柄組合せ(後述の図28参照)が有効ライン上に表示されると(移行条件(6)が成立すると)、主制御回路90は、遊技状態をRT2状態からRT3状態に移行させる。

In the RT0 state, when the symbol combination related to the abbreviation "bell spilled eye" is displayed on the valid line (when the transition condition (5) is satisfied), the

RT3状態において、略称「RT4移行リプ」に係る図柄組合せ(後述の図28参照)が有効ライン上に表示されると(移行条件(7)が成立すると)、主制御回路90は、遊技状態をRT3状態からRT4状態に移行させる。また、RT3状態において、略称「ベルこぼし目」又は「RT2移行リプ」に係る図柄組合せ(後述の図28参照)が有効ライン上に表示されると(移行条件(8)が成立すると)、主制御回路90は、遊技状態をRT3状態からRT2状態に遊技状態を移行させる。さらに、RT4状態において、略称「ベルこぼし目」又は「RT2移行リプ」に係る図柄組合せが有効ライン上に表示されると(移行条件(8)が成立すると)、主制御回路90は、遊技状態をRT4状態からRT2状態に遊技状態を移行させる。

In the RT3 state, when the symbol combination (see FIG. 28 described later) related to the abbreviation "RT4 transition lip" is displayed on the valid line (when the transition condition (7) is satisfied), the

なお、略称「ベルこぼし目」に係る図柄組合せは、後述の名称「F_3択ベル_1st」、「F_3択ベル_2nd」又は「F_3択ベル_3rd」に係る内部当籤役(小役)が決定され、かつ、停止操作の順序が該小役の種別ごとに定められた押し順に対して不正解であるときに表示される図柄の組合せである(後述の図24参照)。略称「RT2移行リプ」に係る図柄組合せは、後述の名称「F_維持リプ_1st」、「F_維持リプ_2nd」又は「F_維持リプ_3rd」に係る内部当籤役(リプレイ役)が決定され、かつ、停止操作の順序が該リプレイ役の種別ごとに定められた押し順に対して不正解であるときに表示される図柄の組合せである。 As for the symbol combination related to the abbreviation "bell spilled eyes", the internal winning combination (small combination) related to the names "F_3 selection bell_1st", "F_3 selection bell_2nd" or "F_3 selection bell_3rd" described later is determined. Moreover, it is a combination of symbols displayed when the order of the stop operation is incorrect with respect to the push order determined for each type of the small winning combination (see FIG. 24 described later). As for the symbol combination related to the abbreviation "RT2 transition lip", the internal winning combination (replay combination) related to the names "F_maintenance lip_1st", "F_maintenance lip_2nd" or "F_maintenance lip_3rd" described later is determined, and It is a combination of symbols displayed when the order of the stop operation is incorrect with respect to the push order determined for each type of the replay combination.

略称「RT3移行リプ」に係る図柄組合せは、後述の名称「F_RT3リプ_1st」、「F_RT3リプ_213」、「F_RT3リプ_231」又は「F_RT3リプ_3rd」に係る内部当籤役(リプレイ役)が決定され、かつ、停止操作の順序が該リプレイ役の種別ごとに定められた押し順に対して正解であるときに表示される図柄の組合せである。また、略称「RT4移行リプ」に係る図柄組合せは、後述の名称「F_RT4リプ_123」、「F_RT4リプ_132」、「F_RT4リプ_2nd」又は「F_RT4リプ_3rd」に係る内部当籤役(リプレイ役)が決定され、かつ、停止操作の順序が該リプレイ役の種別ごとに定められた押し順に対して正解であるときに表示される図柄の組合せである。 As for the symbol combination related to the abbreviation "RT3 transition lip", the internal winning combination (replay role) related to the names "F_RT3 lip_1st", "F_RT3 lip_213", "F_RT3 lip_231" or "F_RT3 lip_3rd" described later is determined. Moreover, it is a combination of symbols displayed when the order of the stop operation is the correct answer for the push order determined for each type of the replay combination. Further, the symbol combination related to the abbreviation "RT4 transition lip" has an internal winning combination (replay role) related to the names "F_RT4 lip_123", "F_RT4 lip_132", "F_RT4 lip_2nd" or "F_RT4 lip_3rd" described later. It is a combination of symbols that are determined and displayed when the order of the stop operation is the correct answer for the push order determined for each type of the replay combination.

[報知(ART)機能の作動の有無を考慮した遊技状態の遷移フロー]

本実施形態では、主制御回路90(メインCPU101)により、遊技者にとって有利な停止操作を報知する機能(ART機能)の作動の有無が決定される。それゆえ、本実施形態では、ボーナス非作動状態においてART機能の作動/非作動状態も遊技状態として管理する。

[Transition flow of game state considering whether or not the notification (ART) function is activated]

In the present embodiment, the main control circuit 90 (main CPU 101) determines whether or not the function (ART function) for notifying a stop operation advantageous to the player is activated. Therefore, in the present embodiment, the activated / non-activated state of the ART function is also managed as the gaming state in the bonus non-operating state.

本実施形態のパチスロ1では、図14Aに示すように、主制御回路90は、非ボーナス作動状態において、報知(ART)の有無に基づいて「一般遊技状態」と「ART遊技状態」とを別個の遊技状態として管理する。すなわち、報知(ART)の有無を考慮した遊技状態の管理では、図14Aに示すように、主制御回路90は、大きな分類として、「ボーナス状態」、「一般遊技状態」及び「ART遊技状態」の3種類の遊技状態を管理する。

In the pachi-

なお、一般遊技状態は、基本的には、遊技者にとって有利な停止操作の情報を報知しない遊技状態(非ART)であり、遊技者にとって不利な遊技状態である。また、一般遊技状態は、RT0~RT4状態のいずれかの状態であり、かつ、ART非当籤の遊技状態である。 The general gaming state is basically a gaming state (non-ART) in which information on a stop operation advantageous to the player is not notified, and is a gaming state disadvantageous to the player. Further, the general gaming state is any of the RT0 to RT4 states, and is an ART non-winning gaming state.

一方、ART遊技状態は、遊技者にとって有利な停止操作の情報を報知する遊技状態であり、遊技者にとって有利な遊技状態である。また、ART遊技状態は、基本的には、RT4状態であり、かつ、ART当籤中の遊技状態である。なお、本実施形態では、ART当籤後、RT状態がRT4状態まで移行すると、ART遊技が開始される。 On the other hand, the ART gaming state is a gaming state in which information on a stop operation advantageous to the player is notified, and is a gaming state advantageous to the player. Further, the ART gaming state is basically the RT4 state and the gaming state during the ART winning. In this embodiment, when the RT state shifts to the RT4 state after winning the ART, the ART game is started.

また、本実施形態では、図14Aに示すように、一般遊技状態として、「通常遊技状態」及び「CZ(チャンスゾーン)」と称する2種類の状態が設けられる。 Further, in the present embodiment, as shown in FIG. 14A, two types of states called "normal gaming state" and "CZ (chance zone)" are provided as general gaming states.

通常遊技状態は、遊技者にとって最も不利な遊技状態であるが、通常遊技状態の遊技ではCZへの移行抽籤を行っている。そして、図14A及び14Bに示すように、通常遊技状態の遊技において、CZへの移行抽籤に当籤すると(移行条件(A)が成立すると)、主制御回路90は、遊技状態を、通常遊技状態からCZに移行させる。

The normal game state is the most disadvantageous game state for the player, but in the game in the normal game state, a lottery for shifting to the CZ is performed. Then, as shown in FIGS. 14A and 14B, in the game in the normal gaming state, when the lottery for transition to the CZ is won (when the transition condition (A) is satisfied), the

CZは、ART遊技状態への移行に対する期待度が高い遊技状態(チャンスゾーン)であり、CZ中の遊技ではARTへの移行抽籤が行われている。そして、図14A及び14Bに示すように、CZ中の遊技において、ARTへの移行抽籤に非当籤である場合には(移行条件(B)が成立すると)、主制御回路90は、遊技状態を、CZから通常遊技状態に移行させる。一方、CZ中の遊技において、ARTへの移行抽籤に当籤すると(移行条件(C)が成立すると)、主制御回路90は、遊技状態を、CZからART遊技状態に移行させる。この際、図14Aには示さないが、主制御回路90は、遊技状態を、CZから後述のART準備状態を経由してART遊技状態(後述の通常ART又はCT)に移行させる。

The CZ is a gaming state (chance zone) in which the expectation for the transition to the ART gaming state is high, and the lottery for the transition to the ART is performed in the game during the CZ. Then, as shown in FIGS. 14A and 14B, in the game in CZ, when the lottery for transition to ART is not won (when the transition condition (B) is satisfied), the

ART遊技状態は、上述のように、ART当籤後にRT状態がRT4状態まで移行すると開始される。なお、図13Aで示したように、RT4状態は、RT0~RT2状態からRT3状態を経由して移行するので、ART当籤後であってもすぐにART遊技状態が開始されない。そこで、本実施形態のパチスロ1では、ART当籤後からRT状態がRT4状態に移行するまでの期間の遊技状態をART準備状態とする。そして、このART準備状態の遊技では、RT状態をRT4状態に移行させるために必要な停止操作の情報が報知される。

As described above, the ART gaming state is started when the RT state shifts to the RT4 state after winning the ART. As shown in FIG. 13A, since the RT4 state shifts from the RT0 to RT2 states via the RT3 state, the ART gaming state is not started immediately even after winning the ART. Therefore, in the pachi-

また、本実施形態では、図14Aに示すように、ART遊技状態として、遊技性が互いに異なる、「通常ART」及び「CT(上乗せチャンス)」と称する2種類の状態が設けられる。 Further, in the present embodiment, as shown in FIG. 14A, two types of ART gaming states, called "normal ART" and "CT (additional chance)", in which the playability is different from each other, are provided.

通常ARTは、所定ゲーム数の期間、遊技者にとって有利な停止操作(例えば、払い出されるメダルの枚数が多い図柄組合せを表示させるための停止操作や、RT4状態を維持するために必要な停止操作)が報知される遊技状態である。また、通常ART中の遊技では、CTへの移行抽籤が行われる。 Normally, ART is a stop operation that is advantageous for the player for a predetermined number of games (for example, a stop operation for displaying a symbol combination having a large number of medals to be paid out, or a stop operation necessary for maintaining the RT4 state). Is a gaming state to be notified. In addition, in a game during normal ART, a lottery for transition to CT is performed.

CTは、遊技者にとって有利な停止操作が報知されるとともに、特定期間(1セット8ゲームの期間)、通常ARTの継続期間を上乗せすることが可能となる遊技状態であり、上乗せチャンスゾーンとして機能する遊技状態である。また、CT中では、通常ARTの継続期間を消化せずに遊技が行われる。なお、CT中の遊技性については、後述の図52A~52Cを参照して後で詳述する。 CT is a gaming state in which a player is notified of an advantageous stop operation and can add a normal ART duration for a specific period (a period of 8 games per set), and functions as an additional chance zone. It is a game state to play. Also, during CT, the game is usually played without digesting the duration of ART. The playability during CT will be described in detail later with reference to FIGS. 52A to 52C described later.

図14A及び14Bに示すように、通常ART中の遊技において、CTへの移行抽籤に当籤すると(移行条件(D)が成立すると)、主制御回路90は、遊技状態を、通常ARTからCTに遊技状態を移行させる。また、通常ARTにおいて、当該通常ARTの継続期間が終了すると(移行条件(E)が成立すると)、主制御回路90は、遊技状態を、通常ARTから一般遊技状態(通常遊技状態又はCZ)に移行させる。なお、本実施形態では、ゲーム数により通常ARTの継続期間を管理するが、本発明はこれに限定されず、通常ARTの継続期間の管理方法は任意である。例えば、通常ARTの継続期間を、通常ART中に払い出されるメダルの枚数や差枚数により管理してもよいし、通常ART中にメダルの払い出しに影響を与える報知を行った回数(ナビ回数)により管理してもよい。

As shown in FIGS. 14A and 14B, in a game during normal ART, when the lottery for transition to CT is won (when the transition condition (D) is satisfied), the

図14A及び14Bに示すように、CT中の遊技において、CTの継続期間(1セット8ゲーム)が終了すると(移行条件(F)が成立すると)、主制御回路90は、遊技状態を、CTから通常ARTに移行させる。

As shown in FIGS. 14A and 14B, in the game during CT, when the duration of CT (1 set of 8 games) ends (when the transition condition (F) is satisfied), the

また、図14Aに示すように、一般遊技状態(通常遊技状態又はCZ)又はART遊技状態(通常ART又はCT)において、ボーナス役が入賞すると(図13A及び13B中で説明した移行条件(2)が成立すると)、主制御回路90は、遊技状態を、一般遊技状態又はART遊技状態からボーナス状態に移行させる。

Further, as shown in FIG. 14A, when the bonus combination is won in the general gaming state (normal gaming state or CZ) or ART gaming state (normal ART or CT) (transition condition (2) described in FIGS. 13A and 13B). When is established), the

ボーナス状態の遊技では、上述のように、ARTへの移行抽籤を行っており、ボーナス状態の遊技において、ARTへの移行抽籤が非当籤である場合には(移行条件(G)が成立すると)、主制御回路90は、遊技状態を、ボーナス状態から一般遊技状態(通常遊技状態又はCZ)に移行させる。ただし、ART遊技状態(通常ART又はCT)からボーナス状態に移行していた場合には、ボーナス状態の遊技においてARTの移行抽籤に非当籤であっても、主制御回路90は、遊技状態を、ボーナス状態からART遊技状態(通常ART又はCT)に移行させる。一方、ボーナス状態の遊技において、ARTへの移行抽籤に当籤すると(移行条件(H)が成立すると)、主制御回路90は、遊技状態を、ボーナス状態からART遊技状態(通常ART又はCT)に移行させる。なお、上述のように、ボーナス状態の終了時には、RT状態がRT1状態に移行するので、ボーナス状態からART遊技状態に遊技状態を移行する場合には、主制御回路90は、遊技状態を、ART準備状態を経由してART遊技状態に移行させる。

In the game in the bonus state, as described above, the lottery for transition to ART is performed, and in the game in the bonus state, if the lottery for transition to ART is non-winning (when the transition condition (G) is satisfied). , The

<メインROMに記憶されているデータテーブルの構成>

次に、図15~図27を参照して、メインROM102に記憶されている各種データテーブルの構成について説明する。なお、一般遊技状態中及びART遊技状態中の遊技性(CZ、通常ART,CTの遊技性)に係る各種抽籤で用いられる各種データテーブルについては、別途、各遊技性の説明と一緒に後述する。

<Structure of data table stored in main ROM>

Next, the configurations of various data tables stored in the

[図柄配置テーブル]

まず、図15を参照して、図柄配置テーブルについて説明する。図柄配置テーブルは、左リール3L、中リール3C及び右リール3Rのそれぞれの回転方向における各図柄の位置と、各位置に配置された図柄の種類を特定するデータ(以下、図柄コード(図15中の図柄コード表を参照)という)との対応関係を規定する。

[Design layout table]

First, the symbol arrangement table will be described with reference to FIG. The symbol arrangement table is data that specifies the position of each symbol in each rotation direction of the

図柄配置テーブルでは、リールインデックスが検出されたときに、リール表示窓4の枠内における各リールの中段領域に位置する図柄の位置を「0」と規定する。そして、各リールにおいて、図柄位置「0」を基準としてリールの回転方向(図15中の図柄位置「19」から図柄位置「0」に向かう方向)に進む順に、図柄カウンタの値に対応する「0」~「19」が、図柄位置として、各図柄に割り当てられる。

In the symbol arrangement table, when the reel index is detected, the position of the symbol located in the middle region of each reel in the frame of the

すなわち、図柄カウンタの値(「0」~「19」)と、図柄配置テーブルとを参照することにより、リール表示窓4の枠内における各リールの上段領域、中段領域及び下段領域に表示されている図柄の種類を特定することができる。なお、本実施形態では、図柄として、「白7」、「青7」、「チリ上1」、「チリ上2」、「チリ下」、「リプレイ」、「帽子」、「サボテン1」、「サボテン2」及び「サボテン3」の10種類の図柄を用いる。

That is, by referring to the value of the symbol counter ("0" to "19") and the symbol arrangement table, it is displayed in the upper region, the middle region, and the lower region of each reel in the frame of the

また、本実施形態では、図柄コード表に示すように、図柄「白7」(図柄コード1)には、データとして「00000001」が割り当てられ、図柄「青7」(図柄コード2)には、データとして「00000010」が割り当てられている。図柄「チリ上1」(図柄コード3)には、データとして「00000011」が割り当てられ、図柄「チリ上2」(図柄コード4)には、データとして「00000100」が割り当てられている。

Further, in the present embodiment, as shown in the symbol code table, "00000001" is assigned as data to the symbol "white 7" (symbol code 1), and the symbol "blue 7" (symbol code 2) is assigned. "00000010" is assigned as data. The symbol "

図柄「チリ下」(図柄コード5)には、データとして「00000101」が割り当てられ、図柄「リプレイ」(図柄コード6)には、データとして「00000110」が割り当てられている。図柄「帽子」(図柄コード7)には、データとして「00000111」が割り当てられ、図柄「サボテン1」(図柄コード8)には、データとして「00001000」が割り当てられている。また、図柄「サボテン2」(図柄コード9)には、データとして「00001001」が割り当てられ、図柄「サボテン3」(図柄コード10)には、データとして「00001010」が割り当てられている。

"00000011" is assigned as data to the symbol "Chile bottom" (symbol code 5), and "00000011" is assigned as data to the symbol "replay" (symbol code 6). The symbol "hat" (symbol code 7) is assigned "000000111" as data, and the symbol "

[内部抽籤テーブル]

次に、図16及び図17を参照して、内部当籤役を決定する際に参照される内部抽籤テーブルについて説明する。なお、図16は、RT0状態~RT4状態のそれぞれにおいて参照される内部抽籤テーブルである。また、図17Aは、RT5状態において参照される内部抽籤テーブルであり、図17Bは、ボーナス状態において参照される内部抽籤テーブルである。

[Internal lottery table]

Next, the internal lottery table referred to when determining the internal winning combination will be described with reference to FIGS. 16 and 17. Note that FIG. 16 is an internal lottery table referred to in each of the RT0 state to the RT4 state. Further, FIG. 17A is an internal lottery table referenced in the RT5 state, and FIG. 17B is an internal lottery table referenced in the bonus state.

内部抽籤テーブルは、遊技状態毎に設けられ、各種内部当籤役と、各内部当籤役が決定されるときの抽籤値との対応関係を規定する。なお、抽籤値は、予め設定されたボーナス役や小役等の内部当籤の期待値を調整するための設定(設定1~6)毎に規定される。この設定は、例えば、リセットスイッチ76及び設定用鍵型スイッチ54(図7参照)を用いて変更される。

The internal lottery table is provided for each game state, and defines the correspondence between various internal winning combinations and the lottery value when each internal winning combination is determined. The lottery value is defined for each setting (

本実施形態の内部抽籤処理では、まず、乱数回路110の乱数レジスタ0により、予め定められた数値の範囲(例えば、0~65535)から抽出される乱数値を、各内部当籤役に対応して規定された抽籤値で順次加算する。次いで、抽籤結果(抽籤値+乱数値)が65535を超えたか否か(抽籤結果がオーバーフローしたか否か)の判定を行う。そして、所定の内部当籤役において、抽籤結果が65535を超えた場合、該内部当籤役が当籤したと判定される。なお、本実施形態の内部抽籤処理では、抽出した乱数値に抽籤値を加算して抽籤を行う例を説明したが、本発明はこれに限定されず、乱数値から抽籤値を減算して、減算結果(抽籤結果)が「0」を下回ったか否か(抽籤結果がアンダーフローしたか否か)を判定して、内部抽籤の当籤/非当籤を決定してもよい。

In the internal lottery process of the present embodiment, first, a random number value extracted from a predetermined numerical range (for example, 0 to 65535) by the