JP6533643B2 - マイクロプロセッサ及びこれを使用した電子機器 - Google Patents

マイクロプロセッサ及びこれを使用した電子機器 Download PDFInfo

- Publication number

- JP6533643B2 JP6533643B2 JP2014051308A JP2014051308A JP6533643B2 JP 6533643 B2 JP6533643 B2 JP 6533643B2 JP 2014051308 A JP2014051308 A JP 2014051308A JP 2014051308 A JP2014051308 A JP 2014051308A JP 6533643 B2 JP6533643 B2 JP 6533643B2

- Authority

- JP

- Japan

- Prior art keywords

- rename

- data

- renaming

- checkpoint

- rob

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/22—Microcontrol or microprogram arrangements

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30098—Register arrangements

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3836—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution

- G06F9/3838—Dependency mechanisms, e.g. register scoreboarding

- G06F9/384—Register renaming

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3854—Instruction completion, e.g. retiring, committing or graduating

- G06F9/3856—Reordering of instructions, e.g. using queues or age tags

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3861—Recovery, e.g. branch miss-prediction, exception handling

- G06F9/3863—Recovery, e.g. branch miss-prediction, exception handling using multiple copies of the architectural state, e.g. shadow registers

Landscapes

- Engineering & Computer Science (AREA)

- Software Systems (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Retry When Errors Occur (AREA)

- Advance Control (AREA)

- Executing Machine-Instructions (AREA)

Description

一部命令語はブランチングポイントを発生させ、実行の1つの経路が他の経路に優先して選択される。

仮にマイクロプロセッサが選択する経路に対する正確な推論的な予測(speculative prediction)を実行し、その経路にしたがって予め命令語(instruction)を実行すれば、マイクロプロセッサは向上した速度を有することができる。

非順次的CPUの課題は、書込み後書込み(WAW:Write−After−Write)と書込み後読出し(WAR:Write−After−Read)のような危険要素である。

このような危険要素は、レジスター再命名(rename)によって防止され得り、これは再命名されたソース及び目的地レジスターを持続的に把握する再命名テーブルの助けによって実現可能である。

フラッシュは、ブランチが非順次的に実行され得るので、誤りを予測されたブランチの命令語より古い命令語が再書込み(rewrite)を待機することができるという点で問題である。

このような古い命令語に対する再命名情報(rename information)は再命名テーブルに再構成されなければならない。

再構成過程の間に再命名ロジックは、パイプのフロントエンドが再命名のために新しい命令語を伝送することを停止しなければならない。このような停止は遅延をもたらし、ブランチの予測ミスに対するペナルティー(penalty)であるとすることができる。

このようなペナルティーは再構成遅延のみならず、リダイレクション(redirection)遅延及びパイプフロントエンドの深さによって決定される。

このスキームで、各ブランチの命令語は新しいチェックポイントウインドウを開始する。

しかしながら、このようなアプローチは、機械で許諾されて進行中である(in−flight)ブランチが存在して、多いチェックポイントが要求されるので、高級な領域にあるという短所がある。

前記再命名テーブルは、静的関係の側面で許諾される場合のみ、前記チェックポイントテーブルに格納された前記再命名データを利用して再構成されることを特徴とする。

再命名データを生成する再命名器(renamer)をさらに有し、前記再命名テーブルは、前記再命名器から前記再命名データを受信することが好ましい。

クロックサイクルを定義するパルスを出力するクロックをさらに有し、前記再命名テーブルの再構成において、1つの前記チェックポイントテーブルから前記再命名テーブルへの再命名データのコピーは、前記クロックサイクルの中の1つのサイクル内で行われるものであることが好ましい。

再命名データが前記再命名テーブルからフラッシュされる場合、リオーダーバッファエントリのリオーダーバッファ再構成ウインドウが定義され、前記リオーダーバッファから前記再命名テーブルにコピーされる前記再構成再命名データの部分は、前記リオーダーバッファ再構成ウインドウ内に存在することが好ましい。

前記マイクロオペレーションの実行において、予測ミスを感知するためのブランチ実行ロジックをさらに含み、前記予測ミスが感知されたことに応答して、前記再命名データは、前記再命名テーブルからラッシュされることが好ましい。

クロックサイクルを定義するパルスを出力するクロックをさらに含み、前記再命名データの前記チェックポイントされたバーションが、前記クロックサイクル中の1つのサイクル内で前記チェックポイントテーブルから前記再命名テーブルにコピーされることが好ましい。

予測ミスを感知するためのブランチ実行ロジックをさらに有し、前記予測ミスが感知されたことに応答して前記再命名テーブルは、フラッシュされることが好ましい。

再命名データを生成する再命名器をさらに有し、前記再命名テーブルは、前記再命名器から前記再命名データを受信することが好ましい。

クロックサイクルを定義するパルスを出力するクロックをさらに有し、前記再命名テーブルの再構成において、1つの前記チェックポイントテーブルから前記再命名テーブルへの再命名データのコピーは、前記クロックサイクルの中の1つのサイクル内で行われるものであることが好ましい。

マイクロプロセッサ110は命令語を受信し、この命令語をマイクロオペレーション(以下、micro−ops)として知られるマイクロ命令語(micro−operation)にデコーディングするデコーダー120を含む。

図1では、3つの実行ユニット、即ち、実行ユニット−A(151)、実行ユニット−B(152)、実行ユニット−C(153)が示される。但し、ユニットの名は例示として示したものであり、本発明の技術的思想はこれに限定されない。

このような付加的な構成要素の中の1つは、結局のところ、「micro−ops」を実行ユニットに発送する(dispatching)ように提供されるディスパッチャー140である。

図1の例で、ディスパッチングは、3つのスケジューラー、即ち、スケジューラー−A(141)、スケジューラー−B(142)、及びスケジューラー−C(143)の中の1つの直前で実行される。

スケジューラーは、「micro−ops」を実行ユニット(151、152、153)に伝送する。この実行ユニットは物理的レジスターファイルPRF(Physical Register File)150からソースを読み出して、「micro−ops」を実行する。当業者は上述した内容がパイプの構造に対する一実施形態に過ぎなく、他の構造が可能であることを明確に理解できる。

再命名器130は、「micro−ops」にしたがって再命名データを生成する。

マイクロプロセッサ110は、さらに再命名テーブル136を含む。

再命名(rename)テーブル136は、再命名データを格納し、矢印(符号135)にしたがって再命名器130から受信する。

ROB160は、図1に個別的に開示していないROBエントリを含む。

以下で詳述するが、ROB160は、各々ROBエントリの中で可変的な1つのエントリをポインティングするリタイアポインター(Retire Pointer)とフラッシュポインター(Flush Ponter)を含む。

ROB160は循環されることもあり(circular)、循環されないこともあり得る。

一実施形態においては、各ROBエントリは、1つの「micro−ops」を格納するが、他の実施形態では、さらに多い「micro−ops」が1つのROBエントリに格納され得る。

ROBデータ162は、望ましくは、再命名テーブル136に格納された再命名データに応答する再構成再命名データ182を含む。

図1の実施形態でROBデータ162は、ディスパッチャー140から受信する。

CPTに対して可能である具現化は、以下でさらに詳細に敍述する。

CPT170は、再命名テーブル136とその広さが同一である。

CPT170は、図1に個別的には示さなかったがCPTエントリを有する。

CPTエントリの個数は、再命名テーブル136の個数と同一であり、これはCPTが再命名テーブル136のような深さ(depth)を有することを意味する。

CPTエントリの数はCPT深さを定義する。

再命名データのチェックポイントされたバーション180は、再命名データを生成する任意のバーションであるか、或いは、再命名データそれ自体であり、このような場合、再命名データはCPT170に格納されるので、チェックポイントされた再命名データ(check−pointed rename data)180と称される。

図1の実施形態で、再命名データのチェックポイントされたバーション180は、ディスパッチャー140から受信する。

静的関係(符号188)は、以下で詳述するように、固定される。

このような方式でROBエントリに新しい「micro−ops」が割り当てられれば、選択されたCPTエントリは、「micro−ops」が目的地を有する場合、「micro−ops」に対する目的地再命名情報(destination rename information)としてアップデートされる。

図1の実施形態で、マイクロプロセッサ110は、ブランチ実行ロジック157を含む。

ブランチ実行ロジック157は、フラッグ(符号190)で示される「micro−ops」の実行の中の予測ミス(符号190)を感知することができる。

再命名テーブル136は、予測ミス(符号190)の感知に応答してフラッシュされる。

再構成の目的のために、マイクロプロセッサ110は、リタイアチェックポイントデータ(retire check−point data)を格納するリタイアテーブル138を包含することができる。

リタイアチェックポイントデータは、再構成の開始過程で矢印(符号139)にしたがって再命名テーブル136にコピーされ得る。

再構成の目的のために、フラッシュされた再命名データは、リタイアテーブルからの初期コピーを追加的に、データの2つのデータソース(data of sources)から再命名テーブル136に再格納することができる。

多量流入は、以下で説明するように、静的関係(符号188)の観点から許諾される場合、同時に生じるコピーで具現され得る。

第2に、ROBデータ162内の再構成再命名データ182の少なくとも一部分は、矢印(符号160)にしたがってROB160から再命名テーブル136にコピーされ、これは“walking the ROB”としても公知されたプロセスである。

このような具現化は、プロセッサ時間を倹約するために、矢印(符号165)のコピーが成される間に、矢印(符号175)の同時コピーを経て再構成の目的のために具現することができることを分かる。実施形態は以下で記述する。

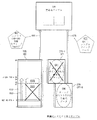

より具体的には、ROB260は、ROB“0”から“95”に命名された96個のエントリを有する。

ROB260は、ROBエントリの中で任意の数を有することができる。そして、1つのCPTが提供される。

この場合、ROBチェックポイントウインドウは、ROBエントリ“0”から“47”になされたグループである。

何らかのグループであることとは関係なく、ROBチェックポイントウインドウは、96個のROBチェックポイントウインドウに対して固定される。

このように、静的関係(符号288−1)は、ROB、より具体的にはROBチェックポイントウインドウが、CPT270にマッピングされる方法を示す。

このマッピングは、しばしば連関(association)であると称される。

本実施形態で、ROB260の中でROBエントリ“48”から“95”まではCPT270にマッピングされない。

仮にCPTからのコピーが許容されれば、この過程はより早くなり得る。

適用可能である静的関係(この実施形態で、符号288−1)は、ROB260からのみでなく、CPT270からも再構成をしなければならないか否か、及びどの程度に再構成しなければならないかに対して部分的に関与する。

実際には、静的関係(符号288−1)の観点から許諾されることによって、CPT270からのコピーが行われる。

許諾される場合に対する実施形態を以後に開示する。

したがって、ROB260がウォーキング(walking)されなければならないさらに多いシナリオが存在し、このようなシナリオは以下でより詳細に説明される。

図2Aとは異なり、すべてのROBエントリが、上述されたCPT又は付加的なCPTにマッピングされる。

図2B、図2Cを参照して、2つの実施形態を開示する。

ROB261は、2つの静的ROBチェックポイントウインドウ、即ち“0”から“47”のROBエントリを含むウインドウ、ROBエントリ“48”から“95”を含むウインドウに分けられる。

また、2つのCPT、即ち、CPT−0(271)及びCPT−1(272)が存在する。

CPT(271、272)は、再命名テーブルの深さと同一の深さを有する。

図2Bの実施形態で、ROBチェックポイントウインドウ−0とCPT271との間の連関と、ROBチェックポイントウインドウ−1とCPT272との間の連関に、図に示す静的関係(符号288−2)が存在する。

また、各々ROB263のROBチェックポイントウインドウに対応する4つのCPT、即ちCPT−0(273)、CPT−1(274)、CPT−2(275)、及びCPT−3(276)が存在する。

発明を実施するために要求されるものではないが、4つのROBチェックポイントウインドウの各々は同一の深さを有する。

静的関係(符号288−3)は、静的関係(符号288−2)と同様に、固定された一対一の連関関係のグループに対するものである。

以下と合わせて、大部分の場合、図2Cの実施形態は、4つのCPTを有するので、単なる2つを有する時とは異なり、再命名テーブルを再構成するのに要求されるサイクルの数が減少することを分かる。

マイクロプロセッサ310は、デコーダー320、再命名器330、再命名テーブル336、リタイアテーブル338、ディスパッチャー340、スケジューラー(341、342、343)、物理的レジスターファイル(PRF)350、実行ユニット(351、352、353)、ブランチ実行ロジック357、及びROB360を含み、これは図1と同様の構成要素を参照して説明される。

ROBデータ362は、再構成再命名データ182と同様の再構成再命名データ382を含む。

また、マイクロプロセッサ310は、ROB360と静的関係を有する2つのCPT、即ち、CPT−0(370)及びCPT−1(371)を含む。

CPT−0(370)及びCPT−1(371)は、図2Bの静的関係(符号288−2)と同様の静的関係を有する。

CPT−0(370)及びCPT−1(371)は静的関係にしたがって各々チェックポイントされた再命名データ380、381を格納する。

命令語はパイプを通じてデコーダー320から受信され、実行ユニット(351、352、353)で実行される。

図3Bで、フラッグとして示す予測ミス(符号390)が感知される。

その結果、再命名テーブル336はフラッシュ(符号392)され、コメントによって示される。

図3Cで、コメント「再成」(符号393)によって示すように、再命名テーブル336は再構成される。

その結果、コメント「停止」(符号391)が示すようにパイプのフロントエンドで停止が発生する。

最初に、リタイアチェックポイントが矢印(符号339)にしたがってリタイアテーブル338からコピーされる。

再構成は、2つの他のソースから来るデータによって実行される。

チェックポイントされた再命名データ(380、381)は、適用可能である静的関係の観点から許諾された場合、矢印(符号375、376)にしたがってコピーされる。

そして、再命名データ382は矢印(符号365)にしたがってROB360をウォーキング(walking)することによってコピーされる。

マイクロプロセッサ310は、一般的に、図に示さなかったクロックを含む。

クロックは、クロックサイクルを定義するパルスを出力する。

クロックサイクルは、本発明の長所を評価する良い方法である。実施形態を以下に説明する。

クロックサイクル412は、シングルパルス(single pulse)で示すNサイクルのグループ415を含む。数字“N”は後で詳細に説明する。

図4では予測ミスを感知し、以後のペナルティー(penalties)を説明する。

延長された停止パルス491はコメント(符号391)による、パイプ(pipe)が停止された時間に対応する。

パルス491の持続は、予測ミスに対する時間ペナルティー及び以後のマイクロプロセッサの動作性能減少と関連する。

パルス491とサイクルのグループ415で、仮に“N”が大きければ、ペナルティーはさらに大きい。

パルス493Aとパルス493Bは、コメント(符号393)に対応して各々再構成の開始と終了を示す。

サイクル439は、矢印(符号339)の動作実行の際に、リタイアチェックポイントをコピーするためのものである。

サイクル475は、矢印(符号375)にしたがってCPTから同時にコピーするためのものである。

サイクル476は、矢印(符号376)にしたがって他の同時コピーに関するものである。

サイクルのグループ415と同様に、サイクル465は1つで図に示している。

但し、これは例示的なものであり、サイクルのグループ415とサイクル465とはN値を有することもあり得る。

矢印(符号339、375、376、365)は理解の便宜を助けるために図4で適切な位置で反復される。

しかし、具体的に、再命名サイクル436の一部は、毎度は包含されない。

いずれかが含まれ、いずれかが含まれないかに関する問題は予測ミスが感知され、以後の再命名テーブルがフラッシュされる時点で定義されるシナリオによる。具体的な動作のシナリオは図4を参照して説明する。

ROB再構成ウインドウは、リタイアポインターから開始し、フラッシュポインターが1つ先行するところで終了するROBエントリを有する。

ROB再構成ウインドウ内のROBエントリは、再命名テーブルに再格納される必要があると定義され、再格納は、1つ又はそれ以上のCPTからの同時のコピー動作又はROBをウォーキング(walking)する動作のいずれか1つによって実行される。

各場合において、ROBから再命名テーブルにコピーされる再構成再命名データの部分はROB再構成ウインドウ内に属する。

異なるシナリオ自体は、ROB再構成ウインドウが以前に言及されたROBチェックポイントウインドウの深さと関連して、どのようにして異なる大きさを有するのかを検証する。

また以下のシナリオの一側面は、CPTテーブルが同時に再命名テーブルにコピーされることが許諾されるか否か、又はROBをワーキング(walking)することによって同一の内容がコピーされるか否かを判断することに連関する。

シナリオの説明をするために、ROB360とCPT(370、371)とが図2Bで示したものと同様なものが使用されたと仮定する。

さらに、静的関係(符号288−2)と同様のROBチェックポイントウインドウとCPT(370、371)を示す波括弧によって示される静的関係が適用される。

CPT−0(370)はチェックポイントされた再命名データ580を格納し、CPT−1(371)はチェックポイントされた再命名データ581を格納する。

矢印で示したROB再構成ウインドウ563は、リタイアポインターが示すROBエントリ“15”で始めて、フラッシュポインターが示すROBエントリ“38”より1つ小さいROBエントリ“37”で終了する。

ROB再構成ウインドウ563内のROBデータ562は、CPT(370、371)からの同時コピー又は直接的にROB360をウォーキングすることによって再命名テーブル336に再格納される再構成再命名データ582を含む。

このように、チェックポイントされた再命名データ581は、図で線を引いて消されたように、要求されない。

さらに、ROBエントリ“38”で“47”までのコンテンツはフラッシュされ、したがってチェックポイントされた再命名データ580は、CPT−0(370)が全て再命名テーブル336にコピーされるので、再構成プロセスの一部として再命名テーブルにコピーされない。

このように、チェックポイントされた再命名データ580もやはり、図で線を引いて消されたように要求されない。

したがって、コメント(符号567)によって、すべてのROBエントリ“15”〜“37”内の再構成再命名データ582は矢印(符号565)にしたがって、即ち、ROB360をウォーキングすることによって再格納される。

言い換えれば、図5のCPTは、再構成のために使用されなく、したがって、本発明は図5のシナリオでは長所を提供しない。

図5のシナリオに対して図4を簡略的に参照すれば、再命名サイクル475と再命名サイクル476とは全て包含しなく、数字“N”は最大“m”であり、ここで、“m”はこのようなシナリオの下でROB360がウォーキングされることができる最も多い段階の数を示す。

停止パルス491の期間は本発明ではない状態では減少しない。このようなことは残るシナリオ例では適用されない。

CPT−0(370)はチェックポイントされた再命名データ部分680を格納し、CPT−1(371)はチェックポイントされた再命名データ部分681を格納する。

ROB360内のROB再構成ウインドウ663は“15”から“54”のROBエントリに掛かっている。

ROB再構成ウインドウ663内で、ROBデータ662は、再命名テーブル336に再格納される再構成再命名データの一部分(682A、682B)を含む。

再構成再命名データをROB360内の所定部分(682A、682B)に分割したことがROBチェックポイントの境界で発生したことにより理解できる。

実際に、“15”から“47”のROBエントリはチェックポイントされた再命名データ部分680にマッピングされ、“48”から“54”のROBエントリはチェックポイントされた再命名データ部分681にマッピングされる。

したがって、再構成再命名データ部分682Aは必要としないようになって、示したように図で線を引いたように消される。

しかし、チェックポイントされた再命名データ部分681は、図5でと同様の理由で使用されないので、図に線を引いて示したように消される。

コメント(符号667)によって、“48”から“54”のROBエントリ内の再構成再命名データ部分682BはROB360をウォーキング(walking)することによって矢印(符号665)にしたがって再格納される。

“N”は“m”より小さく、“0”より大きく、停止パルス491の持続期間は本発明によって減少される。

図6のシナリオでの再構成は、図5に比べてさらに多いデータをコピーことを要求するように見えるが、本発明の技術的思想によれば、より短い時間の所要ですむ。

CPT−0(370)はチェックポイントされた再命名データ部分780を格納し、CPT−1(371)はチェックポイントされた再命名データ部分781を格納する。

ROB再構成ウインドウ763は“80”のROBエントリから始めて、“95”のROBエントリから“0”のROBエントリを経て、“9”のROBエントリまで続ける。

ROBデータ部分762Aは再構成再命名データ部分782Aを含み、ROBデータ部分762Bは再構成再命名データ部分782Bを含む。

“80”から“95”のROBエントリはチェックポイントされた再命名データ部分781にマッピングされ、“0”から“9”のROBエントリはチェックポイントされた再命名データ部分780にマッピングされる。

したがって、再構成再命名データ部分782Aは必要がなくなって、図に線を引いて示したように消される。

しかし、チェックポイントされた再命名データ部分780は、図5でと同様の理由で使用できなくなり、コメント(符号767)によって、再構成再命名データ782Bが矢印(符号765)にしたがってROB360をウォーキング(walking)して再格納される。

“N”は“0”より大きく、“m”より小さく、停止パルス491の持続期間は本発明によって最少化される。

CPT−0(370)はチェックポイントされた再命名データ部分880を格納し、CPT−1(371)はチェックポイントされた再命名データ部分881を格納する。

ROB再構成ウインドウ863はROBエントリ“80”で始めて、ROBエントリ“95”でROBエントリ“0”を含んで、ROBエントリ“74”まで続けることを図に示す。

ROBエントリ“80”〜“95”及び“48”〜“74”はチェックポイントされた再命名データ部分881にマッピングされ、ROBエントリ“0”〜“47”はチェックポイントされた再命名データ部分880にマッピングされる。

したがって、再構成再命名データ部分(882B)は、図で線を引いて消されたように必要としない。

しかし、チェックポイントされた再命名データ部分881は使用可能でない。

したがって、コメント(符号867)によって、再構成再命名データ部分882A及び882Cは矢印(符号865)にしたがって、即ちROB360をウォーキングすることによって再格納される。

“N”は“0”よりは大きく、“m”よりは小さく、本発明によって停止パルス491は減少される。

CPT−0(370)はチェックポイントされた再命名データ部分980を格納し、CPT−1(371)はチェックポイントされた再命名データ部分981を格納する。

ROB再構成ウインドウ963はROBエントリ“0”〜“48”に掛かっている。

ROBデータ962は再構成再命名データ982を含む。

言い換えれば、ROBエントリ“0”〜“47”はROBチェックポイントウインドウの下の部分に正確に包含される。これは特別な場合であり、統計的に小さい頻度で発生する。

したがって、再構成再命名データ部分982は図で線を引いて消されたように必要としない。

さらに、このシナリオでコメント(符号967)によってROB360のウォーキングは無く、何らかの再構成再命名データもROB360から再命名テーブル336にコピーされない。従って、チェックポイントされた再命名データ部分981もやはり線を引いて消されたように必要としない。

“N”は“0”になり、パルス415、465のグループはない。本発明によって停止パルス491は減少される。

システム1000は、PDA(personal digital assistant)、ラップトップコンピュータ、モバイルコンピュータ、ウェブタブレット、無線フォン、携帯電話機、デジタル音楽再生器、有線又は無線電気装置、又は少なくとも前記の機器の中で2つ以上を含む複合電子装置内で使用され得る。

コントローラ1010は、例えば、本発明の実施形態にしたがって製造された少なくとも1つのマイクロプロセッサ、デジタル信号プロセッサ、マイクロコントローラのようなものを包含する。

システム(或いは電子機器)1000は、通信ネットワークを通じてデータを伝送するか、或いは受信するユーザーインターフェイス1040を使用する。

伝送動作は、例えば、ケーブル、USBインターフェイスのような有線を経由することがあり得る。他の例として、通信ネットワークは無線であり、インターフェイス1040は無線であり、例えば、アンテナ、無線送受信機のようなものであり得る。

フローチャート1100の動作方法は、上述した実施形態、マイクロプロセッサ、電子装置によって実行される。

次に、S1120段階にて、再命名データが「micro−ops」によって発生する。

次に、S1130段階にて、再命名データを再命名テーブルに格納する。

次に、S1150段階にて、「micro−ops」から発生されたROBデータをROBに格納する。

ROBデータは必要である場合、結局のところ再命名テーブルを再構成するために使用される再構成再命名データを包含することができる。ROBはCPTと静的関係を維持する。

次に、S1160段階にて、「micro−ops」が実行される。

言い換えれば、再命名データは再命名テーブルからフラッシュされる。

仮に「いいえ」であれば、S1110段階にもどる。

一実施形態において、再命名テーブルは上述したように予測ミスを感知することに応答してフラッシュされる。

仮に再命名テーブルがフラッシュされたら(「はい」であれば)、以後のS1180段階にしたがって、再命名データを再命名テーブルに再格納する。即ち、再命名テーブルが再構成される。

S1180段階で、ROBエントリのROB再構成ウインドウは再命名テーブルがフラッシュされた時、定義される。

ROB再構成ウインドウ内のこのようなROBエントリの再構成再命名データは、S1182段階によって、又はS1184段階によって再命名テーブルに再格納される。

一実施形態において、再命名データのチェックポイントされたバーションは1つのクロックサイクル内でコピーされる。

望ましくは、これはS1182段階によってカバーされないで残ることに対して実行され、ROBをウォーキング(walking)することによって実行される。

さらに、他の実施形態で、新しい段階が追加されたり、各段階が修正されるか、或いは削除されることもあり得る。

120、320 デコーダー

130、330 再命名器(renamer)

136、336 再命名テーブル

138、338 リタイアテーブル

140、340 ディスパッチャー

141〜143、341〜343 スケジューラー(A〜C)

150、350 物理的レジスターファイル(PRF)

151〜153、351〜353 実行ユニット(A〜C)

157、357 ブランチ実行ロジック

160、360 リオーダーバッファ(ROB)

162、362 ROBデータ

170、370、371 チェックポイントテーブル(CPT)

180 再命名データのチェックポイントされたバーション

182、382 再構成再命名データ

380、381 チェックポイントされた再命名データ

Claims (16)

- 再命名データ(rename data)を格納する再命名テーブルと、

ディスパッチャー(dispatcher)と、

前記ディスパッチャーから受信した再命名データを格納するチェックポイントテーブル(Check Point Table:CPT)と、

リオーダーバッファ(Re−Order Buffer:ROB)エントリを含むリオーダーバッファとを有し、

前記再命名テーブルがフラッシュ(flush)されれば、前記再命名テーブルは、前記チェックポイントテーブルに格納された前記再命名データを利用して再構成(rebuild)され、

前記リオーダーバッファエントリのグループは、リオーダーバッファチェックポイントウインドウとして定義され、

前記リオーダーバッファチェックポイントウインドウと、前記チェックポイントテーブルとの間のマッピングは、固定された静的関係(static relationship)に従うものであり、

前記再命名テーブルは、静的関係の側面で許諾される場合のみ、前記チェックポイントテーブルに格納された前記再命名データを利用して再構成されることを特徴とするマイクロプロセッサ。 - 予測ミス(mis−prediction)を感知するためのブランチ実行ロジック(branch execution logic)をさらに有し、

前記予測ミスが感知されたことに応答して、前記再命名テーブルはフラッシュされることを特徴とする請求項1に記載のマイクロプロセッサ。 - 再命名データを生成する再命名器(renamer)をさらに有し、

前記再命名テーブルは、前記再命名器から前記再命名データを受信することを特徴とする請求項1に記載のマイクロプロセッサ。 - クロックサイクルを定義するパルスを出力するクロックをさらに有し、

前記再命名テーブルの再構成において、1つの前記チェックポイントテーブルから前記再命名テーブルへの再命名データのコピーは、前記クロックサイクルの中の1つのサイクル内で行われるものであることを特徴とする請求項1に記載のマイクロプロセッサ。 - 命令語をマイクロオペレーション(micro−ops)にデコーディングするデコーダーと、

前記マイクロオペレーションを実行する実行ユニットと、

前記マイクロオペレーションにしたがって再命名データを生成する再命名器と、

再命名テーブルと、

前記再命名データのチェックポイントされたバーション(check−pointed version)を格納するチェックポイントテーブル(CPT)と、

前記マイクロオペレーションから生成されたリオーダーバッファ(Re−order Buffer:ROB)データを格納するリオーダーバッファエントリを有するリオーダーバッファとを有し、

前記再命名テーブルは、前記再命名データを格納するものであり、かつ、所定の条件が成立した場合には、前記再命名データが前記再命名テーブルからフラッシュされるものであり、

前記リオーダーバッファデータは、再構成再命名データを含み、

前記リオーダーバッファエントリのグループは、リオーダーバッファチェックポイントウインドウとして定義され、

前記リオーダーバッファチェックポイントウインドウと、前記チェックポイントテーブルの間のマッピングは、固定された静的関係に従うものであり、

前記静的関係の側面で許諾される場合のみ前記再命名データの前記チェックポイントされたバーションが前記チェックポイントテーブルから前記再命名テーブルにコピーされ、さらに、前記再命名テーブルにコピーされるべき再命名データのうち、残余のものが存在する場合には、前記再構成再命名データの少なくとも一部分が前記リオーダーバッファから前記再命名テーブルにコピーされることによって、

前記再命名テーブルに格納された再命名データが前記再命名テーブルからフラッシュされた場合、再命名データを前記再命名テーブルに再格納することができることを特徴とするマイクロプロセッサ。 - 付加的なチェックポイントテーブルをさらに有し、

前記リオーダーバッファエントリは、前記チェックポイントテーブル又は前記付加的なチェックポイントテーブルにマッピングされることを特徴とする請求項5に記載のマイクロプロセッサ。 - 再命名データが前記再命名テーブルからフラッシュされる場合、リオーダーバッファエントリのリオーダーバッファ再構成ウインドウが定義され、

前記リオーダーバッファから前記再命名テーブルにコピーされる前記再構成再命名データの部分は、前記リオーダーバッファ再構成ウインドウ内に存在することを特徴とする請求項5に記載のマイクロプロセッサ。 - マイクロオペレーション(micro−ops)にしたがって再命名データを生成する再命名器と、

前記再命名データを格納する再命名テーブルと、

前記マイクロオペレーションから生成され再構成再命名データを格納するリオーダーバッファデータを格納するリオーダーバッファ(Re−Order Buffer:ROB)と、

前記再命名データのチェックポイントされたバーションを格納する2つ以上のチェックポイントテーブル(Check Point Table:CPT)とを有し、

前記リオーダーバッファと前記2つ以上のチェックポイントテーブルとの間には、静的関係(static relationship)を有し、前記2つ以上のチェックポイントテーブルは、前記静的関係にしたがって各々チェックポイントされた再命名データを格納し、

前記再命名テーブルに格納された再命名データが、前記再命名デーブルからフラッシュされる場合に、

必要であれば、前記リオーダーバッファから前記再命名テーブルにコピーされる再構成再命名データと、前記静的関係の観点から許容されるのであれば、前記2つ以上のチェックポイントテーブルの少なくともいずれかから前記再命名テーブルにコピーされる再命名データの前記チェックポイントされたバージョンの間に重複がないようにしつつ、前記コピーを行うことにより、再命名データを前記再命名テーブルに格納されることを特徴とするマイクロプロセッサ。 - 前記マイクロオペレーションを実行ユニットに発送する(dispatching)ディスパッチャーをさらに有し、

前記チェックポイントテーブルは、前記ディスパッチャーから前記再命名データの前記チェックポイントされたバーションを受信することを特徴とする請求項5又は8記載のマイクロプロセッサ。 - 前記マイクロオペレーションの実行において、予測ミスを感知するためのブランチ実行ロジックをさらに含み、

前記予測ミスが感知されたことに応答して、前記再命名データは、前記再命名テーブルからフラッシュされることを特徴とする請求項5又は8に記載のマイクロプロセッサ。 - クロックサイクルを定義するパルスを出力するクロックをさらに含み、

前記再命名データの前記チェックポイントされたバーションが、前記クロックサイクル中の1つのサイクル内で前記チェックポイントテーブルから前記再命名テーブルにコピーされることを特徴とする請求項5又は8記載のマイクロプロセッサ。 - バス(Bus)と、

前記バスに接続されたインターフェイスであって、通信ネットワークにデータを伝送し、前記通信ネットワークからデータを受信するように構成された前記インターフェイスと、

前記バスに接続された入出力装置と、

前記バスに接続され、前記入出力装置を通じてアクセス可能であるユーザーデータ又は命令語を格納するよう構成されたメモリと、

前記バスに接続され、前記命令語を利用するよう構成されたコントローラとを有し、

前記コントローラは、少なくとも1つのマイクロプロセッサを含み、

前記マイクロプロセッサは、再命名データを格納する再命名テーブルと、

ディスパッチャーと、

チェックポイントテーブル(Check Point Table:CPT)と、

リオーダーバッファ(Re−Order Buffer:ROB)エントリを含むリオーダーバッファとを含み、

前記リオーダーバッファエントリのグループはリオーダーバッファチェックポイントウインドウ(checkpoint window)として定義され、

前記リオーダーバッファチェックポイントウインドウと、前記チェックポイントテーブルの間のマッピングは、固定された静的関係に従うものであり、

前記再命名テーブルがフラッシュされれば、前記再命名テーブルは、前記チェックポイントテーブルに格納された前記再命名データを利用して再構成され、

前記再命名テーブルは、静的関係の側面で許諾される場合のみ、前記チェックポイントテーブルに格納された前記再命名データを利用して再構成されることを特徴とする電子機器。 - 前記インターフェイスは、無線であり、前記通信ネットワークも無線であることを特徴とする請求項12に記載の電子機器。

- 予測ミスを感知するためのブランチ実行ロジックをさらに有し、

前記予測ミスが感知されたことに応答して前記再命名テーブルは、フラッシュされることを特徴とする請求項12に記載の電子機器。 - 再命名データを生成する再命名器をさらに有し、

前記再命名テーブルは、前記再命名器から前記再命名データを受信することを特徴とする請求項12に記載の電子機器。 - クロックサイクルを定義するパルスを出力するクロックをさらに有し、

前記再命名テーブルの再構成において、1つの前記チェックポイントテーブルから前記再命名テーブルへの再命名データのコピーは、前記クロックサイクルの中の1つのサイクル内で行われるものであることを特徴とする請求項12に記載の電子機器。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/831,522 | 2013-03-14 | ||

| US13/831,522 US9448800B2 (en) | 2013-03-14 | 2013-03-14 | Reorder-buffer-based static checkpointing for rename table rebuilding |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014179098A JP2014179098A (ja) | 2014-09-25 |

| JP6533643B2 true JP6533643B2 (ja) | 2019-06-19 |

Family

ID=51419120

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014051308A Expired - Fee Related JP6533643B2 (ja) | 2013-03-14 | 2014-03-14 | マイクロプロセッサ及びこれを使用した電子機器 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US9448799B2 (ja) |

| JP (1) | JP6533643B2 (ja) |

| KR (1) | KR102021957B1 (ja) |

| CN (1) | CN104050132B (ja) |

| DE (1) | DE102014103283A1 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20030032598A (ko) * | 2001-10-16 | 2003-04-26 | 손규석 | 수유 보조기 |

| US9448799B2 (en) * | 2013-03-14 | 2016-09-20 | Samsung Electronics Co., Ltd. | Reorder-buffer-based dynamic checkpointing for rename table rebuilding |

| US10877768B1 (en) * | 2019-09-06 | 2020-12-29 | Microsoft Technology Licensing, Llc | Minimizing traversal of a processor reorder buffer (ROB) for register rename map table (RMT) state recovery for interrupted instruction recovery in a processor |

| US11061677B1 (en) * | 2020-05-29 | 2021-07-13 | Microsoft Technology Licensing, Llc | Recovering register mapping state of a flushed instruction employing a snapshot of another register mapping state and traversing reorder buffer (ROB) entries in a processor |

| US11113068B1 (en) * | 2020-08-06 | 2021-09-07 | Microsoft Technology Licensing, Llc | Performing flush recovery using parallel walks of sliced reorder buffers (SROBs) |

Family Cites Families (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5694564A (en) * | 1993-01-04 | 1997-12-02 | Motorola, Inc. | Data processing system a method for performing register renaming having back-up capability |

| US5630149A (en) * | 1993-10-18 | 1997-05-13 | Cyrix Corporation | Pipelined processor with register renaming hardware to accommodate multiple size registers |

| DE69408769T2 (de) * | 1993-10-18 | 1998-07-09 | Cyrix Corp | Fliessbandsteuerung und Registerübersetzung in Mikroprozessor |

| EP0815507B1 (en) * | 1995-02-14 | 2013-06-12 | Fujitsu Limited | Structure and method for high-performance speculative execution processor providing special features |

| US5822574A (en) * | 1995-04-12 | 1998-10-13 | Advanced Micro Devices, Inc. | Functional unit with a pointer for mispredicted resolution, and a superscalar microprocessor employing the same |

| US5809268A (en) * | 1995-06-29 | 1998-09-15 | International Business Machines Corporation | Method and system for tracking resource allocation within a processor |

| DE69814415T2 (de) * | 1997-01-29 | 2004-03-11 | Advanced Micro Devices, Inc., Sunnyvale | Zeilenorientierter wiedereinordnungsspeicher für superskalaren mikroprozessor |

| US6026477A (en) * | 1997-12-31 | 2000-02-15 | Intel Corporation | Branch recovery mechanism to reduce processor front end stall time by providing path information for both correct and incorrect instructions mixed in the instruction pool |

| US6742112B1 (en) | 1999-12-29 | 2004-05-25 | Intel Corporation | Lookahead register value tracking |

| US6629233B1 (en) * | 2000-02-17 | 2003-09-30 | International Business Machines Corporation | Secondary reorder buffer microprocessor |

| US6349361B1 (en) | 2000-03-31 | 2002-02-19 | International Business Machines Corporation | Methods and apparatus for reordering and renaming memory references in a multiprocessor computer system |

| US7969451B2 (en) * | 2003-03-27 | 2011-06-28 | International Business Machines Corporation | Method and apparatus for dynamically sizing color tables |

| US7711932B2 (en) | 2003-12-02 | 2010-05-04 | Intel Corporation | Scalable rename map table recovery |

| US20060149931A1 (en) | 2004-12-28 | 2006-07-06 | Akkary Haitham | Runahead execution in a central processing unit |

| US7526583B2 (en) | 2005-06-23 | 2009-04-28 | International Business Machines Corporation | Method and apparatus to launch write queue read data in a microprocessor recovery unit |

| US20070043934A1 (en) * | 2005-08-22 | 2007-02-22 | Intel Corporation | Early misprediction recovery through periodic checkpoints |

| US7747841B2 (en) * | 2005-09-26 | 2010-06-29 | Cornell Research Foundation, Inc. | Method and apparatus for early load retirement in a processor system |

| US7809926B2 (en) | 2006-11-03 | 2010-10-05 | Cornell Research Foundation, Inc. | Systems and methods for reconfiguring on-chip multiprocessors |

| US7613908B2 (en) | 2007-02-23 | 2009-11-03 | Intel Corporation | Selective hardware lock disabling |

| US20190065160A1 (en) * | 2007-11-07 | 2019-02-28 | Haitham Akkary | Pre-post retire hybrid hardware lock elision (hle) scheme |

| US8320372B2 (en) | 2008-06-23 | 2012-11-27 | Alcatel Lucent | Processing of packet fragments |

| US20090327661A1 (en) | 2008-06-30 | 2009-12-31 | Zeev Sperber | Mechanisms to handle free physical register identifiers for smt out-of-order processors |

| US9672019B2 (en) | 2008-11-24 | 2017-06-06 | Intel Corporation | Systems, apparatuses, and methods for a hardware and software system to automatically decompose a program to multiple parallel threads |

| US8301849B2 (en) | 2009-12-23 | 2012-10-30 | Intel Corporation | Transactional memory in out-of-order processors with XABORT having immediate argument |

| US9052890B2 (en) * | 2010-09-25 | 2015-06-09 | Intel Corporation | Execute at commit state update instructions, apparatus, methods, and systems |

| US8549504B2 (en) | 2010-09-25 | 2013-10-01 | Intel Corporation | Apparatus, method, and system for providing a decision mechanism for conditional commits in an atomic region |

| US20120079245A1 (en) | 2010-09-25 | 2012-03-29 | Cheng Wang | Dynamic optimization for conditional commit |

| WO2013101128A1 (en) * | 2011-12-29 | 2013-07-04 | Intel Corporation | Using a single table to store speculative results and architectural results |

| US20130173885A1 (en) * | 2011-12-30 | 2013-07-04 | Advanced Micro Devices, Inc. | Processor and Methods of Adjusting a Branch Misprediction Recovery Mode |

| US9672044B2 (en) * | 2012-08-01 | 2017-06-06 | Nxp Usa, Inc. | Space efficient checkpoint facility and technique for processor with integrally indexed register mapping and free-list arrays |

| US9448799B2 (en) * | 2013-03-14 | 2016-09-20 | Samsung Electronics Co., Ltd. | Reorder-buffer-based dynamic checkpointing for rename table rebuilding |

| KR102010317B1 (ko) * | 2013-03-14 | 2019-08-13 | 삼성전자주식회사 | 재명명 테이블 재구성을 위한 리오더-버퍼를 기초로 하는 동적 체크포인팅 |

-

2013

- 2013-03-14 US US13/831,488 patent/US9448799B2/en active Active

- 2013-03-14 US US13/831,522 patent/US9448800B2/en not_active Expired - Fee Related

- 2013-12-20 KR KR1020130160346A patent/KR102021957B1/ko not_active Expired - Fee Related

-

2014

- 2014-03-12 DE DE102014103283.7A patent/DE102014103283A1/de not_active Withdrawn

- 2014-03-14 JP JP2014051308A patent/JP6533643B2/ja not_active Expired - Fee Related

- 2014-03-14 CN CN201410097564.1A patent/CN104050132B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US9448800B2 (en) | 2016-09-20 |

| KR102021957B1 (ko) | 2019-09-17 |

| CN104050132B (zh) | 2018-10-19 |

| JP2014179098A (ja) | 2014-09-25 |

| KR20140113306A (ko) | 2014-09-24 |

| DE102014103283A1 (de) | 2014-09-18 |

| US20140281414A1 (en) | 2014-09-18 |

| US9448799B2 (en) | 2016-09-20 |

| CN104050132A (zh) | 2014-09-17 |

| US20140281393A1 (en) | 2014-09-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6533643B2 (ja) | マイクロプロセッサ及びこれを使用した電子機器 | |

| CN109358948B (zh) | 用于支持推测的访客返回地址栈仿真的方法和装置 | |

| TWI416407B (zh) | 執行複數快速條件分支指令的方法以及相關之微處理器以及電腦程式產品 | |

| US9298497B2 (en) | Computer processor providing exception handling with reduced state storage | |

| TWI470547B (zh) | 非循序執行微處理器及其操作方法 | |

| JP5904993B2 (ja) | マルチスレッド・コードをデバッグする方法、システム、及びコンピュータ・プログラム | |

| CN108196884B (zh) | 利用生成重命名的计算机信息处理器 | |

| CN105005463A (zh) | 具有世代重命名的计算机处理器 | |

| US6971000B1 (en) | Use of software hint for branch prediction in the absence of hint bit in the branch instruction | |

| CN106406822A (zh) | 具有改进的别名队列和存储冲突检测的处理器 | |

| US8037366B2 (en) | Issuing instructions in-order in an out-of-order processor using false dependencies | |

| KR20190038989A (ko) | 나누기와 곱하기-빼기 연산들을 병합하기 위한 시스템 및 방법 | |

| US9594564B2 (en) | Arithmetic processing device and control method of arithmetic processing device | |

| JP7189935B2 (ja) | 同時の分岐アドレスの予測およびレジスタの内容の更新 | |

| US20180253303A1 (en) | String sequence operations with arbitrary terminators | |

| US20150227371A1 (en) | Processors with Support for Compact Branch Instructions & Methods | |

| CN102163139B (zh) | 微处理器融合载入算术/逻辑运算及跳跃宏指令 | |

| KR102010317B1 (ko) | 재명명 테이블 재구성을 위한 리오더-버퍼를 기초로 하는 동적 체크포인팅 | |

| US5913050A (en) | Method and apparatus for providing address-size backward compatibility in a processor using segmented memory | |

| US20130019085A1 (en) | Efficient Recombining for Dual Path Execution | |

| Celio et al. | Riscv-boom documentation | |

| Mutlu | 18-447: Computer Architecture, Lecture 13: Out-of-Order Execution | |

| Revucky | Optimizing Indirect Branch Prediction Accuracy in Virtual Machine Interpreters |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161227 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180313 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180612 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180911 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181205 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190514 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190527 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6533643 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |