JP6516610B2 - メモリ装置、ホスト装置、及びメモリシステム - Google Patents

メモリ装置、ホスト装置、及びメモリシステム Download PDFInfo

- Publication number

- JP6516610B2 JP6516610B2 JP2015145324A JP2015145324A JP6516610B2 JP 6516610 B2 JP6516610 B2 JP 6516610B2 JP 2015145324 A JP2015145324 A JP 2015145324A JP 2015145324 A JP2015145324 A JP 2015145324A JP 6516610 B2 JP6516610 B2 JP 6516610B2

- Authority

- JP

- Japan

- Prior art keywords

- generation circuit

- data generation

- dummy

- cryptographic module

- stream data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000001514 detection method Methods 0.000 claims description 12

- 238000000034 method Methods 0.000 description 12

- 230000004048 modification Effects 0.000 description 11

- 238000012986 modification Methods 0.000 description 11

- 238000004458 analytical method Methods 0.000 description 10

- 230000007704 transition Effects 0.000 description 5

- 238000010586 diagram Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 230000001052 transient effect Effects 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

Images

Description

また、第1の態様に係るメモリ装置によれば、制御回路は、第1の一時データ生成回路のみが通常動作を実行する期間においては第2のストリームデータ生成回路にダミー動作を実行させ、第1のストリームデータ生成回路のみが通常動作を実行する期間においては第2の一時データ生成回路にダミー動作を実行させる。これにより、メモリ装置全体の消費電力を均一化できるため、DPA攻撃による消費電力特性の解析を困難化することが可能となる。

また、第5の態様に係るホスト装置によれば、制御回路は、第1の一時データ生成回路のみが通常動作を実行する期間においては第2のストリームデータ生成回路にダミー動作を実行させ、第1のストリームデータ生成回路のみが通常動作を実行する期間においては第2の一時データ生成回路にダミー動作を実行させる。これにより、ホスト装置全体の消費電力を均一化できるため、DPA攻撃による消費電力特性の解析を困難化することが可能となる。

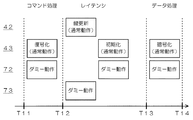

上記実施の形態では、DPA対策をメモリ装置3に実装する例について説明したが、DPA対策をホスト装置2に実装しても良い。

上記実施の形態では、DPA制御情報D11に基づいてDPA対策処理の実行の要否が判定されたが、ホスト装置2からメモリ装置3への不正アクセスがあったことを条件として、DPA対策処理を実行しても良い。

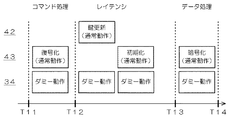

図7は、メモリ装置3の暗号ブロック21の構成を示す図である。図7に示すように暗号ブロック21は、制御回路31、暗号モジュール32〜34、及び演算回路35を有している。暗号モジュール34は、セッション鍵生成回路42(第1の一時データ生成回路)と同様のセッション鍵生成回路72(第2の一時データ生成回路)と、ストリームデータ生成回路43(第1の暗号処理回路)と同様のストリームデータ生成回路73(第2の暗号処理回路)とを有している。

図9は、セッション鍵生成回路42、ストリームデータ生成回路43、及び暗号モジュール34の処理内容を示すタイミングチャートである。

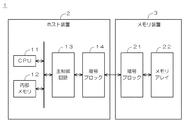

2 ホスト装置

3 メモリ装置

14,21 暗号ブロック

31,51 制御回路

32〜34,52〜54 暗号モジュール

36 不正アクセス検出回路

42,62,72 セッション鍵生成回路

43,63,73 ストリームデータ生成回路

Claims (8)

- ホスト装置に接続されるメモリ装置であって、

通常動作として入力データに基づいて第1の一時データを生成する第1の一時データ生成回路を有する、第1の暗号モジュールと、

通常動作として前記第1の一時データ生成回路によって生成された第1の一時データに基づいて第1のストリームデータを生成する第1のストリームデータ生成回路を有する、第2の暗号モジュールと、

ダミー動作としてダミーの入力データに基づいて第2の一時データを生成する第2の一時データ生成回路と、ダミー動作として前記第2の一時データ生成回路によって生成された第2の一時データに基づいて第2のストリームデータを生成する第2のストリームデータ生成回路とを有する、第3の暗号モジュールと、

前記第3の暗号モジュールの動作を制御する制御回路と、

を備え、

前記制御回路は、

前記第1の一時データ生成回路及び前記第1のストリームデータ生成回路のうち前記第1の一時データ生成回路のみが通常動作を実行する期間において、前記第2のストリームデータ生成回路にダミー動作を実行させ、

前記第1の一時データ生成回路及び前記第1のストリームデータ生成回路のうち前記第1のストリームデータ生成回路のみが通常動作を実行する期間において、前記第2の一時データ生成回路にダミー動作を実行させる、メモリ装置。 - 前記制御回路はさらに、前記第2の暗号モジュールが通常動作を実行し前記第1の暗号モジュールが通常動作を実行しない期間において、前記第1の暗号モジュールにダミー動作を実行させる、請求項1に記載のメモリ装置。

- 前記制御回路はさらに、前記第1の暗号モジュール及び前記第2の暗号モジュールの双方が同時に通常動作を実行する期間において、前記第3の暗号モジュールにダミー動作を実行させる、請求項2に記載のメモリ装置。

- 前記ホスト装置からの不正アクセスを検出する不正アクセス検出回路をさらに備え、

前記制御回路は、前記不正アクセス検出回路が不正アクセスを検出した場合に、前記第3の暗号モジュールにダミー動作を実行させる、請求項1〜3のいずれか一つに記載のメモリ装置。 - メモリ装置が接続されるホスト装置であって、

通常動作として入力データに基づいて第1の一時データを生成する第1の一時データ生成回路を有する、第1の暗号モジュールと、

通常動作として前記第1の一時データ生成回路によって生成された第1の一時データに基づいて第1のストリームデータを生成する第1のストリームデータ生成回路を有する、第2の暗号モジュールと、

ダミー動作としてダミーの入力データに基づいて第2の一時データを生成する第2の一時データ生成回路と、ダミー動作として前記第2の一時データ生成回路によって生成された第2の一時データに基づいて第2のストリームデータを生成する第2のストリームデータ生成回路とを有する、第3の暗号モジュールと、

前記第3の暗号モジュールの動作を制御する制御回路と、

を備え、

前記制御回路は、

前記第1の一時データ生成回路及び前記第1のストリームデータ生成回路のうち前記第1の一時データ生成回路のみが通常動作を実行する期間において、前記第2のストリームデータ生成回路にダミー動作を実行させ、

前記第1の一時データ生成回路及び前記第1のストリームデータ生成回路のうち前記第1のストリームデータ生成回路のみが通常動作を実行する期間において、前記第2の一時データ生成回路にダミー動作を実行させる、ホスト装置。 - 前記制御回路はさらに、前記第2の暗号モジュールが通常動作を実行し前記第1の暗号モジュールが通常動作を実行しない期間において、前記第1の暗号モジュールにダミー動作を実行させる、請求項5に記載のホスト装置。

- 前記制御回路はさらに、前記第1の暗号モジュール及び前記第2の暗号モジュールの双方が同時に通常動作を実行する期間において、前記第3の暗号モジュールにダミー動作を実行させる、請求項6に記載のホスト装置。

- 請求項1〜4のいずれか一つに記載のメモリ装置と、

請求項5〜7のいずれか一つに記載のホスト装置と、

を備える、メモリシステム。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015145324A JP6516610B2 (ja) | 2015-07-22 | 2015-07-22 | メモリ装置、ホスト装置、及びメモリシステム |

| US15/213,918 US10615959B2 (en) | 2015-07-22 | 2016-07-19 | Memory device, host device, and memory system |

| US16/799,836 US11115181B2 (en) | 2015-07-22 | 2020-02-25 | Memory device, host device, and memory system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015145324A JP6516610B2 (ja) | 2015-07-22 | 2015-07-22 | メモリ装置、ホスト装置、及びメモリシステム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017028506A JP2017028506A (ja) | 2017-02-02 |

| JP6516610B2 true JP6516610B2 (ja) | 2019-05-22 |

Family

ID=57946197

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015145324A Active JP6516610B2 (ja) | 2015-07-22 | 2015-07-22 | メモリ装置、ホスト装置、及びメモリシステム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6516610B2 (ja) |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE10061998A1 (de) * | 2000-12-13 | 2002-07-18 | Infineon Technologies Ag | Kryptographieprozessor |

| JP2003018143A (ja) * | 2001-06-28 | 2003-01-17 | Mitsubishi Electric Corp | 情報処理装置 |

| JP2007195132A (ja) * | 2005-12-20 | 2007-08-02 | Sony Corp | 暗号処理装置 |

| JP2013143653A (ja) * | 2012-01-10 | 2013-07-22 | Canon Inc | 情報処理装置、情報処理方法 |

| JP6246516B2 (ja) * | 2013-07-24 | 2017-12-13 | 株式会社メガチップス | 情報処理システム |

| US9735953B2 (en) * | 2015-03-06 | 2017-08-15 | Qualcomm Incorporated | Side channel analysis resistant architecture |

-

2015

- 2015-07-22 JP JP2015145324A patent/JP6516610B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2017028506A (ja) | 2017-02-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11115181B2 (en) | Memory device, host device, and memory system | |

| US11251935B2 (en) | Multiplicative blinding for cryptographic operations | |

| Standaert | Introduction to side-channel attacks | |

| CN105940439B (zh) | 使用排列应对对密码算法的旁通道攻击的对策 | |

| CN113711194B (zh) | 基于密钥更新的高效侧信道攻击抵抗存储器加密器 | |

| US8804949B2 (en) | Method for protecting IC cards against power analysis attacks | |

| TW201701186A (zh) | 實體不可複製功能輔助之記憶體加密裝置技術 | |

| Unterluggauer et al. | Exploiting the physical disparity: Side-channel attacks on memory encryption | |

| WO2016190924A2 (en) | Side channel analysis resistant architecture | |

| JP6533553B2 (ja) | 暗号化/復号装置及びその電力解析保護方法 | |

| US10530567B2 (en) | Encryption device and memory device | |

| WO2008013083A1 (en) | Pseudo random number generator, stream encrypting device, and program | |

| Mondal et al. | A practical key-recovery attack on LWE-based key-encapsulation mechanism schemes using Rowhammer | |

| CN104484615B (zh) | 适用于可重构阵列架构的基于空间随机化抗故障攻击方法 | |

| CN113518988B (zh) | 嵌入式中央处理单元上的抗侧通道攻击存储器访问 | |

| JP2004310752A (ja) | データ処理装置における誤り検出 | |

| JP6516610B2 (ja) | メモリ装置、ホスト装置、及びメモリシステム | |

| US20240413986A1 (en) | Ratchet-based key management | |

| JP6473874B2 (ja) | メモリ装置、ホスト装置、及びメモリシステム | |

| Ege et al. | Practical improvements to statistical ineffective fault attacks | |

| JP2016025532A (ja) | 通信システム、通信装置、及び通信方法 | |

| US12273446B2 (en) | Simplified masking for signed cryptography operations | |

| Cao et al. | Practical lattice-based fault attack and countermeasure on sm2 signature algorithm | |

| JP2005204128A (ja) | 個別鍵生成装置及びプログラム | |

| Tsai et al. | Implementation and Analysis of Using Autoencoder to Suppress Noise Interference on Side-Channel Attacks |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170622 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180731 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180824 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181018 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190116 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20190116 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190416 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6516610 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |