JP6418696B2 - 命令セットシミュレータおよびそのシミュレータ生成方法 - Google Patents

命令セットシミュレータおよびそのシミュレータ生成方法 Download PDFInfo

- Publication number

- JP6418696B2 JP6418696B2 JP2015145452A JP2015145452A JP6418696B2 JP 6418696 B2 JP6418696 B2 JP 6418696B2 JP 2015145452 A JP2015145452 A JP 2015145452A JP 2015145452 A JP2015145452 A JP 2015145452A JP 6418696 B2 JP6418696 B2 JP 6418696B2

- Authority

- JP

- Japan

- Prior art keywords

- instruction

- subroutine

- program

- address

- machine language

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F8/00—Arrangements for software engineering

- G06F8/40—Transformation of program code

- G06F8/53—Decompilation; Disassembly

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F8/00—Arrangements for software engineering

- G06F8/30—Creation or generation of source code

- G06F8/31—Programming languages or programming paradigms

Description

逆コンパイラとは、コンピュータが直接実行する実行バイナリ(機械語)からプログラマ等が作成するプログラムソースコードに変換する技術である。つまり、逆コンパイラとは、プログラムソースコードから実行バイナリに変換するコンパイラの逆変換を行うものである。

翻訳(Interpreter)方式(非特許文献3):実行バイナリから機械語命令を一つずつデコード(解釈)しながらCPU動作を模擬する。デコード処理がオーバーヘッドとなりシミュレーション速度が遅い。

第1に、データ型の復元が困難である。つまり、実行バイナリから元のソースコードのデータ型を推定することが技術的に非常に難しい。

ただし、「手動編集の必要性」を排除または削減する効果についての言及は特になく、逆コンパイラの完全性に関する効果は限定的であると考えられる。

通常は、静的コンパイル方式が実行バイナリすべてをまとめてデコードすることから、最も高速なシミュレーションが可能とされている。しかし、機械語命令のデコード結果をCソースコードに変換する方式の場合(非特許文献4、8、9)、元のプログラムを直接ホストCPUで実行する(ネイティブ実行)と比べ、14倍〜54倍のシミュレーション時間がかかるというデータが非特許文献8で報告されている。

そのため、実際の使用に供されるのは、機械語命令のデコード結果をCソースコードに変換する方式(非特許文献4、8、9)のみである。

また、非特許文献4、8、9の方式は、後記するように、変換したCソースコードの解析が困難であるという問題がある。そのため、ウイルスの発見、解読、解析が困難である。

図54の4行目の「register UL * S = M, *F = H, A = 0, P = START;」は、以下を意味する。

命令セットシミュレーションのメインループであり、HALT命令(cpu停止命令)かdefaultラベル(未定義命令アドレスに分岐、エラー処理)に到達するまで実行を繰返す。

switch(P)は、機械語命令アドレスに対応する各case文(Cマクロ内部に埋込まれている)に分岐する構造を持っている。

分岐命令(CBLS:条件分岐,JSR:サブルーチン呼出し,UNLK:リターン)のCマクロには、プログラムカウンタの更新処理とbreak文を含んでおり、その機械語命令処理の後、switch文に制御が戻り、次命令アドレスに分岐する構造である。

図55Aの1行目の「Region3()」は、特定アドレス範囲の機械語命令の実行動作の記述である。以下、各命令を説明する。

図55Aの3行目の「switch文」は、PC(プログラムカウンタ:図中ac_pc)の値によって、該当する命令アドレスのcase文に分岐する。

図55Aの18行目の「default文」は、Region3()の範囲外の命令アドレスの場合は関数を終了する。

図55Bの1行目の「Execute()」は、シミュレータのメイン関数で、プログラムカウンタの上位ビットによって、該当するプログラム領域に対応するRegionXX()関数を呼ぶ。

Optimization 1(最適化1):PCが不連続な変化(分岐,コール等)をしない通常の命令では、次命令は直後のcase文になるので、無駄なbreak文を削除する。

Optimization 2(最適化2):PCが不連続な変化(分岐,コール等)をするときのみ、PCの更新を行う。

以下に、上記非特許文献4、8、9の手法で得られる命令セットシミュレータのCコード(以降「命令セットシミュレータソースコード」と呼ぶ)に関する課題を説明する。

switch文から任意のcase文へ分岐するコード構造では、分岐先情報が欠如していることからcompilerにおけるコード最適化が非常に掛かりにくくなる。

特に、ここで重要となるコード最適化は、後に使用されない命令を除去する「デッドコード除去」(dead code elimination)であり、シミュレーション実行時間に大きく影響を与える。命令セットシミュレータの動作記述では、 PCや状態フラグ(ゼロフラグ,符号フラグ,オーバーフローフラグ)が最も頻繁に更新され、これらの更新処理の記述が全体の動作記述の大きな部分を占めており、これらが最適化されないため、ネイティブ実行に比べて大きな処理オーバーヘッドとなる原因となっている。

分岐命令では、PC更新処理の後、break文によってプログラム制御がswitch文に戻った後にcase文に分岐する一連の処理も、ジャンプテーブル(メモリ)へのアクセスが発生するため、この部分も処理オーバーヘッドの原因となる。つまり、実行バイナリの関数階層構造が出力Cソースコードに反映されていないため、処理が長く時間がかかる原因となっている。

また、switch文に含むcase文の数の上限からプログラムを機械的に分割したCコード構造は、ソースプログラムとしては著しく可読性が低い。そのため、プログラムのプログラムのエラーを修正するデバッグ作業や、プログラムの機能拡張などのコード改変作業などが著しく困難になっている。

命令セットシミュレーション技術は、プロセッサのシミュレーション機能を実装する部分に対して焦点が当てられ、コンパイラ・逆コンパイラ技術と十分な連携を取らないまま発展してきた経緯がある。そのため、コンパイラ技術のプログラム制御フロー解析の仕組みを取り入れた命令セットシミュレータは存在しない。

図56に、従来の命令セットシミュレータを用いない組込みシステム用ソフトウエア開発環境を示す。

ソフトウエア開発環境がターゲットCPU搭載組み込みシステム製品(実機)の場合、ターゲットCPU用のプログラムソースコードまたはアセンブリコードは、ターゲットCPU用コンパイラで機械語の実行バイナリファイルに変換される。実行バイナリファイルは、ターゲットCPU搭載組み込みシステム製品のメモリに格納される。

ターゲットCPU用のプログラムソースコードまたはアセンブリコードは、ターゲットCPU用コンパイラで機械語の実行バイナリファイルに変換される。実行バイナリファイルは、命令セットシミュレータで、ホストCPU用の実行バイナリファイルに変換される。ホストCPU用の実行バイナリファイルは、ホストCPU搭載コンピュータで実行される。ターゲットCPU用の実行バイナリファイルから命令セットシミュレータで、ホストCPU用の実行バイナリファイルに変換されるので、ホストCPU搭載コンピュータでの詳細動作の再現が可能である。

第1に、データ型の復元が困難である。

第2に、「間接分岐」のプログラム制御フローの解析が困難である。

第3に、関数引数・戻り値の復元が困難である。

第4に、完全性という点で逆コンパイラによって出力されたソースコードは以下の2つの課題がある。一つ目の課題として、多くの既存の逆コンパイラは手動編集なしにコンパイル可能形式にすることが出来ない。二つ目の課題として、プログラム複雑度の制限により扱えるプログラムが限定される。

しかし、前述したように、非特許文献4、8、9の命令セットシミュレータでは、次の解決すべき課題がある。

第2の課題として、シミュレーション実行時間がネイティブ実行に比べ14倍〜54倍かかる。

第3の課題として、compilerにおけるコード最適化が非常に掛かりにくい。

第5の課題として、復元されるソースプログラムがサブルーチンの構造さえ実現していないので、ソースプログラムとしては著しく可読性が低い。

第6の課題として、プログラム制御フロー解析の仕組みが欠如している。

そこで、本願は実際の使用に供される非特許文献4、8、9の上述の第1〜第6の課題を解決するものである。

第1の本発明の命令セットシミュレータは、機械語プログラムをプログラムソースコードに変換して生成される命令セットシミュレータであって、前記機械語プログラムに含まれるサブルーチンを検出するサブルーチン検出手段と、前記機械語プログラムに含まれる命令語のうち分岐先アドレスを有する分岐命令を検出する分岐命令検出手段と、前記機械語プログラムに含まれる命令語のうちサブルーチン呼出し先アドレスを有するサブルーチン呼出し命令を検出するサブルーチン呼出し命令検出手段と、前記機械語プログラムを前記サブルーチン検出手段で検出した各サブルーチン単位のプログラムソースコードを出力するサブルーチンソースコード出力手段と、前記分岐先アドレスを示す識別子を前記プログラムソースコードの分岐先の命令に付加する識別子付加手段と、前記機械語プログラムの前記分岐命令を、前記プログラムソースコードの前記識別子をもつ命令への無条件分岐命令にして出力する無条件分岐命令出力手段と、前記機械語プログラムのサブルーチン呼出し命令を、前記プログラムソースコードのサブルーチン呼出し命令にして出力するサブルーチン呼出し命令出力手段とを備えている。

機械語プログラムの分岐命令がプログラムソースコードで無条件分岐命令にして出力されるとともに機械語プログラムに含まれるサブルーチンがプログラムソースコードのサブルーチンとして生成される。機械語プログラムの階層構造を復元できる(前記第4の課題の解決)。

そのため、コンパイラの最適化が効果的に行え(前記第3の課題の解決)、処理速度が速い(前記第2の課題の解決)。また、命令セットシミュレータの完全性を実現できる。

<本発明の概要>

本発明の命令セットシミュレータは、逆コンパイル技術で構築されてきたプログラムフロー制御解析機能やデータ依存性解析機能をStatic compile(静的コンパイル)方式に適用したものである。これにより、命令セットシミュレータ技術の持つ「完全性」を担保し、シミュレーション速度をネイティブ実行同等まで向上させられる。また、復元ソースコードの一定の可読性を担保する。

なお、「完全性」とは、どのようなプログラムでも確実にシミュレーション可能など実行バイナリを「確実」に実行できることである。

本発明の具体的内容を明らかにするため、第1実施形態の命令セットシミュレータのCソースコード出力について説明する。

図1に、Cソースコードのサンプルを示す。

図1に示すCソースコードサンプルを、C Compiler(gcc:GNU Compiler Collection)で組み込みプロセッサのARMv5命令セットの機械語命令に変換したものを図2に示す。図2には、各機械語命令のアドレスと32ビット機械語命令の16進表示と逆アセンブルしたアセンブリ命令を示している。図2において、左側4桁の英数字が命令アドレスであり、中央8桁の英数字が16進表示機械語命令であり、右側がアセンブリ命令である。

・16個のレジスタ(r0, …, r9, sl, fp, ip, sp, lr, pc):プログラムカウンタ(pc)も通常の命令で書き換えることができるようになっている。また、pcを更新する各種命令によって様々なプログラム制御が実現できる。

以下に本実施形態の命令セットシミュレータによって出力されるCソース記述の特徴を説明する。

第1に、関数の引数(例えばr0)は、CPUレジスタに対応したパラメータ名で引き渡される。関数引数に現れないその他のCPUレジスタは関数のローカル変数として宣言される。図3において、r0, r1, …, r9, sl, fp, …, pcまでがCPU汎用レジスタ変数(ローカル変数)であり、cv, cc, …, cleがCPU状態レジスタ変数(後記)である。

これにより、従来の静的コンパイル方式命令セットシミュレータ(非特許文献4、8、9)が生成していたPC(プログラムカウンタ)に関するswitch文と各命令アドレスに関するcase文のコード構造を用いずに済む。そして、実行バイナリのプログラム制御フローをそのままC言語の記述で表現できる。

本実施形態(本発明)によるCソースコード構造の特質は、実際に本実施形態の命令セットシミュレータによるCソースコードをコンパイルして実行することで確認できる。図3のCソースコードに出現するCマクロの内部構造は、複雑なCPU動作を忠実にC言語の記述で表現するためにかなり複雑なコードで構成されている。ここでは、複雑なCPU動作のC記述にも関わらず、本命令セットシミュレータが出力するCソースコードが如何に効率的な実行コード(ホストCPUの実行バイナリ)を生成するかについて説明する。ホストCPUとは、命令セットシミュレータ等のソフトウエアツールを実行するプロセッサ(デスクトップ・ノートブックPCに搭載されているプロセッサ等)をいう。

・ARMv5コードサイズ:26 + 7 * 2 = 40命令

get_primes関数:26命令

put_prime関数:7命令(インライン展開2ヶ所)

・X86コードサイズ:42命令

ホストCPU:Intel Xeon 3.4GHz (Quad core), 3.25GB memory

で実行すると、ネイティブ実行時間:0.7580秒であった。

これに対して、本実施形態(本発明)の命令セットシミュレータSによるテストプログラムの図2のコードを含む素数計算プログラムのシミュレーション実行時間は、0.7699秒であり、対ネイティブ実行時間:0.7580秒の比で1.016倍であった。

次に、命令セットシミュレータSを用いた組込みシステム用ソフトウエア開発環境について説明する。

図5に、第1実施形態の命令セットシミュレータを用いた組込みシステム用ソフトウエア開発環境を示す。

ホストCPUとは、命令セットシミュレータ等のソフトウエアツールを実行するプロセッサをいう。例えば、デスクトップ・ノートブックPCに搭載されているプロセッサ等をいう。

命令セットシミュレータSは、ソフトウェアを用いて実現される。なお、命令セットシミュレータSのうちの少なくとも一部をハードウェアで構成してもよい。

<実行バイナリデータ構造>

最初に、実行バイナリ(機械語)のデータ構造について説明する。

図6に、ELFファイルの全体構造の概要を示す。

ファイル種類は、実行可能ファイル、リンク可能ファイル、共有ライブラリ等である。

CPU機種・バージョン、エントリーポイント(プログラム実行時の最初のアドレス)、プログラムヘッダーテーブルの格納位置、セクションヘッダーテーブルの格納位置のELFヘッダーのサイズ、プログラムヘッダーテーブルの1つのエントリーのサイズとエントリー数、セクションヘッダーの1つのエントリーのサイズとエントリー数、セクション名文字列テーブルが格納されているセクションヘッダーテーブルインデックス等がある。

セグメント型として読込み可能セグメント、動的リンクセグメント等がある。その他、セグメントの格納位置、セグメントがメモリ上に配置される仮想アドレスと物理アドレス、セグメントのファイルサイズとメモリサイズ、セグメントのアクセス権(実行可、読出し可、書込み可の組合せ)等がある。

セクションとは、メモリ領域(プログラムメモリ・データメモリ)の構成単位として、また補足情報の格納単位として存在している。セクションヘッダーテーブルの1つのエントリーが1つのセクションに関する以下の情報を主要項目として含む。

セクション名文字列情報としてセクションヘッダー内のセクション名文字列テーブルセクションへのインデックスがある。

セクション型としてプログラム定義情報(メモリ領域の構成単位、デバッグ情報他)、シンボルテーブル(プログラムアドレス情報、変数アドレス情報)、文字列デーブル、再配置情報、動的リンク情報等がある。

セクション属性としてメモリ領域占有(読出し可能)、書込み可能、実行可能等がある。

その他、セクションのメモリアドレス、セクションの格納位置、セクションのサイズがある。

シンボルとは、主にメモリに格納されるプログラムアドレス情報と変数情報を含み、いずれかのセクションに属する。

シンボルテーブルは、セクションヘッダーテーブルの1つのエントリーとして格納される。シンボルは以下の情報を主要項目として含む。

シンボルのメモリアドレス、シンボルのサイズがある。

シンボル属性として、バインド属性、タイプ属性、可視性属性がある。特に、タイプ属性では、関数や他の実行可能命令に関連付けられるシンボルの属性を「FUNC型」と呼ぶことにする。

セクションインデックスとして、シンボルが属するセクションのインデックスがある。

「エントリーシンボル」:ELFヘッダーで定義された「エントリーポイント」(プログラム実行時の最初のアドレス)を「シンボルメモリアドレス」として持つ「シンボル」のことを指す。この「エントリーシンボル」の実行を終了することで、プログラム実行が終了するが、通常の終了手段としては、CPU動作を停止する「停止命令」もしくは、次の「プログラム終了処理シンボル」へのサブルーチン呼出し命令を実行する。

「プログラム終了処理シンボル」:プログラム実行を終了する処理を行うシンボルを指す。例えば、C言語ではexit()関数が「プログラム終了処理シンボル」である。

前記ELF構造において、実行プログラムが格納されているメモリ領域に関する情報は、幾つかの階層で定義されている。

・エントリーポイント(ELFヘッダー項目):プログラム起動後に最初に実行される命令が格納されたアドレス

・「実行可能」属性を持つセクションのアドレス領域がセクションヘッダーテーブルで定義される。

ここで、実行ファイルで定義されていることが保証されている情報はエントリーポイントと実行可能セグメントのアドレス領域であり、セクションヘッダーテーブルは省略可能であるため、セクション情報やシンボル情報が欠如する場合もあり得る。

まず、機械語命令解析処理で必要となるデータ構造を説明する。

(1)「シンボルアドレス一時リスト」:実行可能属性を持ち、関数等に関連付けられた実行可能シンボルのアドレスのリスト構造をもつ。機械語命令解釈処理が進行するに従って更新される。

「シンボル情報」とは、実行可能シンボルに関するシンボルアドレスと命令アドレスリストとの情報項目を格納する。

(A)シンボルアドレス

(B)命令アドレスリスト:シンボルアドレスから到達可能な全命令のアドレスのリスト構造をもつ。

(D)「データ依存サブルーチン命令フラグ」:シンボルアドレスから到達可能な全命令のなかで「データ依存サブルーチン命令」が含まれているか(1)否か(0)を示すフラグ。

「次命令情報」とは、ある命令が実行されてから次に実行し得る命令(以降「次命令」と呼ぶ)に関する情報で、以下のデータ項目からなる。

A)次命令アドレス

B)次命令タイプは、以下の3タイプのいずれかである。

2)「分岐」型:分岐命令における分岐先アドレス

3)「呼出し」型:サブルーチン呼出し命令における呼出し先アドレス

また、上記3つの「次命令タイプ」に対応して、「直後型次命令」、「分岐型次命令」、「呼出し型次命令」とそれぞれを呼ぶことにする。

「ジャンプテーブル情報」とは、後記の「データ依存分岐情報抽出部2の処理」によって生成される情報で、以下のデータ項目からなる。

A)データ依存分岐命令アドレス

B)ジャンプテーブルサイズ(データ依存分岐情報抽出部2の処理が成功しなかった場合は、ジャンプテーブルサイズは「0」となる)ジャンプテーブル情報リストに情報がないことを意味する。

C)分岐先アドレステーブル(1つのエントリーは、分岐先アドレスを格納する。「エントリー数」=「ジャンプテーブルサイズ」である。)

(1)リストへの「(非重複)追加」:追加するデータと同一データがリストに存在していない時のみ、リストの最後尾にデータを追加することをいう。以降では、基本的にすべてのリストが保持するデータは「非重複的」であるので、リストへの「追加」という表現は、特別な断りがない限り「非重複的追加」を意味する。

(2)リストからの「取出し」:リストの最後尾のデータを取出し、この最後尾データを削除することをいう。

次に、第1実施形態の命令セットシミュレータSの機械語命令解析部1について説明する。

図7に、第1実施形態の機械語命令解析部の機能ブロック図を示す。

機械語命令解析部1は、シンボルアドレス前処理部1a、シンボルアドレス取得部1b、命令アドレス取得部1c、次命令情報抽出部1d、アドレスリスト更新部1e、およびデータ依存分岐抽出部2を有している。

ここでは、実施形態1の機械語命令解析部1の処理として、セクションヘッダーテーブルが存在し、さらにその中にシンボルテーブルも定義されているという前提が成立する場合での処理の流れを説明する。

シンボルアドレス前処理部1aは、「シンボルアドレス一時リスト」を作成する。

シンボルアドレス前処理部1aは、セクションヘッダーテーブル内で定義されたシンボルテーブルにおいて、実行可能属性を持つセクションのアドレス領域に含まれたシンボルであって、関数や他の実行可能命令に関連付けられたタイプ属性を持つシンボル(前記の「FUNC型シンボルタイプ属性」参照)を「実行可能シンボル」と見なす。シンボルアドレス前処理部1aは、「実行可能シンボル」のアドレスをすべて「シンボルアドレス一時リスト」に「追加」することで「シンボルアドレス一時リスト」を作成する。

その後、シンボルアドレス取得部1bへ進む。

(1)「シンボルアドレス一時リスト」が空でない場合

A)シンボルアドレス取得部1bは、「シンボルアドレス一時リスト」から、シンボルアドレスを一つ「取出す」(以降、このシンボルを「現シンボル」と呼ぶ)。

B)現シンボルに関する「シンボル情報」が既に「シンボル情報リスト」に存在する場合(現シンボルは処理済み)は、以降の処理すべてをスキップし、直ちにシンボルアドレス取得部1bの処理のスタートに戻る。

1)「シンボル情報」の「シンボルアドレス」に「現シンボル」アドレスを設定する。

2)「シンボル名文字列」を生成する。シンボルが「シンボルテーブル」に登録されている場合は、「シンボルテーブル」内の「シンボル名文字列情報」を取得して生成する。一方、シンボルが「シンボルテーブル」に登録されていない場合は、任意の命名規則によりシンボル名として重複しない文字列を生成する(一例としては、「シンボルアドレス」を基にシンボル名を生成する:シンボルアドレスが0x1234の場合に、「func_1234」とする、など)。

3)「データ依存サブルーチン命令フラグ」を「0」に設定する。

(1)「命令アドレス一時リスト」が空でない場合、命令アドレス取得部1cは「命令アドレス一時リスト」から命令アドレスを一つ「取出す」。以降、これを「現命令アドレス」と呼ぶ。

「現命令アドレス」が、「現シンボル情報」の「命令アドレスリスト」に既に存在する場合(現命令アドレスは処理済み)は、以降の処理すべてをスキップし、直ちに命令アドレス取得部1cの処理のスタートに戻る。

一方、「現命令アドレス」が、「現シンボル情報」の「命令アドレスリスト」に存在しない場合、「現命令アドレス」を「現シンボル情報」の「命令アドレスリスト」へ「追加」し、下記の次命令情報抽出部1dの処理へ進む。

そして、シンボルアドレス取得部1bの処理に戻る。

次命令情報抽出部1dは、「現命令アドレス」を基に、「実行バイナリファイル」の「バイナリデータ部」に格納されているバイナリデータを読出し、このバイナリデータを機械語命令と見なす。そして、次命令情報抽出部1dは、この機械語命令をデコード(解釈)して、命令種別に対応した以下(1)〜(4)の処理を実行し「次命令情報」を生成し、「次命令情報一時リスト」に「追加」する。

(2)「データ依存分岐命令」(分岐先アドレスがレジスタ値・メモリ値で決定される分岐命令)の場合、命令語のみでは分岐先を直接特定できないので、以下の処理を実行する。

まず、後記の「データ依存分岐情報抽出部2」を実行して、ジャンプテーブル情報リストr3の「ジャンプテーブル情報」を抽出する。そして、次命令情報抽出部1dは、抽出された「ジャンプテーブル情報」の「分岐先アドレスリストr2」に格納されたすべての分岐先アドレスについて、「分岐型」次命令情報を生成する。

(4)「データ依存サブルーチン呼出し命令」(呼出し先アドレスがレジスタ値・メモリ値で決定されるサブルーチン呼出し命令)の場合、次命令情報抽出部1dは、「現シンボル情報」の「データ依存サブルーチン命令フラグ」を「1」に設定する。なお、「データ依存サブルーチン呼出し命令」の呼出し先アドレスの解決は、後述の別手段で行う。

A)無条件に実行される「単純分岐命令」または「データ依存分岐命令」:いずれかの分岐先アドレスが次命令アドレスになるため。

B)リターン命令:サブルーチンから復帰するときの「リターン命令」は、復帰先アドレスが一意に定まらないため。

C)CPU停止命令:CPUの実行動作を停止する命令。

E)非機械語命令:命令セットで規定されたいずれの命令にも当てはまらない場合。

上記以外のすべての命令(条件付き分岐命令、条件付きデータ依存分岐命令、サブルーチン呼出し命令を含むことに注意)は、すべて「直後命令」を実行する可能性があるので、「直後命令アドレス」から「直後型」次命令情報を生成する。

その後、アドレスリスト更新部1eに進む。

次命令情報抽出部1dで生成された「次命令情報一時リスト」から、以下のように、各種アドレスリストの更新処理を行う。

(1)「直後型」次命令情報による更新は、「次命令情報一時リスト」から、「直後型」次命令情報をすべて「取出し」、これらを命令アドレス一時リストに追加する。

(2)「分岐型」次命令情報による更新は、「次命令情報一時リスト」から、「分岐型」次命令情報をすべて「取出し」、これらを分岐先アドレスリストr2と命令アドレス一時リストとに「追加」する。

その後、命令アドレス取得部1cに戻る。

データ依存分岐情報を生成するためのデータ依存分岐情報抽出部2の処理原理について説明する。

図8に、switch文を含んだ関数jump_testのサンプルCプログラムを示す。

図8のサンプルCプログラムにおいて、jump_test関数内のswitch文(switch(n)[ case 3: … case 8: … default: …])が変数nの値に関するデータ依存分岐命令として実装される。

データ依存分岐命令は、以下の命令要素とデータ要素を予め準備して動作する。

(1)case文の整数定数の最小値と最大値:図8の場合は、最小値3、最大値8である。以後、min_case_value = 3, max_case_value = 8と表記する。

また、min_case_value <= idx <= max_case_valueの範囲の定数idxでcase文に出現しない値については、default文が存在する場合はdefault文に対応する先頭命令アドレスが格納され、default文が存在しない場合はswitch文直後の先頭命令アドレスが格納されている。

(4)ジャンプテーブルオフセット値の範囲判定命令:前記ジャンプテーブルオフセット値jt_offsetについて、jt_offset >= 0かつjt_offset <= max_jt_index = max_case_value ‐ min_case_valueであるかの範囲判定を行う。もし、前記範囲判定が「真」の場合、データ依存分岐先アドレスはジャンプテーブル内に存在し、範囲判定が「偽」の場合は、データ依存分岐先アドレスはジャンプテーブル内に存在しない。

(1)ジャンプテーブルオフセット値の範囲判定命令

(2)ジャンプテーブルオフセット値の範囲判定による条件付き分岐命令

(3)ジャンプテーブル格納メモリ読出し命令

(4)データ依存分岐命令

なお、(3)、(4)が一つの機械語命令となる場合もある(前記)。(2)は(4)の直後に来る場合もある。

図9に、データ依存分岐情報抽出部の機能ブロック図を示す。

データ依存分岐情報抽出部2は、以下の一連の処理を行う。データ依存分岐命令のアドレスは既に前記の次命令情報抽出部1d(図7)で与えられているとする。

(1)「ジャンプテーブル格納メモリ読出し命令」抽出部2a

データ依存分岐命令そのものがメモリ読出しを行う場合は、この命令が「ジャンプテーブル格納メモリ読出し命令」である。また、レジスタ値をPCに代入するデータ依存分岐命令の場合は、このデータ依存分岐命令が実行される前のレジスタにメモリロードする命令が「ジャンプテーブル格納メモリ読出し命令」となる。

ジャンプテーブル格納メモリ読出し命令において、メモリアドレスが「ベースアドレス値(固定アドレス)+オフセット値」の形式で計算されている場合、「ベースアドレス値」を「ジャンプテーブル格納メモリアドレス値」と特定し、オフセット値を格納するレジスタを「ジャンプテーブルオフセットレジスタ」と特定する。

「ジャンプテーブル格納メモリ読出し命令」が実行される前に位置する「ジャンプテーブルオフセットレジスタに対する範囲判定命令」を特定する。この範囲判定命令の比較対象定数値が前述のmax_jt_indexであり、max_jt_index + 1 = max_case_value ‐ min_case_value + 1がジャンプテーブルサイズであることが特定できる。「ジャンプテーブルオフセットレジスタに対する範囲判定命令」が特定できない場合や、範囲判定命令の比較対象が定数値でない場合は、データ依存分岐情報抽出部2の処理が不可能であると判断し、「データ依存分岐情報抽出部2の処理」を終了する。

前記で特定した「ジャンプテーブル格納メモリアドレス値」と「ジャンプテーブルサイズ」の情報から、ジャンプテーブルに格納される分岐先アドレスをすべて読み出し、分岐先アドレステーブル(機械語アドレステーブル)に格納する。

予め与えられた「データ依存分岐命令」と、上記(1)〜(4)の工程で得られた「ジャンプテーブルサイズ」と「分岐先アドレステーブル」からなる「データ依存分岐ジャンプテーブル情報」を生成し、「データ依存分岐情報リスト」に「追加」する。生成したデータ依存分岐ジャンプテーブルの情報は、前記した次命令情報抽出部1dで使用される。

図10に、図8のjump_test関数のARMv5命令セットの機械語命令とアセンブリ命令を示す。各行は、「命令アドレス」(16進表記)、「機械語命令データ」(16進表記)、「アセンブリ命令記述」の順で表記されており、PC(プログラムカウンタ)に作用する命令については、その命令種別も表記している。

以下の説明では、「シンボルアドレス一時リスト」から“jump_test”のアドレス0x8340を取得したことを前提に、その後の機械語命令解析処理について説明する。

B)0x834cの命令は「データ依存分岐命令」のため、この部分の次命令情報抽出処理は、データ依存分岐情報抽出部2において行われる。

解析対象命令アドレス0x836直前の命令アドレスリストと命令アドレス一時リストとは、表6の上欄に示す如くである。

図11に、jump_test関数のx86(64-bit)命令セットの機械語命令とアセンブリ命令を示す。各行は、左から、「命令アドレス」(6桁の16進表記)、「機械語命令データ」(左から右への順番で16進数2桁ごとに区切られている)、「アセンブリ命令記述」の順で表記されている。なお、PC(プログラムカウンタ)に作用する命令については、その命令種別も表記している。

B)0x40056aの命令は「条件付き分岐命令」のため、分岐先アドレス0x400575と直後命令アドレス0x40056cが次命令アドレスとなる。

C)0x40056eの命令は「データ依存分岐命令」のため、この部分の次命令情報抽出部1dの処理は、データ依存分岐情報抽出部2において行われる。

図12に、命令セットシミュレータの構成を、解析対象の実行バイナリファイル、命令セットシミュレータが出力する命令セットシミュレータプログラムソースコードとともに示す。

命令セットシミュレータSは、機械語命令解析部1と命令セットシミュレータプログラムソースコード出力部3とを備えている。

命令セットシミュレータプログラムソースコード出力部3は、サブルーチンプログラムソース生成部3aと、シンボルアドレス情報テーブルソース生成部3bと、メモリ初期化プログラム記述生成部3cと、メイン関数プログラム記述生成部3dとを有している。

ここでは、「命令セットシミュレータプログラムソースコード4」を生成するための準備として必要となるCPUリソースのデータ構造記述について説明する。

A)_r_(n): n番目の汎用レジスタを参照するためのマクロ

B)_R_,_C_,_V_,_LS_,_LE_,_GE_:6つの状態レジスタ変数(cr, cc, cv, cls, cge, cle)を参照するためのマクロ

C)_m8_, _m16_, _m32_:メモリから8ビットデータ、16ビットデータ、32ビットデータをそれぞれ「読出し」・「書込み」するためのマクロ

A)AL(無条件):常に命令を実行する。

B)EQ(equal条件)、NE(not equal条件)

1)Z/N/V/C判定式:EQ(Z==1), NE(Z==0)

2)6状態変数判定式:EQ(_R_==0), NE(_R_!=0)

1)Z/N/V/C判定式:CS(C==1), CC(C==0)

2)6状態変数判定式:CS(_C_!=0), CC(_C_==0)

D)MI(minus条件)、PL(plus条件)

1)Z/N/V/C判定式:MI(N==1), PL(N==0)

2)6状態変数判定式:MI(((S32)_R_)<0), PL(((S32)_R_)>=0)

1)Z/N/V/C判定式:VS(V==1), VC(V==0)

2)6状態変数判定式:VS(((S32)_V_)<0), VC(((S32)_V_)>=0)

F)HI(higher条件)、LS(lower or same条件):符号なし

1)Z/N/V/C判定式:HI(C==1 && Z==0), LS(C==0 || Z==1)

2)6状態変数判定式:HI(_LS_==0), LS(_LS_!=0)

1)Z/N/V/C判定式:GE(N==V), LT(N!=V)

2)6状態変数判定式:GE(_GE_!=0), LT(_GE_==0)

H)GT(greater than条件)、LE(less or equal条件):符号付き

1)Z/N/V/C判定式:GT(Z==0 && N==V), LE(Z==1 && N!=V)

2)6状態変数判定式:GT(_LE_==0), LE(_LE_!=0)

「機械語命令プログラム生成マクロ」とは、幾つかの引数(変数、定数、文字列)に基づいて、実行プログラム記述を部分的に生成する機能を持つプログラミング記述手法のことである。

図15に示す4つの機械語命令に対応する「機械語命令プログラムマクロ」呼出し記述を図16に示す。以降、各機械語命令プログラムマクロについて説明する。

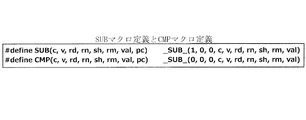

図17に、SUBマクロ定義とCMPマクロ定義を示す。

sub命令に対応してSUBマクロを呼び、cmp命令に対応してCMPマクロを呼んでいる。

・c(実行条件を表す文字列):Z/N/V/Cの4ビットによる状態レジスタ

・v(命令ビットフィールド):主に内部レジスタの更新条件を示す命令属性

・rd(出力レジスタID):計算結果を格納するレジスタ番号

・rn(第1オペランドレジスタID):第1オペランドを格納するレジスタ番号

・sh(シフト属性):第2オペランドに対するシフト処理属性

・rm(第2オペランドレジスタID):第2オペランドを格納するレジスタ番号

・val(即値データ):第2オペランドが即値(定数)の場合の即値データ

・pc(命令アドレス):ここでは命令動作プログラムには関係ない

ここで、SUBマクロとCMPマクロで使われる引数の意味は以下の通りである。

・w_rd(出力属性):1の場合出力レジスタに格納し、0の場合格納しない。

・cin(キャリー入力):減算のキャリー入力

・swap_op(オペランド入れ替え属性):1の場合第1・第2オペランドを入れ替え、0の場合はそのまま。

・c, v, rd, rn, sh, rm, val:SUB/CMPマクロ引数と同じ意味

・IMM(rm, val):図16のSUBマクロ呼出しとCMPマクロ呼出しでは、これらのマクロ引数shとして「IMM」が与えられている。図18における「sh(rm, val)」の記述は、「IMM(rm, val)」に変換され、このIMMマクロ定義では、最終的に「(val)」に変換される。

・__fB_(v), _fH_(v), _fP_(v), _fU_(v), _fW_(v):_fS_(v)と同様に、vの特定ビットを取り出す演算を定義する。後述のSTRマクロで呼び出される。

図16で呼ばれるSTRマクロ定義を図20に示し、そのマクロ内部で呼び出される_ADDR_, _D_CACHE_SIMマクロ定義を図21に示す。(補足:元の機械語のアセンブリ命令記述では「push [lr]」(図15参照)となっているが、これは、スタックポインタsp(arm.r[13])を「デクリメント」(1データワード分のアドレスを減算)した値をメモリアドレスとして、リンクレジスタlr(arm.r[14])をメモリに書込む動作をし、ARMv5におけるstr命令として実装される。)

・c(実行条件を表す文字列):SUBマクロやCMPマクロと同様

・v(命令ビットフィールド):アドレスオフセット計算方法、アドレスレジスタの更新の有無、データ型情報等の命令属性

・rd(書込みデータレジスタID):書込みデータを格納するレジスタ番号

・rn(ベースアドレスレジスタID):ベースアドレスを格納するレジスタ番号

・sh(シフト属性):オフセットオペランドに対するシフト処理属性

・rm(オフセットレジスタID):オフセット値を格納するレジスタ番号

・val(即値データ):オフセット値が即値(定数)の場合の即値データ

・pc(命令アドレス):現命令アドレス(ベースアドレスレジスタがPC(プログラムカウンタ)の場合、現命令アドレスがアドレス計算で使われる)

図16で呼ばれるLDRマクロ定義を図22に示す。(補足:元の機械語のアセンブリ命令記述では「pop [pc]」となっているが、これは、スタックポインタsp(arm.r[13])をメモリアドレスとして、前記push [lr]で記録された「戻り命令アドレス値」をメモリから読出し、スタックポインタを「インクリメント」(1データワード分のアドレスを加算)する動作をし、ARMv5におけるldr命令として実装される。)

前述の4つの命令プログラム生成マクロ(SUB, STR, CMP, LDR)の呼出しは、最終的に、図23に示すプログラム記述を生成する。

図12に示すサブルーチンプログラムソース4aのプログラム記述上における「サブルーチン命名規則」について説明する。

サブルーチン命名規則で注意すべき点は、例えば、C言語では、main関数やexit関数のように特別な意味を持つサブルーチン名が予約されているため、予約サブルーチン名と重複しないようにする必要がある。

ここでは、図16に示すような機械語命令プログラム生成マクロ呼出し記述を含み、サブルーチンプログラムソースを生成する「サブルーチンプログラムソース生成部3a」(図24)について説明する。

前記の機械語命令解析部1で生成したシンボル情報リストr1からシンボル情報を一つ取り出す。以後、ここで取り出したシンボル情報を「現シンボル情報」と呼ぶ。

「現シンボル情報」に含まれる「サブルーチン名文字列」を基に、図25に示すような「サブルーチン定義記述」を生成する。「第1実施形態」では、戻り値がなく(void型)、引数を取らないサブルーチンの定義の記述を生成する。

命令アドレス取得部3a3は、「現シンボル情報」の「命令アドレスリスト」の先頭から「命令アドレス」を順次読み出す。読み出した「命令アドレス」を、以後「現命令アドレス」と呼ぶ。

「現命令アドレスが分岐先アドレスリストr2(機械語命令解析部1で生成)に存在する場合、プログラム分岐記述(goto文等)を可能とするために、命令(コマンド)を識別するための「プログラムラベル記述」を生成する。前記したARMv5命令セットのjump_test関数の機械語命令解析処理で得られた「分岐先アドレスリスト」は、[ 0x8384, 0x839c, 0x836c, 0x83a4]である(表3参照)。これらの分岐先アドレスに対応するC言語のラベル記述は、例えば、"L_08384:", "L_0839c:", "L_0836c:", "L_083a4:"と生成すればよい。

機械語命令種別判定部3a5では、「現命令アドレス」を基に、「実行バイナリファイル」の「バイナリデータ部」に格納されているバイナリデータを読出す。このバイナリデータを機械語命令と見なし、この機械語命令をデコード(解釈)して(前記の次命令情報抽出部1dの機械語命令デコード処理と同じ手順)、以下の命令種別を判定する。

・「単純サブルーチン呼出し命令」(命令語のみで呼出し先アドレスが特定できるサブルーチン呼出し命令)の場合:単純サブルーチン呼出し命令プログラム記述生成部3a7に進む。

・「データ依存サブルーチン呼出し命令」(呼出し先アドレスがレジスタ値・メモリ値で決定されるサブルーチン呼出し命令)の場合:データ依存サブルーチン呼出し命令プログラム記述生成部3a9に進む。

・上記以外の場合:機械語命令プログラム生成マクロ呼出し記述生成部3a10に進む。

ここでは、機械語命令の動作に関する以下の詳細情報を取得する。

・命令種別:機械語命令プログラム生成マクロ名を特定する。図16におけるSUB, STR, CMP, LDRなどの マクロ名を生成するための情報となる。

SUB(AL,0x020, 3, 0, IMM,-1, ...) ( 作用レジスタ番号:3, 0

STR(AL,0x009,14,13, IMM,-1, ...) (作用レジスタ番号:14, 13

CMP(AL,0x024, 0, 3, IMM,-1, ...) (作用レジスタ番号:0, 3

LDR(AL,0x012,15,13, IMM,-1, ...) (作用レジスタ番号:15, 13

AL:実行条件(always:無条件で実行)

0x020:命令ビットフィールド引数vに対応(内部レジスタ更新なし)

IMM:シフト属性引数shに対応(第2オペランドが即値)

0x00000003:即値データ

AL:実行条件(always:無条件で実行)

0x009:命令ビットフィールド引数vに対応(アドレスオフセット計算方法、アドレスレジスタ更新の有無、データ幅情報等を含む)

IMM:シフト属性引数shに対応(アドレスオフセットが即値)

0x00000004:即値データ

AL:実行条件(always:無条件で実行)

0x024:命令ビットフィールド引数v(図17)に対応

IMM:シフト属性引数shに対応(第2オペランドが即値)

0x00000005:即値データ

AL:実行条件(always:無条件で実行)

0x012:命令ビットフィールド引数vに対応

IMM:シフト属性引数shに対応(アドレスオフセットが即値)

0x00000004:即値データ

これらの機械語命令に関する詳細情報に基づき、「機械語命令プログラム生成マクロ呼出し記述」を生成する。

命令語のみで分岐先アドレスが特定できるような「単純分岐命令」については、goto文(無条件分岐命令)などを使ったプログラム分岐の記述を生成する。

以下では、図10の機械語命令記述における図26の無条件分岐命令(図10の6行目)について説明する。

また、条件付き分岐の場合でも、AL(always:無条件で実行)の代わりに、対応する実行条件の文字列(EQ, NEなど)を挿入するだけで実現できる。

命令語のみで呼出し先アドレスが特定できるような「単純サブルーチン呼出し命令」については、図28に示すサブルーチン呼出しを行うプログラム記述を生成する。

以下では、jump_test関数を呼び出す図29の機械語命令記述について説明する。

また、条件付き実行のサブルーチン呼出し命令の場合でも、AL(always:無条件で実行)の代わりに、対応する実行条件の文字列(EQ, NEなど)を挿入するだけで実現できる。

分岐先アドレスがレジスタ値・メモリ値で決定されるような「データ依存分岐命令」については、機械語命令解析部1で生成した「ジャンプテーブル情報リスト」から、「データ依存分岐命令」のアドレスを基に、該当する「ジャンプテーブル情報」を検索し、その中に格納されている「分岐先アドレステーブル」を用いて、「データ依存分岐命令プログラム記述」を生成する。

ここで、「データ依存分岐命令」のアドレス0x834c対応する「ジャンプテーブル情報」は以下の通りである。

・ 分岐先アドレステーブル:[ 0x8384, 0x839c, 0x836c, 0x83a4, 0x836c, 0x8384 ]

このジャンプテーブル情報と、この「データ依存分岐命令」の実行条件(ls: less or same条件)を用いて、図31のようなプログラム記述が生成される。

ここで、各case文後に出てくるgoto文のラベルは、「ジャンプテーブル情報」の「分岐先アドレステーブル」の各分岐先アドレスのラベルに対応している。なお、case 0:とcase 5:に対応する条件分岐は、defaultラベルに対応している。

呼出し先アドレスがレジスタ値・メモリ値で決定されるような「データ依存サブルーチン呼出し命令」については、後記のシンボルアドレス情報テーブルソース生成部3bで生成する「シンボルアドレス情報」を使って、データ依存サブルーチン呼出しをプログラム記述上で実現する。

ここでは、前記したように、0x83acはレジスタr3の値にジャンプする「データ依存分岐命令」であるが、その直前の0x83a8に、pc(実際の値は現命令アドレス0x83a8 + 8)をリンクレジスタlrに代入する命令があるため、0x83acの命令は実際には「データ依存サブルーチン呼出し命令」であることが判別できる。0x83a8と0x83acの2命令に対応するプログラム記述は図33のようになる。

なお、ここで生成された図33のプログラム記述の内容については、後記するシンボルアドレス情報テーブルソース生成部3bで説明する。

図10の"jump_test"関数のARMv5命令セットの機械語命令記述に対応するサブルーチンプログラム記述の出力例を図34に示す。

ここでは、前記したデータ依存サブルーチン呼出し命令プログラム記述生成部3a9によって生成されるプログラム記述を実行するための情報を生成し、プログラムソースに出力する処理について説明する。この処理は、「シンボル情報」の「データ依存サブルーチン呼出し命令フラグ」が「1」であるものが「シンボル情報リスト」に含まれる場合にのみ必要となる。

また、図33にある_GET_FPI_(_r_(3))は、_r_(3)の値が示す「シンボルアドレス」を基に、後記の「シンボルアドレス情報テーブル」から該当する「シンボルアドレス情報」のデータ構造体へのポインタを返す関数の呼出しである(後述)。つまり、fpiが指す「シンボルアドレス情報」のデータ構造体へのポインタを使い、このデータ構造体に格納されているサブルーチンのアドレス(func)を使うことで、fpi->func()というデータ依存サブルーチン呼出しをプログラム上で実現している。

また、シンボルアドレス情報テーブルに含まれるシンボル数が非常に多いと、_GET_FPI_関数の処理時間が長くなる懸念はあるが、その場合は、「2分木探索法」や「ハッシュ探索法」などを使って、シンボルアドレスを基とした探索処理の高速化手法を適用すればよい。

メモリ初期化プログラム記述生成部3c(命令セットシミュレータプログラムソースコード出力部3)では、命令セットシミュレータSのプログラム記述におけるCPUのメモリ領域の初期化を行うためのプログラム記述を生成する。

メモリ領域の初期化の対象は、初期値が定義されているデータ領域の他にも、プログラム領域にも初期値データが含まれる場合がある。そこで、プログラム領域も初期化の対象とする。

ここでは、最終的に生成する命令セットシミュレータSのプログラム記述の最上位関数(main関数)のプログラム記述について説明する。最上位関数(main関数)のプログラムはメイン関数プログラム記述生成部3dが作成する。

前記したように、実行バイナリファイルで定義されている「エントリーポイント」(プログラム実行時の最初のアドレス)を「シンボルアドレス」として持つ「エントリーシンボル」が最初に実行するサブルーチンに対応している。そこで、「命令セットシミュレータ」のプログラム記述の最上位関数から、「エントリーシンボル」に対応するサブルーチンを呼び出すプログラム記述を生成する。

以上により生成される命令セットシミュレータプログラム記述構造は以下の特徴を持つ。

また、単純分岐命令においてgoto文とラベル文が明確に対応し、データ依存分岐命令においてswitch文とcase文が明確に対応しており、プログラム制御の流れも理解しやすい。

従って、プログラム記述の可読性が高く、プログラムのデバッグ作業やプログラムの機能拡張などのコード改変作業を効率的に行うことができる。

これらのことから、命令セットシミュレータSの処理速度が大幅に向上する。

1.命令セットシミュレータSを用いた組込みシステム用ソフトウエア開発環境によれば、詳細動作の再現が可能である。

第1の課題として、どの命令が分岐先アドレスとなり得るかを判断する情報がない。

第2の課題として、シミュレーション実行時間がネイティブ実行に比べ14倍〜54倍かかる。

第3の課題として、compilerにおけるコード最適化が非常に掛かりにくい。

第4の課題として、階層構造が欠如している。

第5の課題として、ソースプログラムとしては著しく可読性が低いという

第6の課題として、プログラム制御フロー解析の仕組みが欠如している。

前述したように、第1実施形態の命令セットシミュレータSの構成によれば、分岐先アドレスが分岐先命令にラベル(識別情報)として付加されたり、ジャンプテーブル等があるので、どの命令が分岐先アドレスとなり得るかを判断する情報がある。

また、シミュレーション実行時間がネイティブ実行時間とほぼ同等である。

また、バイナリファイルの階層構造がプログラムソースコードに復元されるので、compilerにおけるコード最適化がかかり易い。

また、バイナリファイルから復元されるソースプログラムは、バイナリファイルの各サブルーチンが関数の構造を持ち、階層構造を有するので可読性が高い。

さらに、単純分岐命令、データ依存分岐命令、データ依存サブルーチン等を解析してジャンプテーブル等で分岐先を明示するので、プログラム制御フロー解析の仕組みを有している。

以上のことから、第1実施形態(本願発明)により、実際の使用に供される非特許文献4、8、9の問題を解決することができる。

第2実施形態の命令セットシミュレータ2S(図43参照)は、第1実施形態の命令セットシミュレータSに「サブルーチン引数抽出機能」を追加したものである。

その他の構成は、第1実施形態の命令セットシミュレータSと同様であるから同様な構成要素には同一の符号を付して示し、詳細な説明は省略する。

第2実施形態の機械語命令解析部21は、第1実施形態のシンボルアドレス前処理部1a、シンボルアドレス取得部1b、命令アドレス取得部1c、次命令情報抽出部1d、アドレスリスト更新部1e、およびデータ依存分岐抽出部2に、新たにサブルーチン引数抽出部1fを加えて構成したものである。

図43に、第2実施形態の命令セットシミュレータ2Sの構成を、解析対象の実行バイナリファイル5、命令セットシミュレータ2Sが出力する命令セットシミュレータプログラムソースコード4とともに示す。

命令セットシミュレータ2Sは、実行バイナリファイル5を入力として、高級言語の命令セットシミュレータプログラムソースコード4を出力する。

<サブルーチン引数抽出部1f>

サブルーチン引数抽出部1fによる処理は、命令アドレス取得部1cが「現シンボル情報」を「シンボル情報リスト」に「追加」する前に、実行する(図42、図7参照)。

サブルーチンの「引数」は、サブルーチン呼出し前にCPUレジスタに設定されたデータであり、プログラムの命令実行がサブルーチンに入った後に参照される(引数がスタックメモリに格納される場合はここでは考慮しない)。どのレジスタが「サブルーチン引数」であるかを解析するためには、命令実行がサブルーチンに入った後にいかなる命令によっても更新されずに参照されるレジスタを見つければよい。この解析のためには、各命令がどのレジスタを参照し、どのレジスタを更新するかを予め解析(把握)しておき、命令実行順序を「逆順」に辿ることで、「サブルーチン引数」を特定することができる。

(2)出力レジスタIDリスト(図44でO(..)と表記):機械語命令がオペランドとして使用するレジスタIDのリスト

A)sub r3, r0, #3:第1オペランド がr0なのでI(0)となり、結果格納レジスタがr3なのでO(3)となる。

B)push [lr]:ベースアドレスがスタックポインタ(sp: r[13])であり、書込みデータがリンクレジスタ(lr: r[14])なのでI(13,14)となり、ベースアドレスレジスタが更新されるのでO(13)となる。

D)ldrls pc, [pc, r3, lsl #2]:ベースアドレスがpc(入力とみなさない)でオフセットがr3であり、条件付き実行命令であるので状態レジスタ(CC)を参照するのでI(3,16)となる。出力レジスタpcは除かれるのでO()となる(出力レジスタはない)。

B)「入力レジスタIDリスト」のすべてのレジスタIDを「生存入力レジスタIDリスト」に(非重複的に)「追加」する。

A)リンクレジスタ(lr:r[14]):「サブルーチン引数」と見なさない。なぜなら、CPU動作上で「サブルーチン呼出し処理」と「サブルーチン復帰処理」を実現するためのレジスタの情報は、プログラム記述上でこれらサブルーチンに関する制御を直接行う「当発明技術」には不要であるからである。

C)その他のレジスタ:「サブルーチン引数」と見なす。

サブルーチンの引数抽出部1fの処理では、以下のデータ構造を使用する。

(1)命令情報リスト:「生存入力レジスタ」を解析するための命令情報リスト。

「命令情報」は以下のデータ項目からなる。

A)命令情報ID:各命令情報に固有のID番号

B)命令アドレス

C)入力レジスタIDリスト

E)生存入力レジスタIDリスト(命令毎の「生存入力レジスタ」)

F)次命令情報リスト:前記の「次命令情報一時リスト」と同じ情報

G)「前方向命令情報IDリスト」:その命令を「次命令」するすべての命令の命令情報IDからなるリスト(命令実行の逆順に辿る時に必要となる)

また、前記した「シンボル情報」に「サブルーチン引数レジスタIDリスト」を追加する。

「第2実施形態のシンボル情報」のデータ項目:

A)シンボルアドレス

B)命令アドレスリスト

C)シンボル名文字列

D)データ依存サブルーチン命令フラグ

E)サブルーチン引数レジスタIDリスト(第2実施形態で新たに加わったもの)

図45に、サブルーチン引数抽出部1fの機能ブロック図を示す。

サブルーチン引数抽出部1fは、入出力レジスタ解析部1f1、前方向命令解析部1f2、サブルーチン引数抽出前処理部1f3、命令情報取得部1f4、生存入力レジスタIDリスト更新部1f5、およびサブルーチン引数レジスタ決定部1f6を有している。以下、サブルーチン引数抽出部1fの各部について説明する。

「現シンボル情報」の「命令アドレスリスト」から「命令アドレス」を一つずつ順次取得し、その命令アドレスに対応する「命令情報」を生成する。そして、「命令情報」に「命令情報ID」を適宜(重複しないように)設定し、その命令の「命令アドレス」を設定し、「入力レジスタIDリスト」、「出力レジスタIDリスト」、「次命令情報リスト」を作成する。なお、「次命令情報リスト」の作成には前記の次命令情報抽出部1dを使う。この時点では、各「命令情報」の「生存入力レジスタIDリスト」と「前方向命令情報IDリスト」は「空」にする。すべての「命令アドレス」に対する処理が終了後、前方向命令解析部1f2の処理へ進む。

「命令情報リスト」の各「命令情報」において(以降この「命令情報」を「現命令情報」と呼ぶことにする)、「次命令情報リスト」に含まれる「直後型次命令」と「分岐型次命令」の各「次命令アドレス」を基に、該当する「命令情報」を探索する。命令情報の命令アドレスが次命令アドレスと一致するものを探索する。以降探索した「命令情報」を「次命令情報」と呼ぶ。この「次命令情報」の「前方向命令情報IDリスト」に「現命令情報」の「命令情報ID」を(非重複的に)「追加」する。すべての「命令情報」に対する処理が終了後、サブルーチン引数抽出前処理部1f3へ進む。

サブルーチン引数抽出処理前処理部1f3の前処理として、以下を実行する。

「命令情報リスト」に含まれる命令情報のうち、「リターン命令」に該当する「命令情報」の「命令情報ID」をすべて「命令情報ID一時リスト」に(非重複的に)「追加」する。「サブルーチン生存入力レジスタID一時リスト」を「空」にする。

その後、命令情報取得部1f4へ進む。

「命令情報ID一時リスト」から「命令情報ID」を「取り出し」、該当する「命令情報」を取得し、生存入力レジスタIDリスト更新部1f5へ進む。以降、これを「現命令情報」と呼ぶ。「命令情報ID一時リスト」が「空」の場合、サブルーチン引数レジスタ決定部1f6へ進む。

以下の処理を実行し、命令情報取得部1f4の処理へ戻る。

(1)「現命令情報」の「出力レジスタIDリスト」の各「出力レジスタID」について、「サブルーチン生存入力レジスタID一時リスト」に含まれる場合は、そのレジスタIDを「サブルーチン生存入力レジスタID一時リスト」から削除する。

(2)「現命令情報」の「入力レジスタIDリスト」の各「入力レジスタID」を「サブルーチン生存入力レジスタID一時リスト」に(非重複的に)「追加」する。

A)「サブルーチン生存入力レジスタID一時リスト」の各レジスタIDを「現命令情報」の「生存入力レジスタIDリスト」に非重複的に「追加」する。つまり、重複する場合、レジスタIDは「生存入力レジスタIDリスト」に追加しない。

B)「現命令情報」の「前方向命令情報IDリスト」の各「命令情報ID」を「命令情報ID一時リスト」に非重複的に「追加」する。つまり、重複する場合、命令情報IDは「命令情報ID一時リスト」に追加しない。

「サブルーチン生存入力レジスタID一時リスト」で、「サブルーチン復帰アドレス」を格納する「リンクレジスタ」のレジスタID以外を「サブルーチン引数レジスタIDリスト」に書き込む。

次に、命令セットシミュレータプログラムソースコード出力部23におけるサブルーチン引数共通化処理部3eについて説明する。

サブルーチン引数共通化処理部3eは、サブルーチン引数抽出部1fの処理を、「シンボル情報リスト」に含まれるすべての「シンボル情報」について実行したのちに実行する(図42参照)。この処理は、「シンボル情報」の「データ依存サブルーチン呼出し命令フラグ」が「1」であるものが「シンボル情報リスト」に含まれる場合にのみ必要となる。この処理が必要な理由は、データ依存サブルーチンをプログラム記述で実現する場合に、全サブルーチンに「共通」の関数ポインタデータ型(引数の個数も共通化)が必要となるからである。

「シンボル情報リスト」に含まれるすべての「シンボル情報」について、その「サブルーチン引数レジスタIDリスト」に含まれるすべてのレジスタIDを「共通サブルーチン引数レジスタIDリスト」に非重複的に「追加」する。つまり、共通サブルーチン引数レジスタIDリストには、レジスタIDは重複して存在しない。

(1)CPUリソース参照マクロ定義:図14のCPUリソース参照マクロ定義は、CPUレジスタ変数がCPUリソースデータ構造体(図13参照)で定義されていることを前提としているが、「第2実施形態」では、CPUレジスタ変数はサブルーチン引数変数またはローカル変数として定義する。そこで、CPUリソース参照マクロを図46のように変更する。

A)サブルーチン「戻り値」:第1実施形態では戻り値のない(void型)関数であったが、第2実施形態ではCPUレジスタのデータ型の戻り値をとる関数にする。(32ビットCPUの場合U32型、64ビットCPUの場合U64型となる)

B)サブルーチン引数:「サブルーチン引数抽出部」及び(必要に応じて実行される)「サブルーチン引数共通化処理部3e(図43参照)で生成した「サブルーチン引数レジスタIDリスト」によりサブルーチン引数の個数を決定する。それぞれの引数のデータ型は「戻り値」と同様にCPUレジスタのデータ型と同じにする。また、引数名は、レジスタ番号やレジスタ別名(r[13]の別名sp等)を基に生成する。

図48に、第2実施形態のサブルーチン定義記述例を示す。ここでは、「サブルーチン引数共通化処理部3e」実行後もサブルーチン引数の個数が変化しないことを想定している。

A)サブルーチン引数引き渡し記述:「呼出し先シンボル情報」の「サブルーチン引数レジスタIDリスト」を取得し、引数変数またばローカル変数のレジスタを使って呼出しサブルーチンの引数引き渡し記述を生成する。

図50に第2実施形態のサブルーチン呼出しプログラム記述を示す。

図51に、第3実施形態の命令セットシミュレータを用いた組込みシステム用ソフトウエア開発環境を示す。

第3実施形態の命令セットシミュレータ3Sは、第1実施形態と第2実施形態とにおいて、シンボルテーブルがない場合の機械語命令解析部31を含むものである。

第1実施形態および第2実施形態では、実行バイナリファイルに「シンボルテーブル」が含まれていることを前提にしている。ここでは、「シンボルテーブル」が存在しない場合に対応するための第3実施形態について説明する。

第3実施形態では、第1・第2実施形態の機械語命令解析部1(21)と命令セットシミュレータプログラムソースコード出力部3とが、機械語命令解析部31、命令セットシミュレータプログラムソースコード出力部33に変更される。

(ア)機械語命令解析部31は、未解析シンボルアドレス検出部31aをもつ。

「シンボルテーブル」が存在しない場合、機械語命令の位置を特定する唯一の情報は「エントリーポイント」(プログラム起動後に最初に実行される命令アドレス)である。従って、まず、未解析シンボルアドレス検出部31aが「エントリーポイント」のみを「シンボルアドレス一時リスト」に追加する。

シンボル候補アドレスリスト31a1の初期状態は「空」であり、「未解析」のシンボルアドレスが見つかった場合に未解析シンボルアドレス検出部31aは、シンボル候補アドレスに追加する(後述)。この「シンボル候補アドレスリスト」の各アドレスを「シンボルアドレス一時リスト」に追加する。

「データ依存サブルーチン呼出し命令」による呼出し先アドレスに該当する「シンボル情報」がない(そのアドレスのシンボルが「未解析」であるということ)場合に、命令セットシミュレータを「強制終了」させる仕組みがある。

この特徴により、「未解析」シンボルが呼び出された時に、命令セットシミュレータを「異常終了」させる(exit(-1)。そして、更新された「シンボル候補アドレスリスト」を使って機械語命令解析部31、命令セットシミュレータプログラムソースコード出力部33を再度実行し、生成された命令セットシミュレータプログラムソースコード34を再度コンパイル・実行する。

また、第1実施形態と同様な作用効果を奏し、詳細動作の再現が可能で、シミュレータの処理速度が速い。

1.なお、前記した実施形態1〜3では、実行バイナリから逆コンパイルさせる高級プログラム言語としてC言語を例示したが、逆コンパイルさせる言語をC言語以外の高級プログラム言語に代替できるのは勿論である。

1d 次命令情報抽出部(サブルーチン検出手段、サブルーチン呼出し命令検出手段、分岐命令検出手段、単純分岐命令検出手段、単純サブルーチン呼出し命令検出手段、データ依存分岐命令検出手段、データ依存サブルーチン呼出し命令検出手段)

1e アドレスリスト更新部(サブルーチン検出手段、単純サブルーチン呼出し命令検出手段、データ依存サブルーチン呼出し命令検出手段)

1f サブルーチン引数抽出部(サブルーチン検出手段、レジスタ変数展開手段)

2 データ依存分岐情報抽出部(サブルーチン検出手段、分岐命令検出手段、データ依存分岐命令検出手段、データ依存サブルーチン呼出し命令検出手段、分岐先アドレス情報読出し部)

2f (サブルーチン機械語アドレステーブル生成手段、)

2g ジャンプテーブル情報生成部(ジャンプテーブル記録手段、サブルーチン機械語アドレステーブル生成手段)

3 命令セットシミュレータプログラムソースコード出力部(データ依存分岐命令生成手段)

3a サブルーチンプログラムソース生成部(サブルーチンソースコード出力手段、サブルーチン呼出し命令出力手段)

3a4 プログラムラベル記述生成部(識別子付加手段)

3a5 機械語命令種別判定部(無条件分岐命令出力手段)

3a6 単純分岐命令プログラム記述生成部(無条件分岐命令出力手段、サブルーチン呼出し命令出力手段)

3a7 単純サブルーチン呼出し命令プログラム記述生成部(サブルーチンソースコード出力手段、サブルーチン呼出し命令出力手段)

3a8 データ依存分岐命令プログラム記述生成部(無条件分岐命令出力手段、データ依存分岐命令生成手段、サブルーチン呼出し命令出力手段、データ依存サブルーチン呼出し命令生成手段)

3a9 データ依存サブルーチン呼出し命令プログラム記述生成部(サブルーチンソースコード出力手段、サブルーチン呼出し命令出力手段、サブルーチンアドレス検索処理命令生成手段)

3e サブルーチン引数共通化処理部(サブルーチンソースコード出力手段、レジスタ変数展開手段)

23 命令セットシミュレータプログラムソースコード出力部(データ依存分岐命令生成手段、レジスタ変数展開手段)

33 命令セットシミュレータプログラムソースコード出力部(サブルーチンソースコード出力手段)

r3 ジャンプテーブル情報リスト(ジャンプテーブル情報記憶部、機械語アドレステーブル)

S、2S、3S 命令セットシミュレータ

Claims (9)

- 機械語プログラムをプログラムソースコードに変換してシミュレータ実行プログラムが生成される命令セットシミュレータであって、

前記機械語プログラムに含まれるサブルーチンを検出するサブルーチン検出手段と、

前記機械語プログラムに含まれる命令語のうち分岐先アドレスを有する分岐命令を検出する分岐命令検出手段と、

前記機械語プログラムに含まれる命令語のうちサブルーチン呼出し先アドレスを有するサブルーチン呼出し命令を検出するサブルーチン呼出し命令検出手段と、

前記機械語プログラムを前記サブルーチン検出手段で検出した各サブルーチン単位のプログラムソースコードを出力するサブルーチンソースコード出力手段と、

前記分岐先アドレスを示す識別子を前記プログラムソースコードの分岐先の命令に付加する識別子付加手段と、

前記機械語プログラムの前記分岐命令を、前記プログラムソースコードの前記識別子をもつ命令への無条件分岐命令にして出力する無条件分岐命令出力手段と、

前記機械語プログラムのサブルーチン呼出し命令を、前記プログラムソースコードのサブルーチン呼出し命令にして出力するサブルーチン呼出し命令出力手段と、

を備え、

前記分岐命令検出手段は、

前記機械語プログラムに含まれる命令語のうち分岐先アドレスが特定できる単純分岐命令を検出する単純分岐命令検出手段と、

前記機械語プログラムに含まれる分岐先アドレスがレジスタ値またはメモリ値で決定されるデータ依存分岐命令を検出するデータ依存分岐命令検出手段と、

を有し、

前記機械語プログラムの前記データ依存分岐命令の分岐先アドレスを、ジャンプテーブル情報記憶部に記録するジャンプテーブル記録手段と、

前記ジャンプテーブル情報記憶部から、前記データ依存分岐命令のアドレスを基に、該当するジャンプテーブル情報を検索し、検索されたジャンプテーブル情報を用いて、前記プログラムソースコードの前記無条件分岐命令を生成するデータ依存分岐命令生成手段と、

をさらに備えることを特徴とする命令セットシミュレータ。 - 機械語プログラムをプログラムソースコードに変換してシミュレータ実行プログラムが生成される命令セットシミュレータであって、

前記機械語プログラムに含まれるサブルーチンを検出するサブルーチン検出手段と、

前記機械語プログラムに含まれる命令語のうち分岐先アドレスを有する分岐命令を検出する分岐命令検出手段と、

前記機械語プログラムに含まれる命令語のうちサブルーチン呼出し先アドレスを有するサブルーチン呼出し命令を検出するサブルーチン呼出し命令検出手段と、

前記機械語プログラムを前記サブルーチン検出手段で検出した各サブルーチン単位のプログラムソースコードを出力するサブルーチンソースコード出力手段と、

前記分岐先アドレスを示す識別子を前記プログラムソースコードの分岐先の命令に付加する識別子付加手段と、

前記機械語プログラムの前記分岐命令を、前記プログラムソースコードの前記識別子をもつ命令への無条件分岐命令にして出力する無条件分岐命令出力手段と、

前記機械語プログラムのサブルーチン呼出し命令を、前記プログラムソースコードのサブルーチン呼出し命令にして出力するサブルーチン呼出し命令出力手段と、

を備え、

前記サブルーチン呼出し命令検出手段は、

前記機械語プログラムに含まれる命令語のうち呼出し先アドレスが特定できる単純サブルーチン呼出し命令を検出する単純サブルーチン呼出し命令検出手段と、

前記機械語プログラムに含まれる呼出し先アドレスがレジスタ値またはメモリ値で決定されるデータ依存サブルーチン呼出し命令を検出するデータ依存サブルーチン呼出し命令検出手段と、

を有し、

サブルーチン名とサブルーチン機械語アドレスを対とした情報に関するサブルーチン機械語アドレステーブルを生成するサブルーチン機械語アドレステーブル生成手段と、

サブルーチン機械語アドレスから前記プログラムソースコード上のサブルーチンを検索して前記プログラムソースコード上のサブルーチンアドレスを取得するサブルーチンアドレス検索処理のプログラムを生成するサブルーチンアドレス検索処理命令生成手段と、

前記サブルーチンアドレス検索処理の命令によって前記プログラムソースコードのデータ依存サブルーチン呼出し命令の呼出し先サブルーチンを特定して、これを呼び出す処理を行うデータ依存サブルーチン呼出し命令生成手段と、

をさらに備えることを特徴とする命令セットシミュレータ。 - 請求項2に記載の命令セットシミュレータにおいて、機械語プログラムにシンボル情報が欠如しているがために、前記サブルーチン検出手段においてすべてのサブルーチンを検出できない場合に対処する手段として、

前記シミュレータ実行プログラムの実行において前記サブルーチン機械語アドレステーブルに登録されていない機械語アドレスがデータ依存サブルーチン命令によって呼び出された場合には、当該未登録機械語アドレスを記録した後に、前記シミュレータ実行プログラムを強制終了させる未登録機械語アドレス検出手段と、

未登録機械語アドレスのサブルーチンについて、前記手段によりプログラムソースコードを追加生成する未登録サブルーチンプログラムソースコード生成手段とを、

備えることを特徴とする命令セットシミュレータ。 - 請求項1から請求項3のうちの何れか一項に記載の命令セットシミュレータにおいて、

前記機械語プログラムのレジスタ値を、前記プログラムソースコード上のサブルーチン引数変数またはローカル変数として記述するレジスタ変数展開手段を備える

ことを特徴とする命令セットシミュレータ。 - 請求項1から請求項4のうちの何れか一項に記載の命令セットシミュレータにおいて、

前記プログラムソースコードは、C言語のプログラムであり、プログラムカウンタに関するswitch文と各命令アドレスに関するcase文のコード構造を用いずに、プログラムソースコード上の識別子を持つ命令への無条件分岐命令とサブルーチン呼出し命令が用いられていて、前記機械語プログラムのサブルーチンと前記プログラムソースコードのサブルーチンとが対応しており、前記機械語プログラムにおけるサブルーチンの階層が前記プログラムソースコードにおけるサブルーチンの階層に復元され、

前記シミュレータ実行プログラムは、前記プログラムソースコードがコンパイルされることによって生成される

ことを特徴とする命令セットシミュレータ。 - 機械語プログラムをプログラムソースコードに変換してシミュレータ実行プログラムが生成される命令セットシミュレータのシミュレータ実行プログラム生成方法であって、

前記命令セットシミュレータは、サブルーチン検出手段と分岐命令検出手段とサブルーチン呼出し命令検出手段とサブルーチンソースコード出力手段と識別子付加手段と無条件分岐命令出力手段とサブルーチン呼出し命令出力手段とを備え、

前記サブルーチン検出手段は、前記機械語プログラムに含まれるサブルーチンを検出し、

前記分岐命令検出手段は、前記機械語プログラムに含まれる命令語のうち分岐先アドレスを有する分岐命令を検出し、

前記サブルーチン呼出し命令検出手段は、前記機械語プログラムに含まれる命令語のうちサブルーチン呼出し先アドレスを有するサブルーチン呼出し命令を検出し、

前記サブルーチンソースコード出力手段は、前記機械語プログラムを前記サブルーチン検出手段で検出した各サブルーチン単位のプログラムソースコードを出力し、

前記識別子付加手段は、前記分岐先アドレスを示す識別子を前記プログラムソースコードの分岐先の命令に付加するとともに、前記無条件分岐命令出力手段は、前記機械語プログラムの前記分岐命令を、前記プログラムソースコードの前記識別子をもつ命令への無条件分岐命令にして出力し、

前記サブルーチン呼出し命令出力手段は、前記機械語プログラムのサブルーチン呼出し命令を、前記プログラムソースコードのサブルーチン呼出し命令にして出力し、

前記命令セットシミュレータは、ジャンプテーブル記録手段とデータ依存分岐命令生成手段とを備え、

前記ジャンプテーブル記録手段は、前記機械語プログラムに含まれる分岐先アドレスがレジスタ値またはメモリ値で決定されるデータ依存分岐命令の分岐先アドレスを、ジャンプテーブル情報記憶部に記録し、

前記データ依存分岐命令生成手段は、前記ジャンプテーブル情報記憶部から、前記データ依存分岐命令のアドレスを基に、該当するジャンプテーブル情報を検索し、検索されたジャンプテーブル情報を用いて、前記プログラムソースコードの前記無条件分岐命令を生成する

ことを特徴とする命令セットシミュレータのシミュレータ実行プログラム生成方法。 - 機械語プログラムをプログラムソースコードに変換してシミュレータ実行プログラムが生成される命令セットシミュレータのシミュレータ実行プログラム生成方法であって、

前記命令セットシミュレータは、サブルーチン検出手段と分岐命令検出手段とサブルーチン呼出し命令検出手段とサブルーチンソースコード出力手段と識別子付加手段と無条件分岐命令出力手段とサブルーチン呼出し命令出力手段とを備え、

前記サブルーチン検出手段は、前記機械語プログラムに含まれるサブルーチンを検出し、

前記分岐命令検出手段は、前記機械語プログラムに含まれる命令語のうち分岐先アドレスを有する分岐命令を検出し、

前記サブルーチン呼出し命令検出手段は、前記機械語プログラムに含まれる命令語のうちサブルーチン呼出し先アドレスを有するサブルーチン呼出し命令を検出し、

前記サブルーチンソースコード出力手段は、前記機械語プログラムを前記サブルーチン検出手段で検出した各サブルーチン単位のプログラムソースコードを出力し、

前記識別子付加手段は、前記分岐先アドレスを示す識別子を前記プログラムソースコードの分岐先の命令に付加するとともに、前記無条件分岐命令出力手段は、前記機械語プログラムの前記分岐命令を、前記プログラムソースコードの前記識別子をもつ命令への無条件分岐命令にして出力し、

前記サブルーチン呼出し命令出力手段は、前記機械語プログラムのサブルーチン呼出し命令を、前記プログラムソースコードのサブルーチン呼出し命令にして出力し、

前記命令セットシミュレータは、サブルーチン機械語アドレステーブル生成手段とサブルーチンアドレス検索処理命令生成手段とデータ依存サブルーチン呼出し命令生成手段とを備え、

前記サブルーチン機械語アドレステーブル生成手段は、サブルーチン名とサブルーチン機械語アドレスを対とした情報に関するサブルーチン機械語アドレステーブルを生成し、

前記サブルーチンアドレス検索処理命令生成手段は、サブルーチン機械語アドレスから前記プログラムソースコード上のサブルーチンを検索して前記プログラムソースコード上のサブルーチンアドレスを取得するサブルーチンアドレス検索処理のプログラムを生成し、

前記データ依存サブルーチン呼出し命令生成手段は、前記サブルーチンアドレス検索処理の命令によって前記プログラムソースコードのデータ依存サブルーチン呼出し命令の呼出し先サブルーチンを特定して、これを呼び出す処理を行う

ことを特徴とする命令セットシミュレータのシミュレータ実行プログラム生成方法。 - 請求項7に記載の命令セットシミュレータのシミュレータ実行プログラム生成方法において、

前記命令セットシミュレータは、未登録機械語アドレス検出手段と未登録サブルーチンプログラムソースコード生成手段とを備え、

前記未登録機械語アドレス検出手段は、前記シミュレータ実行プログラムの実行において前記サブルーチン機械語アドレステーブルに登録されていない機械語アドレスがデータ依存サブルーチン命令によって呼び出された場合には、当該未登録機械語アドレスを記録した後に、前記シミュレータ実行プログラムを強制終了させる機能を有し、

前記未登録サブルーチンプログラムソースコード生成手段は、未登録機械語アドレスのサブルーチンについて、前記手段によりプログラムソースコードを追加生成する

ことを特徴とする命令セットシミュレータのシミュレータ実行プログラム生成方法。 - 請求項6から請求項8のうちの何れか一項に記載の命令セットシミュレータのシミュレータ実行プログラム生成方法において、

前記命令セットシミュレータは、レジスタ変数展開手段を備え、

前記レジスタ変数展開手段は、前記機械語プログラムのレジスタ値を、前記プログラムソースコード上のサブルーチン引数変数またはローカル変数として記述する

ことを特徴とする命令セットシミュレータのシミュレータ実行プログラム生成方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015145452A JP6418696B2 (ja) | 2015-07-23 | 2015-07-23 | 命令セットシミュレータおよびそのシミュレータ生成方法 |

| PCT/JP2016/071632 WO2017014318A1 (ja) | 2015-07-23 | 2016-07-22 | 命令セットシミュレータおよびそのシミュレータ生成方法 |

| CN201680055109.2A CN108027748B (zh) | 2015-07-23 | 2016-07-22 | 指令集模拟器及其模拟器生成方法 |

| US15/877,397 US10459707B2 (en) | 2015-07-23 | 2018-01-23 | Instruction-set simulator and its simulator generation method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015145452A JP6418696B2 (ja) | 2015-07-23 | 2015-07-23 | 命令セットシミュレータおよびそのシミュレータ生成方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017027375A JP2017027375A (ja) | 2017-02-02 |

| JP2017027375A5 JP2017027375A5 (ja) | 2018-08-16 |

| JP6418696B2 true JP6418696B2 (ja) | 2018-11-07 |

Family

ID=57834504

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015145452A Active JP6418696B2 (ja) | 2015-07-23 | 2015-07-23 | 命令セットシミュレータおよびそのシミュレータ生成方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US10459707B2 (ja) |

| JP (1) | JP6418696B2 (ja) |

| CN (1) | CN108027748B (ja) |

| WO (1) | WO2017014318A1 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013242700A (ja) * | 2012-05-21 | 2013-12-05 | Internatl Business Mach Corp <Ibm> | コード最適化方法、プログラム及びシステム |

| US10884720B2 (en) | 2018-10-04 | 2021-01-05 | Microsoft Technology Licensing, Llc | Memory ordering annotations for binary emulation |

| US10684835B1 (en) * | 2018-12-11 | 2020-06-16 | Microsoft Technology Licensing, Llc | Improving emulation and tracing performance using compiler-generated emulation optimization metadata |

| US20200183661A1 (en) * | 2018-12-11 | 2020-06-11 | GM Global Technology Operations LLC | Method and apparatus for cross-execution of binary embedded software |

| CN110309655B (zh) * | 2019-07-05 | 2021-08-17 | 武汉绿色网络信息服务有限责任公司 | 一种检测app更新过程中安全性的方法以及检测装置 |

| CN110659032B (zh) * | 2019-09-24 | 2023-08-22 | 网易(杭州)网络有限公司 | 游戏应用的指令执行方法、装置、终端设备和存储介质 |

| US11900136B2 (en) | 2021-07-28 | 2024-02-13 | Sony Interactive Entertainment LLC | AoT compiler for a legacy game |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH096646A (ja) * | 1995-06-14 | 1997-01-10 | Oki Electric Ind Co Ltd | プログラムシミュレーション装置 |

| JPH1083311A (ja) * | 1996-09-06 | 1998-03-31 | Mitsubishi Electric Corp | シミュレータ |

| JP3495230B2 (ja) * | 1997-06-30 | 2004-02-09 | Necマイクロシステム株式会社 | エミュレーション処理方式 |

| JP2001515240A (ja) * | 1997-09-01 | 2001-09-18 | フジツウ シーメンス コンピューターズ ゲゼルシャフト ミット ベシュレンクテル ハフツング | オブジェクトコードからプログラムコードへの変換方法 |

| AU1809599A (en) * | 1997-12-11 | 1999-06-28 | Digits Corp. | Object code analysis and remediation system and method |

| JP3956131B2 (ja) * | 2002-12-26 | 2007-08-08 | インターナショナル・ビジネス・マシーンズ・コーポレーション | プログラム変換装置、プログラム変換方法及びプログラム |

| US7356672B2 (en) * | 2004-05-28 | 2008-04-08 | The Regents Of The University Of California | Warp processor for dynamic hardware/software partitioning |

| US8621444B2 (en) * | 2004-06-01 | 2013-12-31 | The Regents Of The University Of California | Retargetable instruction set simulators |

| US8056138B2 (en) * | 2005-02-26 | 2011-11-08 | International Business Machines Corporation | System, method, and service for detecting improper manipulation of an application |

| CN101216775A (zh) * | 2008-01-03 | 2008-07-09 | 北京深思洛克数据保护中心 | 一种软件程序的保护方法、装置及系统 |

| US20100274755A1 (en) * | 2009-04-28 | 2010-10-28 | Stewart Richard Alan | Binary software binary image analysis |

| US8510723B2 (en) * | 2009-05-29 | 2013-08-13 | University Of Maryland | Binary rewriting without relocation information |

| JP5542643B2 (ja) * | 2010-12-10 | 2014-07-09 | 三菱電機株式会社 | シミュレーション装置及びシミュレーションプログラム |

| US8726255B2 (en) * | 2012-05-01 | 2014-05-13 | Concurix Corporation | Recompiling with generic to specific replacement |

| KR102147355B1 (ko) * | 2013-09-27 | 2020-08-24 | 삼성전자 주식회사 | 프로그램 변환 방법 및 장치 |

| US20180211046A1 (en) * | 2017-01-26 | 2018-07-26 | Intel Corporation | Analysis and control of code flow and data flow |

-

2015

- 2015-07-23 JP JP2015145452A patent/JP6418696B2/ja active Active

-

2016

- 2016-07-22 CN CN201680055109.2A patent/CN108027748B/zh active Active

- 2016-07-22 WO PCT/JP2016/071632 patent/WO2017014318A1/ja active Application Filing

-

2018

- 2018-01-23 US US15/877,397 patent/US10459707B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US10459707B2 (en) | 2019-10-29 |

| US20180165079A1 (en) | 2018-06-14 |

| WO2017014318A1 (ja) | 2017-01-26 |

| JP2017027375A (ja) | 2017-02-02 |

| CN108027748A (zh) | 2018-05-11 |

| CN108027748B (zh) | 2019-09-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6418696B2 (ja) | 命令セットシミュレータおよびそのシミュレータ生成方法 | |

| US7712092B2 (en) | Binary translation using peephole translation rules | |

| US7536682B2 (en) | Method and apparatus for performing interpreter optimizations during program code conversion | |

| Bansal et al. | Binary Translation Using Peephole Superoptimizers. | |

| Wang et al. | Uroboros: Instrumenting stripped binaries with static reassembling | |

| JP4699580B2 (ja) | データ処理システムの配列の静的初期化方法、データ処理方法、並びにデータ処理システム及びその制御手順をコンピュータに実行させるプログラムを記憶したコンピュータ読み取り可能な記憶媒体 | |

| CN110245467B (zh) | 基于Dex2C与LLVM的Android应用程序保护方法 | |

| US20030088860A1 (en) | Compiler annotation for binary translation tools | |

| US20040255279A1 (en) | Block translation optimizations for program code conversation | |

| WO2004095263A2 (en) | Partial dead code elimination optimizations for program code conversion | |

| CN105446704A (zh) | 一种着色器的解析方法和装置 | |

| Liu | Android native development kit cookbook | |

| CN112379917A (zh) | 浏览器兼容性提升方法、装置、设备及存储介质 | |

| CN113535184A (zh) | 一种跨平台的代码转换方法及设备 | |

| US20040221279A1 (en) | Method and apparatus for performing lazy byteswapping optimizations during program code conversion | |

| Sato et al. | ExanaDBT: A dynamic compilation system for transparent polyhedral optimizations at runtime | |

| Sarda et al. | LLVM essentials | |

| US8869109B2 (en) | Disassembling an executable binary | |

| Bouraqadi et al. | Test-driven development for generated portable Javascript apps | |

| CN115480871B (zh) | 一种通用的tms320c3x处理器指令集虚拟化仿真方法 | |

| US20230113783A1 (en) | Cross-platform code conversion method and device | |

| US7120905B2 (en) | System and method for transformation of assembly code for conditional execution | |

| CN114816435A (zh) | 一种基于逆向技术的软件开发方法 | |

| Bezzubikov et al. | Automatic dynamic binary translator generation from instruction set description | |

| CN114610364A (zh) | 应用程序更新、应用程序开发方法、装置及计算机设备 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20180122 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20180118 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20180122 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180703 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180703 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20180703 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20180709 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180731 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180913 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180925 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20181005 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6418696 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |