JP6256133B2 - ストレージ装置,キャッシュ制御方法及びキャッシュ制御プログラム - Google Patents

ストレージ装置,キャッシュ制御方法及びキャッシュ制御プログラム Download PDFInfo

- Publication number

- JP6256133B2 JP6256133B2 JP2014055034A JP2014055034A JP6256133B2 JP 6256133 B2 JP6256133 B2 JP 6256133B2 JP 2014055034 A JP2014055034 A JP 2014055034A JP 2014055034 A JP2014055034 A JP 2014055034A JP 6256133 B2 JP6256133 B2 JP 6256133B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- storage device

- cache

- storage

- history

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/12—Replacement control

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0804—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches with main memory updating

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0866—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches for peripheral storage systems, e.g. disk cache

- G06F12/0871—Allocation or management of cache space

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/12—Replacement control

- G06F12/121—Replacement control using replacement algorithms

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/12—Replacement control

- G06F12/121—Replacement control using replacement algorithms

- G06F12/123—Replacement control using replacement algorithms with age lists, e.g. queue, most recently used [MRU] list or least recently used [LRU] list

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/10—Providing a specific technical effect

- G06F2212/1041—Resource optimization

- G06F2212/1044—Space efficiency improvement

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/31—Providing disk cache in a specific location of a storage system

- G06F2212/311—In host system

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Memory System Of A Hierarchy Structure (AREA)

- Information Retrieval, Db Structures And Fs Structures Therefor (AREA)

Description

その中で問題になりつつあるのがTOC(Total Cost of Ownership;総所有コスト)である。例えば、総容量1EBのシステムを組もうとした場合に、1TB(テラバイト)のSAS(Serial Attached SCSI(Small Computer System Interface))ドライブを用いると1,000,000台ものドライブが必要であり電力費用だけで毎月数千万円かかることになる。

このようなストレージ装置の消費電力量を低減するための手法として、ライトオフローディング(Write Off-Loading)と呼ばれる手法が知られている。

すなわち、書き戻し元のドライブにおいては、書き戻しを行なった直後においては、キャッシュにはオフロードしていたデータサイズ分だけ価値のないデータを格納している状態と言える。従って、従来のストレージシステムにおいては、オフロードデータの書き戻し後において、キャッシュ領域を効率的に用いることができないという課題がある。

なお、前記目的に限らず、後述する発明を実施するための形態に示す各構成により導かれる作用効果であって、従来の技術によっては得られない作用効果を奏することも本発明の他の目的の1つとして位置付けることができる。

本実施形態のストレージシステム1は、図示しない1つ以上の上位装置に接続され、この上位装置に対して記憶領域を提供するものである。なお、上位装置は、例えば、サーバ機能をそなえたコンピュータ(情報処理装置)である。

本ストレージシステム1は、図1に示すように、ストレージサーバ2及び複数(図1に示す例では2つ)の記憶装置30,40を備える。

ストレージサーバ2は、サーバ機能を備えるコンピュータ(情報処理装置)であり、例えば、上位装置からの要求に従い、記憶装置30,40へのデータの書き込みや読み出しを制御する。ストレージサーバ2は、例えば、IA(Intel Architecture)サーバである。

ディスプレイ205は種々の情報を表示する表示装置であり、例えば、液晶ディスプレイ装置やCRT(Cathode Ray Tube)ディスプレイ装置である。

マウス207及びキーボード206はオペレータが種々の入力を行なうために操作する入力装置である。

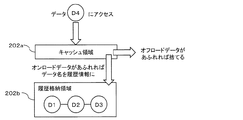

また、メモリ202のRAMは、一次記憶メモリあるいはワーキングメモリとして利用される。このメモリ202のRAMは、種々のデータやプログラムを一時的に格納する記憶装置であり、キャッシュ領域202a,履歴格納領域202b及び図示しないメモリ領域をそなえる。

なお、記憶装置30,40間でデータの移動を行なう際には、キャッシュ領域202aには、この移動されるデータを一時的に格納してもよい。この場合、例えば、記憶装置30から記憶装置40へデータを移動させる場合には、記憶装置30から読み出されたデータが、一旦、キャッシュ領域202aに格納される。そして、その後、このキャッシュ領域202aに格納されたデータが記憶装置40に格納される。このような記憶装置30から記憶装置40へのデータの移動は、後述するオフロードデータの書き戻し処理において行なわれる。

履歴格納領域(押し出し履歴格納部)202bには、後述するオンロードデータ(第2データ)がキャッシュ領域202aから押し出された場合に、この押し出されたオンロードデータに関する情報(例えば、データ名)が押し出し履歴として格納される。

すなわち、CPU201が、キャッシュ制御プログラムを実行することにより、キャッシュ制御部211として機能する。

キャッシュ制御部(メモリ制御部)211は、メモリ202へのデータの書き込みや読み出しを制御する。このキャッシュ制御部211は、図1に示すように、オンロードデータ判定部21,履歴サイズ調節部22,履歴管理部23,載せ直し処理部24,キャッシュ処理部25及びオフロード処理部26としての機能を備える。

そして、ライトオフローディング機能においては、電源オフだった本来の書き込み先の記憶装置が電源オンになると、オフロードしていたデータをこの記憶装置に書き込む(書き戻す)。

この電源オフ状態の記憶装置40に対する書き込み要求が行なわれると、オフロード処理部26は、この記憶装置40が書き込み先であるデータ(第1データ)を、記憶装置40の代わりに、電源オン状態の他の記憶装置(第1の記憶装置)30に一旦書き込む。

その後、電源オフ状態であった本来の書き込み先の記憶装置40が電源オンになると、オフロード処理部26は、記憶装置30にオフロードしていたデータを記憶装置40に書き戻す。

このように、ライトオフローディング機能によれば、電源オフ状態の記憶装置40への書き込みが要求されたとしても記憶装置40を起こす必要がなく、消費電力を削減することができる。なお、このライトオフローディングは既知の技術であり、その詳細な説明は省略する。

ここで、例えば、オフロード処理部26による書き戻しが始まった時点で、すでにオフロードデータがキャッシュ領域202aに載っている場合が考えられる。例えば、書き戻しが始まる少し前にオフロード先に書き込みがあり、そのデータに対してアクセスが発生すると、キャッシュ処理部25は、このオフロードデータをキャッシュ領域202aに格納する。

履歴管理部(押し出し履歴処理部)23は、メモリ202のキャッシュ領域202aから押し出されたオンロードデータを管理するものであり、このキャッシュ領域202aから押し出されたオンロードデータに関する情報をメモリ202の履歴格納領域202bに格納する。オンロードデータに関する情報とは、オンロードデータを特定する情報であり、例えばデータ名や識別番号である。以下、オンロードデータに関する情報としてデータ名を用いる例について示す。例えば、履歴格納領域202bは、オンロードデータのデータ名を格納する可変サイズのリスト構造を有する。

履歴格納領域202bにオンロードデータのデータ名が追加されるのは、データにアクセスがあったがキャッシュミスが発生してキャッシュ領域202aからあふれてしまい結果としてオンロードデータが追い出されてしまった場合である。あふれたオンロードデータのデータ名は履歴格納領域202bのリスト構造の最後尾に追加される。

以下、履歴格納領域202bに格納されたデータ名を履歴情報という場合がある。

図2は実施形態の一例としてのストレージシステムにおける履歴管理部23の処理を説明するための図である。この図2に示す例においては、キャッシュ領域202aは空きがない状態(キャッシュフル)であり、また、この直前の状態では履歴格納領域202bにデータ名D1,D2が格納されているものとする。

この際、データD4をキャッシュ領域202aに格納することにより、代わりにキャッシュ領域202aからデータ名D3のデータが追い出されるものとする。この追い出されたデータがオンロードデータである場合に、履歴管理部23は、このキャッシュ領域202aから追い出されたオンロードデータのデータ名“D3”を履歴格納領域202bに格納する。

履歴管理部23は、上位装置からのリード要求受信時に、キャッシュ領域202aにおいてキャッシュミスが生じた場合に、そのリード要求に基づいて履歴格納領域202bを検索する。すなわち、押し出し履歴処理部23は、履歴格納領域202bに格納されているデータ名に対して受信したリード要求の対象(リード対象)であるデータ名を検索する。

また、履歴格納領域202bが一杯になった場合には、履歴格納領域202bに格納されてから最も長い時間が経ったものから順番に、履歴格納領域202bから押し出される。つまり、載せ直し処理部24は、LRUアルゴリズムをキャッシュ置換アルゴリズムとして用いて履歴格納領域202bからデータ名を押し出す。

載せ直し処理部24は、キャッシュ領域202aに空きが生じると、履歴格納領域202bから、格納されてから経過した時間が最も短い(最後尾の)データ名を読み出し、記憶装置30から、このデータ名によって特定されるオンロードデータを読み出す。そして、載せ直し処理部24は、読み出したオンロードデータをキャッシュ領域202aに載せ直す。

そして、以下、載せ直し処理部24は、キャッシュ領域202aが満杯になるまで、履歴格納領域202bからのデータ名の読み出しと、このデータ名で特定されるオンロードデータの記憶装置30からの読み出し及びキャッシュ領域202aへの格納とを繰り返し行なう。

上述した載せ直し処理は、キャッシュ領域202aにおいて、オフロードデータの削除により空いた領域が、ユーザからのアクセスのキャッシュミスによるデータの追加と、履歴格納領域202bからの載せ直し機能によるデータの追加とによって満杯になったら停止される。

履歴サイズ調節部22は、履歴格納領域202b内のオンロードデータのデータ名の数が、キャッシュ領域202a内におけるオフロードデータの数に一致するように制御する。キャッシュ領域202aへのデータの格納及び読出は所定サイズ単位で行なわれことを前提とするものである。

なお、この履歴サイズ調節部22による履歴格納領域202bのサイズ調節処理手法の詳細は、図6〜図8を用いて後述する。

キャッシュ処理部25は、例えば、ユーザから入力されるデータの読み書き処理要求に対して、記憶装置30から読み出したデータや記憶装置30に書き込むデータを、キャッシュ領域202aに格納する制御を行なう。また、これに伴い、キャッシュ処理部25は、キャッシュ置換アルゴリズムによりキャッシュ領域202aからデータを追い出す制御を行なう。

オンロードデータ判定部21は、キャッシュ処理部25がキャッシュ領域202aにデータを格納する代わりにキャッシュ領域202aから追い出されたデータがオンロードデータであるかオフロードデータであるかを判断する。

載せ直し処理部24は、キャッシュ領域202aに空き領域が生じると、履歴格納領域202bから、格納されてから経過した時間が最も短いデータ名を読み出し、記憶装置30から、このデータ名によって特定されるオンロードデータを読み出す。そして、載せ直し処理部24は、読み出したオンロードデータをキャッシュ領域202aに載せ直す。すなわち、オンロードデータの載せ直し処理を行なう。

上述の如く構成された、実施形態の一例としてのストレージシステム1におけるユーザからI/Oアクセスがあった場合のキャッシュ処理の概要を、図5に示すフローチャート(ステップA1〜A7)に従って説明する。

I/O要求されたデータのデータ名が履歴格納領域202bに格納されていない(ヒットしない)場合には(ステップA2のNoルート参照)、ステップA4に移行する。

キャッシュ領域202aにおいてキャッシュミスが生じた場合に、キャッシュ領域202aがいっぱいである場合には、新たに記憶装置30から読み出されたデータをキャッシュ領域202aに格納することにより、キャッシュ領域202aからあふれるデータが生じる。

一方、キャッシュ領域202aからあふれたデータがある場合には(ステップA4のYesルート参照)、ステップA5において、オンロードデータ判定部21が、あふれたデータがオンロードデータであるか否かを判断する。

キャッシュ領域202aにおいてキャッシュミスが発生し、その後のI/O要求に応じてキャッシュ領域202aにデータの格納が行なわれた場合に、履歴サイズ調節部22は、図7に例示する算出アルゴリズムを用いて変数「許容サイズ」の値を変更する(ステップB1)。

履歴サイズ調節部22は、キャッシュ処理部25から取得したキャッシュ領域202aへの入出力の結果に基づき、上述した算出アルゴリズムを適用することで、許容サイズの変更を行なう。

ステップB2において、サイズ調節機能が停止状態であるか否かを確認する。具体的には、履歴サイズ調節部22は、後述するサイズ調整機能の停止状態を示す情報(例えばフラグ)が設定されているか否かを確認する。

一方、サイズ調整機能の停止状態が解除されている場合には(ステップB2のNoルート参照)、ステップB3において、履歴サイズ調節部22は、履歴格納領域202bに格納されるオフロードデータのデータ名の数、すなわち、履歴サイズと許容サイズの値とを比較する。

次に、図6のステップB2に示したサイズ調整機能の停止状態の設定方法を、図8に示すフローチャート(ステップC1〜C4)を用いて説明する。

本ストレージシステム1の起動時等の動作開始時においては、初期状態として、変数「許容サイズ」の値には0が設定され、また、サイズ調節機能の停止状態が設定される。

この確認の結果、オフロードデータの書き戻しが行なわれていない場合には(ステップC1のNoルート参照)、ステップC1に戻り、書き戻しが行なわれるまでステップC1の確認処理が繰り返し実行される。

その後、ステップC3において、履歴サイズ調節部22は、載せ直し処理部24によるキャッシュ領域202aへのオンロードデータの載せ直し処理が完了したか否かを確認する。この載せ直し処理部24による載せ直し処理が完了していない場合には(ステップC3のNoルート参照)ステップC3に戻り、載せ直し処理が完了するまで、ステップC3の確認処理が繰り返し行なわれる。

従って、サイズ調整停止状態は、載せ直し処理部24によるキャッシュ領域202aへのオンロードデータの載せ直し処理が実行されている状態を表すと言える。

次に、実施形態の一例としてのストレージシステム1の載せ直し処理部24によるオンロードデータのキャッシュ領域202aへの載せ直し処理を、図9に示すフローチャート(ステップD11〜D13)を用いて説明する。

ステップD11において、載せ直し処理部24は、メモリ202のキャッシュ領域202aがいっぱいであるか否かを確認する。キャッシュ領域202aに空きがある場合には(ステップD11のNoルート参照)、ステップD12において、載せ直し処理部24は、履歴格納領域202bが空であるか否かを確認する。

このように、実施形態の一例としてのストレージシステム1によれば、キャッシュ領域202aのオフロードデータをオフロード処理部26が記憶装置40に書き戻すことにより当該キャッシュ領域202aに生じた空き領域に、載せ直し処理部24がオンロードデータを格納する。これにより、キャッシュ領域202aを有効に用いることができる。

キャッシュ領域202aからあふれたデータがオンロードデータである場合には、このオンロードデータを将来キャッシュ領域202aに載せ直す可能性があると考えられ、履歴格納領域202bを検索することで、このオンロードデータへのアクセスを高速に行なうことができる。

また、具体的には、履歴サイズ調節部22が、キャッシュ領域202a内におけるオフロードデータの数に合わせて履歴格納領域202bのサイズ調節を行なう。具体的には、履歴サイズ調節部22は、履歴格納領域202bのサイズ(格納するデータ名の数)をキャッシュ領域202a内におけるオフロードデータの数に一致させるように調節する。これにより、履歴格納領域202bのサイズを必要最小限に抑えることができ、メモリ202を有効に利用することができる。

また、上述した開示により本実施形態を当業者によって実施・製造することが可能である。

(付記1)

データを格納する第1の記憶装置と、

第2の記憶装置の電源断状態において、書き込み先が当該第2の記憶装置である第1データを前記第1の記憶装置に記録し、前記第2の記憶装置の電源投入後に、前記第1の記憶装置に記録された前記第1データを前記第2の記憶装置に移動させる代理格納処理部と、

前記代理格納処理部が前記第1の記憶装置に記録された前記第1データを前記第2の記憶装置に格納させた後に、キャッシュメモリから前記第1データを削除するキャッシュ解放部と

を備えることを特徴とする、ストレージ装置。

書き込み先が前記第1の記憶装置である第2データが前記キャッシュメモリから押し出された場合に、当該押し出された第2データに関する情報を押し出し履歴格納部に格納する押し出し履歴処理部と、

前記キャッシュメモリに空き領域が生じると、前記押し出し履歴格納部から前記押し出された前記第2データに関する情報を読み出し、当該第2データに関する情報に基づいて前記第1の記憶装置から読み出した第2データを、前記キャッシュメモリに格納する載せ直し処理部と

を備えることを特徴とする、付記1記載のストレージ装置。

前記キャッシュメモリにおける前記第1データのサイズに応じて、前記押し出し履歴格納部の格納領域サイズを変更する押し出し履歴格納領域調節部をそなえることを特徴とする、付記2記載のストレージ装置。

(付記4)

前記押し出し履歴処理部が、リード要求受信時に前記キャッシュメモリにおいてキャッシュミスが生じた場合に、前記リード要求に基づいて前記押し出し履歴格納部を検索し、当該押し出し履歴格納部において前記リード要求にかかる前記第2データに関する情報が検出された場合には、当該押し出し履歴格納部から当該第2データに関する情報を削除する

ことを特徴とする、付記2又は3記載のストレージ装置。

第2の記憶装置の電源断状態において、書き込み先が当該第2の記憶装置である第1データを第1の記憶装置に記録し、前記第2の記憶装置の電源投入後に、前記第1の記憶装置に記録された前記第1データを前記第2の記憶装置に移動させる処理と、

前記第1の記憶装置に記録された前記第1データを前記第2の記憶装置に格納させた後に、キャッシュメモリから前記第1データを削除する処理と

を備えることを特徴とする、キャッシュ制御方法。

書き込み先が前記第1の記憶装置である第2データが前記キャッシュメモリから押し出された場合に、当該押し出された第2データに関する情報を押し出し履歴格納部に格納する処理と、

前記キャッシュメモリに空き領域が生じると、前記押し出し履歴格納部から前記押し出された前記第2データに関する情報を読み出し、当該第2データに関する情報に基づいて前記第1の記憶装置から読み出した第2データを、前記キャッシュメモリに格納する処理と

を備えることを特徴とする、付記5記載のキャッシュ制御方法。

前記キャッシュメモリにおける前記第1データのサイズに応じて、前記押し出し履歴格納部の格納領域サイズを変更する処理

をそなえることを特徴とする、付記6記載のキャッシュ制御方法。

(付記8)

リード要求受信時に前記キャッシュメモリにおいてキャッシュミスが生じた場合に、前記リード要求に基づいて前記押し出し履歴格納部を検索し、当該押し出し履歴格納部において前記リード要求にかかる前記第2データに関する情報が検出された場合には、当該押し出し履歴格納部から当該第2データに関する情報を削除する処理

を備えることを特徴とする、付記6又は7記載のキャッシュ制御方法。

第2の記憶装置の電源断状態において、書き込み先が当該第2の記憶装置である第1データを第1の記憶装置に記録し、前記第2の記憶装置の電源投入後に、前記第1の記憶装置に記録された前記第1データを前記第2の記憶装置に移動させる処理と、

前記第1の記憶装置に記録された前記第1データを前記第2の記憶装置に格納させた後に、キャッシュメモリから前記第1データを削除する処理と

をコンピュータに実行させることを特徴とする、キャッシュ制御プログラム。

書き込み先が前記第1の記憶装置である第2データが前記キャッシュメモリから押し出された場合に、当該押し出された第2データに関する情報を押し出し履歴格納部に格納する処理と、

前記キャッシュメモリに空き領域が生じると、前記押し出し履歴格納部から前記押し出された前記第2データに関する情報を読み出し、当該第2データに関する情報に基づいて前記第1の記憶装置から読み出した第2データを、前記キャッシュメモリに格納する処理と

を前記コンピュータに実行させることを特徴とする、付記9記載のキャッシュ制御プログラム。

前記キャッシュメモリにおける前記第1データのサイズに応じて、前記押し出し履歴格納部の格納領域サイズを変更する処理

を前記コンピュータに実行させることを特徴とする、付記10記載のキャッシュ制御プログラム。

リード要求受信時に前記キャッシュメモリにおいてキャッシュミスが生じた場合に、前記リード要求に基づいて前記押し出し履歴格納部を検索し、当該押し出し履歴格納部において前記リード要求にかかる前記第2データに関する情報が検出された場合には、当該押し出し履歴格納部から当該第2データに関する情報を削除する処理

を前記コンピュータに実行させることを特徴とする、付記10又は11記載のキャッシュ制御プログラム。

2 ストレージサーバ

4 上位装置

21 オンロードデータ判定部(代理格納処理部)

22 履歴サイズ調節部(押し出し履歴格納領域調節部)

23 履歴管理部(押し出し履歴処理部)

24 載せ直し処理部

25 キャッシュ処理部(キャッシュ解放部)

26 オフロード処理部(代理格納処理部)

30 記憶装置(第1の記憶装置)

40 記憶装置(第2の記憶装置)

201 CPU

202 メモリ(キャッシュメモリ)

202a キャッシュ領域

202b 履歴格納領域(押し出し履歴格納部)

205 ディスプレイ

206 キーボード

207 マウス

211 キャッシュ制御部

Claims (4)

- データを格納する第1の記憶装置と、

第2の記憶装置の電源断状態において、書き込み先が当該第2の記憶装置である第1データを前記第1の記憶装置に記録し、前記第2の記憶装置の電源投入後に、前記第1の記憶装置に記録された前記第1データを前記第2の記憶装置に移動させる代理格納処理部と、

前記代理格納処理部が前記第1の記憶装置に記録された前記第1データを前記第2の記憶装置に格納させた後に、キャッシュメモリから前記第1データを削除するキャッシュ解放部と、

書き込み先が前記第1の記憶装置である第2データが前記キャッシュメモリから押し出された場合に、当該押し出された第2データに関する情報を押し出し履歴格納部に格納する押し出し履歴処理部と、

前記キャッシュメモリに空き領域が生じると、前記押し出し履歴格納部から前記押し出された前記第2データに関する情報を読み出し、当該第2データに関する情報に基づいて前記第1の記憶装置から読み出した第2データを、前記キャッシュメモリに格納する載せ直し処理部と、

前記キャッシュメモリにおける前記第1データの数に応じて、前記押し出し履歴格納部の格納領域サイズを変更する押し出し履歴格納領域調節部と

を備えることを特徴とする、ストレージ装置。 - 前記押し出し履歴処理部が、リード要求受信時に前記キャッシュメモリにおいてキャッシュミスが生じた場合に、前記リード要求に基づいて前記押し出し履歴格納部を検索し、当該押し出し履歴格納部において前記リード要求にかかる前記第2データに関する情報が検出された場合には、当該押し出し履歴格納部から当該第2データに関する情報を削除する

ことを特徴とする、請求項1記載のストレージ装置。 - プロセッサが、第2の記憶装置の電源断状態において、書き込み先が当該第2の記憶装置である第1データを第1の記憶装置に記録し、前記第2の記憶装置の電源投入後に、前記第1の記憶装置に記録された前記第1データを前記第2の記憶装置に移動させるステップと、

前記プロセッサが、前記第1の記憶装置に記録された前記第1データを前記第2の記憶装置に格納させた後に、キャッシュメモリから前記第1データを削除するステップと、

前記プロセッサが、書き込み先が前記第1の記憶装置である第2データが前記キャッシュメモリから押し出された場合に、当該押し出された第2データに関する情報を押し出し履歴格納部に格納するステップと、

前記プロセッサが、前記キャッシュメモリに空き領域が生じると、前記押し出し履歴格納部から前記押し出された前記第2データに関する情報を読み出し、当該第2データに関する情報に基づいて前記第1の記憶装置から読み出した第2データを、前記キャッシュメモリに格納するステップと、

前記プロセッサが、前記キャッシュメモリにおける前記第1データの数に応じて、前記押し出し履歴格納部の格納領域サイズを変更するステップと

を備えることを特徴とする、キャッシュ制御方法。 - 第2の記憶装置の電源断状態において、書き込み先が当該第2の記憶装置である第1データを第1の記憶装置に記録し、前記第2の記憶装置の電源投入後に、前記第1の記憶装置に記録された前記第1データを前記第2の記憶装置に移動させる処理と、

前記第1の記憶装置に記録された前記第1データを前記第2の記憶装置に格納させた後に、キャッシュメモリから前記第1データを削除する処理と、

書き込み先が前記第1の記憶装置である第2データが前記キャッシュメモリから押し出された場合に、当該押し出された第2データに関する情報を押し出し履歴格納部に格納する処理と、

前記キャッシュメモリに空き領域が生じると、前記押し出し履歴格納部から前記押し出された前記第2データに関する情報を読み出し、当該第2データに関する情報に基づいて前記第1の記憶装置から読み出した第2データを、前記キャッシュメモリに格納する処理と、

前記キャッシュメモリにおける前記第1データの数に応じて、前記押し出し履歴格納部の格納領域サイズを変更する処理と

をコンピュータに実行させることを特徴とする、キャッシュ制御プログラム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014055034A JP6256133B2 (ja) | 2014-03-18 | 2014-03-18 | ストレージ装置,キャッシュ制御方法及びキャッシュ制御プログラム |

| US14/633,289 US9846654B2 (en) | 2014-03-18 | 2015-02-27 | Storage apparatus, cache control method, and computer-readable recording medium having cache control program recorded thereon |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014055034A JP6256133B2 (ja) | 2014-03-18 | 2014-03-18 | ストレージ装置,キャッシュ制御方法及びキャッシュ制御プログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015176575A JP2015176575A (ja) | 2015-10-05 |

| JP6256133B2 true JP6256133B2 (ja) | 2018-01-10 |

Family

ID=54142253

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014055034A Expired - Fee Related JP6256133B2 (ja) | 2014-03-18 | 2014-03-18 | ストレージ装置,キャッシュ制御方法及びキャッシュ制御プログラム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9846654B2 (ja) |

| JP (1) | JP6256133B2 (ja) |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04148225A (ja) | 1990-10-08 | 1992-05-21 | Hitachi Ltd | ファイルアクセス制御方式および装置 |

| JPH0863397A (ja) | 1994-08-24 | 1996-03-08 | Hitachi Ltd | ディスクキャッシュ制御方法 |

| JPH11288387A (ja) | 1998-12-11 | 1999-10-19 | Fujitsu Ltd | ディスクキャッシュ装置 |

| JP4742432B2 (ja) * | 2001-03-07 | 2011-08-10 | 富士通株式会社 | メモリシステム |

| JP4890048B2 (ja) | 2006-02-24 | 2012-03-07 | 株式会社日立製作所 | 記憶制御装置及び記憶制御装置を用いたデータマイグレーション方法 |

| US8074014B2 (en) * | 2008-03-31 | 2011-12-06 | Microsoft Corporation | Storage systems using write off-loading |

| US8122217B2 (en) * | 2009-05-06 | 2012-02-21 | International Business Machines Corporation | Method of a full coverage low power mode for storage systems storing replicated data items |

| US8868863B2 (en) * | 2012-01-12 | 2014-10-21 | Alcatel Lucent | Method and apparatus for a frugal cloud file system |

| WO2014002160A1 (ja) | 2012-06-25 | 2014-01-03 | 富士通株式会社 | ストレージ制御装置、ストレージ制御方法およびストレージ制御プログラム |

| JP6264116B2 (ja) * | 2014-03-18 | 2018-01-24 | 富士通株式会社 | 情報処理装置,制御方法及び制御プログラム |

| JP6269253B2 (ja) * | 2014-03-29 | 2018-01-31 | 富士通株式会社 | 分散ストレージシステム、記憶装置制御方法、および記憶装置制御プログラム |

-

2014

- 2014-03-18 JP JP2014055034A patent/JP6256133B2/ja not_active Expired - Fee Related

-

2015

- 2015-02-27 US US14/633,289 patent/US9846654B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015176575A (ja) | 2015-10-05 |

| US9846654B2 (en) | 2017-12-19 |

| US20150269078A1 (en) | 2015-09-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN103562843B (zh) | 用于管理顺序存取存储设备中的数据的方法和设备 | |

| JP6016939B2 (ja) | テープ・ドライブ・システム・サーバ、それを含むテープ・アライアンス・システムおよびシステム、ならびにコンピュータ・プログラム | |

| US10503423B1 (en) | System and method for cache replacement using access-ordering lookahead approach | |

| US8327076B2 (en) | Systems and methods of tiered caching | |

| JP6870246B2 (ja) | ストレージ装置、及びストレージ制御装置 | |

| US10540296B2 (en) | Thresholding task control blocks for staging and destaging | |

| US20120089782A1 (en) | Method for managing and tuning data movement between caches in a multi-level storage controller cache | |

| US20170091054A1 (en) | Methods and Systems for Using a Write Cache in a Storage System | |

| CN103688249B (zh) | 固态盘的自适应记录高速缓存 | |

| JP6099059B2 (ja) | ストレージのためのトラックのキャッシュ管理するプログラム、システム、および方法 | |

| CN103703440A (zh) | 预取用于使更新轨道离台的数据轨道和奇偶校验数据 | |

| US20140304479A1 (en) | Grouping tracks for destaging | |

| KR20140142154A (ko) | 솔리드 스테이트 드라이브 캐싱 환경에서 디스크 조각 모음 관리 방법 | |

| JP2017204037A (ja) | 情報処理装置、重複除去プログラム、及び重複除去方法 | |

| US10719240B2 (en) | Method and device for managing a storage system having a multi-layer storage structure | |

| US9471252B2 (en) | Use of flash cache to improve tiered migration performance | |

| JP5729479B2 (ja) | 仮想テープ装置及び仮想テープ装置の制御方法 | |

| JP2000330729A (ja) | オンラインバックアップ機能を持つディスクアレイシステム | |

| JP6256133B2 (ja) | ストレージ装置,キャッシュ制御方法及びキャッシュ制御プログラム | |

| JP6521694B2 (ja) | 記憶制御システム及び記憶制御装置 | |

| WO2016001959A1 (ja) | ストレージシステム | |

| WO2015145707A1 (ja) | 追記型記憶装置への書き込みデータ決定方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161206 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170823 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170905 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171027 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20171107 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20171120 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6256133 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |