JP6167876B2 - 電子回路、電子機器及び認証システム - Google Patents

電子回路、電子機器及び認証システム Download PDFInfo

- Publication number

- JP6167876B2 JP6167876B2 JP2013246421A JP2013246421A JP6167876B2 JP 6167876 B2 JP6167876 B2 JP 6167876B2 JP 2013246421 A JP2013246421 A JP 2013246421A JP 2013246421 A JP2013246421 A JP 2013246421A JP 6167876 B2 JP6167876 B2 JP 6167876B2

- Authority

- JP

- Japan

- Prior art keywords

- output

- input

- latch circuit

- random number

- latch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09C—CIPHERING OR DECIPHERING APPARATUS FOR CRYPTOGRAPHIC OR OTHER PURPOSES INVOLVING THE NEED FOR SECRECY

- G09C1/00—Apparatus or methods whereby a given sequence of signs, e.g. an intelligible text, is transformed into an unintelligible sequence of signs by transposing the signs or groups of signs or by replacing them by others according to a predetermined system

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/027—Generators characterised by the type of circuit or by the means used for producing pulses by the use of logic circuits, with internal or external positive feedback

- H03K3/037—Bistable circuits

- H03K3/0375—Bistable circuits provided with means for increasing reliability; for protection; for ensuring a predetermined initial state when the supply voltage has been applied; for storing the actual state when the supply voltage fails

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/08—Key distribution or management, e.g. generation, sharing or updating, of cryptographic keys or passwords

- H04L9/0861—Generation of secret information including derivation or calculation of cryptographic keys or passwords

- H04L9/0866—Generation of secret information including derivation or calculation of cryptographic keys or passwords involving user or device identifiers, e.g. serial number, physical or biometrical information, DNA, hand-signature or measurable physical characteristics

Description

(付記1)

入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路を使用して乱数を生成する方法であって、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路から出力される信号を固定する信号を入力し、

前記複数のRSラッチ回路それぞれの出力の排他的論理和を演算する、ことを有することを特徴とする方法。

(付記2)

入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路を使用して固体別情報を生成する方法であって、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路から出力される信号を固定する信号を入力し、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成する、ことを有することを特徴とする方法。

(付記3)

入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路を使用して個体別情報を生成する方法であって、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が定数であると判定されたときに、入力された前記クロック信号の何れかを入力信号として選択し、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成する、ことを有することを特徴とする方法。

(付記4)

入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路を使用して個体別情報を生成する方法であって、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が乱数であると判定されたときに、入力された前記クロック信号の何れかを入力信号として選択し、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成する、ことを有することを特徴とする方法。

(付記5)

入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路を使用してデータを暗号化する方法であって、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路から出力される信号を固定する信号を入力し、

前記複数のRSラッチ回路それぞれの出力の排他的論理和を演算し、

演算された前記乱数を暗号鍵として使用して、データを暗号化する、ことを有することを特徴とする方法。

(付記6)

入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路を使用してデータを暗号化する方法であって、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路から出力される信号を固定する信号を入力し、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成し、

生成された前記個体別情報を暗号鍵として使用して、データを暗号化する、ことを有することを特徴とする方法。

(付記7)

入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路を使用してデータを暗号化する方法であって、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が定数であると判定されたときに、入力された前記クロック信号の何れかを入力信号として選択し、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成し、

生成された前記個体別情報を暗号鍵として使用して、データを暗号化する、ことを有することを特徴とする方法。

(付記8)

入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路を使用してデータを暗号化する方法であって、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が乱数であると判定されたときに、入力された前記クロック信号の何れかを入力信号として選択し、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成し、

生成された前記個体別情報を暗号鍵として使用して、データを暗号化する、ことを有することを特徴とする方法。

(付記9)

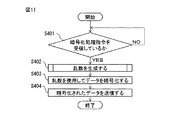

入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路を使用して生成された固体別情報を認証する方法であって、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路から出力される信号を固定する信号を入力し、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成し、

生成された前記個体別情報を個体別情報を認証する、ことを有することを特徴とする方法。

(付記10)

入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路を使用して生成された固体別情報を認証する方法であって、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が定数であると判定されたときに、入力された前記クロック信号の何れかを入力信号として選択し、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成し、

生成された前記個体別情報を個体別情報を認証する、ことを有することを特徴とする方法。

(付記11)

入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路を使用して生成された固体別情報を認証する方法であって、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が乱数であると判定されたときに、入力された前記クロック信号の何れかを入力信号として選択し、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成し、

生成された前記個体別情報を個体別情報を認証する、ことを有することを特徴とする方法。

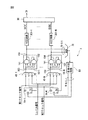

2、3、200、300 ラッチPUF(個体別情報生成装置)

10、10−1〜10−N RSラッチ回路

20 出力選択回路

30−1〜30−N フリップフロップ

40−1〜40−N 選択部

50、70、80 乱数判定回路(判定部)

60 排他的論理和素子

90 個体別情報生成部

301−1〜301−N 判定回路

400、501 電子機器

500 認証システム

502 認証装置

Claims (12)

- 入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路と、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定する判定部と、

前記判定部の判定結果に応じて、前記複数のRSラッチ回路のそれぞれに入力するクロック信号を維持するか、周波数が異なる他のクロック信号に変更するか、又は出力される信号を固定する信号に変更するかを選択する選択部と、を有する、ことを特徴とする電子回路。 - 前記選択部は、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路から出力される信号を固定する信号を入力する、請求項1に記載の電子回路。 - 前記選択部は、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路から出力される信号を固定する信号を入力する、請求項1に記載の電子回路。 - 前記選択部は、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が定数であると判定されたときに、入力された前記クロック信号の何れかを入力信号として選択する、請求項1に記載の電子回路。 - 前記選択部は、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が乱数であると判定されたときに、入力された前記クロック信号の何れかを入力信号として選択する、請求項1に記載の電子回路。 - 入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路と、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定する判定部と、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路から出力される信号を固定する信号を入力する選択部と、

前記複数のRSラッチ回路それぞれの出力の排他的論理和を演算する排他的論理和素子と、を有する乱数発生器と、

前記乱数発生器が生成した乱数を暗号鍵として使用して、データを暗号化する暗号化器と、

を有することを特徴とする電子機器。 - 入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路と、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定する判定部と、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路から出力される信号を固定する信号を入力する選択部と、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成する個体別情報生成装置と、

前記個体別情報生成装置が生成した個体別情報を暗号鍵として使用して、データを暗号化する暗号化器と、

を有することを特徴とする電子機器。 - 入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路と、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定する判定部と、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が定数であると判定されたときに、入力された前記クロック信号の何れかを入力信号として選択する選択部と、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成する個体別情報生成装置と、

前記個体別情報生成装置が生成した個体別情報を暗号鍵として使用して、データを暗号化する暗号化器と、

を有することを特徴とする電子機器。 - 入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路と、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定する判定部と、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が乱数であると判定されたときに、入力された前記クロック信号の何れかを入力信号として選択する選択部と、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成する個体別情報生成装置と、

前記個体別情報生成装置が生成した個体別情報を暗号鍵として使用して、データを暗号化する暗号化器と、

を有することを特徴とする電子機器。 - 入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路と、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定する判定部と、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路から出力される信号を固定する信号を入力する選択部と、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成する個体別情報生成装置と、

前記個体別情報生成装置が生成した個体別情報を出力する通信部と、を有する、電子機器と、

前記電子機器から出力された個体別情報を認証する認証装置と、を有することを特徴とする認証システム。 - 入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路と、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定する判定部と、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が定数であると判定されたときに、入力された前記クロック信号の何れかを入力信号として選択する選択部と、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成する個体別情報生成装置と、

前記個体別情報生成装置が生成した個体別情報を出力する通信部と、を有する、電子機器と、

前記電子機器から出力された個体別情報を認証する認証装置と、を有することを特徴とする認証システム。 - 入力されるクロック信号に応じて、それぞれがメタステーブルになる複数のRSラッチ回路と、

前記複数のRSラッチ回路のそれぞれの出力が乱数又は定数の何れかであるかを判定する判定部と、

RSラッチ回路の出力が定数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を維持し、

RSラッチ回路の出力が乱数であると判定されたときに、前記RSラッチ回路に入力されるクロック信号を、周波数が異なる他のクロック信号に変更し、

周波数が異なるクロック信号の何れを入力した場合にも、RSラッチ回路の出力が乱数であると判定されたときに、入力された前記クロック信号の何れかを入力信号として選択する選択部と、

前記複数のRSラッチ回路の出力を使用して個体別情報を生成する個体別情報生成装置と、

前記個体別情報生成装置が生成した個体別情報を出力する通信部と、を有する、電子機器と、

前記電子機器から出力された個体別情報を認証する認証装置と、を有することを特徴とする認証システム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013246421A JP6167876B2 (ja) | 2013-11-28 | 2013-11-28 | 電子回路、電子機器及び認証システム |

| US14/521,616 US9384682B2 (en) | 2013-11-28 | 2014-10-23 | Electronic circuit, electronic apparatus, and authentication system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013246421A JP6167876B2 (ja) | 2013-11-28 | 2013-11-28 | 電子回路、電子機器及び認証システム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015106172A JP2015106172A (ja) | 2015-06-08 |

| JP6167876B2 true JP6167876B2 (ja) | 2017-07-26 |

Family

ID=53182675

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013246421A Active JP6167876B2 (ja) | 2013-11-28 | 2013-11-28 | 電子回路、電子機器及び認証システム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9384682B2 (ja) |

| JP (1) | JP6167876B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9621141B1 (en) * | 2016-01-11 | 2017-04-11 | Oracle International Corporation | Micro-pipeline frequency-comparison circuit |

| US10579339B2 (en) * | 2017-04-05 | 2020-03-03 | Intel Corporation | Random number generator that includes physically unclonable circuits |

| US11005669B2 (en) * | 2017-11-14 | 2021-05-11 | Taiwan Semiconductor Manufacturing Co., Ltd. | PUF generators based on SRAM bit cells |

| EP3671435B1 (en) * | 2018-12-20 | 2023-08-09 | Secure-IC SAS | Methods and devices for random number generation |

| US11537755B1 (en) * | 2019-10-09 | 2022-12-27 | University Of South Florida | SR flip-flop based physical unclonable functions for hardware security |

| CN116054816B (zh) * | 2023-03-29 | 2023-07-14 | 山东云海国创云计算装备产业创新中心有限公司 | 加密逻辑单元电路、加密芯片、服务器和图像加密方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6631390B1 (en) | 2000-03-06 | 2003-10-07 | Koninklijke Philips Electronics N.V. | Method and apparatus for generating random numbers using flip-flop meta-stability |

| JP3604674B2 (ja) * | 2001-09-26 | 2004-12-22 | 株式会社東芝 | 乱数生成回路 |

| US6771104B2 (en) * | 2002-07-25 | 2004-08-03 | Koninklijke Philips Electronics N.V. | Switching electronic circuit for random number generation |

| US7124155B2 (en) * | 2002-07-25 | 2006-10-17 | Koninklijke Philips Electronics N.V. | Latching electronic circuit for random number generation |

| JP4095002B2 (ja) | 2002-09-13 | 2008-06-04 | 株式会社東芝 | 乱数生成回路 |

| TWI282934B (en) | 2002-09-13 | 2007-06-21 | Toshiba Corp | Random number generator |

| US7484192B2 (en) * | 2006-09-18 | 2009-01-27 | International Business Machines Corporation | Method for modeling metastability decay through latches in an integrated circuit model |

| JP5171315B2 (ja) * | 2008-02-28 | 2013-03-27 | 株式会社東芝 | 乱数生成回路 |

| US8489660B2 (en) * | 2009-06-26 | 2013-07-16 | Intel Corporation | Digital random number generator using partially entropic data |

| JP5273294B2 (ja) * | 2010-03-26 | 2013-08-28 | 富士通株式会社 | 乱数生成器、暗号化装置、及び認証装置 |

| US20110299678A1 (en) * | 2010-06-07 | 2011-12-08 | Alexander Roger Deas | Secure means for generating a specific key from unrelated parameters |

| JP5333669B2 (ja) * | 2010-06-30 | 2013-11-06 | 富士通株式会社 | 個体別情報生成装置及び個体別情報生成方法 |

| JP5831202B2 (ja) | 2011-12-20 | 2015-12-09 | 富士通株式会社 | 個体別情報生成装置及び個体別情報生成方法 |

-

2013

- 2013-11-28 JP JP2013246421A patent/JP6167876B2/ja active Active

-

2014

- 2014-10-23 US US14/521,616 patent/US9384682B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US9384682B2 (en) | 2016-07-05 |

| US20150146869A1 (en) | 2015-05-28 |

| JP2015106172A (ja) | 2015-06-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6167876B2 (ja) | 電子回路、電子機器及び認証システム | |

| CN110389747B (zh) | 具有物理不可复制功能的真随机数生成系统 | |

| JP5273294B2 (ja) | 乱数生成器、暗号化装置、及び認証装置 | |

| Güneysu et al. | Cryptanalysis with COPACOBANA | |

| CN104468089B (zh) | 数据保护装置及其方法 | |

| KR101727130B1 (ko) | 암호화 키를 획득하기 위한 디바이스 및 방법 | |

| CN111492616B (zh) | 用于基于晶格的密码学的可配置设备 | |

| JP5857726B2 (ja) | 温度センサ、暗号化装置、暗号化方法、及び個体別情報生成装置 | |

| US20160013939A1 (en) | Generating a key based on a combination of keys | |

| JP5831202B2 (ja) | 個体別情報生成装置及び個体別情報生成方法 | |

| JP4986206B2 (ja) | 暗号処理方法及び暗号処理装置 | |

| JPWO2008056613A1 (ja) | 認証装置 | |

| JPWO2012001796A1 (ja) | 個体別情報生成装置及び個体別情報生成方法 | |

| WO2012130575A1 (en) | Establishing unique key during chip manufacturing | |

| JP2016171452A (ja) | 電子回路、認証装置及び認証システム | |

| JP6533553B2 (ja) | 暗号化/復号装置及びその電力解析保護方法 | |

| CN112906070B (zh) | 具有块密码侧信道攻击减轻的集成电路和IoT设备及相关方法 | |

| US11934323B2 (en) | Diversifying a base symmetric key based on a public key | |

| US20190294417A1 (en) | Method and system for deriving deterministic prime number | |

| CN110493265A (zh) | 加密数据的方法及存储介质 | |

| WO2018067865A1 (en) | Generating an authentication result by using a secure base key | |

| JP6348273B2 (ja) | 情報処理システム | |

| KR20000062151A (ko) | 암호 기능 출력을 생성하기 위한 안전 방법 | |

| CN110249334B (zh) | 设备间高效安全通信的系统和方法 | |

| CN113271202B (zh) | 一种数据加密方法及装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160804 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170530 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170531 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170612 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6167876 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |