JP6123510B2 - 半導体装置及び半導体装置の制御方法 - Google Patents

半導体装置及び半導体装置の制御方法 Download PDFInfo

- Publication number

- JP6123510B2 JP6123510B2 JP2013124053A JP2013124053A JP6123510B2 JP 6123510 B2 JP6123510 B2 JP 6123510B2 JP 2013124053 A JP2013124053 A JP 2013124053A JP 2013124053 A JP2013124053 A JP 2013124053A JP 6123510 B2 JP6123510 B2 JP 6123510B2

- Authority

- JP

- Japan

- Prior art keywords

- bank

- data

- index

- array

- access instruction

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

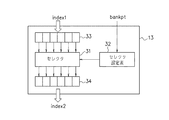

11−0〜11−3 インタフェース

20−0〜20−4 データメモリ

12 命令制御部

13 インデックス変換器

14 セレクタ

15 加算器

16 アドレス保持部

17 バンク選択用デコーダ

31 セレクタ

32 セレクタ設定表

33、34 レジスタ

Claims (7)

- 複数のバンクを有するデータメモリと、

前記データメモリへのアクセス命令に応じてアクセスを行うプロセッサとを有し、

前記プロセッサは、

入力された前記アクセス命令が、配列のデータを配置する前記データメモリのバンクの振り分けを指定する指定情報を含むアクセス命令である場合には、前記指定情報により指定されるバンクの振り分けに応じて、前記アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを変換し、変換した前記インデックスに従って前記バンクの選択を行い、前記配列に係る前記データメモリへのアクセスを行うことを特徴とする半導体装置。 - 前記プロセッサは、

入力された前記アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを、前記指定情報により指定されるバンクの振り分けに応じて変換するインデックス変換部を有し、

前記アクセス命令が前記指定情報を含むアクセス命令である場合には、変換したインデックスに基づいて前記バンクの選択を行い、前記配列に係る前記データメモリへのアクセスを行うことを特徴とする請求項1記載の半導体装置。 - 前記インデックス変換部は、

配列のインデックスと前記配列のデータを配置する前記バンクとの対応関係を示すテーブルと、

前記指定情報に応じて選択した前記テーブルを参照して、前記アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを変換する変換部とを有することを特徴とする請求項2記載の半導体装置。 - 前記インデックス変換部が有する前記テーブルには、配列のインデックスの下位ビットの値と前記配列のデータを配置する前記バンクとが一意に対応するテーブルを含むことを特徴とする請求項3記載の半導体装置。

- 前記プロセッサは、

前記アクセス命令が、前記指定情報を含むアクセス命令である場合には、変換したインデックスを選択し、前記指定情報を含むアクセス命令でない場合には、前記アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを選択する選択部を有し、

前記選択部により選択したインデックスに基づいて前記バンクの選択を行い、前記配列に係る前記データメモリへのアクセスを行うことを特徴とする請求項2記載の半導体装置。 - 複数のバンクを有するデータメモリと、前記データメモリへのアクセス命令に応じてアクセスを行うプロセッサとを有する半導体装置の制御方法であって、

入力された前記アクセス命令が、配列のデータを配置する前記データメモリのバンクの振り分けを指定する指定情報を含むアクセス命令である場合に、前記指定情報により指定されるバンクの振り分けに応じて、前記アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを変換する工程と、

変換したインデックスに基づいて前記バンクの選択を行い、前記配列に係る前記データメモリへのアクセスを行う工程とを有することを特徴とする半導体装置の制御方法。 - 前記配列のインデックスを変換する工程は、

前記指定情報に応じて、配列のインデックスと前記配列のデータを配置する前記バンクとの対応関係を示すテーブルを選択する工程と、

選択した前記テーブルを参照して、前記アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを変換する工程とを有することを特徴とする請求項6記載の半導体装置の制御方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013124053A JP6123510B2 (ja) | 2013-06-12 | 2013-06-12 | 半導体装置及び半導体装置の制御方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013124053A JP6123510B2 (ja) | 2013-06-12 | 2013-06-12 | 半導体装置及び半導体装置の制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014241107A JP2014241107A (ja) | 2014-12-25 |

| JP6123510B2 true JP6123510B2 (ja) | 2017-05-10 |

Family

ID=52140311

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013124053A Active JP6123510B2 (ja) | 2013-06-12 | 2013-06-12 | 半導体装置及び半導体装置の制御方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6123510B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN116820344B (zh) * | 2023-07-03 | 2024-04-26 | 摩尔线程智能科技(北京)有限责任公司 | 存储器访问电路及存储器访问方法、集成电路和电子设备 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05143326A (ja) * | 1991-11-18 | 1993-06-11 | Matsushita Electric Ind Co Ltd | バンク処理装置 |

| EP1050819A1 (en) * | 1999-05-03 | 2000-11-08 | Sgs Thomson Microelectronics Sa | Computer memory access |

| JP2004157695A (ja) * | 2002-11-06 | 2004-06-03 | Matsushita Electric Ind Co Ltd | 情報処理方法および情報処理装置 |

-

2013

- 2013-06-12 JP JP2013124053A patent/JP6123510B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014241107A (ja) | 2014-12-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3950831B2 (ja) | メモリインタリーブ方式 | |

| US6968440B2 (en) | Systems and methods for processor memory allocation | |

| KR20200129843A (ko) | 연산 회로를 포함하는 메모리 장치, 이를 제어하는 메모리 컨트롤러 및 이를 포함하는 메모리 시스템 | |

| CN101341473B (zh) | 具有共享存储体的多处理器电路 | |

| CN109478252B (zh) | 用于神经网络硬件加速的多播网络和存储器转移优化 | |

| JP2012137839A (ja) | メモリ制御装置、及びメモリ制御方法 | |

| JP2009529756A (ja) | テストデータのフォーマット変換 | |

| GB2457309A (en) | Process allocation in a processor array using a simulated annealing method | |

| KR20130011961A (ko) | 연산 제어 장치, 연산 제어 방법, 프로그램, 및 병렬 프로세서 | |

| JPWO2007069506A1 (ja) | 記憶領域割当システム及び方法と制御装置 | |

| JP5885481B2 (ja) | 情報処理装置、情報処理方法、及びプログラム | |

| CN100410919C (zh) | 处理器 | |

| KR20090087689A (ko) | 다중 채널 플래시 메모리 시스템 및 그것의 액세스 방법 | |

| JP6123510B2 (ja) | 半導体装置及び半導体装置の制御方法 | |

| CN104866297A (zh) | 一种优化核函数的方法和装置 | |

| KR20030055467A (ko) | 다단계 분할을 이용한 기억소자 할당방법 | |

| CN116360858A (zh) | 数据的处理方法、图形处理器、电子设备及存储介质 | |

| US11625269B1 (en) | Scheduling for locality of reference to memory | |

| JP2013512479A (ja) | Simdモードで動作するプロセッシング・エレメントの内部メモリに分散記憶された正方マトリックス及びその転置マトリックスに、時間と面積の効率良いアクセスを可能とする装置及び方法 | |

| KR20150078951A (ko) | 메모리 관리 방법 및 장치 | |

| JP7225904B2 (ja) | ベクトル演算処理装置、ベクトル演算処理装置による配列変数初期化方法、及び、ベクトル演算処理装置による配列変数初期化プログラム | |

| JP4810542B2 (ja) | メモリ制御方法、プログラム及び装置 | |

| CN101322107A (zh) | 高效访问存储器中的矩阵元素的方法和装置 | |

| JP2014109938A (ja) | プログラム起動装置、プログラム起動方法、及びプログラム起動プログラム | |

| JP7168731B1 (ja) | メモリアクセス制御装置、メモリアクセス制御方法、及び、メモリアクセス制御プログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160310 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161209 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161220 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170215 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170307 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170320 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6123510 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |