JP6098429B2 - 演算処理装置及び演算処理装置の制御方法 - Google Patents

演算処理装置及び演算処理装置の制御方法 Download PDFInfo

- Publication number

- JP6098429B2 JP6098429B2 JP2013167781A JP2013167781A JP6098429B2 JP 6098429 B2 JP6098429 B2 JP 6098429B2 JP 2013167781 A JP2013167781 A JP 2013167781A JP 2013167781 A JP2013167781 A JP 2013167781A JP 6098429 B2 JP6098429 B2 JP 6098429B2

- Authority

- JP

- Japan

- Prior art keywords

- instruction

- signal

- branch instruction

- completion

- branch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3802—Instruction prefetching

- G06F9/3804—Instruction prefetching for branches, e.g. hedging, branch folding

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

- G06F9/3001—Arithmetic instructions

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/3005—Arrangements for executing specific machine instructions to perform operations for flow control

- G06F9/30058—Conditional branch instructions

Description

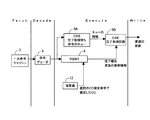

令を命令の実行順に蓄積するキュー構造のストレージと、完了処理回路とを有する。CSE

9の完了処理回路は、RSBR8や演算器12、一次データキャッシュ11等から各処理の完了報告を受け取る。CSE9の完了処理回路は、その受け取った完了報告と、キューに蓄積

された情報を基に、命令完了の処理を行う。この命令完了の処理をCOMMITという。命令デコーダ4で解読された命令はCSE9のキューに蓄積される。CSE9のキューに蓄積された命令は、命令処理完了の報告を待つ。各リザベーションステーションに蓄積され、アウトオブオーダーで実行された命令の完了報告は、CSE9に送られる。CSE9の完了処理回路は、CSE9のキューに蓄積された完了報告待ちの命令の中から完了報告に対応する命令を、プ

ログラム本来の実行順序にしたがってCOMMITする。命令がCOMMITされると、資源の更新が行われる。

処理待ち記憶部の例示である。また、解読された結果、分岐命令であると判断された命令は、RSBR8に蓄積される。RSBR8に蓄積された分岐命令は、分岐が判断できる状態になるのを待つ。分岐命令では、Condition Code(CC)レジスタ19と呼ばれるレジスタの値によって、分岐する(TAKEN)か分岐しない(NOT TAKEN)かが確定(Resolve)する。した

がって、後続の分岐命令のResolveは、Condition Codeを変更する命令の完了を待つ。な

お、Condition Codeを変更する命令がCOMMITされた時にCCレジスタ19は更新される。しかし、CCレジスタ19が更新されてからRSBR8で分岐の判断を行うのでは時間がかかる。そこで、演算器12で計算されたCondition Codeを、演算器12からRSBR8に送ってもよい。RSBR8は演算器12から送られたCondition Codeを基に分岐判断を行えばよい。分岐判断できる状態になるとRSBR8は分岐判断を行う。RSBR8は、分岐命令の完了報告と資源の更新情報をCSE9の完了処理回路9Bに送る。資源の更新情報は、例えば、上述のTAKENやNOT TAKENが例示される。RSBR8は、分岐命令の完了を管理する分岐命令実行管理部の

例示である。CSE9の完了処理回路9BはRSBR8からの報告を受けて、CSE9のキュー9Aに蓄積された完了報告待ちの命令の中から完了報告に対応する分岐命令の完了処理を行い、資源の更新を行う。CSE9の完了処理回路9Bは、分岐命令の実行に伴う資源の更新処理を起動する完了処理部の例示である。

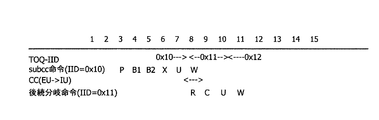

になっている命令のIIDである。subcc命令(IID=0x10)は、図3で例示されるsubcc命令

のIIDが0x10であることを例示している。CC(EU->IU)は、subcc命令のCondition Codeが演算器12からRSBR8に送信されている事を例示する。EUは演算器12を例示し、IUはRSBR8を例示している。後続分岐命令(IID=0x11)は、subcc命令によって確定したCondition Codeに基づいて分岐判断を行う分岐命令のIIDが0x11であることを例示する。Resolved(IID=0x11)は、後続分岐命令(IID=0x11)の分岐の成立、不成立の確定を示す。BR_COMPは、後続分岐命令(IID=0x11)の完了を示す信号の例示である。

ンステーションは、実行待ちの命令の中から優先度の高いものを選んで、演算器12に送る。B1、B2サイクルでは、演算器12は、リザベーションステーションから送られてきた命令を実行する準備を行う。Xサイクルでは、演算器12が命令を実行する。Uサイクルでは、CSE9が命令完了の判断を行う。Wサイクルでは、各資源の更新信号がPC18などの資源の更新を行う。

路9Bに送られる。UサイクルでCSE9は命令完了の判断を行う。Wサイクルでは、各資源

の更新信号が資源の更新を行う。

のCondition Codeが、演算器12からRSBR8に送られる。第8サイクルでは、第7サイクルで送られてきたCondition Codeを基に、後続分岐命令の分岐判断が行われる。第9サイクルでは、分岐命令が完了する。分岐命令の完了を示す、BR_COMP信号105が生成され

る。第10サイクルでは、資源の更新信号が作成される。第11サイクルでは、WRITE信

号を基に、各資源の更新信号が資源の更新を行う。

、他の命令の実行結果等によって確定する。そのため、分岐命令は他の命令との依存関係が生じやすい。したがって、分岐命令は完了待ちの状態になりやすい。その結果として、プロセッサの性能が低下する場合がある。

比較例として、分岐命令の完了報告を待って分岐命令のCOMMIT処理を行うシステムを例示する。図4は、複数のプロセッサ(CPU401、CPU402)とプロセッサに接続されたメモリ(メモリ403、メモリ404)、プロセッサと外部装置との入出力制御を行うインターコネクト制御部405を例示する図である。比較例のシステムは、例えば、図4のCPU401、CPU402に適用できる。また、比較例のシステムは、図1に例示するようなアウトオブオーダー機能及びパイプライン機能を有するスーパースカラプロセッサであってもよい。

、後続分岐命令(IID=0x11)の項目の意味については、図3の場合と同様であるので、説明は省略する。

。第8サイクルでは、第7サイクルで送られてきたCondition Codeを基に、後続分岐命令の分岐判断が行われる。第9サイクルでは、分岐命令が完了する。第10サイクルでは、資源の更新信号が作成される。第11サイクルでは、WRITE信号を基に、各資源の更新信

号が資源の更新を行う。

クルでは、RSBR8は、RSBR8内の命令の内容による分岐条件と、Condition Codeに基づいて、分岐するかどうか判断する(S62)。CSE9のキュー9Aでは、subcc命令の完了を受け、後続の分岐命令がCSE9のキュー9Aの先頭(以下、TOQ-CSEという)となる。TOQ-CSEとなった分岐命令は、RSBR8からの完了報告であるBR_COMP信号105を待つ(S63)。第9サイクルでは、各RSBR8は、分岐判断情報からCSE9に送信する分岐判断情報を

選択する。選択された分岐判断情報を基に、RSBR8はBR_COMP信号105及びBR_TAKEN信

号を生成する(S64)。CSE9のキュー9Bでは、TOQ-CSEの分岐命令はCOMMIT処理を待つ。RSBR8からのBR_COMP信号105及びBR_TAKEN信号を受けて、CSE9の完了処理回路9Bは、TOQ_BR_COMP信号及びTOQ_BR_TAKEN信号を生成する(S65)。TOQ_BR_COMP信号を受けて、CSE9の完了処理回路9Bは分岐命令の完了を判断する。CSE9の完了処理回路9Bは、COMMIT信号であるTOQ_COMMIT信号を生成する。さらに、CSE9の完了処理回路9B

は、TOQ_BR_TAKEN信号等を基に資源の更新信号であるWRITE信号を作成する(S66)。WRITE信号を基に、各資源の更新信号が資源の更新を行う(S67)。

おけるCSE9は、CSE9のキュー9AとCSE9の完了処理回路9Bとを有する。CSE9の完了処理回路9Bは、WRITE信号生成回路20、ラッチ24a〜24c、AND回路114a〜114c、OR回路115a、を有する。

ある場合、CSE9のキュー9Aは分岐命令がTOQ-CSEの命令である事を示すTOQ_BR_USE信号104を生成する。TOQ_BR_USE信号104は、ラッチ24aに保存される。分岐命令が完了すると、RSBR8は、分岐命令の完了を示すBR_COMP信号105を生成する。RSBR8の分

岐命令がTOQ-CSEの命令である場合、TOQ_BR_COMP_SEL信号106が生成される。TOQ_BR_COMP_SEL信号106は、RSBR8で実行された分岐命令がTOQ-CSEの命令である事を示す信号である。TOQ_BR_COMP_SEL信号106は、例えば、RSBR8からBR_COMP信号105を送られる命令のIIDとTOQ-CSEの命令のIIDとが一致するとCSE9の完了処理回路9Bで生成される。AND回路114bでは、TOQ_BR_COMP_SEL信号106とRSBR8から送られたBR_COMP信号

105とのAND演算を行い、TOQ_BR_COMP信号107を生成する。TOQ_BR_COMP信号107

は、TOQ-CSEの分岐命令の完了を示す信号である。TOQ_BR_COMP信号107は、ラッチ24bに保存される。AND回路114cは、TOQ_BR_COMP_SEL信号106とRSBR8からのBR_TAKEN信号108とのAND演算を行い、TOQ_BR_TAKEN信号109を生成する。TOQ_BR_TAKEN信

号109は、TOQ-CSEの分岐命令が分岐した(TAKEN)ことを示す信号である。TOQ_BR_TAKEN信号109は、ラッチ24cに保存される。

の命令が分岐命令ではないことがわかる。そこで、OR回路115aでは、ラッチ24aに保存されたTOQ_BR_USE信号104信号をNOT演算したものとラッチ24bに保存されたTOQ_BR_COMP信号107とのOR演算を行い、TOQ_BR_COMMIT信号111を生成する。TOQ_BR_COMMIT信号111は、TOQ-CSEの分岐命令のCOMMIT処理を行ってもよい事を示す信号の例示で

ある。

、論理演算により生成される。-TOQ_EU_USE信号とTOQ_EU_COMP信号のOR演算は、TOQ_EU_COMMIT信号112を生成する論理演算の例示である。TOQ_EU_COMP信号は、TOQ-CSEのEU命

令が完了した事を示す信号の例示である。-TOQ_EU_USE信号は、TOQ-CSEの命令がEU命令ではない事を示す信号の例示である。TOQ-CSEの命令が分岐命令の場合、TOQ-CSEの命令はEU命令ではないので、-TOQ_EU_USE信号が生成される。その結果、TOQ_EU_COMMIT信号112が生成される。

である。-TOQ_FCH_USE信号は、TOQ-CSEの命令がFCH命令ではない事を示す信号の例示である。TOQ-CSEの命令が分岐命令の場合、TOQ-CSEの命令はFCH命令ではないので、-TOQ_FCH_USE信号が生成される。その結果、TOQ_FCH_COMMIT信号113が生成される。なお、LOAD

命令やSTORE命令はFCH命令の例示である。

113のAND演算を行う事で、TOQ_COMMIT信号110を生成する。

、各資源の更新信号が資源の更新を行う。

行われた。

比較例では、分岐命令の完了を待ってCOMMIT処理が行われた。実施形態1では、分岐命令の完了を待たずに行う分岐命令のCOMMIT処理を例示する。実施形態1のシステムは、例えば、図4のCPU401,CPU402に適用できる。また、実施形態1のシステムは、図1に例示するようなアウトオブオーダー機能及びパイプライン機能を有するスーパースカラプロセッサであってもよい。図1のプロセッサや図4のCPU401、CPU402は、演算処理装置の例示である。また、分岐命令はCondition Codeが確定してから所定のサイクルで完了する事を前提とする。実施形態1では、所定のサイクルが2サイクルの場合を例示する。

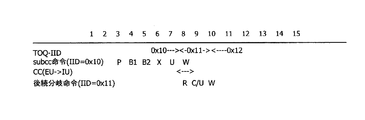

示す信号の例示である。TOQ-IID、subcc命令(IID=0x10)、CC(EU->IU)、後続分岐命令(IID=0x11)、RESOLVE(IID=0x11)、BR_COMPの項目の意味については、図3の場合と同様であるので、説明は省略する。

イクルでは、第7サイクルで送られてきたCondition Codeを基に後続分岐命令の分岐判断が行われる。第9サイクルでは、分岐命令が完了する。BR_COMP信号105の生成を待た

ずに、TOQ-CSEの分岐命令の完了を示すTOQ_BR_COMP信号107が生成される。分岐命令の完了に伴い、分岐命令の完了を示すBR_COMP信号105が生成される。BR_TAKEN信号10

8等を基にWRITE信号が作成される。第10サイクルでは、WRITE信号を基に、各資源の更新信号が資源の更新を行う。

るように、CSE9のキュー9A、CSE9の完了処理回路9B、分岐命令のCOMMITを高速化する分岐命令COMMIT高速化回路22、セレクタ25、を有する。

分岐命令COMMIT高速化回路22は、TOQ_BR_USE信号104を受信すると、分岐命令の完了処理を開始させるSET_FORCE_BR_COMP信号101を生成する。SET_FORCE_BR_COMP信号101の生成では、分岐命令COMMIT高速化回路22は、分岐命令の完了信号であるBR_COMP信

号105を待たなくてよい。分岐命令COMMIT高速化回路22は、促進部の例示である。

る命令は既に完了していると考えられる。そのため、分岐判断に用いるCondition Codeは確定していると考えられる。したがって、分岐命令は所定のサイクルで完了すると考えられる。実施形態1では、所定のサイクルとして、Condition Codeの確定から2サイクルで分岐命令は完了する場合を例示する。そのため、分岐命令がTOQ-CSEの命令になれば、分

岐命令は次のサイクルで完了できると考えられる。そこで、分岐命令がTOQ-CSEの命令に

なると、CSE9内での分岐命令の完了を示すTOQ_BR_COMP信号107が生成される。CSE9

の完了処理回路9BはRSBR8からの分岐命令の完了を示すBR_COMP信号105を待たなく

よい。その結果、分岐命令のCOMMITのタイミングが比較例と比べて1サイクル早くなる。そのため、比較例と同じタイミングで資源の更新情報をWRITE信号生成回路20に送信し

たのでは、WRITE信号の生成に間に合わない。そこで、実施形態1では、資源の更新情報

を1サイクル早くWRITE信号生成回路20に送信する回路が追加される。

施形態1におけるCSE9は、CSE9のキュー9AとCSE9の完了処理回路9Bとを有する。CSE9の完了処理回路9Bは、WRITE信号生成回路20、ラッチ24a〜24d、AND回路114a〜114c、OR回路115a〜115bとを有する。比較例と同一の構成要素については、同一の符号を付し、その説明を省略する。

こで、TOQ_BR_USE信号104が生成されると、OR回路115bはBR_COMP信号105を待

たずにTOQ_BR_COMP信号107を生成する。TOQ_BR_COMP信号107はラッチ24bに保存される。BR_COMP信号105を待たないことで、TOQ_BR_COMP信号107を比較例より1サイクル早く生成することができる。これ以降の、TOQ_COMMIT信号110を生成する流れは比較例と同様であるため、その説明を省略する。

に保存される。ラッチ24dに保存されたSET_FORCE_BR_COMP信号101は、FORCE_BR_COMP信号101aとして、セレクタ25に送信される。FORCE_BR_COMP信号101aを受信

したセレクタ25は、ラッチ24cを迂回する経路を選択して、BR_TAKEN信号108をWRITE信号生成回路20に送信する。ラッチ24cを迂回することでWRITE信号の生成を1サイクル早める事ができる。

を開始できる。そのため、分岐命令の処理サイクルを比較例の場合よりも1サイクル短縮できる。

実施形態1では、分岐命令が所定のサイクルで完了する事を前提に、分岐命令の完了を高速化した。変形例1では、分岐命令が所定のサイクルで完了しない場合にも本案を適用する構成を開示する。

してSET_FORCE_BR_COMP信号101を生成した。したがって、所定のサイクルで分岐命令

が完了しない場合、分岐命令COMMIT高速化回路22はSET_FORCE_BR_COMP信号101を生

成してはいけない。そこで、変形例1では、所定のサイクルで分岐命令が完了しない場合に、分岐命令COMMIT高速化回路22の動作を抑止する抑止信号生成回路が追加される。抑止信号生成回路は、抑止部の例示である。

、以下の(1)〜(3)が例示される。以下の(1)〜(3)の状態を通知する信号は、所定の条件信号の例示である。

、TOQ-CSEの命令が分岐命令であってもCondition Codeが確定していない。そのため、分

岐の判断材料が揃っていない場合がある。

分岐命令COMMIT高速化回路の抑止信号生成回路23(以下、抑止信号生成回路23)を追加する。抑止信号生成回路23は、分岐命令COMMIT高速化回路22の動作を抑止する回路の例示である。変形例1では、Condition Codeが確定してから2サイクルで分岐命令が完了する場合を考える。実施形態1と同じ構成要素は実施形態1と同一の符号を付し、その説明を省略する。

。

2を生成する。分岐命令COMMIT高速化回路22のAND回路114dは、INH_SET_FORCE_BR_COMP信号102をNOT演算したものと、TOQ_BR_USE信号104とのAND演算を行う。その結果、INH_SET_FORCE_BR_COMP信号102がアサートされた場合には、SET_FORCE_BR_COMP信号101は生成されない。この処理によって、分岐予測ミス等の場合には、TOQ_BR_COMMIT信号111は、RSBR8からのBR_COMP信号105を待って生成される。さらに、RSBR8からの資源の更新情報は、セレクタ25によって、ラッチ24cを経由してWRITE信号生成

回路20に送信される。

(EU->IU)、後続分岐命令(IID=0x11)の項目の意味については、図3の場合と同様であるので、説明は省略する。

れる。第8サイクルでは、第7サイクルで送られてきたCondition Codeを基に、後続分岐命令の分岐判断が行われる。第9サイクルでは、分岐命令が完了する。 INH_SET_FORCE_BR_COMP信号102が生成されない場合、BR_COMP信号105の生成を待たずに、TOQ-CSEの分岐命令の完了を示すTOQ_BR_COMP信号107が生成される。分岐命令の完了に伴い、分

岐命令の完了を示すBR_COMP信号105が生成される。BR_TAKEN信号108等を基にWRITE信号が作成される。第10サイクルでは、WRITE信号を基に、各資源の更新信号が資源の

更新を行う。

1を基にTOQ_BR_COMP信号107のセット信号が生成される(S142)。第9サイクル

では、TOQ_BR_COMP信号107を受信したCSE9がTOQ_BR_COMMIT信号111を生成する。

また、分岐命令がTOQ-CSEの場合、EU命令やFCH命令ではないので、TOQ_EU_COMMIT信号1

12とTOQ_FCH_COMMIT信号113が生成される。TOQ_BR_COMMIT信号111、TOQ_EU_COMMIT信号112、TOQ_FCH_COMMIT信号113の各信号をAND演算し、TOQ_COMMIT信号110

が生成される。資源の更新情報が、RSBR8からWRITE信号生成回路20に送信される。資

源の更新情報としては、BR_TAKEN信号108等が例示される。WRITE信号生成回路20は

、TOQ_COMMIT信号110とRSBR8から受信した更新情報を合わせてWRITE信号を生成する

(S143)。第10サイクルでは分岐命令が完了し、WRITE信号を基に資源の更新が行

われる(S144)。

了しない場合がある。分岐命令が所定のサイクルで完了しない場合、分岐命令COMMIT高速化回路22は、SET_FORCE_BR_COMP信号101を生成してはいけない。この場合、抑止信

号生成回路23は、SET_FORCE_BR_COMP信号101の生成を抑止する抑止信号を生成する

。INH_SET_FORCE_BR_COMP信号102は、抑止信号の例示である。その結果、TOQ_BR_COMMIT信号111は、RSBR8からのBR_COMP信号105を待って生成される。

。TOQ-IID、subcc命令(IID=0x10)、CC(EU->IU)、後続分岐命令(IID=0x11)の項目の意味については、図3の場合と同様であるので、説明は省略する。

命令COMMIT高速化回路22は、SET_FORCE_BR_COMP信号を生成しない。第9サイクル以降

の処理は、図5と同様のため、説明を省略する。

路22は、SET_FORCE_BR_COMP信号101を生成しない(S161)。そのため、TOQ-CSEになった後続分岐命令は、RSBR8からのBR_COMP信号105を待ってから完了する(S1

62)。第9サイクル以降の処理は、図6と同様のため、説明を省略する。

実施形態1及び変形例1では、スレッドの切り替えが発生しないプロセッサに対して本案を適用した。変形例2では、Simultaneous Multithreading(SMT)機能を有するプロセッサに本案を適用する構成を例示する。SMTとは、単一プロセッサによって複数のスレッ

ドを同時に実行する機能の例示である。SMT機能を有するプロセッサに本案を用いるには

、抑止信号生成回路23が抑止信号を生成する条件を追加すればよい。変形例2では、1サイクルにひとつのスレッドを選択して、COMMIT処理を行う構成を例示する。この場合、前後のサイクルで処理を行うスレッドが異なる場合が考えられる。スレッドが異なると実行している命令も異なる事が考えられる。そのため、異なるスレッドのSET_FORCE_BR_COMP信号101を用いてTOQ_BR_COMP信号107を生成できない。そこで、スレッドの切り替えを検出した場合、抑止信号生成回路23は分岐命令COMMIT高速化回路22の動作を抑止する。したがって、CSE9の完了処理回路9Bは、RSBR8から送信されるBR_COMP信号105を待ってCOMMIT処理を行う。

を例示した図である。図17を参照して、変形例2で追加した抑止条件を説明する。図1

7に記載されている(1)〜(3)の抑止条件は、変形例1において所定のサイクルで分岐命令が完了できない場合として例示した(1)〜(3)にそれぞれ対応する。図17において、NEXT_U_STRAND_ID信号117は、次にUサイクル完了処理を行うスレッドを示し

ている。変形例2では、スレッドの数が2本の場合を例示する。すなわち、この場合、NEXT_U_STRAND_ID信号117の値は、例えば、0または1となる。NEXT_U_STRAND_ID信号117は、NEXT_U_STRAND_ID_1TD値118としてラッチ24eに保存される。ラッチ24eは、スレッド管理部の例示である。現在のサイクルのNEXT_U_STRAND_ID信号117の値と、ラッチ24eに保存された1サイクル前のNEXT_U_STRAND_ID_1TD信号118との値が異なれば、スレッドが切り替わっている。NEXT_U_STRAND_ID信号117とNEXT_U_STRAND_ID_1TD信号118は、スレッド識別子の例示である。スレッドの切り替えがあった場合、XOR回路116は、抑止信号をOR回路115cに出力する。OR回路115cは、INH_SET_FORCE_BR_COMP信号102(図17では、INHと省略)を生成する。このスレッドの切り替え

を検知する仕組みは、所定の条件信号の例示である。

ロセッサに対しても本案を適用できる。

<付記>

本実施の形態は、以下の態様(付記と呼ぶ)を含む。各付記の構成は、他の付記の構成を組み合わせることができる。

実行待ち分岐命令が蓄積され、分岐命令の分岐条件が確定すると実行される分岐命令の完了を管理する分岐命令実行管理部と、

プログラムの実行順に完了処理待ちの命令の識別子が蓄積される完了処理待ち記憶部と、

前記識別子で特定される命令の実行完了報告を前記分岐命令実行管理部から受けて、前記分岐命令の実行に伴う資源の更新処理を起動する完了処理部と、

前記完了処理待ち記憶部の先頭に蓄積された識別子が分岐命令である場合に、前記分岐命令の完了報告を待たず、前記完了処理部による資源の更新処理を起動する促進部と、

を備える演算処理装置。

所定の条件信号を受けて前記促進部の動作を抑止する抑止部、

をさらに備える付記1に記載の演算処理装置。

前記所定の条件信号は、前記分岐命令実行管理部からの分岐命令の分岐予測ミスを通知する信号である、

付記2に記載の演算処理装置。

前記所定の条件信号は、前記分岐命令実行管理部からの分岐命令の種類を通知する信号である、

付記2または付記3に記載の演算処理装置。

前記演算処理装置は、複数のスレッドを並行して実行する演算処理装置であり、

前記スレッドを識別するスレッド識別子を保持するスレッド管理部をさらに備え、

前記所定の条件信号は、現在のスレッドのスレッド識別子が、前記スレッド管理部に保持された前記スレッド識別子と異なっている場合に送信される信号である、

付記2乃至付記4のいずれか一項に記載の演算処理装置。

実行待ち分岐命令が蓄積され、分岐命令の分岐条件が確定すると実行される分岐命令の完了を管理する分岐命令実行管理部と、プログラムの実行順に完了処理待ちの命令の識別子が蓄積される完了処理待ち記憶部とを有する演算処理装置の制御方法において、

前記演算処理装置が有する完了処理部が、前記識別子で特定される命令の実行完了報告を前記分岐命令実行管理部から受けて、前記分岐命令の実行に伴う資源の更新処理を起動し、

前記演算処理装置が有する促進部が、前記完了処理待ち記憶部の先頭に蓄積された識別子が分岐命令である場合に、前記分岐命令の完了報告を待たず、前記完了処理部による資源の更新処理を起動する、

演算処理装置の制御方法。

2・・・分岐予測機構

3・・・一次命令キャッシュ

4・・・命令デコーダ

5・・・RSA

6・・・RSE

7・・・RSF

8・・・RSBR

9・・・CSE

9A・・・CSEのキュー

9B・・・CSEの完了処理回路

10・・・オペランドアドレス生成器

11・・・一次キャッシュデータ

12・・・演算器

13・・・固定小数点更新バッファ

14・・・浮動小数点更新バッファ

15・・・固定小数点レジスタ

16・・・浮動小数点レジスタ

17・・・NEXT Program Counter(NEXT PC)

18・・・Program Counter(PC)

19・・・CCレジスタ

20・・・WRITE信号生成回路

22・・・分岐命令COMMIT高速化回路

23・・・抑止信号生成回路

24a〜24e・・・ラッチ

25・・・セレクタ

101・・・SET_FORCE_BR_COMP信号

101a・・・FORCE_BR_COMP信号

102・・・INH_SET_FORCE_BR_COMP信号(INH信号)

103・・・BR_USE信号

104・・・TOQ_BR_USE信号

105・・・BR_COMP信号

106・・・TOQ_BR_COMP_SEL信号

107・・・TOQ_BR_COMP信号

108・・・BR_TAKEN信号

109・・・TOQ_BR_TAKEN信号

110・・・TOQ_COMMIT信号

111・・・TOQ_BR_COMMIT信号

112・・・TOQ_EU_COMMIT信号

113・・・TOQ_FCH_COMMIT信号

114a〜114d・・・AND回路

115a〜115c・・・OR回路

116・・・XOR回路

117・・・NEXT_U_STRAND_ID信号

118・・・NEXT_U_STRAND_ID_1TD信号

Claims (4)

- 実行待ち分岐命令が蓄積され、分岐命令の分岐条件が確定すると実行される分岐命令の完了を管理する分岐命令実行管理部と、

プログラムの実行順に完了処理待ちの命令の識別子が蓄積される完了処理待ち記憶部と、

前記識別子で特定される命令の実行完了報告を前記分岐命令実行管理部から受けて、前記分岐命令の実行に伴う資源の更新処理を起動する完了処理部と、

前記完了処理待ち記憶部の先頭に蓄積された識別子が分岐命令である場合に、前記分岐命令の完了報告を待たず、前記完了処理部による資源の更新処理を起動する促進部と、

を備える演算処理装置。 - 所定の条件信号を受けて前記促進部の動作を抑止する抑止部、

をさらに備える請求項1に記載の演算処理装置。 - 前記演算処理装置は、複数のスレッドを並行して実行する演算処理装置であり、

前記スレッドを識別するスレッド識別子を保持するスレッド管理部をさらに備え、

前記所定の条件信号は、現在のスレッドのスレッド識別子が、前記スレッド管理部に保持された前記スレッド識別子と異なっている場合に送信される信号である、

請求項2に記載の演算処理装置。 - 実行待ち分岐命令が蓄積され、分岐命令の分岐条件が確定すると実行される分岐命令の完了を管理する分岐命令実行管理部と、プログラムの実行順に完了処理待ちの命令の識別子が蓄積される完了処理待ち記憶部とを有する演算処理装置の制御方法において、

前記演算処理装置が有する完了処理部が、前記識別子で特定される命令の実行完了報告を前記分岐命令実行管理部から受けて、前記分岐命令の実行に伴う資源の更新処理を起動し、

前記演算処理装置が有する促進部が、前記完了処理待ち記憶部の先頭に蓄積された識別子が分岐命令である場合に、前記分岐命令の完了報告を待たず、前記完了処理部による資源の更新処理を起動する、

演算処理装置の制御方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013167781A JP6098429B2 (ja) | 2013-08-12 | 2013-08-12 | 演算処理装置及び演算処理装置の制御方法 |

| EP14179013.9A EP2843544A2 (en) | 2013-08-12 | 2014-07-29 | Arithmetic processing unit and method for controlling arithmetic processing unit |

| US14/447,682 US20150046689A1 (en) | 2013-08-12 | 2014-07-31 | Arithmetic processing unit and method for controlling arithmetic processing unit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013167781A JP6098429B2 (ja) | 2013-08-12 | 2013-08-12 | 演算処理装置及び演算処理装置の制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015036855A JP2015036855A (ja) | 2015-02-23 |

| JP6098429B2 true JP6098429B2 (ja) | 2017-03-22 |

Family

ID=51300529

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013167781A Expired - Fee Related JP6098429B2 (ja) | 2013-08-12 | 2013-08-12 | 演算処理装置及び演算処理装置の制御方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20150046689A1 (ja) |

| EP (1) | EP2843544A2 (ja) |

| JP (1) | JP6098429B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6314620B2 (ja) * | 2014-04-11 | 2018-04-25 | 富士通株式会社 | 演算処理装置および演算処理装置の制御方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0740226B2 (ja) * | 1987-08-04 | 1995-05-01 | 富士通株式会社 | 分岐命令制御方式 |

| US5487156A (en) * | 1989-12-15 | 1996-01-23 | Popescu; Valeri | Processor architecture having independently fetching issuing and updating operations of instructions which are sequentially assigned and stored in order fetched |

| JPH0820950B2 (ja) * | 1990-10-09 | 1996-03-04 | インターナショナル・ビジネス・マシーンズ・コーポレイション | マルチ予測型分岐予測機構 |

| US5884059A (en) * | 1996-01-26 | 1999-03-16 | Advanced Micro Devices, Inc. | Unified multi-function operation scheduler for out-of-order execution in a superscalar processor |

| JP3709933B2 (ja) | 2002-06-18 | 2005-10-26 | 日本電気株式会社 | 分岐予測による分岐命令高速化方法、およびプロセッサ |

| JP3808013B2 (ja) * | 2002-07-05 | 2006-08-09 | 富士通株式会社 | 命令実行装置 |

| EP2416250B1 (en) * | 2009-03-30 | 2014-08-27 | Fujitsu Limited | Prefetch request circuit |

| JP5861354B2 (ja) * | 2011-09-22 | 2016-02-16 | 富士通株式会社 | 演算処理装置及び演算処理装置の制御方法 |

-

2013

- 2013-08-12 JP JP2013167781A patent/JP6098429B2/ja not_active Expired - Fee Related

-

2014

- 2014-07-29 EP EP14179013.9A patent/EP2843544A2/en not_active Withdrawn

- 2014-07-31 US US14/447,682 patent/US20150046689A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015036855A (ja) | 2015-02-23 |

| US20150046689A1 (en) | 2015-02-12 |

| EP2843544A2 (en) | 2015-03-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100234648B1 (ko) | 프로세서내 인스트럭션 실행 방법 및 시스템과 데이타 처리 시스템 | |

| US6542921B1 (en) | Method and apparatus for controlling the processing priority between multiple threads in a multithreaded processor | |

| US8099586B2 (en) | Branch misprediction recovery mechanism for microprocessors | |

| US10318296B2 (en) | Scheduling execution of instructions on a processor having multiple hardware threads with different execution resources | |

| US10176104B2 (en) | Instruction predecoding | |

| US7734897B2 (en) | Allocation of memory access operations to memory access capable pipelines in a superscalar data processing apparatus and method having a plurality of execution threads | |

| JP2006040142A (ja) | プロセッサシステムおよびスレッド切り替え制御方法 | |

| US20080005544A1 (en) | Method and apparatus for partitioned pipelined execution of multiple execution threads | |

| US10853072B2 (en) | Arithmetic processing apparatus and method of controlling arithmetic processing apparatus | |

| US10776123B2 (en) | Faster sparse flush recovery by creating groups that are marked based on an instruction type | |

| US20080005534A1 (en) | Method and apparatus for partitioned pipelined fetching of multiple execution threads | |

| JP7064134B2 (ja) | 演算処理装置及び演算処理装置の制御方法 | |

| EP2159691B1 (en) | Simultaneous multithreaded instruction completion controller | |

| US20080244244A1 (en) | Parallel instruction processing and operand integrity verification | |

| JP6098429B2 (ja) | 演算処理装置及び演算処理装置の制御方法 | |

| JP7064135B2 (ja) | 演算処理装置及び演算処理装置の制御方法 | |

| US20100100709A1 (en) | Instruction control apparatus and instruction control method | |

| JP2001060152A (ja) | 分岐予測を抑止する情報処理装置および方法 | |

| JP2020077333A (ja) | 演算処理装置および演算処理装置の制御方法 | |

| US20070162723A1 (en) | Technique for reducing traffic in an instruction fetch unit of a chip multiprocessor | |

| US5737562A (en) | CPU pipeline having queuing stage to facilitate branch instructions | |

| US10929137B2 (en) | Arithmetic processing device and control method for arithmetic processing device | |

| JP5093237B2 (ja) | 命令処理装置 | |

| US10318303B2 (en) | Method and apparatus for augmentation and disambiguation of branch history in pipelined branch predictors | |

| JPWO2012132214A1 (ja) | プロセッサ及びその命令処理方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160510 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161227 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170124 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170206 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6098429 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |