JP6069918B2 - シミュレーション方法及びデバイスシミュレータ - Google Patents

シミュレーション方法及びデバイスシミュレータ Download PDFInfo

- Publication number

- JP6069918B2 JP6069918B2 JP2012153970A JP2012153970A JP6069918B2 JP 6069918 B2 JP6069918 B2 JP 6069918B2 JP 2012153970 A JP2012153970 A JP 2012153970A JP 2012153970 A JP2012153970 A JP 2012153970A JP 6069918 B2 JP6069918 B2 JP 6069918B2

- Authority

- JP

- Japan

- Prior art keywords

- gate

- potential

- current

- charge

- simulation method

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

[実施例1]

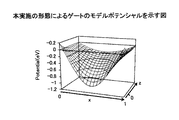

図16は、ゲート長16原子、chainは32原子の場合を示す図である。図16において、ゲート長が16原子分の長さの場合を示している。ゲート長16原子、chainは32原子の場合における、モデルポテンシャルを図16(A)に示し、誘起電荷を図16(B)に示す。リード長は、これ以上長くてもよく、誘起電荷は、現実の誘起電荷に対応し、同じ結果を示す。

[実施例2]

図17は、ダブルゲート構造の場合を示す図である。図17では、カーボンチェーンの反対側にも面電荷があるものとし、上述した数2のポテンシャルを重ね合わせたもので、ダブルゲート構造を模している。このようなダブルゲート構造における、モデルポテンシャルを図17(A)に示し、誘起電荷を図17(B)に示す。ダブルゲートの効果により、図16と比較して2倍程度の電荷が誘起されていることが分かる。

[実施例3]

図17のダブルゲート構造の場合で、面電荷間の間隔をひろげ、カーボンチェーンを2本配置することもできる。2本のカーボンチェーンに同じ電荷が誘起されていることが分かり、チャネル層が厚みをもっていても、即ち、厚み方向に2以上のカーボンチェーンを持っていても、この方法が適用できる。

[実施例4]

実施例2のダブルゲート構造の場合は、面電荷の電荷密度が1013cm−2であった。電荷密度を変化させることで、それに応じて誘起される電荷を制御することができる。図19は、図17のダブルゲート構造の場合で、面電荷の密度を変化させた場合の誘起電荷を示す図である。図19において、数値は、chainの中央の原子に誘起された電荷の量を示している。

(付記1)

コンピュータによって実行されるシミュレーション方法であって、

記憶部に記憶されたデバイスの構造モデルを読み込み、

非平衡グリーン関数法による量子伝導計算において、1方向に無限長であって他方に前記構造モデルで与えられるゲート幅で端を持つ面電荷がつくる解析的なポテンシャルを、伝導方向に垂直な2方向に周期的な形で加えて、電流を計算する

ことを特徴とするシミュレーション方法。

(付記2)

上記ポテンシャルは、周期的であるが連続でなく飛びがあることを特徴とする付記1記載のシミュレーション方法。

(付記3)

前記構造モデルによって表される原子構造に真空層を設け、該真空層において前記飛びをもつことを特徴とする付記2記載のシミュレーション方法。

(付記4)

2以上の面電荷によって前記ポテンシャルが重ねられることを特徴とする付記1乃至3のいずれか一項記載のシミュレーション方法。

(付記5)

前記構造モデルは、前記ポテンシャルの平坦な領域に厚みのある伝導層の原子構造を有することを特徴とする付記4記載のシミュレーション方法。

(付記6)

デバイスの構造モデルを記憶した記憶部と、

非平衡グリーン関数法による量子伝導計算を行う際に、1方向に無限長であって他方に前記記憶部に記憶された前記構造モデルで与えられるゲート幅で端を持つ面電荷がつくる解析的なポテンシャルを、伝導方向に垂直な2方向に周期的な形で加えて、電流を計算する特性計算部と

を有することを特徴とするデバイスシミュレータ。

(付記7)

記憶部に記憶されたデバイスの構造モデルを読み込み、

非平衡グリーン関数法による量子伝導計算において、1方向に無限長であって他方に前記構造モデルで与えられるゲート幅で端を持つ面電荷がつくる解析的なポテンシャルを、伝導方向に垂直な2方向に周期的な形で加えて、電流を計算する

ことを特徴とするシミュレーション方法。

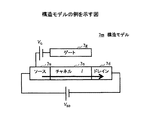

7d ドレイン

7g ゲート

7s ソース

7m 構造モデル

11 CPU

12 主記憶装置

13 補助記憶装置

14 入力装置

15 表示装置

16 出力装置

17 通信I/F

18 ドライブ

19 記憶媒体

21 原子座標入力部

22 ゲートデータ入力部

23 電流電圧特性計算部

31 原子座標データ

32 ゲートデータ

33 計算結果

100 デバイスシミュレータ

130 記憶部

Claims (5)

- コンピュータによって実行されるシミュレーション方法であって、

記憶部に記憶されたデバイスの構造モデルを読み込み、

非平衡グリーン関数法によるソースとドレイン間のチャネルを流れる電流の量子伝導計算において、伝導方向に垂直な2方向のうち1方向に無限長であって他方に垂直であり前記構造モデルで与えられるチャネルに対向するゲートのゲート幅で端を持つ面電荷がつくる解析的なポテンシャルを、該伝導方向に垂直な2方向に周期的な形で加えて、電流を計算する

ことを特徴とするシミュレーション方法。 - 上記ポテンシャルは、周期的であるが連続でなく飛びがあることを特徴とする請求項1記載のシミュレーション方法。

- 前記構造モデルによって表される原子構造に真空層を設け、該真空層において前記飛びをもつことを特徴とする請求項2記載のシミュレーション方法。

- 2以上の面電荷によって前記ポテンシャルが重ねられることを特徴とする請求項1乃至3のいずれか一項記載のシミュレーション方法。

- デバイスの構造モデルを記憶した記憶部と、

非平衡グリーン関数法によるソースとドレイン間のチャネルを流れる電流の量子伝導計算を行う際に、伝導方向に垂直な2方向のうち1方向に無限長であって他方に前記記憶部に記憶された前記構造モデルで与えられるチャネルに対向するゲートのゲート幅で端を持つ面電荷がつくる解析的なポテンシャルを、該伝導方向に垂直な2方向に周期的な形で加えて、電流を計算する特性計算部と

を有することを特徴とするデバイスシミュレータ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012153970A JP6069918B2 (ja) | 2012-07-09 | 2012-07-09 | シミュレーション方法及びデバイスシミュレータ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012153970A JP6069918B2 (ja) | 2012-07-09 | 2012-07-09 | シミュレーション方法及びデバイスシミュレータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014017382A JP2014017382A (ja) | 2014-01-30 |

| JP6069918B2 true JP6069918B2 (ja) | 2017-02-01 |

Family

ID=50111819

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012153970A Expired - Fee Related JP6069918B2 (ja) | 2012-07-09 | 2012-07-09 | シミュレーション方法及びデバイスシミュレータ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6069918B2 (ja) |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3660137B2 (ja) * | 1998-09-25 | 2005-06-15 | 株式会社東芝 | シミュレーション方法、シミュレータ、シミュレーションプログラムを記録した記録媒体および半導体装置の製造方法 |

-

2012

- 2012-07-09 JP JP2012153970A patent/JP6069918B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014017382A (ja) | 2014-01-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| Anagnostopoulos et al. | Corona discharge simulation in wire-duct electrostatic precipitator | |

| CN109074512A (zh) | 使用神经网络压缩图像 | |

| JP2023533631A (ja) | ハードウェア用に最適化されたニューラルアーキテクチャ検索 | |

| US11023639B2 (en) | Systems and methods for providing approximate electronic-structure models from calculated band structure data | |

| Marin et al. | Analytic potential and charge model for III-V surrounding gate metal-oxide-semiconductor field-effect transistors | |

| CN113168555A (zh) | 减少卷积神经网络的资源消耗的系统及相关方法 | |

| KR102400557B1 (ko) | 알티에스(rts) 노이즈를 고려한 회로 설계 방법 및 시뮬레이션 방법 | |

| KR101213268B1 (ko) | 시뮬레이션 방법 및 시뮬레이션 장치 | |

| Lee et al. | Device simulations with a U-Net model predicting physical quantities in two-dimensional landscapes | |

| Choi et al. | Enhancement and expansion of the neural network-based compact model using a binning method | |

| Jiang et al. | Accuracy of the Frensley inflow boundary condition for Wigner equations in simulating resonant tunneling diodes | |

| JP6069918B2 (ja) | シミュレーション方法及びデバイスシミュレータ | |

| JP6108519B2 (ja) | ドレイン電流のシミュレーション装置及びドレイン電流のシミュレーションプログラム | |

| JP6992534B2 (ja) | データ作成装置、誘導モデル学習装置、誘導推定装置、データ作成方法、誘導モデル学習方法、誘導推定方法及びプログラム | |

| US8122406B2 (en) | Generating models for integrated circuits with sensitivity-based minimum change to existing models | |

| Gerstenmayer et al. | Comparison of a finite-element and finite-volume scheme for a degenerate cross-diffusion system for ion transport: A. Gerstenmayer, A. Jüngel | |

| Barraud | Dissipative quantum transport in silicon nanowires based on Wigner transport equation | |

| KR100230466B1 (ko) | 반도체 소자의 수치해석에 사용하기 위한 소자 시뮬레이션 방법 | |

| US20100125442A1 (en) | Model parameter extracting apparatus and model parameter extracting program for semiconductor device model | |

| US8515715B2 (en) | Method, system and program storage device for simulating electronic device performance as a function of process variations | |

| JP2011205034A (ja) | イオン注入分布発生方法及びシミュレータ | |

| Li | A two-dimensional thin-film transistor simulation using adaptive computing technique | |

| Amoroso et al. | Statistical Study of Bias Temperature Instabilities by Means of 3D “Atomistic” Simulation | |

| Vellasques et al. | A dual-purpose memory approach for dynamic particle swarm optimization of recurrent problems | |

| Li et al. | Fast inverse using nested dissection for NEGF |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150406 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160705 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160902 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20161206 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20161219 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6069918 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |