JP5975791B2 - Image processing apparatus and method, and image display apparatus and method - Google Patents

Image processing apparatus and method, and image display apparatus and method Download PDFInfo

- Publication number

- JP5975791B2 JP5975791B2 JP2012186484A JP2012186484A JP5975791B2 JP 5975791 B2 JP5975791 B2 JP 5975791B2 JP 2012186484 A JP2012186484 A JP 2012186484A JP 2012186484 A JP2012186484 A JP 2012186484A JP 5975791 B2 JP5975791 B2 JP 5975791B2

- Authority

- JP

- Japan

- Prior art keywords

- frame

- data

- reduced

- motion vector

- block

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Controls And Circuits For Display Device (AREA)

- Image Analysis (AREA)

- Television Systems (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Description

本発明は、画像処理装置及び方法、並びに画像表示装置及び方法に関する。本発明は特に、画像のフレーム間に新たな補間フレームを挿入するフレーム補間処理に関するものである。 The present invention relates to an image processing apparatus and method, and an image display apparatus and method. The present invention particularly relates to a frame interpolation process for inserting a new interpolation frame between frames of an image.

液晶ディスプレイなどのホールド型ディスプレイは、1フレーム期間同じ画像を表示し続けており、画像中の物体が動いた場合に、動く物体に対する人間の目の追従が連続的に移動するのに対して、物体の移動が1フレーム単位の不連続な移動を行っているためにエッジ部分がぼやけて見える問題がある。これに対し、フレームを補間することで表示フレーム数を多くして物体の移動をスムーズにすることが考えられる。 A hold-type display such as a liquid crystal display continues to display the same image for one frame period, and when the object in the image moves, the tracking of the human eye to the moving object moves continuously, There is a problem that the edge portion looks blurry because the object moves discontinuously in units of one frame. On the other hand, it is conceivable to increase the number of display frames by interpolating frames to make the object move smoothly.

また、映画などのフィルム映像がテレビ信号に変換された素材については、両者(フィルム映像とテレビ信号)のフレーム周波数の違いから、2フレーム又は3フレームが同じフレームから作られた画像信号となっており、そのまま表示すると、動きがぼやけたり、動きがギクシャクしたジャダーが発生したりする問題がある。 In addition, for a material in which a film image such as a movie is converted into a TV signal, two or three frames are image signals made from the same frame because of the difference in frame frequency between the two (film image and TV signal). However, if displayed as it is, there is a problem that the motion is blurred or judder with a jerky motion occurs.

また、同様にコンピュータ処理された映像がテレビ信号に変換された素材についても、2フレームが同じフレームから作られた画像信号であり、そのまま表示すると同様にジャダーが発生する問題がある。 Similarly, for a material in which computer-processed video is converted into a television signal, two frames are image signals made from the same frame, and there is a problem that judder occurs similarly when displayed as it is.

従来の画像処理装置及び方法は、補間フレームに対して1フレーム前のフレームと同じ画像で補間する零次ホールド法か、補間フレームに対して1フレーム前の画像と1フレーム後の画像の平均画像で補間する平均値補間法などがあるが、零次ホールド法は、一定方向に動く画像に対して、滑らかな移動をしないので、依然ホールド型ディスプレイのぼやけの問題は解決されない。また、平均値補間法は、動いた画像が2重像になる問題がある。 The conventional image processing apparatus and method are either a zero-order hold method in which interpolation is performed with the same image as the previous frame with respect to the interpolation frame, or an average image of the previous image and the subsequent image with respect to the interpolation frame. However, since the zero-order hold method does not move smoothly with respect to an image moving in a certain direction, the problem of blurring of the hold type display is still not solved. Further, the average value interpolation method has a problem that a moving image becomes a double image.

この改善策として、補間フレームの補間画素に対して点対称の位置にある時間的に前のフレーム上の画素と時間的に後のフレーム上の画素との画素間の相関が最も大きい画素から補間フレームの補間画素を生成するものがある(例えば、特許文献1参照)。この方法では、画素単位での相関検出のため、画像の内容が異なるにも拘らず、画素間の相関が大きいと検出される場合があり、正しく補間フレームが生成できない場合がある。 As an improvement measure, interpolation is performed from the pixel having the highest correlation between the pixels on the temporally previous frame and the temporally subsequent frame that are in point symmetry with respect to the interpolated pixel of the interpolated frame. Some generate interpolated pixels of a frame (see, for example, Patent Document 1). In this method, since correlation is detected in units of pixels, it may be detected that the correlation between pixels is large even though the contents of the image are different, and an interpolation frame may not be generated correctly.

従来のフレーム補間処理は、上記の様に構成されており、動きがぼやけたり、動きがギクシャクしたジャダーが発生したりする問題がある。また、画素単位の相関を検出する方法では、正しく相関検出ができないために正しく補間フレームが生成できず、特に補間するフレーム前後で物体が隠れたり出現したりする場合、補間フレームが著しく乱れるという問題、及びフレーム補間処理は演算量が多い(ハードウェアでは回路規模が大きい)という問題がある。 The conventional frame interpolation process is configured as described above, and there is a problem that motion is blurred or judder with motion is generated. In addition, in the method of detecting the correlation in pixel units, the interpolation frame cannot be generated correctly because the correlation cannot be detected correctly, and particularly when the object is hidden or appears before and after the frame to be interpolated, the interpolation frame is significantly disturbed. In addition, the frame interpolation processing has a problem that the calculation amount is large (the circuit scale is large in hardware).

本発明の画像処理装置は、

画像の現フレームと前記現フレームの1フレーム前のフレームである第1の遅延フレームとの間に補間フレームを挿入する画像処理装置において、

前記第1の遅延フレームのデータ及び前記現フレームの2フレーム前のフレームである第2の遅延フレームのデータを参照して前記第2の遅延フレームから前記第1の遅延フレームへの第1の動きベクトルを算出し、前記現フレームのデータ及び前記第1の遅延フレームのデータを参照して前記現フレームから前記第1の遅延フレームへの第2の動きベクトルを算出する動きベクトル検出部と、

前記第1の動きベクトルを前記第1の遅延フレームから前記補間フレームへの第3の動きベクトルに変換し、前記第2の動きベクトルを前記現フレームら前記補間フレームへの第4の動きベクトルに変換する動きベクトル変換部と、

前記第3の動きベクトル、前記第4の動きベクトル、前記第1の遅延フレームのデータ、及び前記現フレームのデータから、前記補間フレームのデータを生成し、前記補間フレームのデータを前記現フレームのデータと前記第1の遅延フレームのデータの間に挿入した画像データを出力する補間フレーム生成部とを有し、

前記動きベクトル検出部は、

前記現フレームを画素ごとにランダムに位相をずらして縮小して現縮小フレームを出力し、前記第1の遅延フレームを画素ごとにランダムに位相をずらして縮小して第1の縮小遅延フレームを出力し、前記第2の遅延フレームを画素ごとにランダムに位相をずらして縮小して第2の縮小遅延フレームを出力するディザ縮小部と、

前記現縮小フレーム、前記第1の縮小遅延フレーム及び前記第2の縮小遅延フレームから検出された動きベクトルを拡大して出力する動きベクトル拡大部とを有する

ことを特徴とする。

The image processing apparatus of the present invention

In an image processing apparatus for inserting an interpolation frame between a current frame of an image and a first delay frame which is a frame one frame before the current frame,

The first movement from the second delay frame to the first delay frame with reference to the data of the first delay frame and the data of the second delay frame which is a frame two frames before the current frame A motion vector detector that calculates a vector and calculates a second motion vector from the current frame to the first delay frame by referring to the data of the current frame and the data of the first delay frame;

The first motion vector is converted into a third motion vector from the first delay frame to the interpolation frame, and the second motion vector is converted into a fourth motion vector from the current frame to the interpolation frame. A motion vector conversion unit to convert,

The interpolation frame data is generated from the third motion vector, the fourth motion vector, the first delay frame data, and the current frame data, and the interpolation frame data is converted into the current frame data. An interpolation frame generator for outputting image data inserted between the data and the data of the first delay frame,

The motion vector detection unit

The current frame is reduced by shifting the phase at random for each pixel, and the current reduced frame is output. The first delayed frame is reduced by shifting the phase at every pixel, and the first reduced delay frame is output. A dither reduction unit that outputs the second reduced delay frame by reducing the phase of the second delayed frame at random for each pixel, and

And a motion vector expanding unit that expands and outputs a motion vector detected from the current reduced frame, the first reduced delay frame, and the second reduced delay frame.

本発明によれば、時間的に連続する3枚のフレームの中心のフレームを最も確からしいものとして、時間的に前のフレーム及び後のフレームから中心のフレームへの動きベクトルを評価することで高精度な動きベクトルを算出することができるため、画像の乱れなく補間フレームを内挿することができる。さらに補間するフレーム前後で物体が隠れたり出現したりする場合でも、画像の乱れなく補間フレームを内挿することができる。また、動きベクトルの検出に縮小画像を用いることで、演算量(回路規模)を削減することができる。さらにまた、ランダムに位相をずらし画像縮小処理を行うことで、縮小画像を用いることによる動きベクトルの検出精度の低下を抑制することができる。 According to the present invention, the center frame of three consecutive frames in time is most likely to be the most probable by evaluating the motion vector from the previous frame and the subsequent frame to the center frame in time. Since an accurate motion vector can be calculated, an interpolation frame can be interpolated without image distortion. Furthermore, even when an object is hidden or appears before and after the interpolated frame, the interpolated frame can be interpolated without image distortion. In addition, by using a reduced image for motion vector detection, the amount of computation (circuit scale) can be reduced. Furthermore, by performing the image reduction process by randomly shifting the phase, it is possible to suppress a decrease in detection accuracy of the motion vector due to the use of the reduced image.

以下、本発明の実施の形態を図面により説明する。本発明に係る画像処理装置は、入力動画像を構成するフレーム列のうちの現フレームと現フレームの1フレーム前のフレームとの間に新たな補間フレームを補間により生成するものであり、本発明に係る画像表示装置には、上記の画像処理装置から出力された画像データを表示する画像表示部を備えるものである。 Hereinafter, embodiments of the present invention will be described with reference to the drawings. The image processing apparatus according to the present invention generates a new interpolated frame by interpolation between a current frame in a frame sequence constituting an input moving image and a frame one frame before the current frame. The image display apparatus according to the present invention includes an image display unit that displays the image data output from the image processing apparatus.

図1は、本発明の実施の形態に係る画像表示装置の構成を示す図である。図示の画像表示装置は、画像処理装置10と、画像表示部15を備え、画像処理装置10は、フレームメモリ11と、動きベクトル検出部12と、動きベクトル変換部13と、補間フレーム生成部14と、画像表示部15を備える。

FIG. 1 is a diagram showing a configuration of an image display apparatus according to an embodiment of the present invention. The illustrated image display device includes an

この画像処理装置は、例えば、放送受信装置、画像記録再生装置、又はパーソナルコンピュータ(PC)などの一部を構成することができる。また、画像表示部15は、例えば、テレビ、映像プロジェクター、又はPCなどの一部を構成することができる。

This image processing apparatus can constitute a part of, for example, a broadcast receiving apparatus, an image recording / reproducing apparatus, or a personal computer (PC). Further, the

画像データF0が、フレームメモリ11、動きベクトル検出部12、及び補間フレーム生成部14に入力される。

フレームメモリ11は、入力動画像の現フレームの画像を表す画像データF0を2フレーム分保存し、画像データF0に対して1フレーム分遅延した画像データF1と、画像データF0に対して2フレーム分遅延した画像データF2を出力する。これより画像データF0を現フレームのデータ、画像データF1を第1の遅延フレームのデータ、画像データF2を第2の遅延フレームのデータと言う。また、現フレーム、第1の遅延フレーム、第2の遅延フレームをそれぞれのフレームデータと同じ符号F0、F1、F2で表す。

The image data F0 is input to the

The

第1の遅延フレームF1のデータは動きベクトル検出部12と補間フレーム生成部14に入力され、第2の遅延フレームF2のデータは動きベクトル検出部12に入力される。

The data of the first delay frame F1 is input to the motion

動きベクトル検出部12は、現フレームF0のデータと、第1の遅延フレームF1のデータと、第2の遅延フレームF2のデータを参照して、第1の遅延フレームF1上の複数のブロックの各々(フレームの一部を成す、複数の画素で構成される)を順次選択し、選択されているブロックについて、第2の遅延フレームF2から第1の遅延フレームF1への第1の動きベクトルMV1及び現フレームF0から第1の遅延フレームF1への第2の動きベクトルMV2を算出して、動きベクトル変換部13に出力する。第1の遅延フレームF1上のブロックは、第1の遅延フレームF1を例えば複数の矩形の領域に分割することで得られるものである。

The motion

動きベクトル変換部13は、第1の動きベクトルMV1と第2の動きベクトルMV2を、第1の遅延フレームF1から補間フレームIFへの第3の動きベクトルMV3と、現フレームF0から補間フレームIFへの第4の動きベクトルMV4に変換して、補間フレーム生成部14に出力する。

The motion

補間フレーム生成部14は、第1の遅延フレームF1のデータ、現フレームF0のデータ、第3の動きベクトルMV3及び第4の動きベクトルMV4から、現フレームF0と第1の遅延フレームF1の間に位置する補間フレームIFのデータを生成し、生成した補間フレームIFのデータを現フレームF0のデータと第1の遅延フレームF1のデータの間に挿入したフレーム列で構成される画像データDOを画像表示部15に出力する。

画像表示部15は、画像データDOを表示する。

The interpolated

The

次に、動きベクトル検出部12の構成について詳細に説明する。

動きベクトル検出部12は、ディザ縮小部2と、ブロック切り出し部3と、テスト補間部4と、補間データ評価部5と、動きベクトル決定部6と、動きベクトル拡大部7とを有し、ディザ縮小部2は、現フレームディザ縮小部21と、第1の遅延フレームディザ縮小部22と、第2の遅延フレームディザ縮小部23とを有し、ブロック切り出し部3は、現フレームブロック切り出し部31と、第1の遅延フレームブロック切り出し部32と、第2の遅延フレームブロック切り出し部33とを有する。

Next, the configuration of the motion

The motion

現フレームディザ縮小部21は、現フレームF0の画像を縮小して現縮小フレームSF0を出力し、第1の遅延フレームディザ縮小部22は、第1の遅延フレームF1の画像を縮小して第1の縮小遅延フレームSF1を出力し、第2の遅延フレームディザ縮小部23は、第2の遅延フレームF2の画像を縮小して第2の縮小遅延フレームSF2を出力する。現フレームディザ縮小部21、第1の遅延フレームディザ縮小部22、及び第2の遅延フレームディザ縮小部23における縮小率は同じであり、符号αで表される。

The current frame

ディザ縮小部21、22、23の各々におけるディザ縮小について説明する。最初に縮小を一次元にのみ行うものとして説明する。

画像を一次元方向に1/4に縮小する場合、一般的には縮小の方向に並んだ4個ずつの画素から成る群に分ける。即ち、点線Gaで囲って示すように、互いに近くにある4個の画素ごとに画素群を形成する。そして、各群の画素の単純な平均値あるいは左右対称な重み付け平均値を算出し、上記の4個の画素から成る群の中心(図2(a)で位相PH2と示した位置)に、算出した平均値の画素を配置した画像を縮小画像とする。

The dither reduction in each of the

When the image is reduced to ¼ in the one-dimensional direction, it is generally divided into a group of four pixels arranged in the reduction direction. That is, as indicated by a dotted line Ga, a pixel group is formed for every four pixels close to each other. Then, a simple average value or a bilaterally weighted average value of the pixels of each group is calculated, and calculated at the center of the group of the above four pixels (the position indicated as phase PH2 in FIG. 2A). An image in which the average value pixels are arranged is defined as a reduced image.

ここで位相とは、元の画像において、各群を構成する4個の画素が占める空間を1周期と見たときの画像上の各周期内の位置を示す。図示の例では、位相PH0、PH1、PH2、PH3はそれぞれ、元の画像における各群の4個の画素の、画素間中心に位置する。縮小画像では、1個の画素で1周期を構成するので、位相PH0、PH1、PH2、PH3相互の間隔は、縮小画像の画素間距離の1/4となる。

図2(a)に示す例では、上記の4個の画素から成る群のいずれにおいても、同じ位相PH2の位置に、平均値を持つ画素が配置される。

Here, the phase indicates a position in each period on the image when a space occupied by four pixels constituting each group is regarded as one period in the original image. In the illustrated example, the phases PH0, PH1, PH2, and PH3 are each located at the center between the pixels of the four pixels in each group in the original image. In the reduced image, one pixel constitutes one cycle, and therefore the intervals between the phases PH0, PH1, PH2, and PH3 are ¼ of the inter-pixel distance of the reduced image.

In the example shown in FIG. 2A, pixels having an average value are arranged at the same phase PH2 in any of the groups of four pixels.

これに対してディザ縮小では出力する画素ごとに位相をランダムにずらした位置、例えば位相0から3に相当する画素のどれかを縮小画像の画素として出力する。ランダムに位置をずらす結果、例えば、図2(b)に示すように、群Ga(1)では位相PH1に、群Ga(3)では位相PH0に、群Ga(3)では位相PH2に、それぞれの群の平均を持つ画素が配置されることになる。従って、縮小画像においては、画素間の距離は一定ではなく、1から7までの範囲で変動する。ここで画素間距離は元の画像の画素ピッチで正規化された値で表されている。

On the other hand, in dither reduction, a position where the phase is randomly shifted for each pixel to be output, for example, one of pixels corresponding to

二次元に縮小を行う場合、水平方向と垂直方向ともにランダムの位相の組み合わせになる。即ち、画像を、それぞれ水平方向及び垂直方向に近接した位置にある画素から成る、複数の矩形領域に分割し、各矩形領域内の画素の平均値を持つ画素を、水平方向及び垂直方向の双方においてランダムに位相をずらした位置に配置した画素を縮小画像の画素とする。 When the reduction is performed two-dimensionally, a combination of random phases is obtained in both the horizontal and vertical directions. That is, the image is divided into a plurality of rectangular areas each composed of pixels located in the horizontal direction and the vertical direction, and pixels having an average value of the pixels in each rectangular area are displayed in both the horizontal direction and the vertical direction. The pixels arranged at the positions whose phases are randomly shifted in FIG.

なお、図2(b)では4つの画素から成る群の各々について求めた平均値を持つ画素を、4つの位相のいずれかに配置しているが、各群の画素の数(平均を求めるために用いた画素の数)よりも、平均値を持つ縮小画像上の画素が配置される位相の数を多くしても良い。これにより、縮小画像上の画素がより多様な位相配置パターンを持つことになる。二次元に縮小を行う場合も同様である。 In FIG. 2B, pixels having an average value obtained for each group of four pixels are arranged in any of the four phases, but the number of pixels in each group (to obtain the average) The number of phases in which the pixels on the reduced image having the average value are arranged may be larger than the number of pixels used in (1). Thereby, the pixels on the reduced image have more various phase arrangement patterns. The same applies when performing reduction in two dimensions.

現フレームブロック切り出し部31、第1の遅延フレームブロック切り出し部32、及び第2の遅延フレームブロック切り出し部33は、それぞれ、現縮小フレームSF0、第1の縮小遅延フレームSF1、及び第2の縮小遅延フレームSF2を受け、それぞれ、画面の一部を成すブロックを切り出し(抽出し)、ブロック内の画素のデータ(画素値)の集合をブロックデータとして出力する。即ち、現フレームブロック切り出し部31は、現縮小フレームSF0からブロックを切り出し、第1の遅延フレームブロック切り出し部32は、第1の縮小遅延フレームSF1からブロックを切り出し、第2の遅延フレームブロック切り出し部33は、第2の縮小遅延フレームSF2からブロックを切り出す。

The current frame

各ブロックは例えば横方向X個、縦方向Y個の画素(Y個のライン)のサイズを有する矩形の領域から成る。即ち、現縮小フレームSF0から切り出されるブロックと、第1の縮小遅延フレームSF1から切り出されるブロックと、第2の縮小遅延フレームSF2から切り出されるブロックは、縦方向のサイズ(画素数)及び横方向のサイズ(画素数乃至ライン数)が互いに等しい。 Each block is composed of a rectangular area having a size of, for example, X pixels in the horizontal direction and Y pixels (Y lines) in the vertical direction. That is, the block cut out from the current reduced frame SF0, the block cut out from the first reduced delay frame SF1, and the block cut out from the second reduced delay frame SF2 have a vertical size (number of pixels) and a horizontal direction. The size (number of pixels or number of lines) is equal to each other.

以下では、補間フレームIF内の一つのブロックを補間により生成するに当たっての処理を説明する。この処理のためには、補間フレームIF内の補間しようとするブロック(補間対象ブロック)を、縮小フレームSF0、SF1、SF2を生成する際と同じ縮小率αで縮小したブロック(縮小ブロック)に対応する、第1の縮小遅延フレームSF1内の一つのブロックF1Baを処理対象ブロックとして設定し、該処理対象ブロックF1Baと、現縮小フレームSF0内の複数のブロックと、第2の縮小遅延フレームSF2内の複数のブロックが切り出される(抽出される)。現縮小フレームSF0から切り出されるブロックと、第2の縮小遅延フレームSF2から切り出されるブロックとは、処理対象ブロックF1Ba(厳密には、その中心)を中心として点対称の位置にあるもので、これらが対として用いられる。

現フレームブロック切り出し部31及び第2の遅延フレームブロック切り出し部33は、処理対象ブロックF1Baを中心とし、互いに点対称の位置にあり、一方が現縮小フレームSF0内に位置し、他方が第2の縮小遅延フレームSF2内に位置するブロックの対を複数個切り出す。

Hereinafter, a process for generating one block in the interpolation frame IF by interpolation will be described. For this processing, the block (interpolation target block) to be interpolated in the interpolation frame IF corresponds to the block (reduced block) reduced at the same reduction ratio α as that when the reduced frames SF0, SF1, and SF2 are generated. One block F1Ba in the first reduced delay frame SF1 is set as a processing target block, the processing target block F1Ba, a plurality of blocks in the current reduced frame SF0, and a second reduced delay frame SF2 A plurality of blocks are cut out (extracted). The block cut out from the current reduced frame SF0 and the block cut out from the second reduced delay frame SF2 are in point-symmetrical positions around the processing target block F1Ba (strictly, the center), and these are Used as a pair.

The current frame

例えば、現縮小フレームSF0から切り出されるブロックF0B1(厳密には、その中心)と、第2の縮小遅延フレームSF2から切り出されるブロックF2B1(厳密には、その中心)とは、第1の縮小遅延フレームSF1内の処理対象ブロックF1Ba(厳密には、その中心)を中心として点対称の位置にあるもので、これらの点対称の位置にある2つのブロックが対(ペア)として用いられる。 For example, the block F0B1 (strictly the center) cut out from the current reduced frame SF0 and the block F2B1 (strictly the center) cut out from the second reduced delay frame SF2 are the first reduced delay frame. The processing target block F1Ba in SF1 (strictly, its center) is located at a point-symmetrical position, and two blocks at these point-symmetrical positions are used as a pair.

現縮小フレームSF0及び第2の縮小遅延フレームSF2から切り出されるブロックの対は、動きベクトル検出部12において検出される動きベクトルの候補に対応するものであり、例えば動きベクトルの探索範囲内のすべてのブロックが切り出される。例えば、第1の縮小遅延フレームSF1内の一つのブロックの中心を中心として、横方向に±HS画素、縦方向に±VS画素(±VSライン)の範囲を探索する場合、第2の縮小遅延フレームSF2及び現縮小フレームSF0から、それぞれ(2HS+1)×(2VS+1)個のブロックが切り出される。

The block pairs cut out from the current reduced frame SF0 and the second reduced delay frame SF2 correspond to the motion vector candidates detected by the motion

なお、探索範囲内のすべてのブロックについて評価を行う必要がない場合、例えば予め或いは他の情報により動きの方向の範囲が予測できる場合には、上記の探索範囲の予測される範囲内のブロックのみを切り出すこととしても良い。また、探索範囲内のブロックを間引きながら(例えば水平方向及び垂直方向に1画素おきに)切り出すこととしても良い。 In addition, when it is not necessary to evaluate all the blocks in the search range, for example, when the range of the motion direction can be predicted in advance or by other information, only the blocks in the predicted range of the search range are included. It is good also as cutting out. Alternatively, the blocks in the search range may be cut out while thinning out (for example, every other pixel in the horizontal direction and the vertical direction).

以下では、現縮小フレームSF0及び第2の縮小遅延フレームSF2から切り出されるブロックの数をMとし、現縮小フレームSF0から切り出されるブロックを第1乃至第MのブロックF0B1〜F0BM、第2の縮小遅延フレームSF2から切り出されるブロックを第1乃至第MのブロックF2B1〜F2BMと呼ぶ。また、各ブロックのデータをブロックと同じ符号で表す。 In the following, the number of blocks cut out from the current reduced frame SF0 and the second reduced delay frame SF2 is M, and the blocks cut out from the current reduced frame SF0 are the first to Mth blocks F0B1 to F0BM, the second reduced delay. The blocks cut out from the frame SF2 are referred to as first to Mth blocks F2B1 to F2BM. In addition, the data of each block is represented by the same code as the block.

第2の縮小遅延フレームSF2内の第mのブロックF2Bm(m=1〜M)と現縮小フレームSF0内の第mのブロックF0Bmとは、第1の縮小遅延フレームSF1内の処理対象ブロックF1Ba(厳密にはその中心の画素)を中心として点対称の位置にあるので、ブロックF2Bmの処理対象ブロックF1Baに対する横方向のずれをh(h=−HS〜+HS)、縦方向のずれをv(v=−VS〜+VS)とすると、ブロックF0Bmの処理対象ブロックF1Baに対する横方向のずれは−h、縦方向のずれは−vである。 The m-th block F2Bm (m = 1 to M) in the second reduced delay frame SF2 and the m-th block F0Bm in the current reduced frame SF0 are the processing target block F1Ba (in the first reduced delay frame SF1). Strictly speaking, since it is in a point-symmetrical position with respect to the center pixel), the horizontal shift of the block F2Bm with respect to the processing target block F1Ba is h (h = −HS to + HS), and the vertical shift is v (v = −VS to + VS), the horizontal shift of the block F0Bm with respect to the processing target block F1Ba is −h, and the vertical shift is −v.

現フレームブロック切り出し部31は、現縮小フレーム内の複数の、即ち第1乃至第Mのブロックを切り出して、第1乃至第MのブロックデータF0B1〜F0BMを出力する。

第1の遅延フレームブロック切り出し部32は、第1の縮小遅延フレーム内の処理対象ブロックF1Baを切り出す。このブロックF1Baは、補間フレームIF内の補間対象ブロックを縮小したブロックに対応するものである。

第2の遅延フレームブロック切り出し部33は、第2の縮小遅延フレーム内の複数の、即ち第1乃至第Mのブロックを切り出して、第1乃至第MのブロックデータF2B1〜F2BMを出力する。

The current frame

The first delay frame

The second delay frame

現縮小フレームSF0のブロックデータと第2の縮小遅延フレームSF2のブロックデータが、テスト補間部4に入力される。テスト補間部4は、第2の縮小遅延フレームSF2のブロックデータと現縮小フレームSF0のブロックデータのうち、処理対象ブロックF1Baを中心として、互いに点対称の位置にある第2の縮小遅延フレームSF2内のブロックと、現縮小フレームSF0内のブロックから成るブロック対のデータに基づいて、テスト補間データTDA1〜TDAMを生成する。複数のブロック対に基づいて複数のテスト補間データが生成される。このテスト補間は、上記点対称の中心の位置、即ち上記処理対象ブロックF1Baのデータが未知であると仮定して行うものであり、補間が正確であればあるほど、テスト補間データは、処理対象ブロックF1Baのデータとの相関が強いものとなる。

The block data of the current reduced frame SF0 and the block data of the second reduced delay frame SF2 are input to the

テスト補間部4は、さらに入力された現縮小フレームSF0のブロックデータをそのまま処理対象ブロックF1Baの位置のデータとしたものを、テスト補間データTDB1〜TDBMとして出力し、入力された第2の縮小遅延フレームSF2のブロックデータをそのまま処理対象ブロックF1Baの位置のデータとしたものを、テスト補間データTDC1〜TDCMとして出力する。

区別のため、テスト補間データTDA1〜TDAMは第1群の第1乃至第Mのテスト補間データと呼ばれ、テスト補間データTDB1〜TDBMは第2群の第1乃至第Mのテスト補間データと呼ばれ、テスト補間データTDC1〜TDCMは第3群の第1乃至第Mのテスト補間データと呼ばれる。

The

For the sake of distinction, the test interpolation data TDA1 to TDAM are referred to as the first group of first to Mth test interpolation data, and the test interpolation data TDB1 to TDBM are referred to as the second group of first to Mth test interpolation data. The test interpolation data TDC1 to TDCM are referred to as a third group of first to Mth test interpolation data.

補間データ評価部5は、第1の縮小遅延フレームSF1のブロックデータを参照して複数のテスト補間データの評価を行い、評価データEDを動きベクトル決定部6に出力する。この評価においては、テスト補間データと、第1の縮小遅延フレームSF1のブロックデータとの相関を求め、相関が強いほど高い評価が与えられる。

The interpolation

動きベクトル決定部6は、評価データEDに基づいて第1の縮小動きベクトルSMV1と第2の縮小動きベクトルSMV2を生成して出力する。

The motion

動きベクトル拡大部7は、第1の縮小動きベクトルSMV1と第2の縮小動きベクトルSMV2の値を拡大して第1の動きベクトルMV1と第2の動きベクトルMV2を生成して出力する。ここで、拡大率は縮小フレームSF0、SF1、SF2の生成の際の縮小率αの逆数に等しく、1/αで表される。 The motion vector expansion unit 7 expands the values of the first reduced motion vector SMV1 and the second reduced motion vector SMV2 to generate and output the first motion vector MV1 and the second motion vector MV2. Here, the enlargement rate is equal to the reciprocal of the reduction rate α when the reduced frames SF0, SF1, and SF2 are generated, and is expressed by 1 / α.

次に、図3及び図4を参照して動きベクトル検出部12のテスト補間部4、補間データ評価部5及び動きベクトル決定部の具体例についてさらに詳しく説明する。

Next, specific examples of the

テスト補間部4は、複数の、即ち第1乃至第Mのテスト補間データ生成部4−1〜4−Mを備え、補間データ評価部5は、第1群の第1乃至第Mの相関値算出部5A−1〜5A−Mと、第2群の第1乃至第Mの相関値算出部5B−1〜5B−Mと、第3群の第1乃至第Mの相関値算出部5C−1〜5C−Mを備える。

The

テスト補間データ生成部4−1〜4−Mは、現縮小フレームSF0のブロックのデータF0B1〜F0BMと、それぞれこれらと対をなす第2の縮小遅延フレームSF2のブロックのデータF2B1〜F2BMを画素ごとに平均することで得られる平均値から成るデータを第1群のテスト補間データTDA1〜TDAMとして算出する。テスト補間データ生成部4−1〜4−Mで、平均を求めるのに用いられるデータは、互いに異なる位置にあるブロックのデータである。

テスト補間部4また、上記のように、現縮小フレームSF0のブロックのデータF0B1〜F0BMを第2群のテスト補間データTDB1〜TDBMとして、第2の縮小遅延フレームSF2のブロックのデータF2B1〜F2BMを第3群のテスト補間データTDC1〜TDCMとして出力する。図1には、テスト補間データTDA1〜TDCMの集合が符号TDで表されている。

The test interpolation data generation units 4-1 to 4-M generate the data F0B1 to F0BM of the block of the current reduced frame SF0 and the data F2B1 to F2BM of the block of the second reduced delay frame SF2 that make a pair with them respectively for each pixel. The data consisting of the average value obtained by averaging is calculated as the first group of test interpolation data TDA1 to TDAM. In the test interpolation data generation units 4-1 to 4 -M, data used for obtaining an average is data of blocks at different positions.

以下、より詳しく説明する。

現縮小フレームSF0の第1のブロックデータF0B1と第2の縮小遅延フレームSF2の第1のブロックデータF2B1がテスト補間データ生成部4−1に入力される。

This will be described in more detail below.

The first block data F0B1 of the current reduced frame SF0 and the first block data F2B1 of the second reduced delay frame SF2 are input to the test interpolation data generation unit 4-1.

テスト補間データ生成部4−1は、現縮小フレームSF0の第1のブロックデータF0B1と第2の縮小遅延フレームSF2の第1のブロックデータF2B1の画素ごとの平均値を第1群の第1のテスト補間データTDA1として相関値算出部5A−1に出力する。ここで画素ごとの平均値とは、現縮小フレームSF0内のブロックにおける各画素と、第2の縮小遅延フレームSF2内のブロックにおける対応する位置の画素の画素値(例えばそれぞれのブロックの基準位置、例えば左上隅を原点として同じ座標値で表される画素の画素値)の平均値を意味する。

The test interpolation data generation unit 4-1 calculates the average value for each pixel of the first block data F0B1 of the current reduced frame SF0 and the first block data F2B1 of the second reduced delay frame SF2 in the first group. It outputs to correlation

同様に、現縮小フレームSF0の第2のブロックデータF0B2と第2の縮小遅延フレームSF2の第2のブロックデータF2B2がテスト補間データ生成部4−2に入力される。テスト補間データ生成部4−2は、現縮小フレームSF0の第2のブロックデータF0B2と第2の縮小遅延フレームSF2の第2のブロックデータF2B2の画素ごとの平均値を第1群の第2のテスト補間データTDA2として相関値算出部5A−2(図示しない)に出力する。

Similarly, the second block data F0B2 of the current reduced frame SF0 and the second block data F2B2 of the second reduced delay frame SF2 are input to the test interpolation data generation unit 4-2. The test interpolation data generation unit 4-2 calculates the average value for each pixel of the second block data F0B2 of the current reduced frame SF0 and the second block data F2B2 of the second reduced delay frame SF2 in the second group of the first group. It outputs to correlation

テスト補間データ生成部4−3(図示しない)〜4−Mも同様に現縮小フレームSF0の第3のブロックデータF0B3乃至第MのブロックデータF0BMと第2の縮小遅延フレームSF2の第3のブロックデータF2B3乃至第MのブロックデータF2BMに基づいて第1群の第3のテスト補間データTDA3乃至第Mのテスト補間データTDAMを生成し、相関値算出部5A−3(図示しない)〜5A−Mに出力する。

Similarly, the test interpolation data generation units 4-3 (not shown) to 4-M also apply the third block data F0B3 to Mth block data F0BM of the current reduced frame SF0 and the third block of the second reduced delay frame SF2. Based on the data F2B3 to Mth block data F2BM, the first group of third test interpolation data TDA3 to Mth test interpolation data TDAM is generated, and correlation

一般化して言えば、テスト補間データ生成部4−mは、現縮小フレームSF0の第mのブロックデータF0Bm(m=1〜M)と第2の縮小遅延フレームSF2の第mのブロックデータF2Bmに基づいて、例えばこれらの画素ごとの平均を求めることで、第1群の第mのテスト補間データTDmを生成し、相関値算出部5A−mに出力する。

Generally speaking, the test interpolation data generation unit 4-m converts the mth block data F0Bm (m = 1 to M) of the current reduced frame SF0 and the mth block data F2Bm of the second reduced delay frame SF2. Based on this, for example, an average for each pixel is obtained, and the m-th test interpolation data TDm of the first group is generated and output to the correlation

テスト補間部4さらに、現縮小フレームSF0のブロックのデータF0B1〜F0BMを、テスト補間データTDB1〜TDBMとして、相関値算出部5B−1〜5B−Mに出力し、第2の縮小遅延フレームSF2のブロックのデータF2B1〜F2BMを、テスト補間データTDC1〜TDCMとして相関値算出部5B−1〜5C−Mに出力する。

一般化して言えば、テスト補間部4は、現縮小フレームSF0の第mのブロックのデータF0Bmを、第2群の第mのテスト補間データTDBmとして相関値算出部5B−mに出力し、第2の縮小遅延フレームSF2の第mのブロックのデータF2Bmを、第3群の第mのテスト補間データTDCmとして相関値算出部5C−mに出力する。

Generally speaking, the

第1の縮小遅延フレームSF1の処理対象ブロックF1Baのデータが補間データ評価部5内の相関値算出部5A−1〜5C−Mに入力される。

Data of the processing target block F1Ba of the first reduced delay frame SF1 is input to the correlation

相関値算出部5A−1〜5C−Mは、それぞれテスト補間部4から出力されるテスト補間データTDA1〜TDCMと第1の縮小遅延フレームSF1の処理対象ブロックF1Baのデータの相関値、例えば差分絶対値和を算出し、評価データEDA1〜EDCMとして出力する。

Correlation

相関値算出部5A−1は、第1群の第1のテスト補間データTDA1の各画素のデータと第1の縮小遅延フレームSF1の処理対象ブロックF1Baの各画素のデータの差分絶対値の和を算出し、評価データEDA1として動きベクトル決定部6に出力する。差分絶対値和は下記の式(1)により表される。

The correlation

ここで、BK1、BK2はブロック内の各画素のデータであり、BK1をテスト補間データTDA1を構成する各画素のデータ、BK2を処理対象ブロックF1Ba内の各画素のデータとすると式(1)は第1群の第1のテスト補間データTDA1の各画素のデータと第1の遅延フレームF1の処理対象ブロックF1Baの各画素のデータの差分絶対値和となる。差分絶対値和SADは、相関の度合いを表すものであり、評価データEDA1として相関値算出部5A−1から出力される。

Here, BK1 and BK2 are the data of each pixel in the block, and BK1 is the data of each pixel constituting the test interpolation data TDA1, and BK2 is the data of each pixel in the processing target block F1Ba. This is the sum of absolute differences between the data of each pixel of the first group of first test interpolation data TDA1 and the data of each pixel of the processing target block F1Ba of the first delay frame F1. The difference absolute value sum SAD represents the degree of correlation, and is output from the correlation

式(1)で与えられる差分絶対値和は、その値が小さいほど、相関が強いことを意味し、差分絶対値和SADを評価データとして用いる場合、その値が小さいほど、評価が高いことを表す。 The difference absolute value sum given by equation (1) means that the smaller the value, the stronger the correlation. When the difference absolute value sum SAD is used as evaluation data, the smaller the value, the higher the evaluation. Represent.

相関値算出部5A−2〜5C−Mも同様に、第1群の第2のテスト補間データTDA2乃至第3群の第Mのテスト補間データTDCMと第1の縮小遅延フレームSF1の処理対象ブロックF1Baのデータの差分絶対値和を算出し、評価データEDA2〜EDCMとして動きベクトル決定部6に出力する。

Similarly, the correlation

評価データEDA1〜EDCMのうち、第1群のテスト補間データTDA1〜TDAMに対応するものを第1群の評価データEDA1〜EDAMと言い、第2群のテスト補間データTDB1〜TDBMに対応するものを第2群の評価データEDB1〜EDBMと言い、第3群のテスト補間データTDC1〜TDCMに対応するものを第3群の評価データEDC1〜EDCMと言う。 Of the evaluation data EDA1 to EDCM, the data corresponding to the first group of test interpolation data TDA1 to TDAM is referred to as the first group of evaluation data EDA1 to EDAM, and the data corresponding to the second group of test interpolation data TDB1 to TDAM. The second group of evaluation data EDB1 to EDBM is referred to as the third group of test interpolation data TDC1 to TDCM, and the third group of evaluation data EDC1 to EDCM is referred to as the third group of evaluation data EDC1 to EDCM.

動きベクトル決定部6は、評価データEDA1〜EDCMのうちの値が最小のもの(最も高い評価を示すもの)を見つける。

The motion

評価データEDA1〜EDCMのうち値が最小のものが第1群の評価データEDA1〜EDAMのいずれかである場合には、動きベクトル決定部6は、第1の縮小遅延フレームSF1の処理対象ブロックF1Baの位置に対する、当該最小値の評価データに対応する、第2の縮小遅延フレームSF2内のブロックの相対位置(位置の差)を第1の縮小動きベクトルSMV1として出力し、第1の縮小遅延フレームSF1の処理対象ブロックF1Baの位置に対する、当該最小値の評価データに対応する、現縮小フレームSF0内のブロックの相対位置(位置の差)を第2の縮小動きベクトルSMV2として出力する。なお、同じ評価データに対応する第2の縮小遅延フレームSF2内のブロックと現縮小フレームSF0内のブロックとは、処理対象ブロックF1Baを中心として点対称の位置にあるので、SMV2=−SMV1の関係がある。

When the evaluation data EDA1 to EDCM having the smallest value is any one of the first group of evaluation data EDA1 to EDAM, the motion

評価データEDA1〜EDCMのうち値が最小のものが第2群の評価データEDB1〜EDBMのいずれかである場合には、動きベクトル決定部6は、第1の縮小遅延フレームSF1の処理対象ブロックF1Baの位置に対する、当該最小値の評価データに対応する、現縮小フレームSF0内のブロックの相対位置(位置の差)を第2の縮小動きベクトルSMV2として出力し、第1の縮小動きベクトルSMV1の代わりに対応するブロックがない(差分絶対値和が十分に小さいブロックがない)こと、即ち有効データがないことを示す信号(データ乃至フラグ)を出力する。

When the evaluation data EDA1 to EDCM having the smallest value is any one of the second group of evaluation data EDB1 to EDBM, the motion

評価データEDA1〜EDCMのうち値が最小のものが第3群の評価データEDB1〜EDCMのいずれかである場合には、動きベクトル決定部6は、第1の縮小遅延フレームSF1の処理対象ブロックF1Baの位置に対する、当該最小値の評価データに対応する、第2の縮小遅延フレームSF2内のブロックの相対位置(位置の差)を第1の縮小動きベクトルSMV1として出力し、第2の縮小動きベクトルSMV2の代わりに対応するブロックがない(差分絶対値和が十分に小さいブロックがない)こと、即ち有効データがないことを示す信号を出力する。

When the evaluation data EDA1 to EDCM having the smallest value is any one of the third group of evaluation data EDB1 to EDCM, the motion

動きベクトル拡大部7は、下記の式(2A)及び式(2B)により縮小動きベクトルSMV1及びSMV2を拡大して、動きベクトルMV1及びMV2を出力する。ここで、縮小動きベクトルSMV1及びSMV2は縮小画像における値(縮小フレーム基準、即ち画像基準の動きベクトル)であり、動きベクトルMV1及びMV2は入力画像における値(入力フレーム基準、即ち入力画像基準の動きベクトル)である。つまり、縮小動きベクトルSMV1及びSMV2は、それぞれ第2の縮小遅延フレームSF2から第1の縮小遅延フレームSF1及び現縮小フレームSF0から第1の縮小遅延フレームSF1への動きベクトルであり、動きベクトルMV1及びMV2はそれぞれ第2の遅延フレームF2から第1の遅延フレームF1、及び現フレームF0から第1の遅延フレームF1への動きベクトルである。 The motion vector enlargement unit 7 enlarges the reduced motion vectors SMV1 and SMV2 by the following equations (2A) and (2B), and outputs the motion vectors MV1 and MV2. Here, the reduced motion vectors SMV1 and SMV2 are values in the reduced image (reduced frame reference, that is, image-based motion vector), and the motion vectors MV1 and MV2 are values in the input image (input frame reference, that is, input image-based motion). Vector). That is, the reduced motion vectors SMV1 and SMV2 are motion vectors from the second reduced delay frame SF2 to the first reduced delay frame SF1 and from the current reduced frame SF0 to the first reduced delay frame SF1, respectively, and the motion vectors MV1 and MV2 is a motion vector from the second delay frame F2 to the first delay frame F1, and from the current frame F0 to the first delay frame F1, respectively.

MV1=SMV1/α …(2A)

MV2=SMV2/α …(2B)

MV1 = SMV1 / α (2A)

MV2 = SMV2 / α (2B)

ただし、縮小動きベクトルSMV1の代わりに対応ブロックなしを示す信号が出力されている場合、動きベクトルMV1の代わりに対応ブロックなしを示す信号を出力し、縮小動きベクトルSMV2の代わりに対応ブロックなしを示す信号が出力されている場合、動きベクトルMV2の代わりに対応ブロックなしを示す信号を出力する。 However, when a signal indicating no corresponding block is output instead of the reduced motion vector SMV1, a signal indicating no corresponding block is output instead of the motion vector MV1, and no corresponding block is indicated instead of the reduced motion vector SMV2. When a signal is output, a signal indicating no corresponding block is output instead of the motion vector MV2.

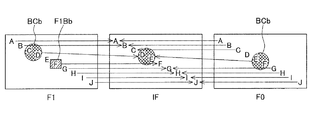

図5は、動きベクトル検出部12の動作を説明するための図である。ここでは、M=1の場合について説明する。

第1の縮小遅延フレームSF1の一部の領域が第1の縮小遅延フレームSF1の処理対象ブロックF1Baとして切り出されている。

FIG. 5 is a diagram for explaining the operation of the motion

A partial area of the first reduced delay frame SF1 is cut out as a processing target block F1Ba of the first reduced delay frame SF1.

第1の縮小遅延フレームSF1の処理対象ブロックF1Baに対してベクトル−V1ずらした位置に対応する領域が第2の縮小遅延フレームSF2の第1のブロックデータF2B1として設定されて切り出され、ベクトル+Vずらした位置に対応する領域が現縮小フレームSF0の第1のブロックデータF0B1として設定されて切り出される。 An area corresponding to the position shifted by the vector −V1 with respect to the processing target block F1Ba of the first reduced delay frame SF1 is set and cut out as the first block data F2B1 of the second reduced delay frame SF2, and shifted by the vector + V. The area corresponding to the selected position is set and cut out as the first block data F0B1 of the current reduced frame SF0.

テスト補間データ生成部4−1は、現縮小フレームSF0の第1のブロックデータF0B1と第2の縮小遅延フレームSF2の第1のブロックデータF2B1を画素ごとに平均してテスト補間データTDA1を生成する。

さらに、テスト補間部4は、現縮小フレームSF0の第1のブロックデータF0B1をテスト補間データTDB1として、第2の縮小遅延フレームSF2の第1のブロックデータF2B1をテスト補間データTDC1として出力する。

The test interpolation data generation unit 4-1 generates the test interpolation data TDA1 by averaging the first block data F0B1 of the current reduced frame SF0 and the first block data F2B1 of the second reduced delay frame SF2 for each pixel. .

Further, the

相関値算出部5A−1は、テスト補間データTDA1と第1の縮小遅延フレームSF1の処理対象ブロックF1Baのデータから上記の式(1)を使って差分絶対値和SADを算出し、評価データEDA1として出力する。

The correlation

相関値算出部5B−1も同様に、テスト補間データTDB1と第1の縮小遅延フレームSF1の処理対象ブロックF1Baのデータから上記の式(1)を使って差分絶対値和SADを算出し、評価データEDB1として出力する。

相関値算出部5C−1も同様に、テスト補間データTDC1と第1の縮小遅延フレームSF1の処理対象ブロックF1Baのデータから上記の式(1)を使って差分絶対値和SADを算出し、評価データEDC1として出力する。

Similarly, the

Similarly, the correlation

動きベクトル決定部6は、評価データEDA1、EDB1、EDC1のうち最小の値を生じさせたブロック又はブロック対と第1の縮小遅延フレームSF1内の処理対象ブロックF1Baの相対位置に基づいて縮小動きベクトルを求める。

The motion

評価データEDA1が最小値である場合には、第1の縮小遅延フレームSF1内の処理対象ブロックF1Baに対する第2の縮小フレームSF2内のブロックの相対位置を第1の縮小動きベクトルSMV1(=V1)として出力し、第1の縮小遅延フレームSF1内の処理対象ブロックF1Baに対する現縮小フレームSF0内のブロックの相対位置を第2の縮小動きベクトルSMV2(=−V1)として出力する。 When the evaluation data EDA1 is the minimum value, the relative position of the block in the second reduced frame SF2 with respect to the processing target block F1Ba in the first reduced delay frame SF1 is expressed as the first reduced motion vector SMV1 (= V1). And the relative position of the block in the current reduced frame SF0 with respect to the processing target block F1Ba in the first reduced delay frame SF1 is output as the second reduced motion vector SMV2 (= −V1).

評価データEDB1が最小値である場合、第1の縮小動きベクトルSMV1の代わりに、対応ブロックなしを示す信号が出力され、第1の縮小遅延フレームSF1内の処理対象ブロックF1Baに対する現縮小フレームSF0内のブロックの相対位置が第2の縮小動きベクトルSMV2(=−V1)として出力される。 When the evaluation data EDB1 is the minimum value, a signal indicating no corresponding block is output instead of the first reduced motion vector SMV1, and the signal in the current reduced frame SF0 for the processing target block F1Ba in the first reduced delay frame SF1 is output. Is output as the second reduced motion vector SMV2 (= −V1).

評価データEDC1が最小値である場合、第1の縮小遅延フレームSF1内の処理対象ブロックF1Baに対する第2の縮小遅延フレームSF2内のブロックの相対位置が第1の縮小動きベクトルSMV1(=V1)として出力され、第2の縮小動きベクトルSMV2の代わりに対応ブロックなしを示す信号が出力される。 When the evaluation data EDC1 is the minimum value, the relative position of the block in the second reduced delay frame SF2 with respect to the processing target block F1Ba in the first reduced delay frame SF1 is the first reduced motion vector SMV1 (= V1). And a signal indicating no corresponding block is output instead of the second reduced motion vector SMV2.

図5では、M=1の場合について説明したが、本発明に係る実施の形態の構成はM=1に限定されない。即ち、候補としてのベクトルに対応するブロック対を2個以上設定しても良い。例えば、第1の縮小遅延フレーム内の処理対象ブロックF1Baに対して、所定の動き量に対応する探索範囲内に位置する第2の縮小遅延フレーム内のすべてのブロック及びこれと点対称位置にある現縮小フレーム内のブロックから成るブロック対について平均値の算出によるテスト補間データの生成を行うこととしても良い。 Although the case of M = 1 has been described in FIG. 5, the configuration of the embodiment according to the present invention is not limited to M = 1. That is, two or more block pairs corresponding to candidate vectors may be set. For example, with respect to the processing target block F1Ba in the first reduced delay frame, all the blocks in the second reduced delay frame located within the search range corresponding to the predetermined motion amount and point symmetric positions thereof. Test interpolation data may be generated by calculating an average value for a block pair consisting of blocks in the current reduced frame.

動きベクトル検出部12では、上記のように実在のデータである第1の縮小遅延フレームSF1内のデータを用いて第2の縮小遅延フレームSF2内のブロック及び現縮小フレームSF0内のブロックから成るブロック対に対応するベクトルの候補を評価することにより動きベクトルを決定しているので第2の縮小遅延フレームSF2及び現縮小フレームSF0から第1の縮小遅延フレームSF1への動きベクトルを精度良く算出することができる。

さらに、第2の縮小遅延フレームSF2内のデータのみ、或いは現縮小フレームSF0内のデータのみを、ベクトル候補に対応するテスト補間データとして用いているので、第2の縮小遅延フレームから現縮小フレームの間で物体が隠れたり、出現したりしても動きベクトルを精度良く算出することができる。

The motion

Furthermore, since only the data in the second reduced delay frame SF2 or only the data in the current reduced frame SF0 is used as test interpolation data corresponding to the vector candidate, the second reduced delay frame to the current reduced frame are changed. Even if an object is hidden or appears in between, a motion vector can be calculated with high accuracy.

なお、補間データ評価部5では差分絶対値和を用いて評価データを算出したが、相関を求める関数は自乗誤差和など他にも多数あり、これに置き換えることも可能である。即ち、補間データ評価部5は、テスト補間データと、処理対象ブロックのデータとの相関を求めるものであれば良く、該相関を示す指標(相関値)は、差分絶対値和以外のものであっても良い。

The interpolation

また、動きベクトル決定部6では、テスト補間データTDA1〜TDCM相互間に異なる重みをつけることで、いずれかのテスト補間データに対応するベクトル候補が、求める動きベクトルであると判定される可能性を高めるようにしても良い。

例えば、相関値算出部5B−1〜5C−Mで求めた差分絶対値和にある係数β1を乗算したものを評価データEDB1〜EDCMとして出力し、相関値算出部5A−1〜5A−Mで求めた差分絶対値和に対して上記の係数β1より小さい係数β2を乗算したものを評価データEDA1〜EDAMとして出力し、動きベクトル決定部6で、これらの評価データEDA1〜EDCMのうちの値が最小のものを見つけるようにしても良い。こうすれば、テスト補間データTDA1〜TDAMに対応するブロック対が求める動きベクトルに対応するものと判断される可能性を高めることができる。言い換えれば、テスト補間データTDA1〜TDAMに対応するブロック対に対応するベクトルを優先的に動きベクトルとして選択することができる。

Further, the motion

For example, the value obtained by multiplying the sum of absolute differences obtained by the correlation

逆に、相関値算出部5B−1〜5C−Mで求めた差分絶対値和にある係数β1を乗算したものを評価データEDB1〜EDCMとして出力し、相関値算出部5A−1〜5A−Mで求めた差分絶対値和に対して上記の係数β1より大きい係数β2を乗算したものを評価データEDA1〜EDAMとして出力し、動きベクトル決定部6で、これらの評価データEDA1〜EDCMのうちの値が最小のものを見つけるようにしても良い。こうすれば、テスト補間データTDB1〜TDCMに対応するブロックが、求める動きベクトルに対応するものと判断される可能性を高めることができる。言い換えれば、テスト補間データTDB1〜TDCMに対応するブロックに対応するベクトルを優先的に動きベクトルとして選択することができる。

Conversely, the sum of absolute differences obtained by the correlation

なお、このような重み付けに加えて、他の要因による重み付けを加えても良い。

例えば、第2の縮小遅延フレームSF2及び現縮小フレームSF0内のブロックのうち、第1の縮小遅延フレームSF1内の処理対象ブロックF1Baの位置に近いブロック又はブロック対(対応するベクトルの絶対値が小さいブロック)について求められる差分絶対値和に対してより小さな係数を乗算することで、より近いブロック又はブロック対が、求める動きベクトルに対応するものと判断される可能性を高めることとしても良い。

要するに、評価データは、差分絶対値和、或いは他の相関値に基づいて定められるものであれば良い。

In addition to such weighting, weighting due to other factors may be added.

For example, among the blocks in the second reduced delay frame SF2 and the current reduced frame SF0, a block or a block pair close to the position of the processing target block F1Ba in the first reduced delay frame SF1 (the absolute value of the corresponding vector is small) It is also possible to increase the possibility that a closer block or block pair is determined to correspond to the desired motion vector by multiplying the sum of absolute differences obtained for the block) by a smaller coefficient.

In short, the evaluation data only needs to be determined based on the sum of absolute differences or other correlation values.

次に、図6〜図8を参照して、動きベクトル変換部13及び補間フレーム生成部14の動作についてより詳細に説明する。

Next, operations of the motion

動きベクトル変換部13は、第2の遅延フレームF2から第1の遅延フレームF1への第1の動きベクトルMV1及び現フレームF0から第1の遅延フレームF1への第2の動きベクトルMV2を、第1の遅延フレームF1から補間フレームIFへの第3の動きベクトルMV3と、現フレームF0から補間フレームIFへの第4の動きベクトルMV4に変換する。

The motion

図6〜図8に示すように入力フレームの時間間隔をt1、第1の遅延フレームF1から補間フレームIFへの時間間隔をt2とした時、下記の式(3A)及び式(3B)により動きベクトルMV3及びMV4を算出する。たとえば、60Hzの入力画像信号から120Hzの画像信号に変換する場合、t1は1/60秒、t2は1/120秒となる。 As shown in FIGS. 6 to 8, when the time interval of the input frame is t1, and the time interval from the first delay frame F1 to the interpolation frame IF is t2, the motion is expressed by the following equations (3A) and (3B). Vectors MV3 and MV4 are calculated. For example, when converting an input image signal of 60 Hz to an image signal of 120 Hz, t1 is 1/60 seconds and t2 is 1/120 seconds.

MV3=MV1×t2/t1 …(3A)

MV4=MV2×(t1−t2)/t1 …(3B)

MV3 = MV1 × t2 / t1 (3A)

MV4 = MV2 × (t1−t2) / t1 (3B)

ただし、動きベクトルMV1の代わりに対応ブロックなしを示す信号が出力されている場合、動きベクトルMV3の代わりに対応ブロックなしを示す信号を出力し、動きベクトルMV2の代わりに対応ブロックなしを示す信号が出力されている場合、動きベクトルMV4の代わりに対応ブロックなしを示す信号を出力する。 However, when a signal indicating no corresponding block is output instead of the motion vector MV1, a signal indicating no corresponding block is output instead of the motion vector MV3, and a signal indicating no corresponding block is output instead of the motion vector MV2. If it is output, a signal indicating no corresponding block is output instead of the motion vector MV4.

このようにして第3及び第4の動きベクトルMV3及びMV4を求めたら、図6〜図8に示すように補間フレームIFからベクトル−MV3の位置の、縮小前の第1の遅延フレームF1のデータ(処理対象ブロックF1Baに対応するブロックF1Bb内のデータ)と補間フレームIFからベクトル−MV4の位置の、縮小前の現フレームF0のデータ(ブロックF1Bbと同じ大きさのブロックのデータ)の双方又は一方に基づいて補間フレームIFのデータ(ブロックF1Bbと同じ大きさのブロックIFBbのデータ)を求める。 When the third and fourth motion vectors MV3 and MV4 are obtained in this way, the data of the first delay frame F1 before reduction at the position of the vector -MV3 from the interpolation frame IF as shown in FIGS. (Data in block F1Bb corresponding to processing target block F1Ba) and / or data of current frame F0 before reduction (data of block having the same size as block F1Bb) at the position of vector-MV4 from interpolation frame IF The data of the interpolation frame IF (the data of the block IFBb having the same size as the block F1Bb) is obtained based on the above.

例えば、図6に示すように、第3及び第4の動きベクトルMV3及びMV4の双方とも、有効なデータである場合(「対応ブロックなし」ではない場合)には、上記の第1の遅延フレームF1内のデータ及び現フレームF0内のデータの平均を補間フレームIFのデータとして算出する。生成したデータから成る補間フレームIFのデータを第1の遅延フレームF1のデータと現フレームF0のデータ間に配置して出力する。

このとき、補間に用いられる第1の遅延フレームF1のブロックデータ(第1の縮小遅延フレームSF1の処理対象ブロックF1Baに対応するブロックF1Bbのデータ)と、現フレームF0のブロックデータ(現縮小フレームSF0のブロックF0B1に対応するブロック)とは、補間フレームIF内の補間により得られるデータの位置を中心として、互いに対称の位置にある。

For example, as shown in FIG. 6, when both the third and fourth motion vectors MV3 and MV4 are valid data (in the case of “no corresponding block”), the first delay frame described above is used. The average of the data in F1 and the data in the current frame F0 is calculated as the data of the interpolation frame IF. The interpolation frame IF data composed of the generated data is arranged and output between the data of the first delay frame F1 and the data of the current frame F0.

At this time, block data of the first delay frame F1 used for interpolation (data of the block F1Bb corresponding to the processing target block F1Ba of the first reduced delay frame SF1) and block data of the current frame F0 (current reduced frame SF0) And a block corresponding to the block F0B1) are symmetrical with respect to the position of data obtained by interpolation in the interpolation frame IF.

図7又は図8に示すように、第3及び第4の動きベクトルMV3及びMV4の一方の代わりに「対応ブロックなし」の信号が出力されている場合には、他方の動きベクトル(第3及び第4の動きベクトルMV3及びMV4のうちの有効なベクトル)に対応する第1の遅延フレームF1内のデータ又は現フレームF0内のデータを、補間フレームIFのデータ(ブロックF1Bbと同じ大きさのブロックIFBbのデータ)として出力する。図7は、第4の動きベクトルMV4の代わりに「対応ブロックなし」の信号が出力されている場合を示し、図8は、第3の動きベクトルMV3の代わりに「対応ブロックなし」の信号が出力されている場合を示す。このように一方のフレーム内のデータをそのまま補間フレームのデータとして出力する処理は「零次補間」と呼ばれる。

補間フレーム生成部14は、このようにして得られたデータから成る補間フレームIFのデータを第1の遅延フレームF1のデータと現フレームF0のデータ間に配置して出力する。

As shown in FIG. 7 or FIG. 8, when a “no corresponding block” signal is output instead of one of the third and fourth motion vectors MV3 and MV4, the other motion vector (third and The data in the first delay frame F1 or the data in the current frame F0 corresponding to the fourth motion vector MV3 and MV4) is the data of the interpolation frame IF (block having the same size as the block F1Bb). (IFBb data). FIG. 7 shows a case where a “no corresponding block” signal is output instead of the fourth motion vector MV4, and FIG. 8 shows that a “no corresponding block” signal is output instead of the third motion vector MV3. Indicates the case of output. The process of outputting data in one frame as it is as interpolation frame data in this way is called “zero-order interpolation”.

The interpolation

図9は、動きベクトル検出部12に入力される現フレームF0のデータ、第1の遅延フレームF1のデータ、第2のフレームF2のデータの対応関係を説明するための図である。図9に示すような映像を表す信号が入力された場合の本実施の形態の動作を説明する。図9に示す映像においては、クロスハッチングで示す丸BCが時間とともに画面の左上から右下へ移動しており、その背後にある英文字(移動なし)が隠れたり見えたりしている。

FIG. 9 is a diagram for explaining a correspondence relationship between the data of the current frame F0, the data of the first delay frame F1, and the data of the second frame F2 input to the motion

図10は図9に示す入力画像を縮小することで得られる縮小画像を表す画像データを示す図である。但し、図10でも画像は図9と同じ大きさに描いてある。図9の画像の要素(丸BC及びA〜Jを示す文字は、図10でもそのまま現れており、従って、英文字A〜Jが丸BCの陰に隠れたり、見えたりしている。

図11〜図17はテスト補間部4及び補間データ評価部5の動作を説明するための図である。図18は動きベクトル拡大部7の動作を説明するための図である。

FIG. 10 is a diagram showing image data representing a reduced image obtained by reducing the input image shown in FIG. However, in FIG. 10, the image is drawn in the same size as FIG. The elements of the image of FIG. 9 (characters indicating the circles BC and A to J appear in FIG. 10 as they are, and therefore the English characters A to J are hidden or visible behind the circle BC.

FIGS. 11 to 17 are diagrams for explaining the operations of the

図10に示すような第2の縮小遅延フレームSF2のデータ、第1の縮小遅延フレームSF1のデータ、現縮小フレームSF0のデータを入力とした場合の動きベクトル検出部12の動作を説明する。なお、ここではM=2を想定している。

The operation of the

テスト補間部4では、動きベクトルの候補ごとにテスト補間データを生成する。

例えば、図11に示すように第1の縮小遅延フレームSF1の一部の領域を第1の縮小遅延フレームSF1の処理対象ブロックF1Baとし、第1の縮小遅延フレームSF1の処理対象ブロックF1Baから−V1ずらした位置の第2の縮小遅延フレームSF2のブロックを第1のブロックF2B1とし、第1の縮小遅延フレームSF1の処理対象ブロックF1BaからV1ずらした位置の現縮小フレームSF0のブロックをブロックF0B1とする。

また、第1の縮小遅延フレームSF1の処理対象ブロックF1Baから−V2ずらした位置の第2の縮小遅延フレームSF2のブロックをブロックF2B2とし、第1の縮小遅延フレームSF1の処理対象ブロックF1BaからV2ずらした位置の現縮小フレームSF0のブロックをブロックF0B2とする。

The

For example, as shown in FIG. 11, a partial area of the first reduced delay frame SF1 is a processing target block F1Ba of the first reduced delay frame SF1, and the processing target block F1Ba of the first reduced delay frame SF1 is −V1. The block of the second reduced delay frame SF2 at the shifted position is set as the first block F2B1, and the block of the current reduced frame SF0 at the position shifted by V1 from the processing target block F1Ba of the first reduced delay frame SF1 is set as the block F0B1. .

Further, the block of the second reduced delay frame SF2 at the position shifted by −V2 from the processing target block F1Ba of the first reduced delay frame SF1 is referred to as a block F2B2, and is shifted by V2 from the processing target block F1Ba of the first reduced delay frame SF1. The block of the current reduced frame SF0 at the position is designated as block F0B2.

図12に示すように、ブロックF2B1のデータとブロックF0B1のデータから得られる画素ごとの平均をテスト補間データTDA1として生成する。

同様に、図13に示すようにブロックF2B2のデータとブロックF0B2のデータから画素ごとの平均をテスト補間データTDA2として生成する。

さらに、図14及び図15に示すように、ブロックF0B1、F0B2のデータをそれぞれテスト補間データTDB1、TDB2として出力する。

同様に、図16及び図17に示すように、ブロックF2B1、F2B2のデータをそれぞれテスト補間データTDC1、TDC2として出力する。

As shown in FIG. 12, an average for each pixel obtained from the data of the block F2B1 and the data of the block F0B1 is generated as the test interpolation data TDA1.

Similarly, as shown in FIG. 13, an average for each pixel is generated as test interpolation data TDA2 from the data in block F2B2 and the data in block F0B2.

Further, as shown in FIGS. 14 and 15, the data of the blocks F0B1 and F0B2 are output as test interpolation data TDB1 and TDB2, respectively.

Similarly, as shown in FIGS. 16 and 17, the data of the blocks F2B1 and F2B2 are output as test interpolation data TDC1 and TDC2, respectively.

補間データ評価部5では、図12〜図17に示されるテスト補間データTDA1〜TD6の各々と処理対象ブロックF1Baのデータとの差分絶対値和を算出し、評価データEDA1〜ED6を出力する。図10〜図17の具体例では、第1の縮小遅延フレームSF1上の文字「F」を表す領域が処理対象ブロックF1Baとなっており、この文字「F」が、第2の縮小遅延フレームSF2および第1の縮小遅延フレームSF1では見えているが、現縮小フレームF0ではハッチングで示す丸BCの陰に隠れており、従って、第2の縮小遅延フレームSF2内の文字「F」を表す領域から成るブロックF2B1から得られたテスト補間データTD5と、処理対象ブロックF1Baとの差分絶対値和、即ち評価データED5が最小となる。

The interpolation

動きベクトル決定部6では、評価データEDA1〜ED6のうち一番小さい評価データED5に対応した縮小動きベクトルSMV1(=V1)を出力し、縮小動きベクトルSMV2の代わりに対応ブロックなしを示す信号を出力する。

The motion

動きベクトル拡大部7では、縮小動きベクトルSMV1とSMV2に対して上記の式(2A)及び式(2B)を用いて、第2の遅延フレームF2から第1の遅延フレームF1への動きベクトルMV1と現フレームF0から第1の遅延フレームF1への動きベクトルMV2を出力する(図18)。

先にも述べたように、縮小動きベクトルの一方の代わりに対応ブロックなしを示す信号が出力されている場合には、当該縮小動きベクトルに対応する動きベクトル(MV1又はMV2)に対しても、代わりに「対応ブロックなし」を示す信号が出力されるので、図10〜図17の例では、動きベクトルMV1(=V1/α)が出力されるとともに、MV2の代わりに対応ブロックなしを示す信号が出力される。

The motion vector enlargement unit 7 uses the above equations (2A) and (2B) for the reduced motion vectors SMV1 and SMV2, and the motion vector MV1 from the second delay frame F2 to the first delay frame F1 A motion vector MV2 from the current frame F0 to the first delay frame F1 is output (FIG. 18).

As described above, when a signal indicating no corresponding block is output instead of one of the reduced motion vectors, the motion vector (MV1 or MV2) corresponding to the reduced motion vector is also output. Instead, a signal indicating “no corresponding block” is output. Therefore, in the examples of FIGS. 10 to 17, the motion vector MV1 (= V1 / α) is output, and a signal indicating no corresponding block is used instead of MV2. Is output.

第1の遅延フレームF1を縮小した第1の縮小遅延フレームSF1についてもれなく(隙間なく)ブロックを設定し縮小動きベクトルを算出することで第1の縮小遅延フレームSF1のすべての部分について第1及び第2の縮小動きベクトルSMV1及び/又はSMV2を、生成し、第1及び第2の縮小動きベクトルSMV1、SMV2を拡大することで、第1及び第2の動きベクトルMV1及び/又はMV2を得て、上記第1の縮小遅延フレームSF1内の上記の画素に対応する第1の遅延フレームF1内の画素に対応する位置、例えば同じ位置にある、補間フレームIF内の画素について、第1及び第2の動きベクトルMV1及びMV2を用いた変換を行うことで、第3及び第4の動きベクトルMV3及びMV4を求めることとしても良い。 By setting a block without any gap (no gap) and calculating a reduced motion vector for the first reduced delay frame SF1 obtained by reducing the first delayed frame F1, the first and second portions of the first reduced delay frame SF1 are all calculated. Generating two reduced motion vectors SMV1 and / or SMV2 and expanding the first and second reduced motion vectors SMV1, SMV2 to obtain first and second motion vectors MV1 and / or MV2, For the pixel in the interpolation frame IF at the position corresponding to the pixel in the first delay frame F1 corresponding to the pixel in the first reduced delay frame SF1, for example, at the same position, the first and second It is also possible to obtain the third and fourth motion vectors MV3 and MV4 by performing conversion using the motion vectors MV1 and MV2. .

代わりに、第1の遅延フレームF1を縮小した第1の縮小遅延フレームSF1内の各画素を中心とする所定の大きさのブロックについて、上記の処理を行うことで、当該画素についての第1の縮小動きベクトルSMV1及び第2の縮小動きベクトルSMV2を生成し、第1及び第2の縮小動きベクトルSMV1、SMV2を拡大することで、第1及び第2の動きベクトルMV1及び/又はMV2を得て、上記第1の縮小遅延フレームSF1内の上記の画素に対応する第1の遅延フレームF1内の画素に対応する位置、例えば同じ位置にある、補間フレームIF内の画素について、第1及び第2の動きベクトルMV1及びMV2を用いた変換を行うことで、第3及び第4の動きベクトルMV3及びMV4を求めることとしても良い。 Instead, by performing the above processing on a block having a predetermined size centered on each pixel in the first reduced delay frame SF1 obtained by reducing the first delay frame F1, the first delay frame F1 is processed. The reduced motion vector SMV1 and the second reduced motion vector SMV2 are generated, and the first and second reduced motion vectors SMV1 and SMV2 are expanded to obtain the first and second motion vectors MV1 and / or MV2. The first and second pixels corresponding to the pixels in the first delay frame F1 corresponding to the pixels in the first reduced delay frame SF1, for example, the pixels in the interpolation frame IF at the same position The third and fourth motion vectors MV3 and MV4 may be obtained by performing conversion using the motion vectors MV1 and MV2.

図19(a)及び(b)は、動きベクトル変換部13の動作の具体例を説明するための図である。図19(a)は動きベクトル変換部13の入力、図19(b)は動きベクトル変換部13の出力を示す。

FIGS. 19A and 19B are diagrams for explaining a specific example of the operation of the motion

動きベクトル変換部13は、図19(a)に示される、第2の遅延フレームF2から第1の遅延フレームF1への第1の動きベクトルMV1と、現フレームF0から第1の遅延フレームF1への動きベクトルMV2に対して上記の式(3A)及び式(3B)を用いて、図19(b)に示される、第1の遅延フレームF1から補間フレームIFへの第3の動きベクトルMV3と現フレームF0から補間フレームIFへの第4の動きベクトルMV4に変換する。図19(a)及び(b)に示す具体例では、MV1はV1/α、MV2の代わりに対応ブロックなしを示す信号が出力されており、t1は1/60秒、t2はt1の1/2に等しく1/120秒であり、上記の式(3A)及び式(3B)よりMV3はV1/2α、MV4の代わりに対応ブロックなしを示す信号が出力される。

The motion

図20は、補間フレーム生成部14の動作の具体例を説明するための図である。図20は、図9〜図17と同様に、第1の遅延フレームF1上の文字「F」を表す領域が処理対象ブロックF1Baに対応するブロック(非縮小ブロック)F1Bbとなっており、この文字「F」が、第2の遅延フレームF2および第1の遅延フレームF1では見えているが、現フレームF0ではクロスハッチングで示す丸BCの陰に隠れており、従って、第2の遅延フレームF2内の文字「F」を表す領域から成るブロックF2B1から得られたテスト補間データTD5と、処理対象ブロックF1Baとの差分絶対値和、即ち評価データED5が最小となる場合を示している。この場合、図20に示すように補間フレームIFから−MV3動かした位置の第1の遅延フレームF1のデータを補間フレームIFのデータとして出力する。

このような処理を、補間フレームIF内のすべてのブロックに対して行うことで生成した補間フレームIFを第1の遅延フレームF1と現フレームF0の間に内挿して出力する。

FIG. 20 is a diagram for explaining a specific example of the operation of the interpolation

The interpolation frame IF generated by performing such processing for all the blocks in the interpolation frame IF is interpolated between the first delay frame F1 and the current frame F0 and output.

以上より、本実施の形態では、動きベクトルの評価を行うことにより動きベクトルが精度良く検出され、画像の乱れなく補間フレームを内挿することができる。さらに補間するフレーム前後で物体が隠れたり出現したりする場合でも、画像の乱れなく補間フレームを内挿することができる。 As described above, in the present embodiment, motion vectors are detected with high accuracy, and interpolation frames can be interpolated without image distortion. Furthermore, even when an object is hidden or appears before and after the interpolated frame, the interpolated frame can be interpolated without image distortion.

ここで現フレームディザ縮小部21、第1の遅延フレームディザ縮小部22、第2の遅延フレームディザ縮小部23にて画像縮小処理をした場合と画像縮小処理をしない場合を比較する。ディザ縮小部21、22、23による画像縮小処理をしない場合、動きベクトル検出部12では入力画像データがそのまま処理され、ディザ縮小部21、22、23による画像縮小処理をする場合、動きベクトル検出部12には縮小画像データが処理される。この時、動きベクトルの探索に当たり、同じ大きさのベクトルの範囲を探索するとした場合、縮小画像を使用した方が広い範囲を探索することができ、従って、大きい動きを検出することができる。

また、縮小画像を用いる場合には、各ブロックに含まれる画素の数が、非縮小画像の各ブロックに含まれる画素の数よりも少なく、各ブロックについての差分絶対値和の計算において計算に用いられる画素の数が少ないので、演算量が減少して、応答性が向上するとともに、回路規模を小さくすることができる。

Here, the case where the image reduction process is performed in the current frame

In the case of using a reduced image, the number of pixels included in each block is smaller than the number of pixels included in each block of the non-reduced image, and is used for calculation in the calculation of the sum of absolute differences for each block. Since the number of pixels to be obtained is small, the amount of calculation is reduced, the response is improved, and the circuit scale can be reduced.

以下、画像の縮小をディザ縮小による効果を説明する。

図21(a)及び(b)、並びに図22(a)及び(b)はディザ縮小の効果を説明するための図である。図21(a)及び図22(a)は、元の画像における画素値の変化のパターンの一例を示す。図21(b)及び図22(b)は、図21(a)及び図22(a)の画像を通常の方法で(ディザ縮小を用いずに)一次元方向に縮小することで得られる縮小画像における画素値の変化のパターンを示す。図21(a)及び(b)の画像に類似する領域を、図22(a)及び(b)の画像中で探索する場合を想定する。図21(a)の縮小前の画像の点線PAaで囲んだ領域に対して、図22(a)の縮小前の画像では(図示の範囲においては)、領域PBaが類似していることが簡単に検出される。一方、図21(b)の縮小画像中の領域QAaに対しては、図22(b)の縮小画像中の領域QBaよりも領域QBbがより類似していると判断されてしまい、マッチングの誤りが生じる。これは縮小画像において、画素を配置する位相を一定にした場合には、その位相によって画素値の変化のパターンが大きく変わることがあるためである。これに対してディザ縮小ではランダムに位相をずらすことで縮小画像における画素値の変化のパターンの位相への依存度を平均化することができ、その結果、上記のようなマッチングの誤りを低減できる。

Hereinafter, an effect of dithering reduction of an image will be described.

FIGS. 21A and 21B and FIGS. 22A and 22B are diagrams for explaining the effect of dither reduction. FIG. 21A and FIG. 22A show examples of pixel value change patterns in the original image. FIGS. 21B and 22B show the reductions obtained by reducing the images of FIGS. 21A and 22A in the one-dimensional direction by a normal method (without using dither reduction). The pattern of a change in pixel value in an image is shown. Assume that a region similar to the images in FIGS. 21A and 21B is searched in the images in FIGS. 22A and 22B. In the image before reduction in FIG. 22A (in the range shown in the figure), the area PBa is easily similar to the area surrounded by the dotted line PAa in the image before reduction in FIG. Detected. On the other hand, for the area QAa in the reduced image in FIG. 21B, it is determined that the area QBb is more similar to the area QBa in the reduced image in FIG. Occurs. This is because in the reduced image, when the phase in which the pixels are arranged is made constant, the change pattern of the pixel value may greatly change depending on the phase. On the other hand, in dither reduction, the phase dependency of the pixel value change pattern in the reduced image can be averaged by shifting the phase at random, and as a result, matching errors as described above can be reduced. .

以上、本発明を画像処理装置及び画像表示方法として説明したが、上記の装置で実施される画像処理方法及び画像表示方法もまた本発明の一部を成す。

また、本発明をハードウェアで実現する場合について説明したが、図1に示される構成の一部又は全部をソフトウェアにより実現することも可能である。その場合の処理を図23及び図24を参照して説明する。

Although the present invention has been described above as an image processing apparatus and an image display method, the image processing method and the image display method implemented by the above apparatus also form part of the present invention.

Further, although the case where the present invention is realized by hardware has been described, part or all of the configuration shown in FIG. 1 can be realized by software. Processing in that case will be described with reference to FIGS.

図23は、図1に示される構成のうち、フレームメモリ11、動きベクトル検出部12、動きベクトル変換部13及び補間フレーム生成部14による処理をソフトウェアで実現するための、コンピュータシステムで構成された画像処理装置を示す。図示の画像処理装置は、プロセッサ101と、プログラムメモリ102と、データメモリ103と、入力インターフェース104と、出力インターフェース105と、これらを接続するバス106を有する。

FIG. 23 is composed of a computer system for realizing the processing by the

プロセッサ101は、プログラムメモリ102に記憶されたプログラムに従って動作し、入力インターフェース104を介して入力される画像に対する処理を行う。動作の過程で種々のデータをデータメモリ103に記憶させる。処理の結果生成される画像は、インターフェース105を介して図1に示す画像表示部15に供給され、画像表示部15による表示に用いられる。

以下、プロセッサ101により行なわれる処理を、図24を参照して説明する。

The

Hereinafter, processing performed by the

図24は、図23の画像処理装置で実施される画像処理方法のフローを示す。 FIG. 24 shows a flow of an image processing method implemented by the image processing apparatus of FIG.

まず、動きベクトル検出ステップST1では、画像データF0と、画像データF0に対して1フレーム遅延した画像データF1と、画像データF0に対して2フレーム分遅延した画像データF2を参照して第2の遅延フレームF2から第1の遅延フレームF1への第1の動きベクトルMV1、及び現フレームF0から第1の遅延フレームF1への第2の動きベクトルV2を生成する。この動作は、図1の動きベクトル検出部12と同等である。

First, in the motion vector detection step ST1, the second reference is made with reference to the image data F0, the image data F1 delayed by one frame with respect to the image data F0, and the image data F2 delayed by two frames with respect to the image data F0. A first motion vector MV1 from the delay frame F2 to the first delay frame F1 and a second motion vector V2 from the current frame F0 to the first delay frame F1 are generated. This operation is equivalent to the motion

動きベクトル変換ステップST2では、第1及び第2の動きベクトルMV1及びMV2を、第1の遅延フレームF1から補間フレームIF(現フレームF0と第1の遅延フレームF1の間に挿入される)への第3の動きベクトルMV3と、現フレームF0から補間フレームIFへの第4の動きベクトルMV4に変換する。この動作は、図1の動きベクトル変換部13と同等である。

In the motion vector conversion step ST2, the first and second motion vectors MV1 and MV2 are transferred from the first delay frame F1 to the interpolation frame IF (inserted between the current frame F0 and the first delay frame F1). The third motion vector MV3 and the fourth motion vector MV4 from the current frame F0 to the interpolation frame IF are converted. This operation is equivalent to the motion

補間フレーム生成ステップST3では、第1の遅延フレームF1のデータ、現フレームF0のデータ、第3の動きベクトルMV3及び第4の動きベクトルMV4から補間フレームIFのデータを生成する。補間フレームIFのすべてのブロックについて上記の処理が繰り返され、これにより生成された補間フレームIFのデータを現フレームF0のデータと第1の遅延フレームF1のデータの間に挿入した画像データDOを生成する。この動作は、図1の補間フレーム生成部14と同等である。

In the interpolation frame generation step ST3, data of the interpolation frame IF is generated from the data of the first delay frame F1, the data of the current frame F0, the third motion vector MV3, and the fourth motion vector MV4. The above processing is repeated for all the blocks of the interpolation frame IF, and image data DO is generated by inserting the data of the generated interpolation frame IF between the data of the current frame F0 and the data of the first delay frame F1. To do. This operation is equivalent to the interpolation

図24は、本実施の形態に係る画像表示装置の一部をソフトウェアとして実現したものであり、その効果は、図1の場合と同様である。 FIG. 24 realizes a part of the image display apparatus according to the present embodiment as software, and the effect is the same as in the case of FIG.

2 ディザ縮小部、 3 ブロック切り出し部、 4 テスト補間部、 5 補間データ評価部、 6 動きベクトル決定部、 7 動きベクトル拡大部、 10 画像処理装置、 11 フレームメモリ、 12 動きベクトル検出部、 13 動きベクトル変換部、 14 補間フレーム生成部、 15 画像表示部、 21 現フレームディザ縮小部、 22 第1の遅延フレームディザ縮小部、 23 第2の遅延フレームディザ縮小部、 31 現フレームブロック切り出し部、 32 第1の遅延フレームブロック切り出し部、 33 第2の遅延フレームブロック切り出し部。 2 dither reduction unit, 3 block cutout unit, 4 test interpolation unit, 5 interpolation data evaluation unit, 6 motion vector determination unit, 7 motion vector enlargement unit, 10 image processing device, 11 frame memory, 12 motion vector detection unit, 13 motion Vector conversion unit, 14 interpolation frame generation unit, 15 image display unit, 21 current frame dither reduction unit, 22 first delay frame dither reduction unit, 23 second delay frame dither reduction unit, 31 current frame block cutout unit, 32 A first delayed frame block cutout unit, 33 a second delayed frame block cutout unit.

Claims (16)

前記第1の遅延フレームのデータ及び前記現フレームの2フレーム前のフレームである第2の遅延フレームのデータを参照して前記第2の遅延フレームから前記第1の遅延フレームへの第1の動きベクトルを算出し、前記現フレームのデータ及び前記第1の遅延フレームのデータを参照して前記現フレームから前記第1の遅延フレームへの第2の動きベクトルを算出する動きベクトル検出部と、

前記第1の動きベクトルを前記第1の遅延フレームから前記補間フレームへの第3の動きベクトルに変換し、前記第2の動きベクトルを前記現フレームら前記補間フレームへの第4の動きベクトルに変換する動きベクトル変換部と、

前記第3の動きベクトル、前記第4の動きベクトル、前記第1の遅延フレームのデータ、及び前記現フレームのデータから、前記補間フレームのデータを生成し、前記補間フレームのデータを前記現フレームのデータと前記第1の遅延フレームのデータの間に挿入した画像データを出力する補間フレーム生成部とを有し、

前記動きベクトル検出部は、

前記現フレームを画素ごとにランダムに位相をずらして縮小して現縮小フレームを出力し、前記第1の遅延フレームを画素ごとにランダムに位相をずらして縮小して第1の縮小遅延フレームを出力し、前記第2の遅延フレームを画素ごとにランダムに位相をずらして縮小して第2の縮小遅延フレームを出力するディザ縮小部と、

前記現縮小フレーム、前記第1の縮小遅延フレーム及び前記第2の縮小遅延フレームから検出された動きベクトルを拡大して出力する動きベクトル拡大部とを有する

ことを特徴とする画像処理装置。 In an image processing apparatus for inserting an interpolation frame between a current frame of an image and a first delay frame which is a frame one frame before the current frame,

The first movement from the second delay frame to the first delay frame with reference to the data of the first delay frame and the data of the second delay frame which is a frame two frames before the current frame A motion vector detector that calculates a vector and calculates a second motion vector from the current frame to the first delay frame by referring to the data of the current frame and the data of the first delay frame;

The first motion vector is converted into a third motion vector from the first delay frame to the interpolation frame, and the second motion vector is converted into a fourth motion vector from the current frame to the interpolation frame. A motion vector conversion unit to convert,

The interpolation frame data is generated from the third motion vector, the fourth motion vector, the first delay frame data, and the current frame data, and the interpolation frame data is converted into the current frame data. An interpolation frame generator for outputting image data inserted between the data and the data of the first delay frame,

The motion vector detection unit

The current frame is reduced by shifting the phase at random for each pixel, and the current reduced frame is output. The first delayed frame is reduced by shifting the phase at every pixel, and the first reduced delay frame is output. A dither reduction unit that outputs the second reduced delay frame by reducing the phase of the second delayed frame at random for each pixel, and

An image processing apparatus comprising: a motion vector expansion unit that expands and outputs a motion vector detected from the current reduced frame, the first reduced delay frame, and the second reduced delay frame.

前記補間フレームの補間対象ブロックに対応する、前記第1の縮小遅延フレーム内のブロックを処理対象ブロックとして設定し、前記第2の縮小遅延フレームの一部をなすブロックのデータ及び前記現縮小フレームの一部をなすブロックのデータの画素ごとの平均値で構成される第1群のテスト補間データと、前記現フレームの一部をなすブロックのデータで構成される第2群のテスト補間データと、前記第2の縮小遅延フレームのブロックデータで構成される第3群のテスト補間データとを含む複数のテスト補間データを出力するテスト補間部と、

前記第1乃至第3群のテスト補間データのうち、前記処理対象ブロックのデータに対する前記各テスト補間データの相関の強さを評価し、該評価の結果を示す複数の評価データを出力する補間データ評価部と、

前記複数の評価データのうち最も相関の強いことを示す前記評価データを生じさせた前記テスト補間データに対応する動きベクトルを第1の縮小動きベクトル及び第2の縮小動きベクトルの少なくとも一方として出力する動きベクトル決定部とをさらに有し、

前記動きベクトル拡大部は、前記第1の縮小動きベクトル及び第2の縮小動きベクトルの少なくとも一方を拡大して前記第1及び第2の動きベクトルの少なくとも一方として出力し、

前記第1群のテスト補間データは、複数の前記第2の縮小遅延フレームのブロックのデータ及び複数の前記現縮小フレームのブロックから得られ、

前記第2群のテスト補間データは、複数の前記現縮小フレームのブロックから得られ、

前記第3群のテスト補間データは、複数の前記第2の縮小遅延フレームのブロックから得られる

ことを特徴とする請求項1に記載の画像処理装置。 The motion vector detection unit

A block in the first reduced delay frame corresponding to the interpolation target block of the interpolation frame is set as a processing target block, and data of a block forming a part of the second reduced delay frame and the current reduced frame A first group of test interpolation data composed of an average value for each pixel of block data forming a part; a second group of test interpolation data composed of block data forming part of the current frame; A test interpolation unit that outputs a plurality of test interpolation data including a third group of test interpolation data composed of block data of the second reduced delay frame;

Interpolation data that evaluates the strength of correlation of each test interpolation data with respect to the data of the processing target block among the first to third groups of test interpolation data and outputs a plurality of evaluation data indicating the results of the evaluation An evaluation unit;

A motion vector corresponding to the test interpolation data that has generated the evaluation data indicating the strongest correlation among the plurality of evaluation data is output as at least one of the first reduced motion vector and the second reduced motion vector. A motion vector determination unit;

The motion vector expansion unit expands at least one of the first reduced motion vector and the second reduced motion vector and outputs it as at least one of the first and second motion vectors;

The first group of test interpolation data is obtained from a plurality of blocks of the second reduced delay frame and a plurality of blocks of the current reduced frame;

The second group of test interpolation data is obtained from a plurality of blocks of the current reduced frame;

The image processing apparatus according to claim 1, wherein the third group of test interpolation data is obtained from a plurality of blocks of the second reduced delay frame.

各々前記第1の縮小遅延フレーム内の複数の画素から成る複数のブロックを順次処理対象ブロックとして選択し、該処理対象ブロックを中心として、

互いに点対称の位置にある、前記第2の縮小遅延フレーム内のブロックと、前記現縮小フレーム内のブロックとを抽出し、抽出した前記第2の縮小遅延フレームのブロックのデータと抽出した前記現縮小フレームのブロックのデータの画素毎の平均値を、前記第1群のテスト補間データとして求め、

前記抽出した前記現縮小フレーム内の前記ブロックのデータを前記第2群のテスト補間データとして出力し、

前記抽出した前記第2の縮小遅延フレーム内の前記ブロックのデータを前記第3群のテスト補間データとして出力する

ことを特徴とする請求項2に記載の画像処理装置。 The test interpolation unit includes:

A plurality of blocks each consisting of a plurality of pixels in each of the first reduced delay frames are sequentially selected as processing target blocks, and the processing target block is the center.

A block in the second reduced delay frame and a block in the current reduced frame, which are located symmetrically with respect to each other, are extracted, and data of the extracted block of the second reduced delay frame and the extracted current block are extracted. the average value of each pixel data of the block of the reduced small frame, determined as test interpolation data of the first group,

Outputting the data of the block in the extracted current reduced frame as the second group of test interpolation data;

The image processing apparatus according to claim 2, wherein the extracted data of the block in the second reduced delay frame is output as the third group of test interpolation data.

該複数個のテスト補間データ生成部は、それぞれ、前記現縮小フレーム内の互いに異なる位置ブロックのデータと前記第2の縮小遅延フレーム内の互いに異なる位置のブロックのデータを画素ごとに平均することで得られるデータを前記第1群のテスト補間データとして算出する

ことを特徴とする請求項3に記載の画像処理装置。 The test interpolation unit has a plurality of test interpolation data generation units,

Each of the plurality of test interpolation data generation units averages the data of different position blocks in the current reduced frame and the data of blocks in different positions in the second reduced delay frame for each pixel. The image processing apparatus according to claim 3, wherein the obtained data is calculated as the first group of test interpolation data.

前記テスト補間部から出力される前記複数のテスト補間データの各々と、

前記処理対象ブロックのデータとの間の相関を示す相関値を算出し、

該複数のテスト補間データについてそれぞれ求められる複数の相関値に基づいて前記複数の評価データを生成する

ことを特徴とする請求項2から4までのいずれか1項に記載の画像処理装置。 The interpolation data evaluation unit

Each of the plurality of test interpolation data output from the test interpolation unit,

Calculating a correlation value indicating a correlation with the data of the processing target block;

The image processing apparatus according to any one of claims 2 to 4, wherein the plurality of evaluation data are generated based on a plurality of correlation values respectively obtained for the plurality of test interpolation data.

前記テスト補間部から出力される前記複数のテスト補間データと

前記処理対象ブロックのデータとの間の差分の絶対値の総和である差分絶対値和を前記相関値として算出する

ことを特徴とする請求項5に記載の画像処理装置。 The interpolation data evaluation unit

The difference absolute value sum that is a sum of absolute values of differences between the plurality of test interpolation data output from the test interpolation unit and data of the processing target block is calculated as the correlation value. Item 6. The image processing apparatus according to Item 5 .

前記処理対象ブロックのデータと、前記複数のテスト補間データとの差分絶対値和を算出する複数個の相関値算出部を有する

ことを特徴とする請求項6に記載の画像処理装置。 The interpolation data evaluation unit

The image processing apparatus according to claim 6, further comprising a plurality of correlation value calculation units that calculate a sum of absolute differences between the data of the processing target block and the plurality of test interpolation data.

前記補間フレーム生成部から出力された画像データに基づく画像を表示する画像表示部と

を有することを特徴とする画像表示装置。 An image processing apparatus according to any one of claims 1 to 7,

An image display device comprising: an image display unit that displays an image based on the image data output from the interpolation frame generation unit.

前記第1の遅延フレームのデータ及び前記現フレームの2フレーム前のフレームである第2の遅延フレームのデータを参照して前記第2の遅延フレームから前記第1の遅延フレームへの第1の動きベクトルを算出し、前記現フレームのデータ及び前記第1の遅延フレームのデータを参照して前記現フレームから前記第1の遅延フレームへの第2の動きベクトルを算出する動きベクトル検出ステップと、

前記第1の動きベクトルを前記第1の遅延フレームから前記補間フレームへの第3の動きベクトルに変換し、前記第2の動きベクトルを前記現フレームから前記補間フレームへの第4の動きベクトルに変換する動きベクトル変換ステップと、

前記第3の動きベクトル、前記第4の動きベクトル、前記第1の遅延フレームのデータ、及び前記現フレームのデータから、前記補間フレームのデータを生成し、前記補間フレームのデータを前記現フレームのデータと前記第1の遅延フレームのデータの間に挿入した画像データを出力する補間フレーム生成ステップとを有し、

前記動きベクトル検出ステップは、

前記現フレームを画素ごとにランダムに位相をずらして縮小して現縮小フレームを出力し、前記第1の遅延フレームを画素ごとにランダムに位相をずらして縮小して第1の縮小遅延フレームを出力し、前記第2の遅延フレームを画素ごとにランダムに位相をずらして縮小して第2の縮小遅延フレームを出力するディザ縮小ステップと、

前記現縮小フレーム、前記第1の縮小遅延フレーム及び前記第2の縮小遅延フレームから検出された動きベクトルを拡大して出力する動きベクトル拡大ステップとを有する

ことを特徴とする画像処理方法。 In an image processing method of inserting an interpolation frame between a current frame of an image and a first delay frame that is a frame one frame before the current frame,

The first movement from the second delay frame to the first delay frame with reference to the data of the first delay frame and the data of the second delay frame which is a frame two frames before the current frame A motion vector detecting step of calculating a vector and calculating a second motion vector from the current frame to the first delay frame with reference to the data of the current frame and the data of the first delay frame;

Converting the first motion vector into a third motion vector from the first delay frame to the interpolation frame, and converting the second motion vector into a fourth motion vector from the current frame to the interpolation frame; A motion vector conversion step to convert,

The interpolation frame data is generated from the third motion vector, the fourth motion vector, the first delay frame data, and the current frame data, and the interpolation frame data is converted into the current frame data. An interpolation frame generating step of outputting image data inserted between the data and the data of the first delay frame,

The motion vector detection step includes

The current frame is reduced by shifting the phase at random for each pixel, and the current reduced frame is output. The first delayed frame is reduced by shifting the phase at every pixel, and the first reduced delay frame is output. A dither reduction step of reducing the second delay frame by shifting the phase at random for each pixel and outputting a second reduced delay frame;

An image processing method comprising: a motion vector expansion step of expanding and outputting a motion vector detected from the current reduced frame, the first reduced delay frame, and the second reduced delay frame.

前記補間フレームの補間対象ブロックに対応する、前記第1の縮小遅延フレーム内のブロックを処理対象ブロックとして設定し、前記第2の縮小遅延フレームの一部をなすブロックのデータ及び前記現縮小フレームの一部をなすブロックのデータの画素ごとの平均値で構成される第1群のテスト補間データと、前記現フレームの一部をなすブロックのデータで構成される第2群のテスト補間データと、前記第2の縮小遅延フレームのブロックデータで構成される第3群のテスト補間データとを含む複数のテスト補間データを出力するテスト補間ステップと、

前記第1乃至第3群のテスト補間データのうち、前記処理対象ブロックのデータに対する前記各テスト補間データの相関の強さを評価し、該評価の結果を示す複数の評価データを出力する補間データ評価ステップと、

前記複数の評価データのうち最も相関の強いことを示す前記評価データを生じさせた前記テスト補間データに対応する動きベクトルを第1の縮小動きベクトル及び第2の縮小動きベクトルの少なくとも一方として出力する動きベクトル決定ステップとをさらに有し、

前記動きベクトル拡大ステップは、前記第1の縮小動きベクトル及び第2の縮小動きベクトルの少なくとも一方を拡大して前記第1及び第2の動きベクトルの少なくとも一方として出力し、

前記第1群のテスト補間データは、複数の前記第2の縮小遅延フレームのブロックのデータ及び複数の前記現縮小フレームのブロックから得られ、

前記第2群のテスト補間データは、複数の前記現縮小フレームのブロックから得られ、

前記第3群のテスト補間データは、複数の前記第2の縮小遅延フレームのブロックから得られる

ことを特徴とする請求項9に記載の画像処理方法。 The motion vector detection step includes

A block in the first reduced delay frame corresponding to the interpolation target block of the interpolation frame is set as a processing target block, and data of a block forming a part of the second reduced delay frame and the current reduced frame A first group of test interpolation data composed of an average value for each pixel of block data forming a part; a second group of test interpolation data composed of block data forming part of the current frame; A test interpolation step of outputting a plurality of test interpolation data including a third group of test interpolation data composed of block data of the second reduced delay frame;

Interpolation data that evaluates the strength of correlation of each test interpolation data with respect to the data of the processing target block among the first to third groups of test interpolation data and outputs a plurality of evaluation data indicating the results of the evaluation An evaluation step;

A motion vector corresponding to the test interpolation data that has generated the evaluation data indicating the strongest correlation among the plurality of evaluation data is output as at least one of the first reduced motion vector and the second reduced motion vector. A motion vector determination step,

The motion vector expansion step expands at least one of the first reduced motion vector and the second reduced motion vector and outputs it as at least one of the first and second motion vectors;

The first group of test interpolation data is obtained from a plurality of blocks of the second reduced delay frame and a plurality of blocks of the current reduced frame;

The second group of test interpolation data is obtained from a plurality of blocks of the current reduced frame;

10. The image processing method according to claim 9, wherein the third group of test interpolation data is obtained from a plurality of blocks of the second reduced delay frame.

各々前記第1の縮小遅延フレーム内の複数の画素から成る複数のブロックを順次処理対象ブロックとして選択し、該処理対象ブロックを中心として、

互いに点対称の位置にある、前記第2の縮小遅延フレーム内のブロックと、前記現縮小フレーム内のブロックとを抽出し、抽出した前記第2の縮小遅延フレームのブロックのデータと抽出した前記現縮小フレームのブロックのデータの画素毎の平均値を、前記第1群のテスト補間データとして求め、

前記抽出した前記現縮小フレーム内の前記ブロックのデータを前記第2群のテスト補間データとして出力し、

前記抽出した前記第2の縮小遅延フレーム内の前記ブロックのデータを前記第3群のテスト補間データとして出力する

ことを特徴とする請求項10に記載の画像処理方法。 The test interpolation step includes:

A plurality of blocks each consisting of a plurality of pixels in each of the first reduced delay frames are sequentially selected as processing target blocks, and the processing target block is the center.

A block in the second reduced delay frame and a block in the current reduced frame, which are located symmetrically with respect to each other, are extracted, and data of the extracted block of the second reduced delay frame and the extracted current block are extracted. the average value of each pixel data of the block of the reduced small frame, determined as test interpolation data of the first group,

Outputting the data of the block in the extracted current reduced frame as the second group of test interpolation data;

11. The image processing method according to claim 10, wherein data of the block in the extracted second reduced delay frame is output as the third group of test interpolation data.

該複数個のテスト補間データ生成ステップは、それぞれ、前記現縮小フレーム内の互いに異なる位置ブロックのデータと前記第2の縮小遅延フレーム内の互いに異なる位置のブロックのデータを画素ごとに平均することで得られるデータを前記第1群のテスト補間データとして算出する

ことを特徴とする請求項11に記載の画像処理方法。 The test interpolation step includes a plurality of test interpolation data generation steps,