JP5969769B2 - Charge pump circuit and electronic device - Google Patents

Charge pump circuit and electronic device Download PDFInfo

- Publication number

- JP5969769B2 JP5969769B2 JP2012017650A JP2012017650A JP5969769B2 JP 5969769 B2 JP5969769 B2 JP 5969769B2 JP 2012017650 A JP2012017650 A JP 2012017650A JP 2012017650 A JP2012017650 A JP 2012017650A JP 5969769 B2 JP5969769 B2 JP 5969769B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- charge pump

- pump circuit

- schottky diode

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Dc-Dc Converters (AREA)

Description

本発明は、チャージポンプ回路およびそれを備える電子機器に関する。 The present invention relates to a charge pump circuit and an electronic device including the same.

チャージポンプ回路は、入力電圧を昇圧するための回路として周知である。さらに、チャージポンプ回路を含む半導体集積回路も知られている。半導体基板に形成されたチャージポンプ回路の場合、寄生トランジスタが動作することにより、ラッチアップが起こる可能性がある。 The charge pump circuit is well known as a circuit for boosting an input voltage. A semiconductor integrated circuit including a charge pump circuit is also known. In the case of a charge pump circuit formed on a semiconductor substrate, latch-up may occur due to the operation of a parasitic transistor.

たとえば特開2008−277832号公報(特許文献1)は、寄生トランジスタの動作に起因するラッチアップを防止するためのチャージポンプ回路の構成を開示する。このチャージポンプ回路は、第1の電圧発生部、第2の電圧発生部、第3の電圧発生部、およびラッチアップ防止部を備える。ラッチアップ防止部は、第3の電圧発生部から出力される信号が所定の電圧レベルに達するまで、寄生トランジスタによるラッチアップ動作を防止する。 For example, Japanese Patent Laying-Open No. 2008-277832 (Patent Document 1) discloses a configuration of a charge pump circuit for preventing latch-up caused by the operation of a parasitic transistor. The charge pump circuit includes a first voltage generation unit, a second voltage generation unit, a third voltage generation unit, and a latch-up prevention unit. The latch-up prevention unit prevents the latch-up operation by the parasitic transistor until the signal output from the third voltage generation unit reaches a predetermined voltage level.

特開2008−277832号公報(特許文献1)に開示されたチャージポンプ回路は、外付けのショットキーダイオードを用いることなく寄生トランジスタによるラッチアップ動作を防止するよう構成される。外付けのショットキーダイオードを用いないことにより、コストの上昇を抑えることができる。しかしながら、チャージポンプ回路の構成が複雑になるだけでなく、その回路の制御も複雑になるという課題が発生する。 The charge pump circuit disclosed in Japanese Patent Laying-Open No. 2008-277832 (Patent Document 1) is configured to prevent a latch-up operation by a parasitic transistor without using an external Schottky diode. By not using an external Schottky diode, an increase in cost can be suppressed. However, there arises a problem that not only the configuration of the charge pump circuit is complicated, but also the control of the circuit is complicated.

本発明の目的は、チャージポンプ回路のコストの上昇を抑えつつ、寄生トランジスタによるラッチアップ動作を抑えることを可能にすることである。 An object of the present invention is to make it possible to suppress a latch-up operation by a parasitic transistor while suppressing an increase in cost of a charge pump circuit.

本発明のある局面において、チャージポンプ回路は、第1の導電型の第1の領域を有する半導体基板と、クロック信号に応じたスイッチングによって電荷を転送するトランジスタとを備える。トランジスタは、第1の領域に形成された、第2の導電型の第2の領域と、第2の領域に形成された、第1の導電型の第3の領域と、第2の領域に形成された、第1の導電型の第4の領域とを含む。チャージポンプ回路は、第1の領域において第2の領域の外側に形成され、第1の領域の電圧をクランプするショットキーダイオードをさらに備える。 In one aspect of the present invention, a charge pump circuit includes a semiconductor substrate having a first region of a first conductivity type, and a transistor that transfers charges by switching according to a clock signal. The transistor includes a second region of the second conductivity type formed in the first region, a third region of the first conductivity type formed in the second region, and a second region. And a fourth region of the first conductivity type formed. The charge pump circuit further includes a Schottky diode that is formed outside the second region in the first region and clamps the voltage in the first region.

好ましくは、ショットキーダイオードは、第2の領域と、第2の導電型の第5の領域との間に配置される。第5の領域には、第2の領域とは独立に電圧が印加される。 Preferably, the Schottky diode is disposed between the second region and the fifth region of the second conductivity type. A voltage is applied to the fifth region independently of the second region.

好ましくは、半導体基板を平面視した場合、ショットキーダイオードは、第2の領域の少なくとも一部の輪郭に沿って形成される。 Preferably, when the semiconductor substrate is viewed in plan, the Schottky diode is formed along the outline of at least a part of the second region.

好ましくは、ショットキーダイオードは、複数の素子に分割されている。

本発明の別の局面において、電子機器は、チャージポンプ回路と、チャージポンプ回路の出力電圧を電源電圧に用いて動作する回路とを備える。チャージポンプ回路は、第1の導電型の第1の領域を有する半導体基板と、クロック信号に応じたスイッチングによって電荷を転送するトランジスタとを含む。トランジスタは、第1の領域に形成された、第2の導電型の第2の領域と、第2の領域に形成された、第1の導電型の第3の領域と、第2の領域に形成され、第2の領域と電気的に接続された、第1の導電型の第4の領域とを含む。チャージポンプ回路は、第1の領域において第2の領域の外側に形成され、第1の領域の電圧をクランプするショットキーダイオードをさらに含む。

Preferably, the Schottky diode is divided into a plurality of elements.

In another aspect of the present invention, an electronic device includes a charge pump circuit and a circuit that operates using an output voltage of the charge pump circuit as a power supply voltage. The charge pump circuit includes a semiconductor substrate having a first region of a first conductivity type, and a transistor that transfers charges by switching according to a clock signal. The transistor includes a second region of the second conductivity type formed in the first region, a third region of the first conductivity type formed in the second region, and a second region. And a fourth region of the first conductivity type formed and electrically connected to the second region. The charge pump circuit further includes a Schottky diode that is formed outside the second region in the first region and clamps the voltage of the first region.

本発明によれば、チャージポンプ回路のコストの上昇を抑えつつ、寄生トランジスタによるラッチアップ動作を抑えることができる。 According to the present invention, it is possible to suppress a latch-up operation by a parasitic transistor while suppressing an increase in cost of a charge pump circuit.

以下、この発明の実施の形態について、図面を参照しながら詳細に説明する。なお、図中同一または相当部分には同一符号を付してその説明は繰り返さない。 Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. In the drawings, the same or corresponding parts are denoted by the same reference numerals and description thereof will not be repeated.

図1は、この発明の一実施形態によるチャージポンプ回路を備えた例示的な電子機器のブロック図である。図1を参照して、電子機器101は、ディスプレイ102と、回路基板103とを備える。チャージポンプ回路1と、ドライバ104とは回路基板103に実装される。

FIG. 1 is a block diagram of an exemplary electronic device including a charge pump circuit according to an embodiment of the present invention. With reference to FIG. 1, the

電子機器101は、たとえば携帯電話(スマートフォンを含む)、タブレット、ゲーム機、PDA、カーオーディオ等であるが、これらに限定されるものではない。ディスプレイ102は、たとえば液晶ディスプレイである。回路基板103は、たとえばフレキシブルプリント基板である。チャージポンプ回路1は、ドライバ104の電源回路である。チャージポンプ回路1は、電源電圧VDDを昇圧して、その昇圧された電圧(電圧VGH)をドライバ104に供給する。ドライバ104は、チャージポンプ回路1から供給された電圧VGHを用いてディスプレイ102を駆動する。

The

図2は、図1に示したチャージポンプ回路1の概略的な構成を示した回路図である。図2を参照して、チャージポンプ回路1は、PチャネルMOS(Metal Oxide Semiconductor)トランジスタMP1,MP2と、制御回路3と、インバータ5と、コンデンサC1,C2とを備える。PチャネルMOSトランジスタMP1,MP2と、制御回路3と、インバータ5とは、半導体チップ2に形成される。

FIG. 2 is a circuit diagram showing a schematic configuration of

PチャネルMOSトランジスタMP1,MP2は、電荷転送用のトランジスタである。PチャネルMOSトランジスタMP1,MP2は、直列に接続される。PチャネルMOSトランジスタMP1のソースは、電源電圧VDDを受ける。PチャネルMOSトランジスタMP1のドレインは、PチャネルMOSトランジスタMP2のソースに接続される。PチャネルMOSトランジスタMP2のドレインは端子T1に接続される。各々のPチャネルMOSトランジスタのバックゲートは、そのPチャネルMOSトランジスタのドレインに接続される。 P-channel MOS transistors MP1 and MP2 are charge transfer transistors. P-channel MOS transistors MP1 and MP2 are connected in series. The source of P-channel MOS transistor MP1 receives power supply voltage VDD. The drain of P channel MOS transistor MP1 is connected to the source of P channel MOS transistor MP2. The drain of P-channel MOS transistor MP2 is connected to terminal T1. The back gate of each P channel MOS transistor is connected to the drain of the P channel MOS transistor.

端子T1にはコンデンサC1が接続される。コンデンサC1は、端子T1に接続される一方端と、接地される他方端とを有する。電圧VGHが端子T1から出力される。 A capacitor C1 is connected to the terminal T1. Capacitor C1 has one end connected to terminal T1 and the other end grounded. The voltage VGH is output from the terminal T1.

制御回路3は、所定の周期を有するクロックCLKを発生させる。インバータ5は、クロックCLKを反転させて、クロック/CLKを出力する。さらに制御回路3は、PチャネルMOSトランジスタMP1,MP2の各々のスイッチングを制御する。 The control circuit 3 generates a clock CLK having a predetermined cycle. Inverter 5 inverts clock CLK and outputs clock / CLK. Furthermore, the control circuit 3 controls the switching of each of the P channel MOS transistors MP1 and MP2.

PチャネルMOSトランジスタMP1,MP2の接続点は、端子T2を介してコンデンサC2の一方端に接続される。クロック/CLKは、端子T3を介してコンデンサC2の他方端に結合される。 A connection point of the P-channel MOS transistors MP1 and MP2 is connected to one end of the capacitor C2 via the terminal T2. Clock / CLK is coupled to the other end of capacitor C2 via terminal T3.

図3は、図1および図2に示したチャージポンプ回路の動作を説明する波形図である。図2および図3を参照して、クロック/CLKの電圧がVDDである場合、クロック/CLKのレベルはH(ハイ)レベルである。一方、クロック/CLKの電圧がVSである場合、クロック/CLKのレベルはL(ロー)レベルである。たとえば電圧VSは、接地電圧である。 FIG. 3 is a waveform diagram for explaining the operation of the charge pump circuit shown in FIGS. 2 and 3, when the voltage of clock / CLK is VDD, the level of clock / CLK is H (high) level. On the other hand, when the voltage of clock / CLK is VS, the level of clock / CLK is L (low) level. For example, the voltage VS is a ground voltage.

クロック/CLKがLレベルである場合には、PチャネルMOSトランジスタMP1はオン状態であり、PチャネルMOSトランジスタMP2はオフ状態である。この場合、コンデンサC1が充電されるため、PチャネルMOSトランジスタMP1,MP2の接続点の電圧V1はVDDに等しい。 When clock / CLK is at L level, P-channel MOS transistor MP1 is in an on state and P-channel MOS transistor MP2 is in an off state. In this case, since the capacitor C1 is charged, the voltage V1 at the connection point of the P-channel MOS transistors MP1 and MP2 is equal to VDD.

一方、クロック/CLKがHレベルである場合には、PチャネルMOSトランジスタMP1はオフ状態であり、PチャネルMOSトランジスタMP2はオン状態である。この場合、端子T3の電圧が接地電圧からVDDに変化するため、電圧V1はVDDから2VDDに変化する。電圧V1は、PチャネルMOSトランジスタMP2および端子T1を通じて出力される。上記の動作が繰り返されることにより、2VDDに等しい電圧VGHが端子T1から出力される。 On the other hand, when clock / CLK is at the H level, P channel MOS transistor MP1 is in an off state and P channel MOS transistor MP2 is in an on state. In this case, since the voltage at the terminal T3 changes from the ground voltage to VDD, the voltage V1 changes from VDD to 2VDD. The voltage V1 is output through the P channel MOS transistor MP2 and the terminal T1. By repeating the above operation, a voltage VGH equal to 2VDD is output from the terminal T1.

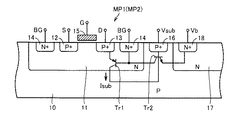

図4は、図2に示された回路が形成された半導体チップの概略的な断面図である。図4を参照して、PチャネルMOSトランジスタMP1,MP2は、P型の半導体基板10に形成される。以下では、PチャネルMOSトランジスタMP1の構成について代表的に説明する。

FIG. 4 is a schematic cross-sectional view of a semiconductor chip on which the circuit shown in FIG. 2 is formed. Referring to FIG. 4, P channel

PチャネルMOSトランジスタMP1は、N型ウェル11と、P+領域12,13と、N+領域14と、ゲート電極15とを有する。P+領域12,13およびN+領域14はN型ウェル11に形成される。P+領域12,13は、それぞれ、PチャネルMOSトランジスタMP1のソース電極(S)およびドレイン電極(D)に接続される。

P-channel

半導体基板10の表面にはP+領域16が形成される。P+領域16および半導体基板10の電圧は基板電圧(電圧Vsub)である。さらに、N型ウェル11から分離したN型ウェル17が半導体基板10に形成される。たとえば、N型ウェル17は、図2に示された制御回路3あるいはインバータ5に含まれるPチャネルMOSトランジスタの一部である。N+領域18はN型ウェル17に形成される。N+領域18には、電圧Vbが印加される。電圧Vbは、たとえば電源電圧VDDあるいは接地電圧である。

A P +

チャージポンプ回路の起動時には、PチャネルMOSトランジスタMP1のドレイン(P+領域13)の電圧がバックゲート(N+領域14)の電圧よりも高くなる可能性がある。この場合、P+領域13、N型ウェル11および半導体基板10によって形成される寄生PNPトランジスタTr1がオンする。これにより、P+領域13からN型ウェル11を介して半導体基板10に電流Isubが流れる。

When the charge pump circuit is started, the voltage of the drain (P + region 13) of the P-channel MOS transistor MP1 may be higher than the voltage of the back gate (N + region 14). In this case, the parasitic PNP transistor Tr1 formed by the P +

一方、N型ウェル11、半導体基板10(およびP+領域16)、およびN型ウェル17によって寄生NPNトランジスタTr2が形成される。電流Isubが流れることによって、寄生NPNトランジスタTr2がオンする可能性がある。

On the other hand, the N-

このように、図3に示したチャージポンプ回路では寄生PNPトランジスタTr1および寄生NPNトランジスタTr2の動作によってラッチアップが生じる可能性がある。なお、図4に示された構成によれば、N型ウェル17は、PチャネルMOSトランジスタMP1に隣接する。しかしながらPチャネルMOSトランジスタMP2にN型ウェル17が隣接する場合にも、上記したような寄生PNPトランジスタおよび寄生NPNトランジスタの動作によりラッチアップが起こる可能性がある。

As described above, in the charge pump circuit shown in FIG. 3, latch-up may occur due to the operations of the parasitic PNP transistor Tr1 and the parasitic NPN transistor Tr2. According to the configuration shown in FIG. 4, N-

図5は、本発明の実施の形態に係るチャージポンプ回路による、ラッチアップを防止するための構成を示した図である。図4および図5を参照して、本発明の実施の形態によれば、ショットキーダイオードD1が寄生NPNトランジスタTr2のベースおよび寄生PNPトランジスタTr1のコレクタに接続される。後に詳細に説明するように、ショットキーダイオードD1のアノードは、P+領域16に接続される。ショットキーダイオードD1のカソードは、接地される。寄生NPNトランジスタTr2のエミッタも接地されるものとする。

FIG. 5 is a diagram showing a configuration for preventing latch-up by the charge pump circuit according to the embodiment of the present invention. Referring to FIGS. 4 and 5, according to the embodiment of the present invention, Schottky diode D1 is connected to the base of parasitic NPN transistor Tr2 and the collector of parasitic PNP transistor Tr1. As described in detail later, the anode of Schottky diode D1 is connected to P +

寄生NPNトランジスタTr2のベースの電圧は、半導体基板10の基板電圧(Vsub)にほぼ等しい。寄生PNPトランジスタTr1に電流Isubが流れた場合、ショットキーダイオードD1によって、電圧VsubはVfにクランプされる。Vfはショットキーダイオードの順方向電圧であり、約0.2Vである。寄生NPNトランジスタTr2のベースの電圧が約0.7Vに達しなければ、寄生NPNトランジスタTr2はオンしない。したがって図5に示された構成によれば、寄生NPNトランジスタTr2がオンすることを防ぐことができる。この結果、ラッチアップを防止することができる。

The base voltage of the parasitic NPN transistor Tr2 is substantially equal to the substrate voltage (Vsub) of the

従来は、ショットキーダイオードは、チャージポンプ回路を含む半導体回路に外付けされていた。本発明の実施の形態によれば、ショットキーダイオードは半導体装置に含まれる。したがって、チャージポンプ回路のコストの上昇を抑えつつ、寄生トランジスタによるラッチアップ動作を抑えることができる。 Conventionally, a Schottky diode is externally attached to a semiconductor circuit including a charge pump circuit. According to the embodiment of the present invention, the Schottky diode is included in the semiconductor device. Therefore, it is possible to suppress the latch-up operation by the parasitic transistor while suppressing an increase in the cost of the charge pump circuit.

図6は、図5に示した回路の一構成例を説明するための半導体基板の概略断面図である。図6を参照して、ショットキーダイオードD1は、N型ウェル11とN型ウェル17との間に配置される。N型ウェル11とN型ウェル17とは、互いに独立に電圧が印加される。たとえばチャージポンプ回路の起動時には、N型ウェル17は接地される。

FIG. 6 is a schematic cross-sectional view of a semiconductor substrate for explaining a configuration example of the circuit shown in FIG. Referring to FIG. 6,

ショットキーダイオードD1は、N型ウェル20と、N+領域21と、P型ウェル22と、P+領域23と、シリサイド電極24とによって構成される。N+領域21とP型ウェル22とはN型ウェル20に形成される。P+領域23はP型ウェル22に形成される。P型ウェル22、P+領域23、N型ウェル20はシリサイド電極24に接続される。

The Schottky diode D1 includes an N-

N+領域21は、接地される。P+領域16,16Aの各々の電圧はVsubである。シリサイド電極24には、電圧Vsubが与えられる。

N +

なお、ショットキーダイオードD1は、公知の半導体製造技術を用いて形成可能である。さらに、他の素子とともにショットキーダイオードD1を形成することができる。したがって、図4に示された構成にショットキーダイオードD1を追加した場合にも、製造工程数の増加を抑制することができる。したがって本発明の実施の形態によれば、チャージポンプ回路のコストの上昇を抑えることができる。 Note that the Schottky diode D1 can be formed using a known semiconductor manufacturing technique. Furthermore, the Schottky diode D1 can be formed together with other elements. Therefore, even when the Schottky diode D1 is added to the configuration shown in FIG. 4, an increase in the number of manufacturing steps can be suppressed. Therefore, according to the embodiment of the present invention, an increase in the cost of the charge pump circuit can be suppressed.

図7は、ショットキーダイオードD1とともに形成される素子の一例を示した概略断面図である。図7を参照して、NチャネルMOSトランジスタは、P型の半導体基板10に形成されたP型ウェル31と、N+領域32,33と、P+領域34と、ゲート電極35とにより構成される。

FIG. 7 is a schematic cross-sectional view showing an example of an element formed together with the Schottky diode D1. Referring to FIG. 7, the N-channel MOS transistor includes a P-type well 31 formed in a P-

N+領域32,33はP型ウェル22に形成される。N+領域32は、ドレイン電極(D)に接続される。N+領域33はソース電極(S)に接続される。P型ウェル22(バックゲート)の電圧を設定するために、P+領域23がP型ウェル22に形成される。N+領域32,33およびP+領域34の各々は、シリサイド電極36に接触する。

N +

図6と図7とを参照して、P型ウェル31は、P型ウェル22が形成される工程により形成される。N+領域32,33は、N+領域14,18,21が形成される工程により形成される。ゲート電極35は、ゲート電極15を形成する工程によって形成される。シリサイド電極36は、シリサイド電極24を形成する工程によって形成される。P領域34は、P+領域12,13,16,16Aを形成する工程によって形成される。

With reference to FIGS. 6 and 7, P-

以上のように、本発明の実施の形態によれば、チャージポンプ回路は、第1の導電型の第1の領域を有する半導体基板(10)と、クロック信号に応じたスイッチングによって電荷を転送するPチャネルMOSトランジスタ(MP1,MP2)とを備える。なお、「第1の領域」とはこの実施の形態では、N型ウェルを形成するための領域すなわちP型の領域である。PチャネルMOSトランジスタ(MP1,MP2)は、その第1の領域に形成されたN型ウェル11と、N型ウェル11に形成された、P+領域12,13とを含む。N型ウェル11、P+領域12,13は、それぞれ「第2の領域」、「第3の領域」および「第4の領域」に対応する。N型ウェル17は「第5の領域」に対応する。

As described above, according to the embodiment of the present invention, the charge pump circuit transfers charges by switching according to the clock signal and the semiconductor substrate (10) having the first region of the first conductivity type. P-channel MOS transistors (MP1, MP2). In this embodiment, the “first region” is a region for forming an N-type well, that is, a P-type region. P-channel MOS transistors (

チャージポンプは、ショットキーダイオードD1をさらに備える。ショットキーダイオードは、半導体基板10の第1の領域においてN型ウェル11の外側に形成される。ショットキーダイオードD1は、第1の領域の電圧をクランプする。

The charge pump further includes a Schottky diode D1. The Schottky diode is formed outside the N-type well 11 in the first region of the

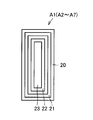

図8は、図6に示したショットキーダイオードの概略的な平面レイアウトの例を示した図である。図8を参照して、PチャネルMOSトランジスタMP1がチップ端の近傍に配置される。 FIG. 8 is a diagram showing an example of a schematic plan layout of the Schottky diode shown in FIG. Referring to FIG. 8, P channel MOS transistor MP1 is arranged in the vicinity of the chip end.

PチャネルMOSトランジスタMP1の周囲の領域のうち、チップ端側の領域にはP+領域41が形成されるものの、他の素子は形成されない。したがって、ショットキーダイオードD1は、PチャネルMOSトランジスタMP1が形成された領域の三方を囲むように形成される。言い換えると、ショットキーダイオードD1は、PチャネルMOSトランジスタMP1の周囲の領域のうち、チップ端側の領域を除く領域に形成される。

Of the regions around the P-channel MOS transistor MP1, the P +

ショットキーダイオードD1とPチャネルMOSトランジスタMP1との間にP+領域16が形成される。さらにショットキーダイオードD1とN型ウェル17との間にP+領域16Aが形成される。N型ウェル17にはN+領域18が形成される。

A P +

ショットキーダイオードD1は、複数の領域A1〜A7にそれぞれ形成された複数の素子によって構成される。領域の数は図8に示されるように限定されるものではない。ショットキーダイオードD1が複数の素子に分割されることにより、ショットキーダイオードD1の全体のリーク電流を少なくすることができる。 The Schottky diode D1 includes a plurality of elements formed in the plurality of regions A1 to A7, respectively. The number of regions is not limited as shown in FIG. By dividing the Schottky diode D1 into a plurality of elements, the overall leakage current of the Schottky diode D1 can be reduced.

なお、図が煩雑になることを避けるために、図8では金属配線(シリサイド電極を含む)は示されていない。同様の理由によって、以後説明する図においても金属配線が省略される。 Note that metal wiring (including silicide electrodes) is not shown in FIG. 8 in order to avoid complication of the figure. For the same reason, the metal wiring is omitted in the drawings described below.

図9は、図8に示した領域A1の平面レイアウトの概略を示した図である。図9を参照して、領域A1には、N型ウェル20が形成される。N型ウェル20にはN+領域21が形成される。N+領域21によって囲まれた領域の内側にP型ウェル22が形成される。P型ウェル22にはP+領域23が形成される。領域A2〜A7の各々も領域A1と同様の平面レイアウトを有する。

FIG. 9 is a diagram showing an outline of the planar layout of the region A1 shown in FIG. Referring to FIG. 9, an N-

図10は、図6に示したショットキーダイオードの概略的な平面レイアウトの他の例を示した図である。図10は図8と対比される図である。図10を参照して、領域A11は、複数の領域A1〜A7が互いにつながった領域に対応する。 FIG. 10 is a diagram showing another example of a schematic planar layout of the Schottky diode shown in FIG. FIG. 10 is a diagram contrasted with FIG. Referring to FIG. 10, a region A11 corresponds to a region where a plurality of regions A1 to A7 are connected to each other.

図11は、図6に示したショットキーダイオードの概略的な平面レイアウトのさらに別の例を示した図である。図11は図8と対比される図である。図11を参照して、PチャネルMOSトランジスタMP1の周囲の領域に他の素子が形成される。図11では、PチャネルMOSトランジスタMP1は、N型ウェル17,17Aに挟まれる。なお、N型ウェル17AにはN+領域18Aが形成される。

FIG. 11 is a diagram showing still another example of the schematic planar layout of the Schottky diode shown in FIG. FIG. 11 is a diagram contrasted with FIG. Referring to FIG. 11, another element is formed in a region around P channel MOS transistor MP1. In FIG. 11, the P-channel MOS transistor MP1 is sandwiched between N-

P+領域16は、PチャネルMOSトランジスタMP1の四方を囲むように形成される。ショットキーダイオードD1は、P+領域16を囲むように形成される。したがって、ショットキーダイオードD1は、PチャネルMOSトランジスタMP1の四方を囲むように形成される。具体的には、ショットキーダイオードD1は、複数の領域A21〜A30に分割して形成される。複数の領域A21〜A30の各々の平面レイアウトは、図9に示されたレイアウトと同様であるので、以後の説明は繰り返さない。

P +

図12は、図6に示したショットキーダイオードの概略的な平面レイアウトのさらに別の例を示した図である。図12は図11と対比される図である。図12を参照して、領域A31は、複数の領域A21〜A30が互いにつながった領域に対応する。 FIG. 12 is a diagram showing still another example of a schematic planar layout of the Schottky diode shown in FIG. FIG. 12 is a diagram contrasted with FIG. Referring to FIG. 12, a region A31 corresponds to a region where a plurality of regions A21 to A30 are connected to each other.

なお、図8、図10〜図12に示された平面レイアウトにおいて、PチャネルMOSトランジスタMP1をPチャネルMOSトランジスタMP2へと置き換えてもよい。図8、図10〜図12に示さるように、ショットキーダイオードD1は、半導体基板を平面視した場合に、PチャネルMOSトランジスタMP1(またはMP2)が形成されるN型ウェルの領域の、少なくとも一部の輪郭に沿って形成される。 In the planar layouts shown in FIGS. 8 and 10 to 12, P channel MOS transistor MP1 may be replaced with P channel MOS transistor MP2. As shown in FIG. 8 and FIG. 10 to FIG. 12, the Schottky diode D1 includes at least an N-type well region where the P-channel MOS transistor MP1 (or MP2) is formed when the semiconductor substrate is viewed in plan view. Formed along some contours.

以上のように、この実施の形態によれば、チャージポンプ回路は、半導体基板10の電圧をクランプするショットキーダイオードを備える。ショットキーダイオードは、半導体基板10に形成される。これにより、チャージポンプ回路のコストの上昇を抑えつつ、寄生トランジスタによるラッチアップ動作を抑えることができる。

As described above, according to this embodiment, the charge pump circuit includes the Schottky diode that clamps the voltage of the

なお、電荷を移動するためのトランジスタがNチャネルMOSトランジスタであってもよい。この場合、図6に示された導電型は、その導電型と逆の導電型に置換される。このような構成であっても基板電圧をクランプするショットキーダイオードによって、チャージポンプ回路のラッチアップを防止することができる。 Note that the transistor for transferring charges may be an N-channel MOS transistor. In this case, the conductivity type shown in FIG. 6 is replaced with a conductivity type opposite to the conductivity type. Even with this configuration, the Schottky diode that clamps the substrate voltage can prevent the charge pump circuit from being latched up.

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施の形態の説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。 The embodiment disclosed this time should be considered as illustrative in all points and not restrictive. The scope of the present invention is shown not by the above description of the embodiments but by the scope of claims for patent, and is intended to include meanings equivalent to the scope of claims for patent and all modifications within the scope.

1 チャージポンプ回路、2 半導体チップ、3 制御回路、5 インバータ、10 半導体基板、11,17,17A,20 N型ウェル、12,13,16,16A P+領域、15,35 ゲート電極、14,18,18A,21,32,33 N+領域、22,31 P型ウェル、24,36 シリサイド電極、101 電子機器、102 ディスプレイ、103 回路基板、104 ドライバ、A1〜A7,A11,A21〜A31 領域、D1 ショットキーダイオード、MP1,MP2 PチャネルMOSトランジスタ、Tr1,Tr2 寄生NPNトランジスタ、T1〜T3 端子。

DESCRIPTION OF

Claims (5)

第1の導電型の第1の領域を有する半導体基板と、

クロック信号に応じたスイッチングによって電荷を転送するトランジスタとを備え、

前記トランジスタは、

前記第1の領域に形成された、第2の導電型の第2の領域と、

前記第2の領域に形成された、第1の導電型の第3の領域と、

前記第2の領域に形成された、第1の導電型の第4の領域とを含み、

前記チャージポンプ回路は、

前記第1の領域において前記第2の領域の外側に形成され、前記第1の領域の電圧をクランプするショットキーダイオードをさらに備え、

前記ショットキーダイオードは、前記第2の領域と、前記第2の導電型の第5の領域との間に配置され、

前記第5の領域には、前記第2の領域とは独立に電圧が印加され、

前記ショットキーダイオードは、

前記第1の領域に形成された、第2の導電型の第6の領域と、

前記第6の領域に形成された、第1の導電型の第7の領域とを含み、

前記第6の領域は、接地に電気的に接続され、

前記第7の領域は、前記第1の領域と同じ電位に接続される、チャージポンプ回路。 A charge pump circuit,

A semiconductor substrate having a first region of a first conductivity type;

A transistor that transfers charges by switching according to a clock signal,

The transistor is

A second region of the second conductivity type formed in the first region;

A third region of the first conductivity type formed in the second region;

A fourth region of the first conductivity type formed in the second region,

The charge pump circuit

A Schottky diode formed outside the second region in the first region and clamping the voltage of the first region ;

The Schottky diode is disposed between the second region and the fifth region of the second conductivity type;

A voltage is applied to the fifth region independently of the second region ,

The Schottky diode is

A sixth region of the second conductivity type formed in the first region;

A seventh region of the first conductivity type formed in the sixth region,

The sixth region is electrically connected to ground;

The charge pump circuit , wherein the seventh region is connected to the same potential as the first region .

前記チャージポンプ回路の出力電圧を電源電圧に用いて動作する回路とを備える、電子機器。 The charge pump circuit according to any one of claims 1 to 4 ,

Ru and a circuit that operates using the output voltage of the charge pump circuit to the supply voltage, the electronic device.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012017650A JP5969769B2 (en) | 2012-01-31 | 2012-01-31 | Charge pump circuit and electronic device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012017650A JP5969769B2 (en) | 2012-01-31 | 2012-01-31 | Charge pump circuit and electronic device |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013158164A JP2013158164A (en) | 2013-08-15 |

| JP2013158164A5 JP2013158164A5 (en) | 2015-04-02 |

| JP5969769B2 true JP5969769B2 (en) | 2016-08-17 |

Family

ID=49052848

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012017650A Active JP5969769B2 (en) | 2012-01-31 | 2012-01-31 | Charge pump circuit and electronic device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5969769B2 (en) |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5131171B2 (en) * | 2001-11-21 | 2013-01-30 | 富士電機株式会社 | Semiconductor device |

| JP4383159B2 (en) * | 2003-12-25 | 2009-12-16 | Necエレクトロニクス株式会社 | Charge pump circuit |

-

2012

- 2012-01-31 JP JP2012017650A patent/JP5969769B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013158164A (en) | 2013-08-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100922681B1 (en) | Charge pump circuit | |

| JP4699851B2 (en) | Booster circuit | |

| US7439795B2 (en) | Charge pump circuit with reduced parasitic capacitance | |

| US20140307354A1 (en) | Esd protection circuit | |

| US9369038B2 (en) | Semiconductor integrated circuit and power supply circuit | |

| TWI765956B (en) | Semiconductor device | |

| US20120161857A1 (en) | Charge pump circuit | |

| US9812437B2 (en) | Semiconductor integrated circuit device, and electronic appliance using the same | |

| KR102371786B1 (en) | Power supply switching circuit and semiconductor device | |

| US20060164135A1 (en) | Driver circuit | |

| JP5969769B2 (en) | Charge pump circuit and electronic device | |

| US8742829B2 (en) | Low leakage digital buffer using bootstrap inter-stage | |

| JP5618963B2 (en) | Semiconductor device | |

| KR20100138196A (en) | Charge pump | |

| JP5027464B2 (en) | Power supply device, liquid crystal drive device, display device | |

| JP2017120968A (en) | Circuit device and electronic equipment | |

| JP4075830B2 (en) | Power supply circuit and driver IC, liquid crystal display device and electronic apparatus using the same | |

| CN112470383B (en) | Charge pump circuit device | |

| US7177167B2 (en) | Semiconductor device containing charge pump type step-up circuit featuring bipolar transistor for carrying out initial charging | |

| JP4965069B2 (en) | Semiconductor integrated circuit | |

| KR20110085698A (en) | Device for providing negative voltage | |

| JP5675566B2 (en) | Bootstrap circuit and inverter device including the same | |

| JP2008283071A (en) | Semiconductor device | |

| JP2014041986A (en) | Semiconductor device | |

| JP2007060872A (en) | Booster circuit and electric apparatus using the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150130 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150210 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20151215 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20151216 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160125 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160614 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160708 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5969769 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |